Description:

The Pixel Address Manager (PAM) of the WD9500 chip set contains:

CPU Interface Unit (CIU), which controls communication with the system bus (via the CPU interface logic block external to the chip set), and passes data to and from all the other units on the chip set. It also performs certain miscellaneous functions, such as forwarding addresses from the system bus to the EPROM.

Graphics Processor (GP), which performs the actual drawing computations. It supports all 8514/A graphics modes plus Western Digital extensions. The modes include line drawing, area fill, area outline drawing (arbitrary polyigons), rectangle drawing, image transfer from the CPU, BITBLT copying (Bit Block Transfer within VRAM), and scissoring. The GP receives its drawing instructions from the CIU and sends the resulting pixels coordinates to the MIC.

Memory Interface Controller (MIC), which controls VRAM addressing and access. In a typical drawing operation, it converts the DP supplied pixel coordinates into VRAM addresses, causes the VRAM to send teh addressed data (pixel color values) to the DP for modification, and then rewrites them back into VRAM. When not involved in a drawing or special-purpose access, the MIC manages the VRAM addressing portion of the constantly on-going screen refresh process. The MIC gives screen refresh the highest priority for VRAM access; next is timer-based VRAM chip refresh. DP-requested drawing access has the lowest priority.

Disclaimer

The info found in this page might not be entirely correct. Check out this guide to learn how you can improve it.

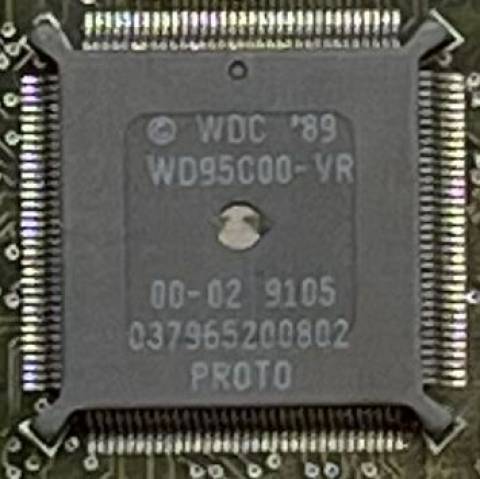

Image 1 of 1 (Douglar)

Image 1 of 1 (Douglar)