# User's Manual

VIA *K8T800* mainboard for AMD Socket 754 based Athlon 64 processor

#### **TRADEMARK**

All products and company names are trademarks or registered trademarks of their respective holders.

These specifications are subject to change without notice.

Manual Revision 1.0 November 02, 2004

## **DISCLAIMER OF WARRANTIES:**

THERE ARE NO WARRANTIES WHICH EXTEND BEYOND THE

DESCRIPTION ON THE FACE OF THE MANUFACTURER LIMITED

WARRANTY. THE MANUFACTURER EXPRESSLY EXCLUDES ALL

OTHER WARRANTIES, EXPRESS OR IMPLIED, REGARDING ITS

PRODUCTS; INCLUDING ANY IMPLIED WARRANTIES OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR

NONINFRINGEMENT. THIS DISCLAIMER OF WARRANTIES SHALL

APPLY TO THE EXTENT ALLOWED UNDER LOCAL LAWS IN THE

COUNTRY PURCHASED IN WHICH LOCAL LAWS DO NOT ALLOW OR

LIMIT THE EXCLUSION OF THE IMPLIED WARRANTIES.

## **80 Port Frequently Asked Questions**

Below is a list of some basic POST Codes, possible problems and solutions. For more detailed information about POST Codes, refer to Appendix C in this manual.

| POST CODE  | Problem                                                                                                                     | Solution                                                                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FFh or CFh | 1.BIOS chip inserted incorrectly 2. Incorrect BIOS update version 3. Mainboard problem 4. Add-on card inserted incorrectly. | 1. Reinsert the BIOS chip 2. Download the correct BIOS version update from the manufacturer's Web site. 3. Replace mainboard 4. Remove and replace the add-on card |

| C1h - C5h  | Memory module     inserted incorrectly     Memory compatibility     problem     Memory module     damaged                   | Reinsert memory     module     Replace memory     with correct type     Replace memory     module                                                                  |

| 2Dh        | Error occured in VGA     BIOS     VGA card inserted     incorrectly                                                         | Replace VGA card     Reinsert the VGA     card                                                                                                                     |

| 26h        | Overclock error                                                                                                             | Clear CMOS or press the insert<br>key to power on the system                                                                                                       |

| 07h - 12h  | Initial Keyboard     controller error     RTC error                                                                         | Ensure that the keyboard and mouse are connected correctly.      Replace the RTC battery.                                                                          |

## **Table of Contents**

|           |                                     | Page |

|-----------|-------------------------------------|------|

| Section 1 | Introduction                        |      |

|           | Package Contents                    | 1-1  |

|           | Mainboard Features                  | 1-2  |

|           | System Block Diagram                | 1-5  |

| Section 2 | Specification                       |      |

|           | Mainboard Specification             | 2-1  |

| Section 3 | Installation                        |      |

|           | Mainboard Layout                    | 3-1  |

|           | Easy Installation Procedure         | 3-2  |

|           | CPU Insertion                       | 3-2  |

|           | Jumper Settings                     | 3-4  |

|           | System Memory Configuration         | 3-5  |

|           | Expansion Slots                     | 3-6  |

|           | Device Connectors                   | 3-7  |

|           | Power-On/Off (Remote)               | 3-13 |

|           | External Modem Ring-in Power ON and |      |

|           | Keyboard Power ON Function (KBPO)   | 3-13 |

|           | STR (Suspend To RAM) Function       | 3-14 |

|           | CPU Overheating Protection          | 3-15 |

| Section 4 | BIOS Setup                          |      |

|           | Main Menu                           | 4-1  |

|           | Standard CMOS Setup                 | 4-2  |

|           | Advanced BIOS Features              | 4-3  |

|           | Advanced Chipset Features           | 4-6  |

|           | Integrated Peripherals              |      |

|           | Power Management Setup              |      |

|           | PNP/PCI Configuration               |      |

|           | <del>-</del>                        |      |

|           | PC Health Status                                    | . 4-21   |

|-----------|-----------------------------------------------------|----------|

|           | Power BIOS Features                                 | . 4-22   |

|           | Defaults Menu                                       | . 4-25   |

|           | Supervisor/User Password Setting                    | . 4-26   |

|           | Exit Selecting                                      | . 4-27   |

| Section 5 | S-ATA RAID Configuration                            |          |

|           | Introduction                                        | . 5-1    |

|           | VIA S-ATA RAID Features                             | . 5-3    |

|           | Silicon Image SiI3114 SATA RAID Features (Optional) | 5-4      |

|           | Enable RAID Function                                | . 5-5    |

| Section 6 | Driver Installation                                 |          |

|           | Easy Driver Installation                            | . 6-1    |

|           | Realtek Sound Manager Quick Guide                   | . 6-2    |

| Appendix  | Appendix A                                          |          |

|           | Update Your System BIOS                             | . A- 1   |

|           | Appendix B                                          |          |

|           | VIA RAID BIOS Utility                               | . B- 1   |

|           | Silicon Image SiI3114 RAID BIOS Utility (Optional)  | . B- 7   |

|           | Appendix C                                          |          |

|           | POST Codes                                          | $C_{-1}$ |

## Section 1 INTRODUCTION

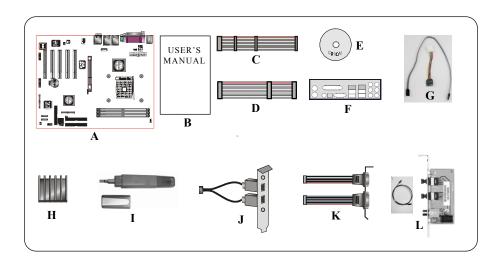

## **1-1 Package Contents**

#### **Contents**

- A. Mainboard

- B. User's manual

- C. Floppy drive cable

- D. HDD drive cable

- E. CD (drivers and utilities)

- F. I/O Shield

- G. S-ATA data and power cable

## Powerpack items (Optional)

- H. Mini heatsink

- I. Tool Pen

- J. Extra USB2.0 port cable

## Optional Items

- K. Game & COM bracket cable

- L. S/PDIF Module

If you need the optional item, please contact your dealer for assistance.

### 1-2 Mainboard Features

#### **Brief Introduction**

#### **★ Athlon™ 64 Processor**

The AMD Athlon<sup>™</sup> 64 processor family is designed to support performance desktop. It provides a high performance HyperTransport<sup>™</sup> link to I/O, as well as a single 64-bit high-performance DDR memory controller.

For more information about all the new features Athlon<sup>TM</sup> 64 Processor deliver, check out the AMD website at http://www.amd.com

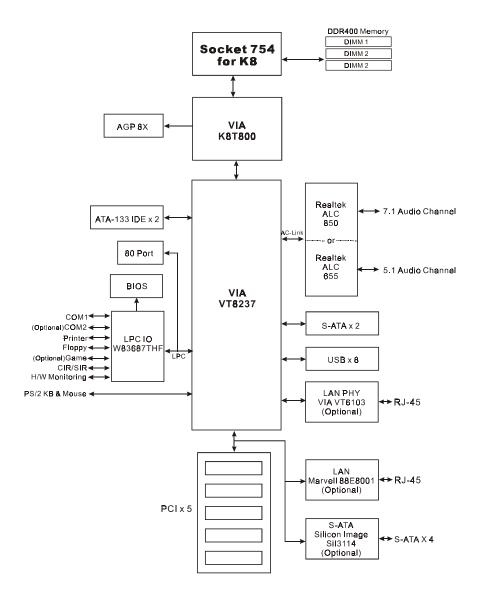

#### ★ Chipset

The board is designed with VIA chipset, K8T800 as North Bridge and VT8237 as South Bridge, providing a feature rich and scalable platform. The K8T800 North Bridge is designed with an ultra fast HyperTransport link to the Athlon<sup>TM</sup> 64 and comes equipped with AGP 8X features for VGA card expansion.

The K8T800 North Bridge connects to the VT8237 South Bridge through the fast Ultra V-Link connection at 1.06GB/s. With support for two Serial ATA channels at 150MB/s bandwidth, integrated RAID (0, 1 & JBOD) capability as well as up to eight USB 2.0 ports, the VT8237 offers the highest possible peripheral performance for professional users. Additional features include a VIA MAC for 10/100Mbps Fast Ethernet, integrated PCI support.

## ★ Accelerated Graphics Port (AGP)

The AGP slot is compliant with the new AGP 3.0 specification. This new specification enhances the functionality of the original AGP specification by allowing 8X data transfers (8 data samples per clock) resulting in maximum bandwidth of 2.1GB/s. Only 1.5V AGP cards are supported.

#### ★ Ultra ATA100/133

The mainboard provides an Ultra ATA100/133 Bus Master IDE controller. This controller supports Ultra ATA100/133 protocols which are ideal to support demanding applications such as real-time video, multimedia, and a high performance operating system. A new IDE cable is required for Ultra ATA100/133.

#### \* Hardware Monitoring

Hardware monitoring enables you to monitor various aspects of the system operation and status. The features include CPU temperature, voltage and fan speed in RPMs.

#### ★ 10/100 LAN (Optional)

This mainboard is mounted with a ethernet LAN PHY. It allows the mainboard to connect to a local area network by means of a network hub.

#### ★ GbE LAN (Optional)

This mainboard is optionally mounted with a Gigabit ethernet LAN chipset. The new Gigabit Ethernet LAN allows data transmission at 1,000 megabits per second (Mbps), which runs 10 times faster than conventional 10/100BASE-T Ethernet LANs

#### **★ Serial ATA**

Support Serial ATA, an evolutionary replacement for Parallel ATA IDE storage interface. Increases the peak data transfer speed up to 150MB/sec and allows future enhancements to the computing platform.

## ★ More S-ATA (Optional)

Extra Silicon Image SiI3114 S-ATA controller onboard for 4 additional S-ATA ports with 150MB/sec supporting RAID 0, 1, 10, 5.

#### **★ USB2.0**

A popular USB standard for plugging in peripherals with up to 480Mbps transfer speed while maintaining backward compatibility with older USB1.1 device.

#### \* Audio

Delivers multi-channel audio to bring you the latest in audio realism from DVD movies and games. Perfect for your home theatre system.

#### **Special Features**

### ♠ Cool 'n'Quiet Technology

AMD Cool'n'Quiet™ Technology enables the processor to operate at a lower speed to reduce system noise and heat dissipation.

#### **№ 80 Port**

An onboard LED-display trouble-shooting device, facilitating user to detect boot-up problems.

#### **♦ QuickSPDIF**

On board SPDIF-out connector for quick connection to multi-channel speakers. Not only removes cable cluttering but also delivers loss-free digital audio to let you enjoy DVD movies and games with crystal clear sound.

#### Magic Health

Reports your system hardware status for every boot-up to help detect faults early. Monitor hardware status including CPU temperature, CPU/Memory/AGP voltage, fan RPM speed for chassis fan, CPU fan & Power supply fan.

####

Simply press "ESC" to select your bootable device. No more hassle to search the BIOS menu, change and re-start.

#### ♠ PowerBIOS

Supporting a full range of overclocking setting via BIOS. Various adjustable feature include clock and voltage tweaking for FSB/AGP/Memory.

## 1-3 System Block Diagram

## Introduction

| 3 |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

## Section 2 SPECIFICATION

## **Mainboard Specification**

#### Processor

Supports 754-pin Socket for AMD Athlon 64 processors with 1.6GTs Hyper Transport FSB up to 3700+

## Chipset

◆ VIA K8T800 AGPset: VIA K8T800 + VT8237

## Main Memory

- Three 184-pin DDR DIMM sockets for 64-bit, Unbuffered, Single/Doubleside and DDR-266/333/400 DIMMs

- Supports up to 3GB memory size

### BIOS

- Flash EEPROM with Award BIOS

- ACPI v2.0 compliant

- S3 (Suspend to DRAM) sleep-state support

- SMBIOS (System Management BIOS) v2.2 compliant

- Supports Power failure recovery

- Able to wake the computer from specific states by LAN, Power switch, PME#, RTC alarm, USB, PS2 K/B, PS2 Mouse, Modem Ring-in COM#1...

## Onboard PCI Devices

◆ LAN--> Embedded 10/100Mbps Fast Ethernet controller with onboard VIA 6103 PHY (Optional)

Integrates 1Gbps Ethernet controller with onboard Marvell 88E8001 LAN Chipset (Optional)

• S-ATA --> Integrated Serial ATA controller from Silicon Image SiI3114 (Optional) for 4 ports solution with RAID 0, 1,10, 5 and support up to 150MB/sec transfer rate

For more detailed information about SiI3114, refer to user's manual in the bundled CD.

## Legacy IO Controller

- Winbond W83687THF LPC IO controller with floppy, printer, game (optional), serial and SIR interface

- Supports Hardware Monitoring function

- Intelligent CPU fan speed control to lower system noise

#### Audio

Six channel audio with analog and digital output using Realtek ALC655 AC'97 CODEC, or

Eight channel audio with analog and digital output using Realtek ALC850 AC'97 CODEC (for high-end model only)

- AC'97 v2.3 compliant

- Supports CD-In, Aux-In and S/PDIF-in/out interface

- Supports Line-out and Mic-In for front panel

- Supports automatic "jack-sensing"

- Rear panel audio jacks configuration:

| Phone Jack Color | 2 channel | 6 channel        | 8 channel        |

|------------------|-----------|------------------|------------------|

| Light Blue       | Line-in   | Rear stereo-out  | Line-in          |

| Lime             | Line-out  | Front stereo-out | Front stereo-out |

| Pink             | Mic-in    | Center&Subwoofer | Mic-in           |

| Gray             |           |                  | Side stereo-out  |

| Black            |           |                  | Rear stereo-out  |

| Orange           |           |                  | Center&Subwoofer |

|                  |           |                  | (for high-end    |

(for high-end model only)

## Peripheral Interfaces

#### At Rear Panel

- PS/2 keyboard and mouse ports

- One Parallel (printer) port

- One S/PDIF-Out Coaxial jack

- One S/PDIF-Out Optical (Optional)

- One Serial port

- One RJ45 LAN connector (Dual LAN optional for high-end level only)

- Four USB2.0 ports

- Three Audio jacks, (or Six Audio jacks for high-end model only)

#### Onboard connector and pin-header

- One floppy drive connector

- Two ATA-133 IDE connectors

- Four extra USB2.0 ports

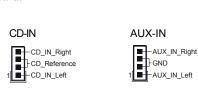

- One CD-IN and One AUX-IN connector

- One S/PDIF in/out connector

- One IR connector

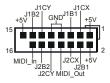

- One Game port connector (Optional)

- One COM2 connector (Optional)

- Six S-ATA connectors (4 optional from Silicon Image SiI3114 chip)

- Three Fan connectors

## Front Panel Controller

- Supports Reset & Soft-Off switches

- ◆ Supports HDD & Power LEDs

- Supports PC speaker

- Supports Front Panel Audio connector

## Expansion Slots

- ◆ One AGP slot supporting 1.5v 4X/8X AGP card

- AGP v3.0 compliant

- Five PCI slots with Bus Master support

- PCI v2.2 compliant

## Other Features

◆ Magic Health – a H/W monitoring software utility, for voltages, temperatures and fan-speeds sensing

## **Specification**

- ◆ EZ Boot Simply press "ESC" to select your bootable device. No more hassle to search the BIOS menu, change and re-start.

- KBPO Keyboard power on, turn on the computer from keyboard

- Supports "Cool'n' Quiet" power saving technology

- Excellent Overclocking capabilities through

- subtle voltage tuning for CPU, Memory, AGP

- subtle frequency tuning on FSB with 1MHz

- Supports complete Asynchronous FSB/Memory and Asynchronous FSB/AGP, PCI scheme for overclocking

- P80P for system debugging

## Form Factor

• 305mm x 245 mm ATX size

## Section 3 INSTALLATION

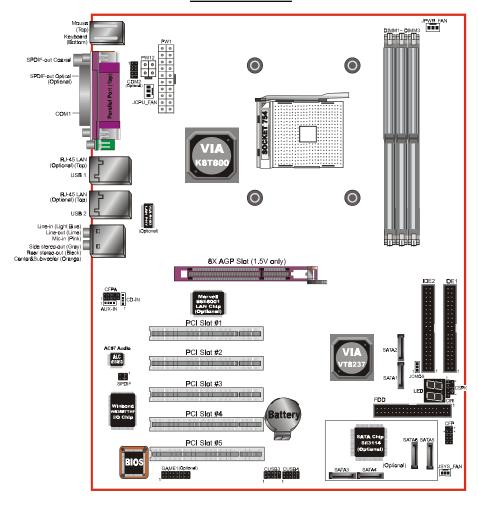

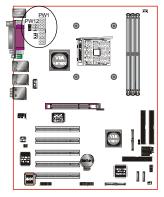

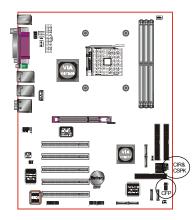

## Mainboard Layout

Note: Depending on the model you purchased, some components are optional and may not be available.

## **Easy Installation Procedure**

The following must be completed before powering on your new system:

- 3-1. CPU Installation

- 3-2. Jumper Settings

- 3-3. System Memory

- 3-4. Expansion Slots

- 3-5. Device Connectors

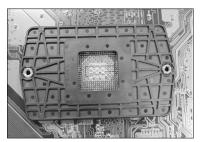

## 3-1 CPU Installation

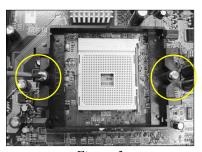

<Figure 1>

## Step 1

Place the back plate into the two holes around the CPU area behind the mainboard.

<Figure 3>

## Step 3

Screw in the two pan head screws.

<Figure 2>

## Step 2

Place the retention mechanism on the mainboard as shown.

<*Figure 4>*

## Step 4

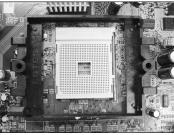

Open the socket by raising the actuation lever.

<Figure 5>

## Step 5

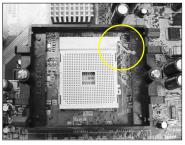

Align pin 1 on the CPU with pin 1 on the CPU socket and gently insert the CPU. The CPU is keyed to prevent incorrect insertion. Do not force the processor into the socket. If it does not go in easily, check for mis-orientation and reinsert the CPU.

Make sure the processor is fully inserted into the socket.

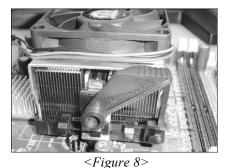

<Figure 7>

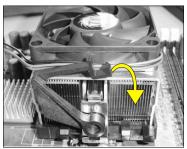

## Step 7

Insert the heatsink as shown above. Press the clips in the direction of the arrows shown in Figure 7 to secure the assembly to the CPU socket.

<Figure 6>

## Step 6

Close the socket by lowering and locking the actuation lever.

Apply thermal compound to the top of the CPU.

#### Note:

Thermal compound and qualified heatsink recommended by AMD are a must to avoid CPU overheat damage.

Step 9

Plug the CPU fan power into the mainboard's CPU fan connector.

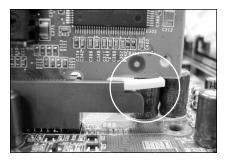

## **3-2 Jumper Settings**

JCMOS: Clear CMOS data Jumper

If the CMOS data becomes corrupted or

you forgot the supervisor or user

password, clear the CMOS data to

reconfigure the system back to the

default values stored in the ROM BIOS.

Settings:

1-2: Normal (Default)

2-3: Clear CMOS

To CMOS Clear data, please follow the steps below.

- 1. Turn off the system.

- 2. Change the jumper from "1-2" to "2-3" position for a few seconds.

- 3. Replace the jumper back to the "1-2" position.

- 4. Turn on the system and hold down the <Del> key to enter BIOS setup.

## 3-3 System Memory Configuration

## **Memory Layout**

The mainboard accommodates three PC2100/PC2700/PC3200 184-pin DIMMs (Dual In-line Memory Modules):

- Supports up to 3.0GB of 266/333/400MHz DDR SDRAM.

- Supports unbuffered DIMM configurations defined in JEDEC DDR DIMM specification.

| DDR DIMM 1 | <figure 9=""></figure> |

|------------|------------------------|

| DDR DIMM 2 |                        |

| DDR DIMM 3 |                        |

Follow the recommendation below for maximum memory performance:

| Clot No | DDR400  |         |    |    |        |       |       |       |

|---------|---------|---------|----|----|--------|-------|-------|-------|

| Slot No | 3 DIMMs | 2 DIMMs |    |    | 1 DIMM |       |       |       |

| DIMM#1  | SS      | SS      | SS | DS | DS     | DS/SS |       |       |

| DIMM#2  | SS      | DS      |    | SS |        |       | DS/SS |       |

| DIMM#3  | SS      |         | DS |    | SS     |       |       | DS/SS |

<sup>\*</sup> DS - Double-sided DIMM, \* SS - Single-sided DIMM

#### For 1 DIMM:

- Mount on any slot to obtain DDR400 speed.

#### For 2 DIMM:

- Mount DS DIMM on Slot 1 and the remaining DIMM on Slot 2 or 3 with SS DIMM.

- Mount SS DIMM on Slot 1 and the remaining DIMM on Slot 2 or 3 with DS DIMM.

#### For 3 DIMM:

- Use SS DIMM on all 3 three slots for DDR400 speed.

#### NOTES:

• Using non-compliant memory with higher bus speeds (overclocking) may severely compromise the integrity of the system.

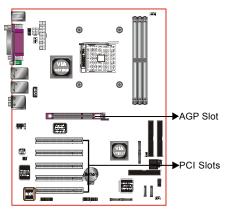

## **3-4 Expansion Slots**

#### **AGP Slot**

The mainboard is equipped with an AGP slot. Make sure you install a card that supports the 1.5V specification.

#### **PCI Slots**

The mainboard is equipped with 5 PCI slots.

## **AGP Card Installation Caution**

When installing the AGP card make sure the AGP card edge connector is inserted fully into the slot and the slot clicker is locked.

## **3-5 Device Connectors**

The I/O back panel for this mainboard is shown below. When installing the mainboard into the computer case, use the bundled I/O shield to protect this back panel.

Figure 10 - I/O Ports

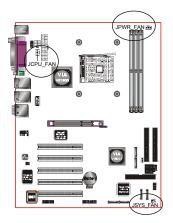

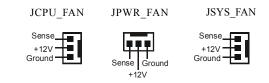

## JCPU FAN/JPWR FAN/JSYS FAN:

CPU/Power/Chassis Fan Power Connectors

JCPU FAN: The CPU must be kept cool by using a

heatsink with fan assembly.

JPWR\_FAN: If you are installing an additional fan

in the unit, connect to this fan

connector.

JSYS\_FAN: The chassis fan will provide adequate

airflow throughout the chassis to prevent overheating the CPU.

This mainboard is equipped with intelligent fan speed control. Refer to the PC Health Status submenu of the BIOS.

#### Installation

**FDD:** Floppy Controller Connector This connects to the floppy disk drive.

**IDE1/IDE2:** Ultra DMA-100/133 Primary/Secondary IDE Connector

This mainboard is equipped with 2 IDE connectors to support up to 4 ATA-100/133 IDE drives. It supports PIO and DMA mode operations for maximum data transfer rate of 133MB/sec per channel.

When using two IDE drives on the same connector, one must be set to Master mode and the other to Slave mode. Refer to your disk drive user's manual for details.

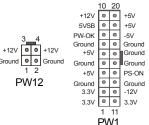

**PW1:** 20-pin ATX Power Connector

**PW12:** 4-pin ATX12V Power Connector

The mainboard is equipped with a standard 20-pin ATX main power connector and a 4-pin +12V power connector for connecting an ATX12V power supply. The plugs of the power cables are designed to fit in only one orientation. Insert the plugs into the connectors until they fit in place.

Caution: The PW1 and PW12 Power Connector must be used simultaneously.

The board requires a minimum of 300 Watt power supply to operate. Your system configuration (amount of memory, add-in cards, peripherals, etc.) may exceed this minimum power requirement. To ensure that adequate power, use a 350 Watt or greater power supply.

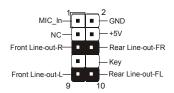

#### **CFPA**: Front Panel Audio Connector

When the jumpers are removed this connector can be used for front panel audio. The front panel phone jack should have "normal close" switch. Without phone plug inserted, the rear panel audio is enabled. With phone plug inserted, the rear panel audio will be disabled.

#### Settinas

Pins (5-6) & (9-10) Short (default): Only the onboard rear panel audio jack can be used.

Pins (5-6) & (9-10) Open: Only front panel audio jack can be used.

In 2-Channel audio mode, Mic-In is shared for both front panel and rear panel. In 6-Channel audio mode, the Mic-In is dedicated for front panel use, and rear panel Mic-In function will switch to Center and Subwoofer support.

## CD-IN/AUX-IN: CD Audio\_IN Connector

The CD-IN and AUX-IN connectors are used to receive audio form a CD-ROM drive, TV tuner or MPEG card.

#### Installation

**SPDIF1:** Sony/Philips Digital InterFace connector This connector links digital audio between the mainboard and your audio devices, such as CD player, sampler or DAT recorder. It allows the digital transmission of audio data in S/PDIF format.

**GAME1:** Game/MIDI connector (Optional)

This port works well with any application that is compatible with the standard PC joystick.

**COM2:** Serial Port Connector (Optional)

The serial port can be used with modems, serial printers, remote display terminals, and other serial device.

#### SATA1 / SATA2: Two Serial ATA Connectors

## SATA3 / SATA4 / SATA5 / SATA6 (Optional):

Four Serial ATA Connectors from Silicon Image SiI3114 chip.

These connectors enable you to connect Serial ATA devices that conform to the Serial ATA specification.

#### **LED1:** 80 Port Debug LED

Provides two-digit POST code to show why the system fail to boot. Allows quick and easy optimization.

80 Port Debug 7-segment LED display (Refer to Appendix C for POST codes)

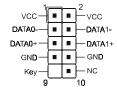

## CUSB3/CUSB4: Four USB 2.0 ports

This mainboard includes 2 additional USB2.0 ports, identified by two 10-pin connector.

If you wish to use the additional USB ports, install the card-edge bracket to the system chassis then insert its cables to this 10-pin connector.

#### **CAUTION!**

Please make sure the USB cable has the same pin assignment. A different pin assignment may cause damage to the system. If you need the USB cable, please contact our retailer.

#### Installation

#### **CFP**

#### CIR

#### **CSPK**

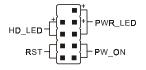

**CFP:** Front Panel Connector

#### • HD LED

This LED will light up whenever the hard drive is being accessed.

## • PWR LED

This connects to the power button of the system chassis

#### • RST

This switch allows you to reboot without having to power off the system thus prolonging the life of the power supply or system.

## • PW ON

This is connected to the power button on the case. To use the Soft-Off by PWR-BTTN feature, refer to the Power Management Setup in the BIOS setup section of this manual.

#### **CIR:** IR connector

Connect the IrDA cable (if available) to this IR connector.

## **CSPK:** Speaker

Connect to the system's speaker for beeping

## 3-6 Power-On/Off (Remote)

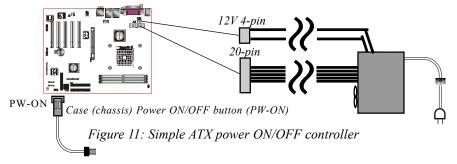

This board has a 20-pin ATX and a 4-pin ATX12V power supply connector to support power supplies with **Remote On/Off** feature. The 4-pin ATX12V connector must be plugged in for the system to operate safely. The chassis power button should be connected to the mainboard front panel PW ON header (Figure 11).

You can turn off the system in two ways: by pressing the front panel power On/Off button or using the "Soft Off" function that can be controlled by an operating system such as Windows®XP/ME/2000/98.

Note: For maintaining the DDR SDRAM power during STR (ACPI S3) function, it is strongly recommended to use power supplies that have a +5VSB current of (>=) 2A. Please check the 5VSB's specification printed on the power supply's outer case.

Note: The board requires a minimum of 300 Watt power supply to operate. Your system configuration (amount of memory, add-in cards, peripherals, etc.) may exceed this minimum power requirement. To ensure that adequate power, use a 350 Watt (or higher) power supply.

## 3-7 External Modem Ring-in Power ON and Keyboard Power ON Functions (KBPO)

## **Modem-Ring Power ON Function**

The mainboard supports External Modem Ring-in Power ON function. Once you connect an external modem to COM port, you can turn on the system through remote and host dial-up control.

## **Keyboard Power ON Function**

The mainboard features a keyboard power on function to turn on the power supply using a keypress. Refer to the Power Management Setup in the BIOS setup section for details. To enable this feature, the BIOS default setting is Keyboard Hot Key (<Ctrl> + <F1>). To power off the system, use the Soft-OFF function under Windows XP/ME/2000/98. (refer to Windows online help).

## 3-8 ACPI S3 (Suspend To RAM) Function

This mainboard supports the STR (Suspend To RAM) power management scheme by maintaining the appropriate power states in the DDR SDRAM interface signals. The power source to the DDR SDRAM is kept active during STR (ACPI S3). Advanced Configuration Power Interface (ACPI) provides many Energy Saving Features for operating systems that support Instant ON and QuickStart<sup>TM</sup> function.

- 1. To enable STR functionality to save system power:

- a. Install ACPI certified add-on cards (such as AGP, LAN, and modem cards).

- b. In BIOS, under Power Management Setup (refer to Section 4), select "ACPI Suspend Type: S3(STR)". If you have a USB mouse or keyboard, set "USB Wake-Up from S3" to "Enabled".

- c. When in Windows, open the Control Panel Power Management application, and click the Advanced tab. In the Power buttons section, select "Stand By" from the drop-down lists.

- 2. To activate the STR function:

- a. Click the START button and choose Shut Down.

- b. In the Shut Down Windows dialog box, select the Stand By option to enter STR mode.

- The following are the differences between STR power saving mode and Suspend (Power On Suspend) mode:

- a. STR is the most advanced Power Management mode.

- STR cuts all the power supplied to peripherals except to memory max. power saving.

- STR saves and keeps all on-screen data including any executed applications to DDR SDRAM.

- d. In STR mode, you must push the power button (connected to the onboard PW-On of CFP pin), click your USB mouse buttons, or press your USB keyboard keys to wake up your system to the last display.

## **3-9 CPU Overheating Protection**

This mainboard is equipped with CPU Overheating Protection. It will automatically remove power to shutdown the system when CPU temperature reaches approximately 110°C. This is to prevent long term damage to the CPU from overheating. This protection is designed through hardware and no BIOS setup is required.

To power on your system again,

- **Step 1**: Unplug the ATX power cord (or turn off the ATX power supply switch)

- **Step 2**: Wait a few minutes for the CPU to cool.

- Step 3: Check that the CPU heatsink and cooling fan assembly is properly installed. Be careful when touching the heatsink as it may be hot.

- **Step 4**: Plug back the ATX power cord (or turn on the ATX power supply switch) and power -on the system.

If the beeping sound persists, repeat Step 1 to remove the power source.

## Installation

| B |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

## Section 4 BIOS SETUP

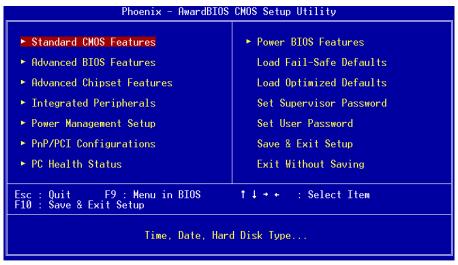

#### **Main Menu**

The ROM BIOS contains a built-in Setup program which allows user to modify the basic system configuration and hardware parameters. The modified data is stored in a battery-backed CMOS, so that data will be retained even when the power is turned off. In general, the information saved in the CMOS RAM will stay unchanged unless there is a configuration change in the system, such as hard drive replacement or a device is added.

It is possible for the CMOS battery to fail causing CMOS data loss. If this happens you will need install a new CMOS battery and reconfigure your BIOS settings.

## To enter the Setup Program:

Power on the computer and press the <Del> key during the POST (Power On Self Test). The BIOS CMOS SETUP UTILITY opens.

Figure 1: CMOS Setup Utility

The main menu displays all the major selection items. Select the item you need to reconfigure. The selection is made by moving the cursor (press any direction (arrow key ) to the item and pressing the 'Enter' key. An on-line help message is displayed at the bottom of the screen as the cursor is moved to various items which provides a better understanding of each function. When a selection is made, the menu of the selected item will appear so that the user can modify associated configuration parameters.

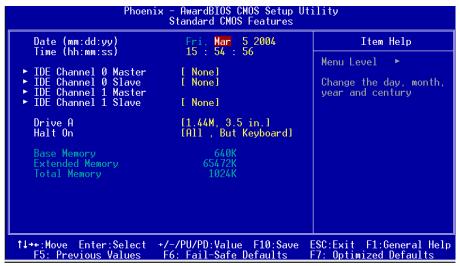

## 4-1 Standard CMOS Setup

Choose "STANDARD CMOS FEATURES" in the CMOS SETUP UTILITY Menu (Figure 2). Standard CMOS Features Setup allows the user to configure system settings such as the current date and time, type of hard disk drive installed, floppy drive type, and display type. Memory size is auto-detected by the BIOS and displayed for your reference. When a field is highlighted (use direction keys to move the cursor and the <Enter> key to select), the entries in the field can be changed by pressing the <PgDn> or the <PgUp> key.

Figure 2: Standard CMOS Setup

**Notes:** • If the hard disk Primary Master/Slave and Secondary Master/Slave are set to Auto, the hard disk size and model will be auto-detected.

The "Halt On." field is used to determine when the BIOS will halt the system if an

error occurs.

#### **4-2 Advanced BIOS Features**

Selecting the "ADVANCED BIOS FEATURES" option in the CMOS SETUP UTILITY menu allows users to change system related parameters in the displayed menu. This menu shows all of the manufacturer's default values for the board.

Pressing the [F1] key displays a help message for the selected item.

Figure 3: BIOS Features Setup

### **Hard Disk Boot Priority**

This item allows you to select the hard disk boot priority.

#### Virus Warning

During and after system boot up, any attempt to write to the boot sector or partition table of the hard disk drive halts the system and an error message appears.

You should then run an anti-virus program to locate the virus. Keep in mind that this feature protects only the boot sector, not the entire hard drive.

#### **BIOS**

**Enabled**: Activates automatically when the system boots up causing a warning

message to appear when anything attempts to access the boot sector.

**Disabled**: No warning message appears when anything attempts to access the boot

sector.

**Note:** Many disk diagnostic programs that access the boot sector table can

trigger the virus warning message. If you plan to run such a program, we

recommend that you first disable the virus warning.

#### **CPU Internal Cache**

This controls the status of the processor's internal cache area. The default is Enabled.

Options: Enabled, Disabled.

#### **External Cache**

This controls the status of the external (L2) cache area. The default is Enabled.

Options: Enabled, Disabled.

#### First /Second/Third/Other Boot Device

The BIOS attempts to load the operating system from the devices in the sequence selected in these items.

Options: Floppy, LS120, Hard Disk, CDROM, ZIP100, USB-FDD, USB-CDROM, Legacy LAN, Disabled.

#### **Boot Other Device**

When enabled, the system searches all other possible locations for an operating system if it fails to find one in the devices specified under the first, second, and third boot devices. The default is Enabled.

Options: Enabled, Disabled.

## **Boot Up Floppy Seek**

If this item is enabled, it checks the size of the floppy disk drives at start-up time.

You don't need to enable this item unless you have a legacy diskette drive with 360K capacity.

Options: Enabled, Disabled.

#### **Boot Up NumLock Status**

This controls the state of the NumLock key when the system boots. The default is On.

On: The keypad acts as a 10-key pad.

Off: The keypad acts like cursor keys.

#### Page 4-4

## **Security Option**

This category allows you to limit access to the System and Setup, or just to Setup.

**System**: The system will not boot and the access to Setup will be denied if the

correct password is not entered at the prompt.

**Setup**: The system will boot; but the access to Setup will be denied if the

incorrect password is not entered at the prompt.

#### **APIC Mode**

This item allows you to enable APIC (Advanced Programmable Interrupt Controller) functionality. APIC is a chip that provides symmetric multiprocessing (SMP) for its Pentium systems.

Options: Enabled, Disabled.

#### **MPS Version Control For OS**

Specifies the Multiprocessor Specification (MPS). Version 1.4 supports multiple PCI bus configurations by incorporating extended bus definitions. Enable this for Windows NT or Linux. For older operating systems, select Version 1.1.

Options: 1.1, 1.4.

#### Video BIOS Shadow

This option allows video BIOS to be copied into RAM. Video Shadowing will increase the video performance of your system.

Options: Enabled, Disabled.

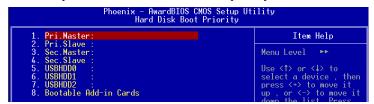

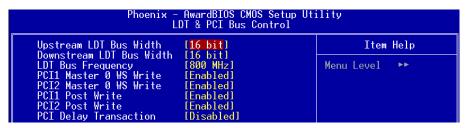

## 4-3 Advanced Chipset Features

Choose the "ADVANCED CHIPSET FEATURES" option in the CMOS SETUP UTILITY menu to display following menu.

Figure 4: Chipset Features Setup

#### **VLink Data Rate**

This item allows you to select VLink Data Rate.

Options: 4X, 8X.

## **Init Display First**

If two video cards are used (1 AGP and 1 PCI) this specifies which one will be the primary display adapter. The default is PCI Slot.

Options: PCI Slot, AGP.

## System BIOS Cacheable

This item allows the system to be cached in memory for faster execution. The default is Enabled.

Options: Disabled, Enabled.

## **▶** DRAM Configuration

Scroll to DRAM Configuration and press <Enter>. The following screen appears:

| Phoenix – AwardBIOS CMOS Setup Utility<br>DRAM Configuration                                           |                                      |  |  |

|--------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| Current FSB Frequency<br>Current DRAM Frequency                                                        | Item Help                            |  |  |

| DDR Clock Setting by [Auto]                                                                            | Menu Level ►►                        |  |  |

| x Max Memclock (Mhz) 100<br>1T/2T Memory Timing [Auto]<br>DDR Timing Setting by [Auto]                 | DDR Timing Setting by<br>SPD or TTEM |  |  |

| x CAS# latency (Tcl) Auto<br>x Row cycle time (tRC) Auto                                               | 0.0 0. 1.2                           |  |  |

| x Row refresh cyc time(tRFC) Auto<br>x RAS# to CAS# delay (Trcd) Auto                                  |                                      |  |  |

| x Row to Row delay (tRRD) Auto<br>x Min RAS# active time(Tras) Auto                                    |                                      |  |  |

| x Row precharge Time (Trp) Auto<br>x Write recovery time (tWR) Auto                                    |                                      |  |  |

| x Write to Read delay (tWTR) Auto<br>x Read to Write delay (tRWT) Auto<br>x Refresh period (tREF) Auto |                                      |  |  |

#### **Current FSB Frequency**

Display the current CPU front side bus frequency information.

## **Current DRAM Frequency**

Display the current DRAM frequency information.

## **DDR Clock Selecting by**

This option sets DRAM clock. Select "Auto" to follow SPD (Serial Presence Detect) information on DRAM module or set to "Manual" to set by next item selection.

Options: Manual, Auto.

## Max Memclock (Mhz)

This item sets the memory clock. By placing an artificial memory clock limit on the system, memory is prevented from running faster than this frequency. Example, "200" will set to DDR400 speed.

Options: 100, 133, 166, 200.

## 1T/2T Memory Timing

For setting DRAM Timing.

Options: Auto, 1T, 2T.

## **DDR Timing Selecting by**

This option sets DRAM access timing parameters. Select "Auto" to follow SPD (Serial Presence Detect) information on DRAM module or set to "Manual" to set by next item selection.

Options: Manual, Auto.

#### **CAS# Latency**

Enables you to select the CAS latency time. The value is set at the factory depending on the DRAM installed. Do not change the values in this field unless you change specifications of the installed DRAM.

Options: Auto, CL=2.0, CL=2.5, CL=3.

#### Row cycle time (tRC)

This filed specifies the Row Cycle Time. RAS# active to RAS# active or auto refresh of the same bank.

Options: Auto, 7 Bus Clocks ~ 22 Bus Clocks in 1 Bus clock increments.

#### Row refresh cyc time (tRFC)

This filed specifies the Row Refresh Cycle Time. Auto-refresh active to RAS# or RAS# to auto refresh

Options: Auto, 9 Bus Clocks ~ 24 Bus Clocks in 1 Bus clock increments.

## RAS# to CAS# delay (tRCD)

This filed specifies the RAS# to CAS# delay to read/write command to the same bank. Options: Auto, 2 Bus Clocks ~ 7 Bus Clocks in 1 Bus clock increments.

## Row to Row delay (tRRD)

This filed specifies the Row to Row delay of different banks.

Options: Auto, 2 Bus Clocks ~ 7 Bus Clocks in 1 Bus clock increments.

## Min RAS# active time (tRAS)

This filed specifies the minimum RAS# active time.

Options: Auto, 5 Bus Clocks ~ 15 Bus Clocks in 1 Bus clock increments.

## Row precharge Time (tRP)

This filed specifies the Row Precharge Time. Precharge to active or Auto-refresh of the same bank.

Options: Auto, 2 Bus Clocks ~ 6 Bus Clocks in 1 Bus clock increments.

## Write recovery time (tWR)

This bits specifies the Write Recovery Time. Called Trd1 by Samsung, measures when the last write datum is safely registered by the DRAM. It measures from the last data to precharge.

Options: Auto, 2 Bus Clocks, 3 Bus Clocks.

## Write to Read delay (tWTR)

This bits specifies the Write to Read delay. Samsung Calls this Tcd1r (last data in to read command). It is measured from the rising edge following the last non-masked data strobe to the rising edge of the next Read Command. (Jedec spec this as exactly one clock).

Options: Auto, 1 Bus Clock.

#### Read to Write delay (tRWT)

This filed specifies the Read to write delay. This is not a DRAM specified timing parameter but must be considered due to routing latencies on the clock forwarded bus. It is counted from first address but slot which was not associated with part of the read burst.

Options: Auto, 1 Bus Clock ~ 6 Bus Clocks in 1 Bus clock increments.

#### Refresh period (tREF)

This filed specifies the number of clock cycles between refresh.

Options: Auto, 1 x 1552 cycles  $\sim$  4 x 4672 cycles.

## ▶ AGP & P2P Bridge Control

Scroll to AGP & P2P Bridge Control and press <Enter>. The following screen appears:

| Phoenix - AwardBIOS CMOS Setup Utility<br>AGP & P2P Bridge Control |                          |               |  |

|--------------------------------------------------------------------|--------------------------|---------------|--|

| AGP Aperture Size                                                  | [128M]                   | Item Help     |  |

| AGP Mode<br>AGP Driving Control                                    | [4X]<br>[Auto]           | Menu Level ►► |  |

| x AGP Driving Value<br>AGP Fast Write                              | [Disabled]               |               |  |

| AGP Master 1 WS Write<br>AGP Master 1 WS Read                      | [Disabled]<br>[Disabled] |               |  |

## AGP Aperture Size (MB)

This item defines the size of the aperture if you use an AGP graphics adapter. It refers to a section of the PCI memory address range used for graphics memory. Options: 32M, 64M, 128M, 256M.

#### **AGP Mode**

Chipset AGP Mode support.

Options: 1X, 2X, 4X, 8X.

## **AGP Driving Control**

This item allows you to adjust the AGP driving force. Choose "Manual" to key in a AGP Driving Value in the next selection. This field is recommended to set in "Auto" to avoid any error to your system.

Options: Auto, Manual.

#### **AGP Fast Write**

Selecting Enabled allows to use Fast Write Protocol for 4X AGP card.

Options: Enabled, Disabled.

#### **AGP Master 1 WS Write**

When Enabled, Writes to the AGP (Accelerated Graphics Port) are executed with one wait states.

Options: Enabled, Disabled.

#### AGP Master 1 WS Read

When Enabled, Reads to the AGP (Accelerated Graphics Port) are executed with one wait states.

Options: Enabled, Disabled.

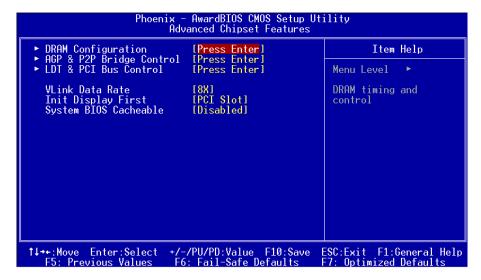

#### ▶ LDT & PCI Bus Control

Scroll to LDT & PCI Bus Control and press <Enter>. The following screen appears:

#### **Upstream LDT Bus Width**

Options: 8 bit, 16 bit.

#### **Downstream LDT Bus Width**

Options: 8 bit, 16 bit.

## **LDT Bus Frequency**

This item sets CPU Hyper Transport front size bus.

Options: Auto, 800MHz, 600MHz, 400MHz, 200MHz.

#### PCI1/2 Master 0 WS Write

When Enabled, Writes to the PCI bus are commanded with zero wait states.

Options: Enabled, Disabled.

#### PCI1/2 Post Write

Enables CPU to PCI bus POST write.

Options: Enabled, Disabled.

## **PCI Delay Transaction**

The chipset has an embedded 32-bit posted write buffer to support delay transactions cycles. Select Enabled to support compliance with PCI specification version 2.2. Options: Enabled, Disabled.

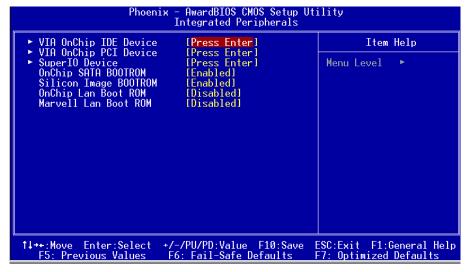

## **4-4 Integrated Peripherals**

Figure 5: Integrated Peripherals

## OnChip SATA Boot ROM / Silicon Image Boot ROM (Optional) / OnChip Lan Boot ROM / Marvell Lan Boot ROM (Optional)

Enables/disable the onboard SATA/Silicon Image/LAN Boot LAN.

Options: Enabled, Disabled.

## ▶ VIA OnChip IDE Device

Scroll to VIA Onchip IDE Device and press <Enter>. The following screen appears:

| Phoenix – AwardBIOS CMOS Setup Utility<br>VIA OnChip IDE Device                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                 |               |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

| OnChip SATA                                                                                                                                                                                                                                                                                                                                  | [Enabled]                                                                                                                                                                                                       | Item Help     |  |

| SATA Mode IDE DMA transfer access OnChip IDE Channel0 OnChip IDE Channel1 IDE Prefetch Mode Primary Master PIO Primary Slave PIO Secondary Master PIO Secondary Slave PIO Primary Slave PIO Primary Slave UDMA Primary Slave UDMA Secondary Master UDMA Secondary Master UDMA Secondary Slave UDMA Secondary Slave UDMA Secondary Slave UDMA | [RAID] [Enabled] [Enabled] [Enabled] [Enabled] [Auto] | Menu Level ►► |  |

## **Onchip SATA**

Enables the onboard SATA feature.

Options: Enabled, Disabled.

#### **SATA Mode**

This allows you to set RAID mode for Serial ATA devices. Refer to section 5 for more RAID information.

Options: RAID, IDE.

#### **IDE DMA transfer access**

Automatic data transfer between system memory and IDE device with minimum CPU intervention. This improves data throughput and frees CPU to perform other tasks. Options: Enabled, Disabled.

## OnChip IDE Channel0/1

The mainboard supports two channel of ordinary IDE interface. Select "Enabled" to activate each channel separately.

Options: Enabled, Disabled.

Note: If you do not use the onboard IDE connector, set the Onboard Primary PCI IDE and Onboard Secondary PCI IDE to "Disabled".

#### **IDE Prefetch Mode**

Selecting "Enabled" reduces latency between each drive read/write cycle, but may cause instability in IDE subsystems that cannot support such fast performance. If

you are getting disk drive errors, try setting this value to Disabled. This field does not appear when the Internal PCI/IDE field, above, is Disabled.

Options: Enabled, Disabled.

#### Primary/Secondary Master/Slave PIO

The four IDE PIO (Programmed Input/Output) fields let you set a PIO mode (0-4) for each of the four IDE devices that the onboard IDE interface supports. Modes 0 to 4 provide successively increased performance. In Auto mode, the system automatically determines the best mode for each device.

Options: Auto, Mode  $0 \sim 4$ .

#### Primary/Secondary Master/Slave UDMA

Select the mode of operation for the IDE drive. Ultra DMA-33/66/100/133 implementation is possible only if your IDE hard drive supports it and the operating environment includes a DMA driver. If your hard drive and your system software both support Ultra DMA-33/66/100/133, select Auto to enable UDMA mode by BIOS. Options: Auto, Disabled.

#### **IDE HDD Block Mode**

Block mode is also called block transfer, multiple commands, or multiple sector read/write. If your IDE hard drive supports block mode (most new drives do), select Enabled for automatic detection of the optimal number of block read/writes per sector the drive can support.

Options: Enabled, Disabled.

## ▶ VIA Onchip PCI Device

Scroll to VIA Onchip PCI Device and press <Enter>. The following screen appears:

| Phoenix - AwardBIOS CMOS Setup Utility<br>VIA OnChip PCI Device |                         |               |  |

|-----------------------------------------------------------------|-------------------------|---------------|--|

| VIA AC97 Audio                                                  | [Auto]                  | Item Help     |  |

| Game Port Address<br>Midi Port Address                          | [201]<br>[Disabled]     | Menu Level ►► |  |

| x Midi Port IRQ<br>Marvell LAN and 80 Port                      | 10<br>[Auto]            |               |  |

| VIA OnChip LAN                                                  | [Auto]                  |               |  |

| VIA-6102 MAC Address Inp<br>OnChip USB Controller               | [All Enabled]           |               |  |

| OnChip EHCI Controller<br>USB Keyboard Support                  | [Enabled]<br>[Disabled] |               |  |

| USB Mouse Support                                               | [Disabled]              |               |  |

#### VIA AC97 Audio

This item allows you to disable the chipset on-chip AC97 Audio.

Options: Auto, Disabled.

#### **Game Port Address (Optional)**

Select an address for the Game port.

Options: 201, 209, Disabled.

#### Midi Port Address (Optional)

Select an address for the Midi port.

Options: 290, 300, 330, Disabled.

#### Midi Port IRQ (Optional)

Select an interrupt for the Midi port.

Options: 5, 10

## VIA Onchip LAN and 80 Port (Optional)

Enables the onboard LAN and 80 port feature.

Options: Auto, Disabled.

## VIA-6102 MAC Address Input (Optional)

Allwos you to input MAC address.

## **Onchip USB Controller**

Enables the USB controller.

Options: Enabled, Disabled.

## **Onchip EHCI Controller**

Enables the EHCI (USB2.0) controller.

Options: Enabled, Disabled.

## **USB Keyboard Support**

Enable/disable support for USB keyboard under DOS.

Options: Enabled, Disabled.

## **USB Mouse Support**

Enable/disable support for USB mouse under DOS.

Options: Enabled, Disabled.

## ▶ Super IO Device

Scroll to Super IO Deivce and press <Enter>. The following screen appears:

| Phoenix – AwardBIOS CMOS Setup Utility<br>Onboard I/O Chip Setup |                         |               |  |

|------------------------------------------------------------------|-------------------------|---------------|--|

| Onboard FDC Controller<br>Onboard Serial Port 1                  | [Enabled]<br>[3F8/IR04] | Item Help     |  |

| Onboard Serial Port 2 UART Mode Select                           | [2F8/IRQ3]<br>[Normal]  | Menu Level ►► |  |

| Onboard Parallel Port<br>Parallel Port Mode                      | [378/IRQ7]<br>[SPP]     |               |  |

| EPP Mode Select<br>ECP Mode Use DMA                              | [EPP1.7]<br>[3]         |               |  |

#### **Onboard FDC Controller**

Select "Enabled" if you wish to use onboard floppy disk controller (FDC). If you install an external FDC or the system has no floppy drive, select "Disabled "in this field. Options: Enabled, Disabled.

#### **Onboard Serial Port 1**

Select an address and corresponding interrupt for the first serial port.

Options: 3F8/IRQ4, 2E8/IRQ3, 3E8/IRQ4, 2F8/IRQ3, Disabled, Auto.

#### **Onboard Serial Port 2 (Optional)**

Select an address and corresponding interrupt for the second serial port.

Options: 3F8/IRQ4, 2E8/IRQ3, 3E8/IRQ4, 2F8/IRQ3, Disabled, Auto.

#### **UART Mode Select**

This field configures the 2nd serial port for IR application. Select the required IR protocol or select "Normal" to disable IR mode.

Options: Normal, IrDA and ASKIR.

#### **Onboard Parallel Port**

This field allows the user to configure the LPT port.

Options: 378/IRQ7, 278/IRQ5, 3BC/IRQ7, Disabled.

#### **Parallel Port Mode**

This field allows the user to select the parallel port mode.

Options: SPP, EPP, ECP, ECP+EPP, Normal.

#### **EPP Mode Select**

This field allows the user to select the EPP mode for parallel port mode.

Options: EPP1.9, EPP1.7.

#### **ECP Mode USE DMA**

This field allows the user to select DMA1 or DMA3 for the ECP mode.

Options: DMA1, DMA3.

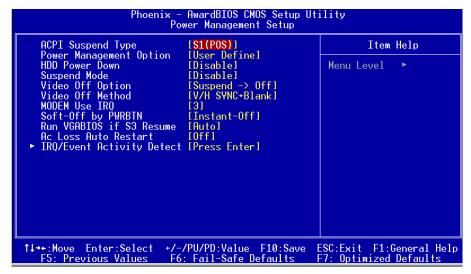

## 4-5 Power Management Setup

Choose the "Power Management setup" in the CMOS Setup Utility to display the following screen. This menu allows the user to modify the power management parameters and IRQ signals. In general, these parameters should not be changed unless it's absolutely necessary.

Figure 6: Power Management

## **ACPI Suspend Type**

This item allows you to select S1(Power-On-Suspend) or S3(Suspend-To-RAM) function.

Options: S1(POS), S3(STR), S1&S3.

## **Power Management Option**

Use this to select your Power Management selection. The default is User define.

Max.saving:Maximum power savings. Inactivity period is 1 minute in each mode.Min. saving:Minimum power savings. Inactivity period is 1 hour in each mode.User define:Allows user to define PM Timers parameters to control power saving

mode.

#### **HDD Power Down**

Powers down the hard disk drive after a preset period of system inactivity.

Options: Disabled, 1min ~ 15min.

#### **Suspend Mode**

Automatically, shuts off all devices except the CPU after a preset period of system inactivity.

Options: Disabled, 1, 2, 4, 6, 8, 10, 20, 30, 40 min and 1 hour.

#### Video Off Option

When enabled, this feature allows the VGA adapter to operate in a power saving mode.

Always On: Monitor will remain on during power saving modes.

Suspend->Off: Monitor blanked when the systems enters the suspend mode.

#### Video Off Method

This option allows you to select how the video will be disabled by the power management. The default is V/H Sync + Blank

V/H Sync + Blank: System turns off vertical and horizontal synchronization ports

and writes blanks to the video buffer.

DPMS Support: Select this option if your monitor supports the Display Power

Management Signaling (DPMS) standard of the Video Electronics Standards Association (VESA). Use the software supplied by your video subsystem to select video power management values.

Blank Screen: System only writes blanks to the video buffer.

#### MODEM Use IRQ

Select the interrupt request (IRQ) line assigned to the modem (if any) on your system. Activity of the selected IRQ always awakens the system. Default is IRQ 3. Options: N/A, 3, 4, 5, 7, 9, 10, 11

## **Soft-Off by PWRBTN**

Pressing the power button for more than 4 seconds forces the system to enter the Soft-Off state when the system has "hung." The default is Instant-off.

Options: Delay 4 Sec, Instant-Off.

#### **Run VGABIOS if S3 Resume**

This determines whether or not to enable the system to run the VGA BIOS when resuming from S3(STR) or S1&S3.

Options: Auto, Yes, No.

#### **AC Loss Auto Restart**

This item enables your computer to automatically restart or return to its last operating status after power returns from a power failure.

**Off:** The system stays off after a power failure.

**Former-Sts:** The system returns to the state it was in just prior to the power

failure

## ▶ IRQ/Event Activity Detect

Scroll to IRQ/Event Activity Detect and press <Enter>. The following screen appears:

| Phoenix - AwardBIOS CMOS Setup Utility<br>IRQ/Event Activity Detect |                          |                                              |  |

|---------------------------------------------------------------------|--------------------------|----------------------------------------------|--|

| PS2KB Wakeup Select                                                 |                          | Item Help                                    |  |

| PS2KB Wakeup from \$3/\$4/\$<br>PS2MS Wakeup from \$3/\$4/\$        | 5[Disabled]              | Menu Level ►►                                |  |

|                                                                     | [Disabled]<br>[Disabled] | When Select Password,                        |  |

| PowerOn by OnBoard LAN<br>Modem Ring Resume                         | [Disabled]<br>[Disabled] | Please press ENTER key<br>to change Password |  |

| RTC Alarm Resume                                                    | [Disabled]               | Max 8 numbers.                               |  |

| x Date (of Month)<br>x Resume Time (hh:mm:ss)                       | 0:0:0                    |                                              |  |

#### **PS2KB Wakeup Select**

This item allows you to select Hot Key or Password to wake-up the system by PS2 Keyboard. If Password is selected, press <Enter> key to change a password with max 8 numbers.

Options: Hot key, Password.

## PS2KB Wakeup form S3/S4/S5

This item allows you to set a Hot Key to wake-up the system by PS2 Keyboard. Options: Disabled, Ctrl+F1, Ctrl+F2, Ctrl+F3, Ctrl+F4, Ctrl+F5, Ctrl+F6, Ctrl+F7, Ctrl+F8,

Ctrl+F9, Ctrl+F10, Ctrl+F11, Ctrl+F12, Power, Wake, Any key.

Note: Power and Wake are Windows98 Keyboard button.

## PS2MS Wakeup form S3/S4/S5

This item allows you to wake-up the system by PS2 Mouse.

Options: Enabled, Disabled.

#### **USB Resume from S3**

This item allows a USB device to wake-up the system from S3 suspend state.

Options: Enabled, Disabled.

#### PowerOn by PCI Card

An input signal from PME on the PCI card awakens the system from soft-off state. Options: Enabled, Disabled.

#### PowerOn by OnBoard LAN

This item allows you to power on the system by onboard LAN from soft-off state. Options: Enabled, Disabled.

## Modem Ring Resume

When set to "Enabled", any event occurring to the Modem Ring will awaken the system from suspend state.

Options: Enabled, Disabled.

#### **RTC Alarm Resume**

When set to Enable rtc alarm resume, you can set the date (of month) and time (hh: mm:ss), that will awaken a system which has been powered down.

Options: Enabled, Disabled.

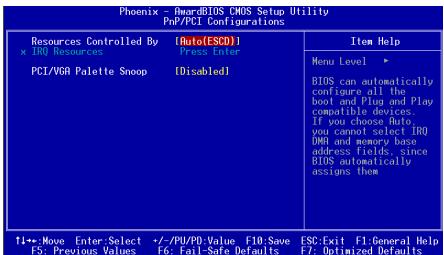

## 4-6 PNP/PCI Configuration

This page lets the user to modify the PCI IRQ signals when various PCI cards are inserted.

WARNING: Conflicting IRQ's may cause system unable to locate certain devices.

Figure 7: PNP/PCI Configuration Setup

## **Resources Controlled By**

Determines what controls system PNP/PCI resources. The default is Auto (ESCD).

Manual: PNP Card's resources are controlled manually. The "IRQ Resources" field

becomes available and you can set which IRQ-X and DMA-X are

assigned to PCI and onboard devices.

**Auto**: BIOS assigns the interrupt resource automatically.

#### **PCI/VGA Palette Snoop**

This item is designed to overcome problems that may be caused by some nonstandard VGA cards

Options: Enabled, Disabled.

## Interrupt requests are shared as shown below:

|                          | INT A | INT B | INT C | INT D |

|--------------------------|-------|-------|-------|-------|

| PCI1                     |       | V     |       |       |

| PCI 2                    |       |       | V     |       |

| PCI3                     |       |       |       | V     |

| PCI4                     | V     |       |       |       |

| PCI 5                    |       | V     |       |       |

| AGP Slot                 | V     |       |       |       |

| AC97                     |       |       | V     |       |

| Onboard USB1             | V     |       |       |       |

| Onboard USB2             |       | V     |       |       |

| Onboard USB3             |       |       | V     |       |

| Onboard USB4             |       |       | V     |       |

| USB2.0                   |       |       |       | v     |

| Onboard S-ATA (Optional) | V     |       |       |       |

| Onboard LAN (Optional)   | ٧     |       |       |       |

#### **IMPORTANT!**

When using PCI cards on shared IRQ slots, make sure its drivers support "Shared IRQ", or that the cards do not need IRQ assignments. IRQ conflicts between the two PCI groups will make the system unstable or cards inoperable.

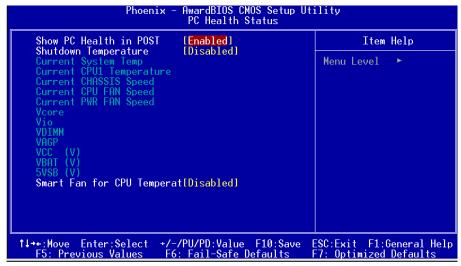

## 4-7 PC Health Status

Figure 8: PC Health Status

#### Show PC Health in POST

When this function is enabled the PC Health information is displayed during the POST (Power On Self Test).

Options: Disabled, Enabled.

## **Shutdown Temperature**

This is the temperature that the computer will turn off the power to combat the effects of an overheating system. (requires ACPI to be enabled in Power Management BIOS and ACPI compliant operating system.) The default is Disabled. Options available are 60°C/140°F to 70°C/158°F in increments of 5°C.

## **Current System/CPU Temperature**

Displays the current system/CPU temperature.

## **Current CHASSIS/CPU/PWR FAN Speed**

Displays the current speed of the CPU, Power and chassis fan speed in RPMs.

#### Vcore

The voltage level of the CPU(Vcore).

#### **VDIMM**

The voltage level of the DRAM.

#### **VAGP**

The voltage level of power supplied to AGP card.

#### VBAT(V)

The voltage level of the battery.

#### VCC, Vio, 5VSB(V)

The voltage level of the switching power supply.

#### **Smart Fan for CPU Temperature**

This item allows you set CPU fan temperature to smartly adjust the fan speeds for more efficient system operation.

Options: Disabled, 35°C/95°F, 40°C/104°F, 45°C/113°F.

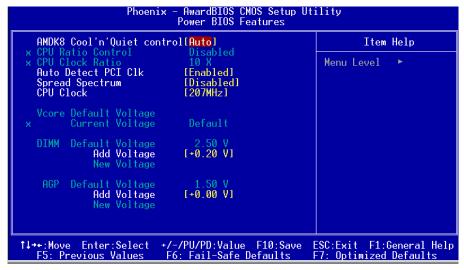

## **4-8 Power BIOS Features**

This page lets you adjust various parameters to obtain improved performance for overclocking.

## Warning:

Overclocking requires expert knowledge and risks permanent damage to system components. We recommend you leave these parameters at their default values for proper operation.

Figure 9: Frequency/Voltage Control

#### AMD K8 Cool'n'Quiet control

Reduce the noise and heat from you PC when AMD's Cool'n'Quiet™ technology is enabled.

Options: Enabled, Disabled.

#### **CPU Ratio Control**

This item allows you to enable the CPU clock ratio control. Choose "Enabled" to key in a CPU clock Ratio in the next selection.

Options: Enabled, Disabled.

#### **CPU Clock Ratio**

Use this item to select a multiplier to set the CPU frequency. See CPU Clock item below for explanation.

Key in the DEC (decimal) number for the CPU Clock Ratio.

#### **Auto Detect PCI CIk**

When enabled the mainboard automatically disables the clock source for a PCI slot which does not have a module in it, reducing EMI (ElectroMagnetic Interference). Options: Enabled, Disabled.

## **Spread Spectrum**

If you enable spread spectrum, it can significantly reduce the EMI (ElectroMagnetic Interference) generated by the system.

Options: Disabled, Enabeld.

#### **CPU Clock**

Enables you to increment the CPU's clock generator at 1MHz step. This works together with CPU Clock Ratio (above) to set the CPU operating frequency.

CPU Clock Generator x CPU Clock Ratio = CPU Frequency

For example, if you have a processor that is rated at 2.4GHz and the clock generator is 200MHz, then 200MHz x 12 = 2.4GHz

Press <Enter> to display the following screen:

```

CPU Clock

200

Kev in a DEC number :

↑↓:Move ENTER:Accept ESC:Abort

```

Key in the DEC (decimalism) number for the CPU clock.

Note: Overclocking failure will cause no display on the monitor. To overcome this switch off the power supply and switch on again. Restart the system, press and hold < Insert> key. This will revert the BIOS to default or initial setting.

In the following items, "Default Voltage" indicates the original factory value, and "New Voltage" indicates the value that you assign.

#### **CPU Vcore Voltage**

This item allows you to set the CPU Vcore voltage.

Options: Default, 1.350V to 1.550V in 0.025V increment and 1.550V to 1.700V in 0.050V increment. We recommend that you leave this at the default value.

## **DIMM Voltage**

This item allows you to adjust the DIMM slot voltage.

Options: +0.00V to +0.30V in 0.10V increments. We recommend that you leave this at the default value

## **AGP Voltage**

This item allows you to adjust the AGP slot voltage.

Options: +0.00V to +0.30V in 0.10V increments. We recommend that you leave this at the default value.

## 4-9 Defaults Menu

Selecting "Defaults" from the main menu shows you two options which are described below

#### **Load Fail-Safe Defaults**

When you press <Enter> on this item you get a confirmation dialog box:

Load Fail-Safe Defaults (Y/N)? N

Pressing 'Y' loads the BIOS default values for the most stable, minimal-performance system operations.

## **Load Optimized Defaults**

When you press <Enter> on this item you get a confirmation dialog box:

Load Optimized Defaults (Y/N)? N

Pressing 'Y' loads the default values that are factory settings for optimal performance system operations.

## 4-10 Supervisor/User Password Setting

This function lets you set either Supervisor or User Password, or both, to prevent unauthorized changes to BIOS menus.

**supervisor password:** full rights to enter and change options of the setup menus.

**user password:** only enter but no rights to change options of the setup

menus.

When you select this function, the following message will appear at the center of the screen to assist you in creating a password.

#### ENTER PASSWORD:

Type the password, up to eight characters in length, and press <Enter>. The password typed now will clear any previously entered password from CMOS memory. You will be asked to confirm the password. Type the password again and press <Enter>. You may also press <Esc> to abort the selection and not enter a password.

To disable a password, just press <Enter> when you are prompted to enter the password. A message will confirm the password will be disabled. Once the password is disabled, the system will boot and you can enter Setup freely.

#### PASSWORD DISABLED.

When a password has been enabled, you will be prompted to key in each time you enter Setup. This prevents an unauthorized person from changing any part of your system configuration.

Additionally, when a password is enabled, you can also require the BIOS to request a password every time your system is rebooted. This would prevent unauthorized use of your computer.

You can determine when the password is required within the Advanced BIOS Features Menu and its Security option. If the Security option is set to "System", the password will be required both at boot and at entry to Setup. If set to "Setup", prompting only occurs when trying to enter Setup.

## 4-11 Exiting BIOS

## Save & Exit Setup

Pressing <Enter> on this item asks for confirmation:

#### Save to CMOS and EXIT (Y/N)? Y

Pressing "Y" stores the selections made in the menus in CMOS – a special section of memory that stays on after you turn your system off. The next time you boot your computer, the BIOS configures your system according to the Setup selections stored in CMOS. After saving the values the system is restarted again.

#### **Exit Without Saving**

Pressing <Enter> on this item asks for confirmation:

#### Quit without saving (Y/N)? Y

This allows you to exit Setup without storing in CMOS any change. The previous selections remain in effect. This exits the Setup utility and restarts your computer.

## **BIOS**

# Section 5 S-ATA RAID CONFIGURATION

## Introduction

This section gives a brief introduction on RAID-related background knowledge and a general procedure to setup RAID system on this mainboard.

#### **RAID Basics**

RAID (Redundant Array of Independent Disks) is a method of combining two or more hard disk drives into one logical unit known as a RAID array. The advantage of RAID is to provide better performance or data fault tolerance. Fault tolerance is achieved through data redundant operation, where if one drives fails, a mirrored copy of the data can be found on another drive. This can prevent data loss if the operating system fails or hangs.

Below is an example of a RAID array with 2 drives.

The individual disk drives in an array are called "members". All disk members in a formed disk array are recognized as a single physical drive to the operating system.

Hard disk drives can be combined together through a few different methods. The different methods are referred to as different RAID levels. Different RAID levels represent different performance levels, security levels and implementation costs. The table below briefly introduced these RAID levels.

| RAID Level         | No. of Drives | Capacity                        | Benefits                                                                    |

|--------------------|---------------|---------------------------------|-----------------------------------------------------------------------------|

| RAID 0 (Striping)  | 2             | INjumber drivers *Smallest size | Highest performance without data protection                                 |

| RAID 1 (Mirroring) | 2             | Smallest size                   | Data protection                                                             |

| JBOD (Spanning)    | 2             |                                 | No data protection and performance improving, but disk capacity fully used. |

## **S-ATA RAID Configuration**

## RAID 0 (Striping)

RAID 0 reads and writes sectors of data interleaved between multiple drives. If any disk member fails, it affects the entire array. The disk array data capacity is equal to the number of drive members times the capacity of the smallest member. The striping block size can be set from 4KB to 64KB. RAID 0 does not support fault tolerance.

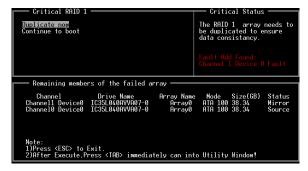

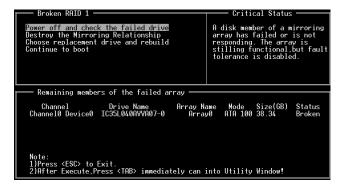

## RAID 1 (Mirroring)

RAID 1 writes duplicate data onto a pair of drives and reads both sets of data in parallel. If one of the mirrored drives suffers a mechanical failure or does not respond, the remaining drive will continue to function. Due to redundancy, the drive capacity of the array is the capacity of the smallest drive. Under a RAID 1 setup, an extra drive called the "spare drive" can be attached. Such a drive will be activated to replace a failed drive that is part of a mirrored array. Due to the fault tolerance, if any RAID 1 drive fails, data access will not be affected as long as there are other working drives in the array.

## JBOD (Spanning)

A spanning disk array is equal to the sum of the all drives when the drives used are having different capacities. Spanning stores data onto a drive until it is full, then proceeds to store files onto the next drive in the array. When any disk member fails, the failure affects the entire array. JBOD is not really a RAID and does not support fault tolerance.

## **Others**

Other RAID derivatives are RAID 10 and RAID 5. These RAID levels require more than 2 drives to operate, combining the benefits of RAID 0 and RAID 1.

This mainboard is equipped with the following SATA RAID controllers:

- 1. VIA SATA from VIA VT8237 south bridge (SATA1/ SATA2)

- 2. (Optional) Silicon Image SiI3114 controller (SATA3/ SATA4/SATA5/SATA6)

Each of these controllers have their own unique RAID setup BIOS and software.

**Note**: Before you proceed, identify which SATA controller your HDD drives are connected to in order to ensure a successful installation.

## **VIA S-ATA RAID Features**

The VIA S-ATA RAID solution uses the VT8237 chip as a RAID controller, which is a 2-channel S-ATA and 1-channel ATA133 solution. Listed below are the main features and benefits of VIA S-ATA RAID:

- Support two S-ATA hard disk drives.

- Supports hard disk drive larger than 137 GB (48-bits LBA).

- Supports RAID 0, 1 and JBOD.

- 4 KB to 64 KB striping block size support.

- Bootable disk or disk array support.

- Windows-based RAID configure and management software tool. (Compatible with BIOS)

- Real-time monitoring of device status and error alarm with popup message box and beeping.

- · Mirroring automatic background rebuilds support.

- ATA SMART function support.

- Microsoft Windows 98, Me, NT4.0, 2000, XP operating systems support.

- Event log for easy troubleshooting.

- On-line help for easy operation for RAID software.

## **Optional - Silicon Image Sil3114 S-ATA RAID Features**

- RAID 0, 1, 5, 10

- · Hot Spare and On-line Mirror Rebuilding

- System GUI Monitoring Utility:

- Displays/Logs/Alerts Users to Vital RAID Set Information

- Manages RAID Set Functions (configures, rebuilds, etc.)

- RAID Set Accommodates Multiple Size HDDs

- HDDs function normally when not in RAID Sets

- Adjustable Stripe Size for RAID 0

- Automatically Selects Highest Available Transfer Speed for All ATA and ATAPI Devices

- Supports:

- UDMA up to 150MB/Sec.

- All UDMA and PIO Modes

- Up to 4 SATA devices

- ACPI and ATA/ATAPI6

#### **Enable RAID Function**

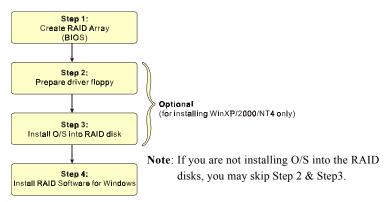

For any RAID controller, the general procedure to enable RAID function are shown below:

## Step 1: Create RAID Array

RAID arrays are created using the RAID controller's BIOS utility.

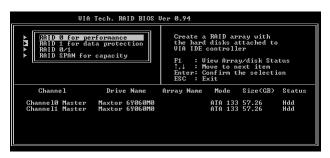

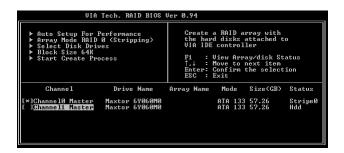

#### VIA VT8237

Power-on the system and wait for the following screen to appear. Press the "Tab" key to enter its BIOS configuration utility.

```

UIA Technologies, Inc. UIA UI6428 RAID BIOS Setting Utility U0.94

Copyright (C) UIA Technologies, Inc. All Right reserved.

Press ( Tab > key into User Vindou!

Scan Devices, Please voit.,

Channel 0 Master: Maxtor 649660M0

Channel 1 Master: Maxtor 649660M0

```

The main interface of the BIOS utility is as below:

```

Create APAID Array

Delete Array

UIA IDE controller

Fig. When Pray/disk Status

I, Howe to next item

Enter: Confirm the selection

ESC: Exit

Channel Drive Name Array Name Mode SizeGB) Status

Channel Master Maxtor 64969MB

Channell Master Maxtor 64969MB

Array Name Array Array

Array Name Mode SizeGB) Status

Channell Master Maxtor 64969MB

Array Name Mode SizeGB) Hdd

```

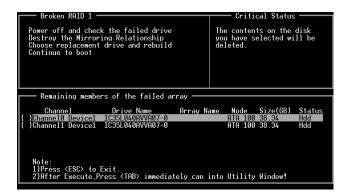

Refer to Appendix B-1 for details about creating RAID array using this utility. After the RAID array is created, press "ESC" to exit.

## (Optional) Silicon Image Sil3114

Wait for the following message to appear during boot-up:

## Press < CTRL-S > or F4 to enter RAID utility.

An easy-to-use screen will appear with the following choices in the top left:

- Create RAID Set

- Delete RAID Set

- · Rebuild RAID Set

- Resolve Conflicts

- Low Level Format

- · Logical Drive Info

Refer to Appendix B-2 for details about creating RAID array using this utility.

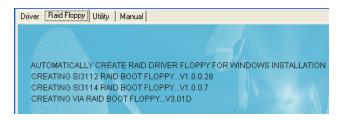

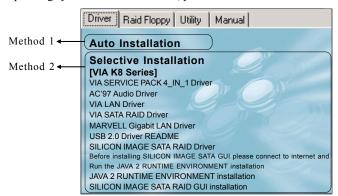

## Step 2: Prepare driver floppy

When installing Windows XP/2000/NT4.0 into any RAID disk, the O/S setup will require a floppy disk containing the RAID driver. This step will show you how to prepare this driver floppy. There are 2 methods to prepare this floppy:

#### Method 1

- Insert the bundled CD into the CD-ROM drive

- 2. Boot the system from the CD-ROM

- 3. A menu of driver for various RAID controllers will appear

- 4. Insert a blank floppy into the A:drive

- 5. Select the appropriate RAID controller to begin copy into the floppy

#### Method 2

- 1. Locate another computer and insert the bundled CD into its CD-ROM drive.

- 2. A main menu screen will appear (Autorun feature)

- 3. Select the page "RAID floppy"

- 4. Insert a blank floppy into the A:drive

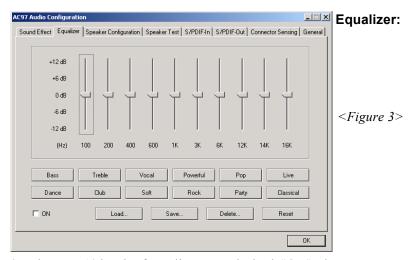

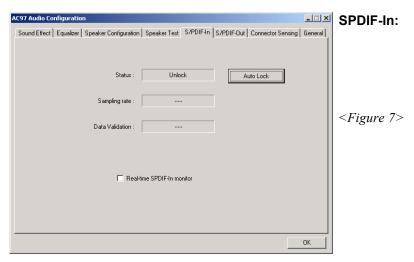

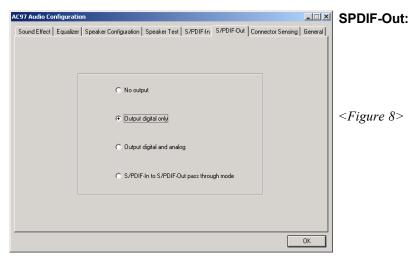

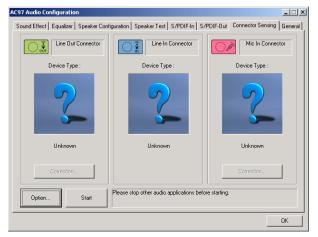

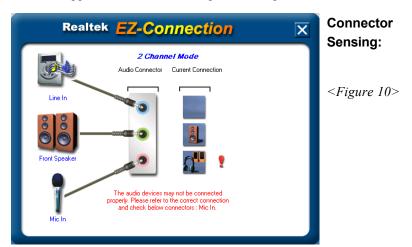

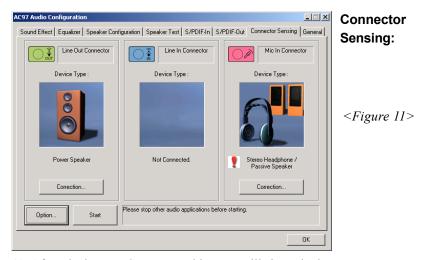

- 5. Click on the required driver to begin copy into the floppy