## **Table of Contents**

| Notice                                                       | IV     |

|--------------------------------------------------------------|--------|

| Introduction                                                 | V      |

| Chapter 1 Pre-Configuration.                                 | 1      |

| Step 1 Setting the Jumpers                                   | 3      |

| Jumper Locations                                             | 4      |

| CMOS Reset                                                   | 5      |

| ATA-Disk Connector Voltage Selection                         | 5      |

| RS422/RS485 Termination Resistors (optional)                 |        |

| Audio Jack Output SelectionBacklight Logic Voltage Selection | b      |

| Inverter Voltage Selection                                   | ە<br>6 |

| Step 2 SDRAM, CPU, and Cables                                |        |

| Installation                                                 | 7      |

| Captor M Memory Configuration                                | 7      |

| CPU Installation                                             |        |

| Installing Cables                                            |        |

| Power and Control Panel Cables                               |        |

| Installing Peripheral Cables                                 |        |

| Index of Connectors                                          | 12     |

| Chapter 2 AMIBIOS8 Setup                                     | 15     |

| Main Setup                                                   | 18     |

| Advanced BIOS Setup                                          | 18     |

| PCI/PnP Setup                                                |        |

| Boot Setup                                                   |        |

| Security Setup                                               |        |

| Chipset Setup                                                |        |

| Power Management Setup                                       |        |

| Exit Menu                                                    | 48     |

| Chapter 3 Upgrading                | 51         |

|------------------------------------|------------|

| Upgrading the Microprocessor       |            |

| Upgrading the System Memory        | 51         |

| Appendix A Technical               |            |

| Specifications                     | 53         |

| Chipsets                           | 53         |

| BIOS                               |            |

| Embedded I/O                       |            |

| Industrial Devices                 |            |

| Miscellaneous                      |            |

| Memory Map                         |            |

| DMA Channels                       |            |

| I/O MapPCI Configuration Space Map |            |

| Interrupts                         |            |

| SMBUS                              |            |

| PCI Interrupt Routing Map          |            |

| Connectors Pin-out                 |            |

| Appendix B Flash BIOS              |            |

| programming and codes              | 73         |

| Troubleshooting POST               | 73         |

| Critical Error BEEP Codes          | 80         |

| Appendix C On-Board Indu           | ıstrial    |

| Devices                            | Q <i>1</i> |

| Device3                            | O I        |

| Post Code Display                  | 81         |

| ISA Bridge                         |            |

| On-board Ethernet                  |            |

| Serial Ports                       |            |

| Watchdog Timer                     | 90         |

| Appendix D | On-Board   | Video |    |

|------------|------------|-------|----|

|            | Controller |       | 91 |

### **Notice**

The company reserves the right to revise this publication or to change its contents without notice. Information contained herein is for reference only and does not constitute a commitment on the part of the manufacturer or any subsequent vendor. They are in no way responsible for any loss or damage resulting from the use (or misuse) of this publication.

This publication and any accompanying software may not, in whole or in part, be copied, photocopied, translated or reduced to any machine readable form without prior consent from the vendor, manufacturer or creators of this publication, except for copies kept by the user for backup purposes.

Brand and product names mentioned in this publication may or may not be copyrights and/or registered trademarks of their respective companies. They are mentioned for identification purposes only and are not intended as an endorsement of that product or its manufacturer.

First Edition.

©January, 2005

## Introduction

Thank you for your purchase of the Captor M industrial single board computer motherboard. The Captor M design was based on the Intel 855GME chipset providing the ideal platform to industrial applications. The Captor M design is based on the Intel Pentium M and Celeron M (μFC-PGA 478) processors.

With proper installation and maintenance, your Captor M will provide years of high performance and trouble free operation.

This manual provides a detailed explanation into the installation and use of the Captor M industrial embedded motherboard. This manual is written for the novice PC user/installer. However, as with any major computer component installation, previous experience is helpful and should you not have prior experience, it would be prudent to have someone assist you in the installation. This manual is broken down into 3 chapters and 4 appendixes.

### **Chapter 1 - System Board Pre-Configuration**

This chapter provides all the necessary information for installing the Captor M. Topics discussed include: installing the CPU (if necessary), DRAM installation and jumper settings. Connecting all the cables from the system board to the chassis and peripherals is also explained.

## Chapter 2 - BIOS Configuration

This chapter shows the final step in getting your system firmware setup.

## Chapter 3 - Upgrading

The Captor M provides a number of expansion options including memory. All aspects of the upgrade possibilities are covered

### Appendix A - Technical Specifications

A complete listing of all the major technical specifications of the Captor M is provided.

### Appendix B - Flash BIOS Programming and Codes

Provides all information necessary to program your AMIBIOS8 Flash BIOS. POST Codes and beep codes are described in details.

### Appendix C - On-Board Industrial Devices

Two on-board 10/100 (10/100/1000 optional) Ethernet controllers (second Ethernet optional), ISA bridge, six serial ports (one optional RS422/485), watchdog timer and Post Code Display.

### Appendix D - On-Board Video Controller

On-board CRT and LVDS video controller.

## Static Electricity Warning!

The Captor M has been designed as rugged as possible but can still be damaged if jarred sharply or struck. Handle the motherboard with care. The Captor M also contains delicate electronic circuits that can be damaged or weakened by static electricity. Before removing the Captor M from its protective packaging, it is strongly recommended that you use a grounding wrist strap. The grounding strap will safely discharge any static electricity build up in your body and will avoid damaging the motherboard. Do not walk across a carpet or linoleum floor with the bare board in hand.

## Warranty

This product is warranted against material and manufacturing defects for two years from the date of delivery. Buyer agrees that if this product proves defective the manufacturer is only obligated to repair, replace or refund the purchase price of this product at manufacturer's discretion. The warranty is void if the product has been subjected to alteration, misuse or abuse; if any repairs have been attempted by anyone other than the manufacturer; or if failure is caused by accident, acts of God, or other causes beyond the manufacturer's control.

## Captor M - An Overview

The Captor M represents the ultimate in industrial embedded motherboard technology. No other system board available today provides such impressive list of features:

## **CPU Support**

• Supports full series of Intel Pentium M, Intel Pentium M on 90nm process with 2MB L2 cache and Celeron M 400MHz PSB processors featuring next-generation Intel SpeedStep® technology on the µFC-PGA 478 package.

## Supported Bus Clocks

400MHz.

## **Memory**

• Two DIMM sockets up to 2GB (unbuffered, ECC & non-ECC) DDR SDRAM, PC1600 (DDR 200MHz), PC2100 (DDR 266MHz) and PC2700 (DDR 333MHz). Please, refer to chapter 3 for memory details.

## On-Board I/O

- 2 Floppies up to 2.88 MB.

- Dual channel PCI 32-bit EIDE controller UDMA 66/100 supported. One extra connector (mini-Header 44 pin) in parallel to IDE2 for Solid State IDE disk or any 44 pin IDE device support.

- Six high speed RS-232 serial ports 16 Bytes FIFO (16550). COM2 optional RS-232 IrDA and COM1 optional RS-422/485.

- One Centronics<sup>TM</sup> compatible bi-directional parallel port. EPP/ECP mode compatible.

- One PS/2 mouse/keyboard combined connector.

- Six Universal Serial Bus connectors, USB 1.1 and USB 2.0 compliant.

- One PICMIG 1.0 rev 2 edge connector (PCI & ISA) and one mini-PCI slot.

- Two RJ45 Ethernet connectors (second optional, both optional 10/100/1000).

- Power Button advanced management support.

- Automatic CPU voltage & temperature monitoring device.

- On-board Buzzer.

- Audio (AD1981B) AC97 compliant. Microphone In, Stereo Line In and Out, CD In.

- On-board POST Display Diagnostics.

- On-board watchdog timer.

## **ROM BIOS**

American Megatrends AMIBIOS8 with FLASH ROM.

## On-Board CRT & LVDS video controller

- Standard CRT video controller (Intel 855GME chipset).

- Dedicated Local Flat Panel (LFP) LVDS interface.

## Conventions Used in this Manual

Notes - Such as a brief discussion of memory types.

Important Information - such as static warnings, or very important instructions.

When instructed to enter keyboard keystrokes, the text will be noted by this graphic.

## Chapter 1 Pre-Configuration

This chapter provides all the necessary information for installing the Captor M into a standard PC chassis with a PICMIG backplane. Topics discussed include: installing the CPU (if necessary), DRAM installation and jumper settings.

## Handling Precautions

The Captor M has been designed to be as rugged as possible but it can be damaged if dropped, jarred sharply or struck. Damage may also occur by using excessive force in performing certain installation procedures such as forcing the system board into the chassis or placing too much torque on a mounting screw.

Take special care when installing or removing the system memory DIMMs. Never force a DIMM into a socket. Screwdrivers slipping off a screw and scraping the board can break a trace or component leads, rendering the board unusable. Always handle the Captor M with care.

## Special Warranty Note:

Products returned for warranty repair will be inspected for damage caused by improper installation and misuse as described in the previous section and the static warning below. Should the board show signs of abuse, the warranty will become void and the customer will be billed for all repairs and shipping and handling costs.

## **Static Warning**

The Captor M contains delicate electronic semiconductors that are highly sensitive to static electricity. These components, if subjected to a static electricity discharge, can be weakened thereby reducing the serviceable life of the system board. BEFORE THE BOARD IS REMOVED FROM ITS PROTECTIVE ANTISTATIC PACKAGING.

## Captor M – Installation Guide

TAKE PROPER PRECAUTIONS! Work on a conductive surface that is connected to the ground. Before touching any electronic device, ground yourself by touching an unpainted metal object or, and highly recommended, use a grounding strap.

## Step 1 Setting the Jumpers

Your Captor M is equipped with a large number of peripherals. As such, there are a large number of configuration jumpers on the board. Taken step by step, setting these jumpers is easy. We suggest you review each section and follow the instructions.

Special note about operating frequency: The Captor M has the ability to run at a variety of speeds without the need to change any crystal, oscillator or jumper.

## Jumper Types

Jumpers are small copper pins attached to the system board. Covering two pins with a shunt closes the connection between them. The Captor M examines these jumpers to determine specific configuration information. There are two different categories of jumpers on the Captor M.

A. Two pin jumpers are used for binary selections such as enable, disable. Instructions for this type of jumper are open, for no shunt over the pins or closed, when the shunt covers the pins.

B. Three or four pin jumpers are used for multiple selections. Instructions for these jumpers will indicate which two pins to cover. For example: for JPx 2-3 the shunt will be covering pins 2 and 3 leaving pins 1 and 4 exposed.

How to identify pin number 1 on *Figure 1-1*: Looking to the solder side (The board side with fewer components) of the PCB (Printed Circuit Board), pin number 1 will have a squared pad . Other pins will have a circular pad . They are numbered sequentially.

Double row jumpers are numbered alternately, i.e. pin number 2 is in the other row, but in the same column of pin number 1. Pin number 3 is in the same row of pin 1, but in the next column and so forth.

## **Jumper Locations**

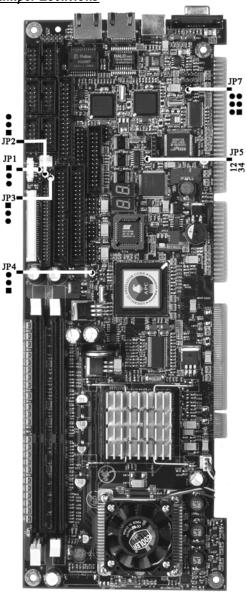

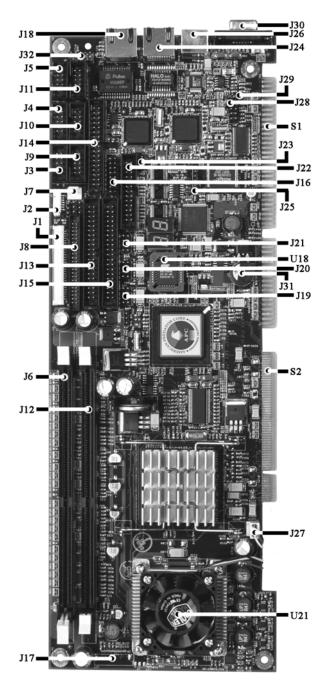

Use the diagram below and the tables on the following pages to locate and set the on-board configuration jumpers.

Figure 1-1 Jumper Locations

## **CMOS Reset**

This option is provided as a convenience for those who need to reset the CMOS registers. It should always be set to "Normal" for standard operation. If the CMOS needs to be reset, turn off the system, move JP4 to 2-3, turn the system on, move jumper to 1-2 and press reset.

Table 1-1 CMOS Reset

| Reset CMOS | Normal | Clear CMOS |

|------------|--------|------------|

| JP4        | 1-2*   | 2-3        |

<sup>\*</sup> Manufacturer's Settings.

## ATA-Disk Connector Voltage Selection

The ATA-Disk Connector J8 can provide either 5Vcc or 3.3Vcc. The jumper JP3 selects the voltage.

Table 1-2 ATA-Disk Connector Voltage Select

| ATA-Disk<br>Voltage | 5Vcc | 3.3Vcc |

|---------------------|------|--------|

| JP3                 | 1-2* | 2-3    |

<sup>\*</sup>Manufacturer's Settings.

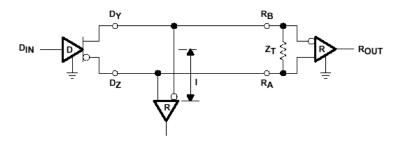

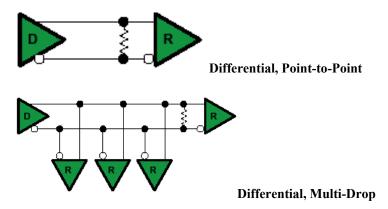

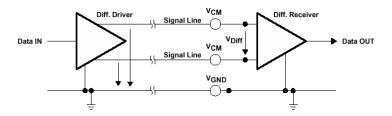

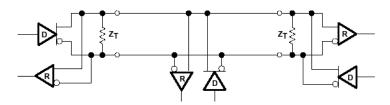

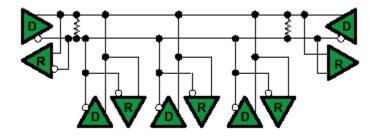

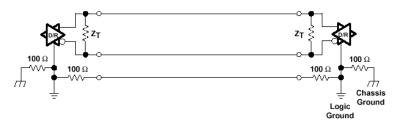

## RS422/RS485 Termination Resistors (optional)

The Jumper JP5 allows the insertion/removal of the termination resistors ( $120\Omega$ ) in the Receiver and Transmitter lines of the COM1 when operating in RS-422/485 mode.

<u>Table 1-3 COM1 RS-422/485 Tx & Rx Termination Resistor Selection</u>

| Termination resistor selection | Transmitter | Receiver |

|--------------------------------|-------------|----------|

| JP5                            | 1-3         | 2-4      |

<sup>\*</sup> Manufacturer's Setting is off.

## **Audio Jack Output Selection**

The audio output on the header connector J32 can be selected to be stereo line out or stereo headphone out (amplified signal). The jumper JP7 selects the audio output signals.

Table 1-4 Audio Output Mode Selection

| Audio Output<br>Mode Selection | Headphone | Line Out  |

|--------------------------------|-----------|-----------|

| JP7                            | 1-3, 2-4  | 3-5, 4-6* |

<sup>\*</sup> Manufacturer's Settings.

## **Backlight Logic Voltage Selection**

The LVDS power connector J2 can supply either 5Vcc or 3.3Vcc for the logic circuits in the backlight inverter. The jumper JP1 selects the voltage.

Table 1-5 Backlight Logic Voltage Select

| Backlight<br>Logic<br>Voltage | 5Vcc | 3.3Vcc |

|-------------------------------|------|--------|

| JP1                           | 1-2  | 2-3*   |

<sup>\*</sup> Manufacturer's Settings.

## **Inverter Voltage Selection**

The LVDS power connector J2 can supply either 5Vcc or 12Vcc for the backlight inverter. The jumper JP2 selects the voltage.

<u>Table 1-6 Inverter Voltage Select</u>

| Inverter<br>Voltage | 12Vcc | 5Vcc |

|---------------------|-------|------|

| JP2                 | 1-2   | 2-3* |

<sup>\*</sup> Manufacturer's Settings.

# Step 2 SDRAM, CPU, and Cables Installation

Depending upon how your Captor M is configured you may need to install the following:

- SDRAM (DIMMs)

- CPU

## Captor M Memory Configuration

The Captor M offers 2 DIMM memory sockets (Locations J6 and J12 – *Figure 1-2*). They can be configured with 2.5V unbuffered SDRAM DDR modules. It is very important that the quality of the DIMMs is good. Unreliable operation of the system may result if poor quality DIMMs are used. Always purchase your memory from a reliable source. Please, refer to chapter 3 for memory details.

## **CPU Installation**

The Captor M currently supports the following CPUs:

• Full series of Intel Pentium M, Intel Pentium M on 90nm process with 2MB L2 cache and Celeron M 400MHz PSB processors featuring next-generation Intel SpeedStep® technology on the  $\mu FC\text{-PGA}$  478 package.

- 1. Improper installation of the CPU may cause permanent damage to both the system board and the CPU. -- Void of warranty

- 2. Always handle the CPU by the edges, never touch the pins.

- 3. Always use a heat-sink and a CPU fan.

Locate the CPU socket on your Captor M system board ( $\mu$ FC-PGA 478 Socket – Location U21 – *Figure 1-2*). To install the processor, rotate the screw of the ZIF socket counter clock-wise until the open position and gently insert the CPU. The CPU will fit only in the right alignment. Make sure the CPU is inserted all the way. Rotate the screw clock-wise

until the closed position. Install the CPU fan. Make sure it is locked and connected to J27 (see pin-out in Appendix A).

The continued push of technology to increase performance levels (higher operating speeds) and packaging density (more transistors) is aggravating the thermal management of the CPU. As operating frequencies increase and packaging sizes decreases, the power density increases and the thermal cooling solution space and airflow become more constrained. The result is an increased importance on system design to ensure that thermal design requirements are met for the CPU.

The objective of thermal management is to ensure that the temperature of the processor is maintained within functional limits. The functional temperature limit is the range within which the electrical circuits can be expected to meet their specified performance requirements. Operation outside the functional limit can degrade system performance, cause logic errors or cause component and/or system damage. Temperatures exceeding the maximum operating limits may result in irreversible changes in the operating characteristics of the component.

If the Captor M industrial embedded motherboard is acquired without the CPU and the thermal solution, extremely care must be taken to avoid improper thermal management. All Intel thermal solution specifications, design guidelines and suggestions to the CPU being used must be followed. The Captor M warranty is void if the thermal management does not comply with Intel requirements.

### Designing for thermal performance

In designing for thermal performance, the goal is to keep the processor within the operational thermal specifications. The inability to do so will shorten the life of the processor.

### Fan Heatsink

An active fan heatsink can be employed as a mechanism for cooling the Intel processors. This is the acceptable solution for most chassis. Adequate clearance must be provided around the fan heatsink to ensure unimpeded air flow for proper cooling.

### Airflow management

It is important to manage the velocity, quantity and direction of air that flows within the system (and how it flows) to maximize the volume of air that flows over the processor.

### Thermal interface management

To optimize the heatsink design for the Pentium M processor, it is important to understand the impact of factors related to the interface between the processor and the heatsink base. Specifically, the bond line thickness, interface material area, and interface material thermal conductivity should be managed to realize the most effective thermal solution.

Once used, the thermal interface should be discarded and a new one installed. Never assemble the heatsink with a previously used thermal interface.

This completes the installation of the CPU. Now is it a good time to double check both the CPU and DIMM installation to make sure that these devices have been properly installed.

## **Installing Cables**

## Power and Control Panel Cables

The Captor M gets power from the PICMG edge connectors S1 and S2 (*Figure 1-2*).

## Installing Peripheral Cables

Now it is a good time to install the internal peripherals such as floppy and hard disk drives. Do not connect the power cable to these peripherals, as it is easier to attach the bulky ribbon cables before the smaller power connectors. If you are installing more than one IDE drive double check your master/slave jumpers on the drives. Review the information supplied with your drive for more information on this subject.

Most modern HDDs are UDMA-5 capable. To make use of the Ultra DMA-5 capabilities, 80-conductor cables must be used. The BIOS and the HDD will check for the existence of the 80-conductor cable. The long leg of the cable must be connected to the board; otherwise it won't work as an 80-conductor cable. If connecting another peripheral that is not UDMA-5 capable (most optical devices are not), the whole IDE channel will be downgraded to UDMA-2. In that case, it is recommended to use a different IDE channel for the non-UDMA-5 capable peripherals.

## <u>Captor M – Installation Guide</u>

Connect the floppy cable (not included) to the system board. Finally, connect the IDE cable (not included) to the system. If using a Solid State Device, connect it to the mini-ATA connector. Connect all interface cables to their headers. Then connect remaining ends of the ribbon cable to the appropriate peripherals.

This concludes the hardware installation of your Captor M system. Now it is a good time to re-check all of the cable connections to make sure they are correct.

## **Index of Connectors**

Please refer to Appendix A for pin-out descriptions.

Table 1-7 Connectors description

| Connector | Description                                         |

|-----------|-----------------------------------------------------|

| J1        | LVDS                                                |

| J2        | LVDS Backlight                                      |

| J3        | COM3                                                |

| J4        | COM1                                                |

| J5        | COM5                                                |

| J6        | DDR DIMM Socket 1                                   |

| J7        | Rear Chassis Fan                                    |

| J8        | Alt. Secondary IDE – 44-pin                         |

| J9        | COM4                                                |

| J10       | COM2                                                |

| J11       | COM6                                                |

| J12       | DDR DIMM Socket 0                                   |

| J13       | Secondary IDE                                       |

| J14       | Floppy Disk Drive Connector                         |

| J15       | Primary IDE                                         |

| J16       | Front Panel Header                                  |

| J17       | ITP                                                 |

| J18       | Ethernet 1 (Optional 10/100/1000) RJ45              |

| J19       | USB Header (Ports 0 & 1)                            |

| J20       | USB Header (Ports 4 & 5)                            |

| J21       | USB Header (Ports 2 & 3)                            |

| J22       | LPT - Parallel                                      |

| J23       | ATX PS Control                                      |

| J24       | Ethernet 2 (Optional 10/100 or 10/100/1000)<br>RJ45 |

| J25       | JTAG                                                |

| J26       | Keyboard/Mouse Combined PS/2                        |

| J27       | CPU Fan                                             |

| J28       | Audio – CD In Header                                |

| J29       | Audio – Line In Header                              |

| Connector | Description                                         |

|-----------|-----------------------------------------------------|

| J30       | VGA DB15                                            |

| J31       | Buzzer – Alt. Speaker Header                        |

| J32       | Audio – Line Out/Microphone In Header               |

| J33       | External RTC/CMOS Battery – Close to Battery Holder |

| J34       | Mini-PCI Slot – Back side of the board              |

| S1        | PICMIG ISA Edge                                     |

| S2        | PICMIG PCI Edge                                     |

| U18       | BIOS Socket                                         |

| U21       | CPU Socket                                          |

## **User's Notes:**

## **User's Notes:**

## Chapter 2

## AMIBIOS8 Setup

Your Captor M features American Megatrends AMIBIOS8. The system configuration parameters are set via the BIOS setup. Since the BIOS Setup resides in the ROM BIOS, it is available each time the computer is turned on.

American Megatrends's AMIBIOS8 brand BIOS (Basic Input/Output System) pre-boot firmware is the industry's standard product used by most designers of X86 computer equipment in the world today. Its superior combination of configurability and functionality enables it to satisfy the most demanding ROM BIOS needs for x86 designers. Its modular architecture and high degree of configurability make it the most flexible BIOS in the world.

When your platform is powered on, AMIBIOS8 tests and initializes the hardware and programs the chipset and other peripheral components. During this time, Power On Self Test (POST) progress codes are written by the system BIOS to I/O port 80h, allowing the user to monitor the progress with a special monitor. Appendix B lists the POST codes and their meanings.

During early POST, no video is available to display error messages should a critical error be encountered; therefore, POST uses beeps on the speaker to indicate the failure of a critical system component during this time. Consult Appendix B for a list of Beep codes used by the BIOS.

## Starting BIOS Setup

AMIBIOS has been integrated into many motherboards for over a decade. In the past, people often referred to the AMIBIOS setup menu as BIOS, BIOS setup, or CMOS setup.

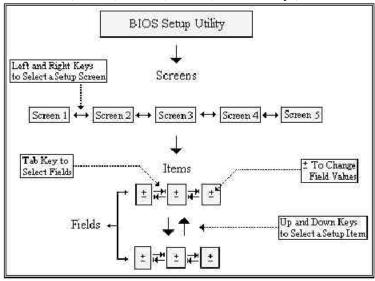

American Megatrends refers to this setup as ezPORT. Specifically, it is the name of the AMIBIOS BIOS setup utility. This chapter describes the basic navigation of the ezPORT setup screens.

To enter the ezPORT setup screens, follow the steps below:

- 1 Power on the motherboard

- 2 Press the <Delete> key on your keyboard when you see the following text prompt:

Press DEL to run Setup

3 After you press the <Delete> key, the ezPORT main BIOS setup menu displays. You can access the other setup screens from the main BIOS setup menu, such as the Chipset and PCI/PnP menus.

### BIOS Setup Main Menu

The ezPORT main BIOS setup menu is the first screen that you can navigate. Each main BIOS setup menu option is described in the Chapter 2.

The Main BIOS setup menu screen has two main frames. The left frame displays all the options that can be configured. "Grayed-out" options cannot be configured. Options in blue can be.

The right frame displays the key legend. Above the key legend is an area reserved for a text message. When an option is selected in the left frame, it is highlighted in white. Often a text message will accompany it.

The ezPORT BIOS setup/utility uses a key-based navigation system called hot keys. Most of the ezPORT BIOS setup utility hot keys can be used at any time during the setup navigation process. These keys include <F1>, <F10>, <Enter>, <ESC>, <Arrow> keys, and so on.

The <F8> key on your keyboard is the Fail-Safe key. It is not displayed on the ezPORT key legend by default. To set the Fail-Safe settings of the BIOS, press the <F8> key on your keyboard. It is located on the upper row of a standard 101 keyboard. The Fail-Safe settings allow the motherboard to boot up with the least amount of options set. This can lessen the probability of conflicting settings.

| Hot Key       | Description                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------|

| → Left/Right  | The Left and Right <arrow> keys allow you to select an ezPORT setup screen.</arrow>               |

|               |                                                                                                   |

|               | For example: Main screen, Advanced screen, Chipset screen, and so on.                             |

| ↑↓ Up/Down    | The Up and Down <arrow> keys allow you to select an ezPORT setup item or sub-screen.</arrow>      |

| +- Plus/Minus | The Plus and Minus <arrow> keys allow you to change the field value of a particular setup</arrow> |

|               | item.                                                                                             |

|               |                                                                                                   |

|               | For example: Date and Time.                                                                       |

| Tab           | The <tab> key allows you to select ezPORT setup fields.</tab>                                     |

| Hot Key | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F1      | The <f1> key allows you to display the General Help screen.  Press the <f1> key to open the General Help screen.</f1></f1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | General Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         | ←→ Select Screen     ←→ Change Screen     ←→ Change Screen     ←→ Change Screen     ←→ Change Screen     ←→ PGDN Next Page     ←→ PGUP Previous Page     ←→ PGUP Previou |

|         | .[ok].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ESC ESC | The <fi0> key allows you to save any changes you have made and exit ezPORT Setup. Press the <fi0> key to save your changes. The following screen will appear:  Save configuration changes and exit now?</fi0></fi0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | [Ok] [Cancel]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | Press the <enter> key to save the configuration and exit. You can also use the <arrow> key to select Cancel and then press the <enter> key to abort this function and return to the previous screen.  The <esc> key allows you to discard any changes you have made and exit the ezPORT Setup Press the <esc> key to exit the ezPORT setup without saving your changes. The following</esc></esc></enter></arrow></enter>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | screen will appear:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | Discard changes and exit setup now?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | [Ok] [Cancel]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Enter   | Press the <enter> key to discard changes and exit. You can also use the <arrow> key to selec  Cancel and then press the <enter> key to abort this function and return to the previous screen.  The <enter> key allows you to display or change the setup option listed for a particular setup.</enter></enter></arrow></enter>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## **Main Setup**

When you first enter the ezPORT Setup Utility, you will enter the Main setup screen. You can always return to the Main setup screen by selecting the *Main* tab. There are two Main Setup options.

### System Time/System Date

Use this option to change the system time and date. Highlight *System Time* or *System Date* using the <Arrow> keys. Enter new values through the keyboard. Press the <Tab> key or the <Arrow> keys to move between fields. The date must be entered in MM/DD/YY format. The time is entered in HH:MM:SS format.

**Note:** The time is in 24-hour format. For example, 5:30 A.M. appears as 05:30:00, and 5:30 P.M. as 17:30:00.

## **Advanced BIOS Setup**

Select the *Advanced* tab from the ezPORT setup screen to enter the Advanced BIOS Setup screen. You can select any of the items in the left frame of the screen, such as SuperIO Configuration, to go to the sub menu for that item. You can display an Advanced BIOS Setup option by highlighting it using the <Arrow> keys. All Advanced BIOS Setup options are described in this section.

### **CPU CONFIGURATION SCREEN**

### Information about the CPU.

## Intel SpeedStep Technology

You can select the behavior of the SpeedStep feature prior to the OS boot. The Optimal and Fail-Safe default setting is *Auto*.

Max Performance. Battery Optimized. Reversed. Auto. Disabled.

### IDE CONFIGURATION SCREEN

## IDE Configuration Settings

You can use this screen to select options for the IDE Configuration Settings. Use the up and down <Arrow> keys to select an item. Use the <Plus> and <Minus> keys to change the value of the selected option. A description of the selected item appears on the right side of the screen.

### Onboard PCI IDE Controller

This item specifies the IDE channels used by the onboard PCI IDE controller. The settings are *Disabled, Primary, Secondary,* or *Both.* The Optimal and Fail-Safe default setting is *Both.*

**Disabled** Set this value to prevent the computer system from using the onboard IDE controller.

**Primary** Set this value to allow the computer system to detect only the Primary IDE channel. This includes both the Primary Master and the Primary Slave.

**Secondary** Set this value to allow the computer system to detect only the Secondary IDE channel. This includes both the Secondary Master and the Secondary Slave.

**Both** Set this value to allow the computer system to detect the Primary and Secondary IDE channels.

This includes both the Primary Master, Primary Slave, Secondary Master, and Secondary Slave. This is the default setting.

## Primary IDE Master, Primary IDE Slave, Secondary IDE Master, Secondary IDE Slave

Select one of the hard disk drives to configure it. Press <Enter> to access the sub menu. The options on the sub menu are described in the following sections.

#### Hard disk drive Write Protect

Set this option to protect the hard disk drive from being overwritten. The Optimal and Fail-Safe default setting is *Disabled*.

**Disabled** Set this value to allow the hard disk drive to be used normally. Read, write, and erase functions can be performed to the hard disk drive. This is the default setting.

Enabled Set this value to prevent the hard disk drive from being erased

### IDE Detect Time Out (Seconds)

Set this option to stop the AMIBIOS from searching for IDE devices within the specified number of seconds. Basically, this allows you to fine-tune the settings to allow for faster boot times. Adjust this setting until a suitable timing that can detect all IDE disk drives attached is found

The Optimal and Fail-Safe default setting is 35.

- **0** This value is the best setting to use if the onboard IDE controllers are set to a specific IDE disk drive in the AMIBIOS.

- **5** Set this value to stop the AMIBIOS from searching the IDE bus for IDE disk drives in five seconds. A large majority of ultra ATA hard disk drives can be detected well within five seconds.

- **10** Set this value to stop the AMIBIOS from searching the IDE bus for IDE disk drives in 10 seconds.

**15** Set this value to stop the AMIBIOS from searching the IDE bus for IDE disk drives in 15 seconds.

**20** Set this value to stop the AMIBIOS from searching the IDE bus for IDE disk drives in 20 seconds.

**25** Set this value to stop the AMIBIOS from searching the IDE bus for IDE disk drives in 25 seconds.

**30** Set this value to stop the AMIBIOS from searching the IDE bus for IDE disk drives in 30 seconds.

**35** *35* is the default value. It is the recommended setting when all IDE connectors are set to *AUTO* in the AMIBIOS setting.

*Note:* Different IDE disk drives take longer for the BIOS to locate than others do.

### ATA (PI) 80 pin Cable Detection

Set this option to select the method used to detect the ATA (PI) 80 pin cable. The Optimal and Fail-Safe setting is *Host & Device*.

**Host & Device** Set this value to use both the motherboard onboard IDE controller and IDE disk drive to detect the type of IDE cable used. This is the default setting.

**Host** Set this value to use motherboard onboard IDE controller to detect the type of IDE cable used.

**Device** Set this value to use IDE disk drive to detect the type of IDE cable used.

The use of an 80-conductor ATA cable is mandatory for running Ultra ATA/66 and Ultra ATA/100 IDE hard disk drives. The standard 40-conductor ATA cable cannot handle the higher speeds.

80-conductor ATA cable is plug compatible with the standard 40-conductor ATA cable. Because of this, the system must determine the presence of the correct cable. This detection is achieved by having a break in one of the lines on the 80-conductor ATA cable that is normally an unbroken connection in the standard 40-conductor ATA cable. It is this break that is used to make this determination. The AMIBIOS can instruct the drive to run at the correct speed for the cable type detected.

### PRIMARY AND SECONDARY IDE MASTER AND SLAVE SUB-MENU

### Primary and Secondary IDE Master and Slave Settings

From the IDE Configuration screen, press <Enter> to access the sub menu for the primary and secondary IDE master and slave drives. Use this screen to select options for the Primary and Secondary IDE drives. Use the up and down <Arrow> keys to select an item. Use the <Plus> and <Minus> keys to change the value of the selected option. The settings are described on the following pages.

#### Drive Parameters

The "grayed-out" items in the left frame are the IDE disk drive parameters taken from the firmware of the IDE disk drive selected. The drive parameters listed are as follows:

Device Type of device, such as Hard disk drive.

Vendor Manufacturer of the device.

Size The size of the device.

**LBA Mode** LBA (Logical Block Addressing) is a method of addressing data on a disk drive. Your AMIBIOS is already equipped with 48-bit LBA mode addressing.

**Block Mode** Block mode boosts IDE drive performance by increasing the amount of data transferred. Only 512 bytes of data can be transferred per interrupt if block mode is not used. Block mode allows transfers of up to 64 KB per interrupt.

**PIO Mode** IDE PIO mode programs timing cycles between the IDE drive and the programmable IDE controller. As the PIO mode increases, the cycle time decreases.

**Async DMA** This indicates the highest Asynchronous DMA Mode that is supported.

**Ultra DMA** This indicates the highest Synchronous DMA Mode that is supported.

**S.M.A.R.T.** Self-Monitoring Analysis and Reporting Technology protocol used by IDE drives of some manufacturers to predict drive failures.

### Type

This option sets the type of device that the AMIBIOS attempts to boot from after the Power-On Self-Test (POST) has completed. The Optimal and Fail-Safe default setting is *Auto*.

**Not Installed** Set this value to prevent the BIOS from searching for an IDE disk drive on the specified channel.

**Auto** Set this value to allow the BIOS auto detect the IDE disk drive type attached to the specified channel. This setting should be used if an IDE hard disk drive is attached to the specified channel. This is the default setting.

**CDROM** This option specifies that an IDE CD-ROM drive is attached to the specified IDE channel. The BIOS will not attempt to search for other types of IDE disk drives on the specified channel.

**ARMD** This option specifies an ATAPI Removable Media Device. This includes, but is not limited to:

udes, but is not iiiiii

- ZIP

- LS-120

- MO

### LBA/Large Mode

LBA (Logical Block Addressing) is a method of addressing data on a disk drive. The Optimal and Fail-Safe default setting is *Auto*.

*Note:* Your AMIBIOS is equipped with 48-bit LBA mode addressing for drive capacities over 137 GB.

**Disabled** Set this value to prevent the BIOS from using Large Block Addressing mode control on the specified channel.

**Auto** Set this value to allow the BIOS to auto detect the Large Block Addressing mode control on the specified channel. This is the default setting.

### Block (Multi-Sector Transfer)

This option sets the block mode multi sector transfers option. The Optimal and Fail-Safe default setting is *Auto*.

**Disabled** Set this value to prevent the BIOS from using Multi-Sector Transfer on the specified channel. The data to and from the device will occur one sector at a time.

**Auto** Set this value to allow the BIOS to auto detect device support for Multi-Sector Transfers on the specified channel. If supported, Set this value to allow the BIOS to auto detect the number of sectors per block for transfer from the hard disk drive to the memory. The data transfer to and from the device will occur multiple sectors at a time. This is the default setting.

#### PIO Mode

IDE PIO (Programmable I/O) mode programs timing cycles between the IDE drive and the programmable IDE controller. As the PIO mode increases, the cycle time decreases. The Optimal and Fail-Safe default setting is *Auto*.

**Auto** Set this value to allow the BIOS to auto detect the PIO mode. Use this value if the IDE disk drive support cannot be determined. This is the default setting.

- **0** Set this value to allow the BIOS to use PIO mode 0. It has a data transfer rate of 3.3 MBs.

- 1 Set this value to allow the BIOS to use PIO mode 1. It has a data transfer rate of 5.2 MBs.

- **2** Set this value to allow the BIOS to use PIO mode 2. It has a data transfer rate of 8.3 MBs.

- **3** Set this value to allow the BIOS to use PIO mode 3. It has a data transfer rate of 11.1 MBs.

- 4 Set this value to allow the BIOS to use PIO mode 4. It has a data transfer rate of 16.6 MBs. This setting generally works with all hard disk drives manufactured after 1999. For other disk drive, such as IDE CD-ROM drives, check the specifications of the drive.

#### DMA Mode

This setting allows you to adjust the DMA mode options. The Optimal and Fail-Safe default setting is *Auto*.

**Auto** Set this value to allow the BIOS to auto detect the DMA mode. Use this value if the IDE disk drive support cannot be determined. This is the default setting.

**SWDMA0** Set this value to allow the BIOS to use Single Word DMA mode 0. It has a data transfer rate of 2.1 MBs.

**SWDMA1** Set this value to allow the BIOS to use Single Word DMA mode 1. It has a data transfer rate of 4.2 MBs.

**SWDMA2** Set this value to allow the BIOS to use Single Word DMA mode 2. It has a data transfer rate of 8.3 MBs.

**MWDMA0** Set this value to allow the BIOS to use Multi Word DMA mode 0. It has a data transfer rate of 4.2 MBs.

**MWDMA1** Set this value to allow the BIOS to use Multi Word DMA mode 1. It has a data transfer rate of 13.3 MBs.

**MWDMA2** Set this value to allow the BIOS to use Multi Word DMA mode 2. It has a data transfer rate of 16.6 MBs.

**UDMA0** Set this value to allow the BIOS to use Ultra DMA mode 0. It has a data transfer rate of 16.6 MBs. It has the same transfer rate as PIO mode 4 and Multi Word DMA mode 2.

**UDMA1** Set this value to allow the BIOS to use Ultra DMA mode 1. It has a data transfer rate of 25 MBs.

**UDMA2** Set this value to allow the BIOS to use Ultra DMA mode 2. It has a data transfer rate of 33.3 MBs

**UDMA3** Set this value to allow the BIOS to use Ultra DMA mode 3. It has a data transfer rate of 44.4 MBs. To use this mode, it is required that an 80-conductor ATA cable is used.

**UDMA4** Set this value to allow the BIOS to use Ultra DMA mode 4. It has a data transfer rate of 66.6 MBs. To use this mode, it is required that an 80-conductor ATA cable is used.

**UDMA5** Set this value to allow the BIOS to use Ultra DMA mode 5. It has a data transfer rate of 99.9 MBs. To use this mode, it is required that an 80-conductor ATA cable is used.

### S.M.A.R.T. for Hard disk drives

Self-Monitoring Analysis and Reporting Technology (SMART) feature can help predict impending drive failures. The Optimal and Fail-Safe default setting is *Auto*.

**Auto** Set this value to allow the BIOS to auto detect hard disk drive support. Use this setting if the IDE disk drive support cannot be determined. This is the default setting.

**Disabled** Set this value to prevent the BIOS from using the SMART feature.

**Enabled** Set this value to allow the BIOS to use the SMART feature on support hard disk drives.

### 32Bit Data Transfer

This option sets the 32-bit data transfer option. The Optimal and Fail-Safe default setting is *Enabled*.

**Disabled** Set this value to prevent the BIOS from using 32-bit data transfers.

**Enabled** Set this value to allow the BIOS to use 32-bit data transfers on support hard disk drives. This is the default setting.

### **ARMD Emulation Type**

ATAPI Removable Media Device (ARMD) is a device that uses removable media, such as the LS120, MO (Magneto-Optical), or Iomega Zip drives. If you want to boot up from media on an ARMD, it is required that you emulate boot up from a floppy or hard disk drive. This is especially necessary when trying to boot to DOS. You can select the type of emulation used if you are booting from such a device. The Optimal and Fail-Safe default setting is *Auto*.

**Auto** Set this value to allow the BIOS to automatically set the emulation used by ARMD. This is the default setting.

**Floppy** Set this value for ARMD to emulate a floppy drive during boot up.

**Hard disk** drive Set this value for ARMD to emulate a hard disk drive during boot up.

### FLOPPY CONFIGURATION SCREEN

### Floppy Configuration Settings

You can use this screen to specify options for the Floppy Configuration Settings. Use the up and down <Arrow> keys to select an item. Use the <Plus> and <Minus> keys to change the value of the selected option.

### Floppy Drive A: and B:

Move the cursor to these fields via up and down <arrow> keys. Select the floppy type. The Optimal setting for floppy drive A: is 1.44 MB 3½". The Fail-Safe setting for floppy drive A: is 1.44 MB 3½". The Optimal setting for floppy drive B: is Disabled. The Fail- Safe setting for floppy drive B: is Disabled.

**Disabled** Set this value to prevent the use of the selected floppy disk drive channel. This option should be set if no floppy disk drive is installed on the specified channel. This is the default setting for *Floppy Drive B*.

360 KB 5  $^{1}$ /4 " Set this value if the floppy disk drive attached to the corresponding channel is a 360 KB 5  $^{1}$ /4 " floppy disk drive.

1.2 MB 5  $\frac{1}{4}$  " Set this value if the floppy disk drive attached to the corresponding channel is a 1.2 MB 5 $\frac{1}{4}$  " floppy disk drive.

720 KB 3  $\frac{1}{2}$  " Set this value if the floppy disk drive attached to the corresponding channel is a 720 KB  $3\frac{1}{2}$  " floppy disk drive.

**1.44 MB 3**  $\frac{1}{2}$  "Set this value if the floppy disk drive attached to the corresponding channel is a 1.44 MB  $\frac{3}{2}$  " floppy disk drive. This is the default setting for *Floppy Drive A*.

### SUPER IO CONFIGURATION SCREEN

### SuperIO Configuration Screen

You can use this screen to select options for the Super I/O settings. Use the up and down <Arrow> keys to select an item. Use the <Plus> and <Minus> keys to change the value of the selected option.

### OnBoard Floppy Controller

Set this option to Enabled to enable the floppy drive controller on the motherboard. The settings are Enabled and Disabled. The default setting is Enabled.

### Serial Port1 Address

This option specifies the base I/O port address and Interrupt Request address of serial port 1. The Optimal setting is *3F8/IRQ4*. The Fail-Safe default setting is *Disabled*.

**Disabled** Set this value to prevent the serial port from accessing any system resources. When this option is set to *Disabled*, the serial port physically becomes unavailable.

**3F8/IRQ4** Set this value to allow the serial port to use 3F8 as its I/O port address and IRQ 4 for the interrupt address. This is the default setting. The majority of serial port 1 or COM1 ports on computer systems use IRQ4 and I/O Port 3F8 as the standard setting. The most common serial device connected to this port is a mouse. If the system will not use a serial device, it is best to set this port to *Disabled*.

**2F8/IRQ3** Set this value to allow the serial port to use 2F8 as its I/O port address and IRQ 3 for the interrupt address. If the system will not use a serial device, it is best to set this port to *Disabled*.

**3E8/IRQ4** Set this value to allow the serial port to use 3E8 as its I/O port address and IRQ 4 for the interrupt address. If the system will not use a serial device, it is best to set this port to *Disabled*.

**2E8/IRQ3** Set this value to allow the serial port to use 2E8 as its I/O port address and IRQ 3 for the interrupt address. If the system will not use a serial device, it is best to set this port to *Disabled*.

### Serial Port2 Address

This option specifies the base I/O port address and Interrupt Request address of serial port 2. The Optimal setting is *2F8/IRQ3*. The Fail-Safe setting is *Disabled*.

**Disabled** Set this value to prevent the serial port from accessing any system resources. When this option is set to *Disabled*, the serial port physically becomes unavailable.

**3F8/IRQ4** Set this value to allow the serial port to use 3F8 as its I/O port address and IRQ 4 for the interrupt address. If the system will not use a serial device, it is best to set this port to Disabled.

**2F8/IRQ3** Set this value to allow the serial port to use 2F8 as its I/O port address and IRQ 3 for the interrupt address. This is the default

setting. The majority of serial port 2 or COM2 ports on computer systems use IRQ3 and I/O Port 2F8 as the standard setting. The most common serial device connected to this port is an external modem. If the system will not use an external modem, set this port to *Disabled*.

**Note:** Most internal modems require the use of the second COM port and use 3F8 as its I/O port address and IRQ 4 for its interrupt address. This requires that the Serial Port2 Address be set to *Disabled* or another base I/O port address and Interrupt Request address.

**3E8/IRQ4** Set this value to allow the serial port to use 3E8 as its I/O port address and IRQ 4 for the interrupt address. If the system will not use a serial device, it is best to set this port to Disabled.

**2E8/IRQ3** Set this value to allow the serial port to use 2E8 as its I/O port address and IRQ 3 for the interrupt address. If the system will not use a serial device, it is best to set this port to *Disabled*.

### Serial Port2 Mode

This option allows installation of an Infra-red device by the Serial Port. The settings are Normal (*default*), IRDA and ASK IR.

### Infra-Red Transmission Mode

The settings are Full Duplex (*default*) or Half Duplex.

### Receiver/Transmitter Polarity

Sets polarity for IR modes.

### Parallel Port Address

This option specifies the I/O address used by the parallel port. The Optimal setting is 378. The Fail-Safe setting is *Disabled*.

**Disabled** Set this value to prevent the parallel port from accessing any system resources. When the value of this option is set to *Disabled*, the printer port becomes unavailable.

**378** Set this value to allow the parallel port to use 378 as its I/O port address. This is the default setting. The majority of parallel ports on computer systems use IRQ7 and I/O Port 378H as the standard setting.

**278** Set this value to allow the parallel port to use 278 as its I/O port address

**3BC** Set this value to allow the parallel port to use 3BC as its I/O port address.

### Parallel Port Mode