# SB686BX Series Single Board Computer Manual

MANUAL NUMBER: 00431-248-1C

CE

# Errata Sheet

#### November 1999

#### Manual Numbers:

00431-220-xx, SB586T Series Single Board Computer 00431-244-xx, P2BX/P3BX Series Feature Card 00431-248-xx, SB686BX Series Single Board Computer

The boards listed in the SB586T Manual have been renumbered as follows:

| SB586T replaces -  | SB586T100<br>SB586T133<br>SB586T166<br>SB586T166X<br>SB586T200<br>SB586T200X<br>SB586T233X<br>SB586T233X<br>SB586T266K<br>SB586T300K | SB586TS replaces -  | SB586TS100<br>SB586TS133<br>SB586TS166<br>SB586TS166X<br>SB586TS200<br>SB586TS200X<br>SB586TS200X<br>SB586TS233X<br>SB586TS266K<br>SB586TS300K | SB586TS2V replaces - | SB586TS2V100<br>SB586TS2V133<br>SB586TS2V166<br>SB586TS2V200X<br>SB586TS2V200X<br>SB586TS2V233X<br>SB586TS2V233X<br>SB586TS2V2300K |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| SB586TT replaces - | SB586TT100<br>SB586TT133<br>SB586TT166X<br>SB586TT200X<br>SB586TT233X<br>SB586TT236K<br>SB586TT300K                                  | SB586T2V replaces - | SB586T2V100<br>SB586T2V133<br>SB586T2V166<br>SB586T2V166X<br>SB586T2V200X<br>SB586T2V233X<br>SB586T2V236K<br>SB586T2V300K                      | SB586TU replaces -   | SB586TU100<br>SB586TU133<br>SB586TU166<br>SB586TU166X<br>SB586TU200X<br>SB586TU233X<br>SB586TU266K<br>SB586TU300K                  |

**Note:** Processors are now identified separately from the boards. Processors are supported up to Intel Pentium 233MHz and 300MHz AMD K6-2.

The boards listed in the P2BX/P3BX Manual have been renumbered as follows:

| P3BXSUT replaces - | P3BXSVT500<br>P3BXSVT450<br>P2BXSVT450<br>P2BXSVT400<br>P2BXSVT350 | P3BXVT replaces - | P3BXVT500<br>P3BXVT450<br>P2BXVT450<br>P2BXVT400<br>P2BXVT350 | P3BXST replaces - | P3BXST500<br>P3BXST450<br>P2BXST450<br>P2BXST400<br>P2BXST350 |

|--------------------|--------------------------------------------------------------------|-------------------|---------------------------------------------------------------|-------------------|---------------------------------------------------------------|

| P3BX replaces -    | P3BX500<br>P3BX450<br>P2BX450                                      |                   |                                                               |                   |                                                               |

Note: Processors are now identified separately from the boards. Processors are supported up to 600MHz.

The boards listed in the SB686BX Manual have been renumbered as follows:

P2BX400 P2BX350

SB686XVC366

| SB686BX replaces - | SB686BX3500<br>SB686BX3450<br>SB686BX450<br>SB686BX400<br>SB686BX350 | SB686BXV replaces - | SB686BXV3500<br>SB686BXV3450<br>SB686BXV450<br>SB686BXV400<br>SB686BXV350 |

|--------------------|----------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|

| Obsoleted numbers  | - SB686XC400<br>SB686XC366<br>SB686XVC400                            |                     |                                                                           |

Note: Processors are now identified separately from the boards. Processors are supported up to 600MHz.

# Errata Sheet

# February 2000

| R | 4   |     | N  |    | ber: |

|---|-----|-----|----|----|------|

| r | чан | lua | IΝ | шш | Det. |

00431-248-xx, SB686BX Series Single Board Computer Manual

■ Please refer to the ICS Advent Web site (www.icsadvent.com) for available processor speeds. Additional processor speeds may be available.

# **FOREWORD**

This product manual provides information to install, operate and or program the referenced product(s) manufactured or distributed by ICS Advent. The following pages contain information regarding the warranty and repair policies.

Check our Web site (http://www.icsadvent.com/techsupport) for technical information, manual, and BIOS updates. Technical assistance is also available at: 800-480-0044 (U.S. and Canada) or 858-677-0877 (international).

Manual errors, omissions, bugs, and/or comments: A Customer Comments section is included at the end of this manual. If you experience any problems with the manual or just want to give us some feedback, please review the information in this section. It will tell you how to easily access our web site and provide immediate feedback online.

The information in this document is provided for *reference* only. ICS Advent does not assume any liability arising out of the application or use of the information or products described herein. This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of ICS Advent, nor the rights of others.

Copyright © 1999 by ICS Advent, a California Corporation, 6260 Sequence Drive, San Diego, CA 92121-4371. ICS Advent is a Registered Trademark of ICS Advent. All trademarks and registered trademarks are the property of their respective owners. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

# Guarantee

A thirty day money-back guarantee is provided on all **standard** products sold. **Special order products** are covered by our Limited Warranty, <u>however they may not be returned for refund or credit</u>. *EPROMs, RAM, Flash EPROMs or other forms of solid electronic media are not returnable for credit - but for replacement only. Extended Warranty available. Consult factory.*

#### Refunds

In order to receive a refund on a product purchase price, the product must not have been damaged by the customer or by the common carrier chosen by the customer to return the goods, and the product must be returned complete (meaning all manuals, software, cables, etc.) within 30 days of receipt and in as-new and resalable condition. The **Return Procedure** must be followed to assure prompt refund.

# Restocking Charges

Product returned *after* 30 days, and *before* 90 days, of the purchase will be subject to a **minimum** 20% restocking charge and any charges for damaged or missing parts.

Products not returned within 90 days of purchase, or products which are not in as-new and resaleable condition, are not eligible for credit return and will be returned to the customer.

# **Limited Warranty**

Effective April 1, 1998, all products carry a two-year limited warranty with the exception of the "Performance Series" I/O products, which are warranted to the original purchaser for as long as they own the product, subject to all other conditions below, including those regarding neglect, misuse and acts of God. Within one year of purchase, ICS Advent will repair or replace, at our option, any defective product. At any time after one year, we will repair or replace, at our option, any defective "Performance Series" I/O product sold. This does not include products damaged in shipment, or damaged through customer neglect or misuse. ICS Advent will service the warranty for all standard catalog products for the first year from the date of shipment. After the second year, for products not manufactured by ICS Advent, the remainder of the manufacturer's warranty, if any, will be serviced by the manufacturer directly.

The **Return Procedure** must be followed to assure repair or replacement. ICS Advent will normally return your replacement or repaired item via Second Day Air. *Overnight delivery or delivery via other carriers is available at additional charge.*

The limited warranty is void if the product has been subjected to alteration, neglect, misuse, or abuse; if any repairs have been attempted by anyone other than ICS Advent or its authorized agent; or if the failure is caused by accident, acts of God, or other causes beyond the control of ICS Advent or the manufacturer. Neglect, misuse, and abuse shall include any installation, operation, or maintenance of the product other than in accordance with the owners' manual.

No agent, dealer, distributor, service company, or other party is authorized to change, modify, or extend the terms of this Limited Warranty in any manner whatsoever. ICS Advent reserves the right to make changes or improvements in any product without incurring any obligation to similarly alter products previously purchased.

Shipments not in compliance with this Guarantee and Limited Warranty Return Policy will not be accepted by ICS Advent.

## Return Procedure

For any Limited Warranty or Guarantee return, please contact ICS Advent's Customer Service at **800-480-0044** (U.S. and Canada) or **858-677-0877** (international) and obtain a Return Material Authorization (RMA) Number. All product(s) returned to ICS Advent for service or credit **must** be accompanied by a Return Material Authorization (RMA) Number. Freight on all returned items **must** be prepaid by the customer who is responsible for any loss or damage caused by common carrier in transit. Returns for Warranty **must** include a Failure Report for each unit, by serial number(s), as well as a copy of the original invoice showing date of purchase.

To reduce risk of damage, returns of product must be in an ICS Advent shipping container. If the original container has been lost or damaged, new shipping containers may be obtained from ICS Advent Customer Service at a nominal cost.

# **Limitation of Liability**

In no event shall ICS Advent be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental, or consequential damages in connection with or arising out of the performance or use of any product furnished hereunder. ICS Advent liability shall in no event exceed the purchase price of the product purchased hereunder. The foregoing limitation of liability shall be equally applicable to any service provided by ICS Advent or its authorized agent.

Some Sales Items and Customized Systems are **not** subject to the guarantee and limited warranty. However in these instances, any deviations will be disclosed prior to sales and noted in the original invoice. ICS Advent reserves the right to refuse returns or credits on software or special order items.

# **Advisories**

Three types of advisories are used throughout the manual to stress important points or warn of potential hazards to the user or the system. They are the *Note*, the *Caution*, and the *Warning*. Following is an example of each type of advisory:

**Note:** The note is used to present information which may provide special instruction or extra information which may help to simplify the use of the product.

#### CAUTION!

A Caution is used to alert you of a situation which if ignored may cause injury or damage equipment.

#### WARNING!

A Warning is used to alert you of a situation which if ignored will cause serious injury.

Cautions and Warnings are accented with triangular symbols. The excalmation symbol is used in all cautions and warnings to help alert you to the important instructions. The lightning flash symbol is used on the left hand side of a caution or a warning if the advisory relates to the presence of voltage which may be of sufficient magnitude to cause electrical shock.

Use caution when servicing any electrical component. We have tried to identify the areas which may pose a Caution or Warning condition in this manual; however, ICS Advent does not claim to have covered all situations which might require the use of a Caution or Warning.

You must refer to the documentation for any component you install into a computer system to insure proper precautions and procedures are followed.

# **Table of Contents**

| FOREWORD                                            | iii |

|-----------------------------------------------------|-----|

| Guarantee                                           | iv  |

| Limited Warranty                                    | iv  |

| Return Procedure                                    |     |

| Limitation of Liability                             |     |

| Advisories                                          |     |

|                                                     |     |

| Chapter 1: Introduction                             | 1-1 |

| General                                             | 1-1 |

| SB686BX and SB686BXC                                | 1-2 |

| SB686BXV and SB686BXVC                              | 1-2 |

| Year 2000 Compliance                                | 1-2 |

| Models Covered by this Manual                       | 1-3 |

| Chapter 2: Specifications                           | 2.4 |

| Processors Supported                                |     |

| Processor Clock Frequency and Bus Speed             |     |

| Memory Capacity                                     |     |

| DIMM Support                                        |     |

| Memory Speed Required                               |     |

| BIOS                                                |     |

| Chip Set                                            |     |

| Graphics Controller (SB686BXV and SB686BXVC only)   |     |

| EIDE Disk Controller (dual port)                    |     |

| Floppy Diskette Controller (dual port)              |     |

| Serial Ports                                        |     |

| Parallel Port                                       |     |

| Keyboard, speaker, and reset port                   |     |

| PS/2 Mouse controller                               |     |

| Universal Serial Bus (USB)                          |     |

| Watchdog Timer                                      |     |

| Realtime Clock                                      |     |

| CMOS Battery                                        |     |

| Supported Operating Systems                         |     |

| Operating Environment                               |     |

| Storage Environment                                 |     |

| MTBF                                                |     |

| Current Requirements                                |     |

| Agency Approvals                                    |     |

| Locations of Major Components on the SB686BX Series |     |

| Chapter 3: Major Components                         | 3-1 |

|-----------------------------------------------------|-----|

| Features                                            | 3-1 |

| Bus Support                                         | 3-1 |

| Onboard Controllers                                 | 3-1 |

| Dual EIDE Disk Drive Controller (J4, J7)            | 3-1 |

| Dual Diskette Drive Controller (J5)                 | 3-1 |

| I/O Ports                                           | 3-1 |

| Serial Ports (J9, J16)                              | 3-1 |

| Enhanced Parallel Port (J8)                         | 3-2 |

| Watchdog Circuit (U28)-Not Shown                    | 3-2 |

| Universal Serial Bus (J12)                          | 3-2 |

| SB686BX Onboard Controllers (U9, U11)               | 3-2 |

| Main Memory (J1, J6)                                | 3-3 |

| Display Controller (U10)                            | 3-3 |

| Flash ROM (U30)                                     | 3-3 |

| Onboard PLD (J19)                                   | 3-4 |

| I/O Port Controller (U12)                           | 3-4 |

| Real-Time Clock, CMOS SRAM, and Battery             | 3-4 |

| Connectors                                          | 3-5 |

| Jumper Connectors                                   | 3-8 |

| Board Layout                                        | 3-9 |

| Observation to Insate Hedison and Oscifferentials   |     |

| Chapter 4: Installation and Configuration           |     |

| Installing the SDRAM DIMM Memory (J1, J6)           |     |

| Dual EIDE and Floppy Drive Connections (J4, J7, J5) |     |

| COM1 and COM2 Dual Serial Ports (J16,J9)            |     |

| Bus Speed (SW1)                                     |     |

| Watchdog Timer Configuration (J17)                  |     |

| Flash BIOS (JP4)                                    |     |

| CMOS Clear (JP2)                                    |     |

| Windows 95 Installation                             |     |

| USB Supplement                                      |     |

| OSR 2.1                                             |     |

| OSR 2.5                                             |     |

| Intel .INF Update                                   |     |

| SB686BX Series Current Requirements                 | 4-5 |

| Chapter 5: Maintenance and Troubleshooting          | 5-1 |

| FCC Compliance Statement for Class A Devices        |     |

| How to Remain CE Compliant                          |     |

| Troubleshooting                                     |     |

| Returns                                             |     |

| Appendix A: AMIBIOS                                      | A-1 |

|----------------------------------------------------------|-----|

| Appendix B: Watchdog Timer Code                          | B-1 |

| Declaration of Conformity                                |     |

| List of Figures                                          |     |

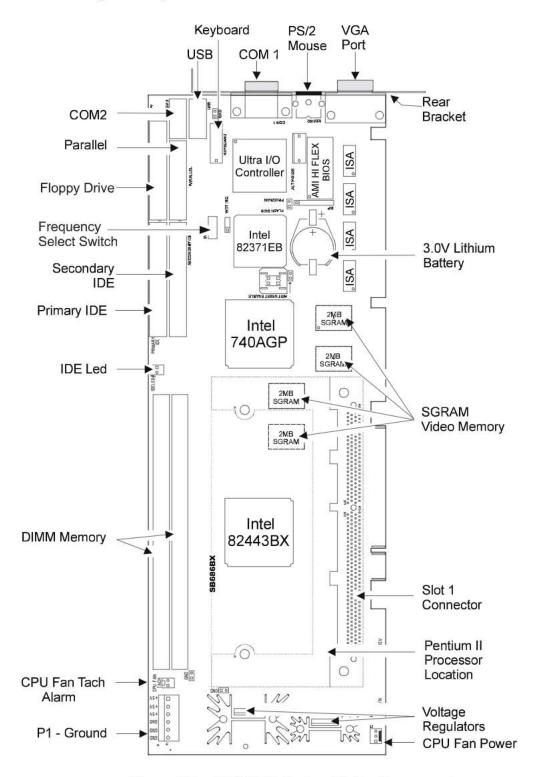

| Figure 2-1: SB686BXV Series Major Components             | 2-6 |

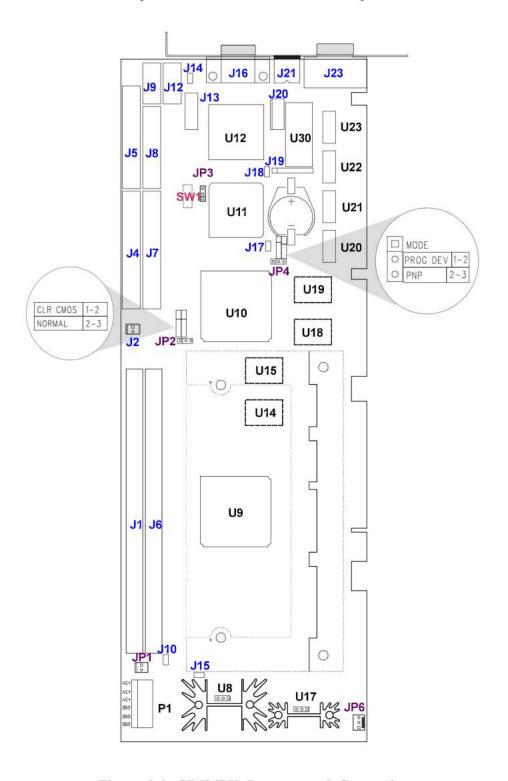

| Figure 3-1: SB686BXV Series Jumpers and Connections      | 3-9 |

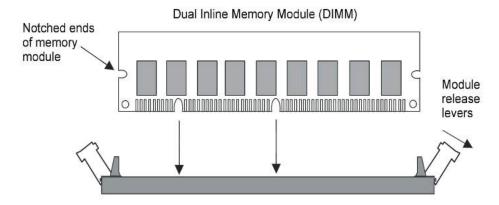

| Figure 4-1: DIMM Orientation                             |     |

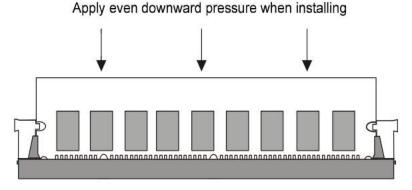

| Figure 4-2: DIMM Installation                            | 4-2 |

| Figure 4-3: SW1 Settings for 350MHz Pentium II Processor | 4-4 |

| List of Tables                                           |     |

| Table 2-1: 740 AGP Video Resolutions                     | 2-2 |

| Table 4-1: SW1 Settings                                  | 4-3 |

| Table 4-2: Power Matrix                                  | 4-6 |

| Table 4-3: Conductor Matrix                              | 4-6 |

|                                                          |     |

**Revision 1C**

July 1999

This page intentionally left blank

# **Chapter 1: Introduction**

This manual describes the SB686BX Series single board computers. A complete list of products covered by this manual appears at the end of this chapter. Chapter 1 provides general information. Chapter 2 contains specifications and dimensional drawings. Chapter 3 lists the connector pinouts and illustrates the board layout. Chapter 4 details component installation and switch settings. Chapter 5 describes maintenance and troubleshooting. Appendix A describes the BIOS and Appendix B provides sample code for the watchdog timer.

## General

The SB686BX is a full featured, industrialized, single board computer with a high-frequency Intel® Pentium III®, Pentium III®, or Celeron® processor that brings advanced CPU technology and processing power to the latest ISA/PCI (PICMG) applications and to older ISA systems. The 440BX AGP set built in to the single board computer is the most efficient and reliable way to upgrade existing ISA systems to Pentium II technology for both the performance PC market (Pentium III) and the basic PC market (Celeron).

The Pentium III, Pentium II, and Celeron processors use the PICMG form factor with a right angle Slot 1 Connector. The PICMG design contains two gold leaf edge connectors compatible with PCI and ISA connectors to allow all peripherals to interface with the processor. This lets the SB686BX take advantage of the high pin density and strict electromechanical criteria imposed on PCI and ISA connectors. The ISA bus is buffered using 64mA drivers to ensure reliable operation for backplanes with more than five ISA slots.

The SB686BX combines the many features needed for system operation into one compact single board computer, including Ultra/DMA IDE drive controllers, high-performance serial ports, enhanced parallel port, and the latest BIOS features. Additional enhancements to the SB686BX include two USB ports and a programmable watchdog timer. Two dual in-line memory module (DIMM) sockets support up to 512MB of synchronous DRAM (SDRAM) memory. An internal 64-bit second level (L2) cache supports 512k of memory. The L2 cache speed is half the CPU core frequency. The Celeron L2 cache equals 128k running at full CPU core.

The 440BX AGPset in the SB686BX incorporates the latest microprocessing technology from Intel to provide the increased bandwidth needed to operate your system bus at speeds up to 100MHz. (The 440BX AGPset uses one chipset for both 66MHz and 100MHz system designs in Pentium III, Pentium II and Celeron processors with speeds of 366MHz and higher.)

The 440BX AGPset is a two-chip set comprised of the Intel 82443BX (PAC) host bridge and the Intel 82371EB (PIIX4E) I/O subsystem. The 64-bit main memory interface in the PAC provides optimized support for SDRAM at 100 and 66/60MHz. The PAC also includes the 32-bit PCI bus interface, the AGP interface with 133MHz data transfer capability, and extensive data buffering for increased throughput and concurrent operations.

The PIIX4E is a PCI Rev 2.1 compliant PCI-ISA bridge that supports 3.3V and 5V 33MHz PCI operations. Like the PAC, the PIIX4E chip includes Desktop Power Management support, enhanced DMA controller and an integrated IDE controller with Ultra DMA/33 support. In addition, it provides USB host interface support for two USB ports and a System Management Bus (SMB) with support for DIMM Serial PD.

The SB686BXV single board computer is further enhanced by the Intel 740 Graphics Accelerator for the Accelerated Graphics Port (AGP) to deliver the most advanced graphics and video support available. The 740 delivers exceptional 2D capabilities and pipelined 3D images to maximize graphics performance. The dedicated video engines support video conferencing and other video applications.

#### SB686BX and SB686BXC

The SB686BX single board computer combines the high-frequency Pentium III or Pentium II processor with the exceptional bandwidth capability of the dual independent bus (DIB) and the 100MHz system bus to deliver the high performance needed for the most demanding system applications. By using the Intel 440BX AGPset, the SB686BX with a Pentium III or Pentium II processor can increase the bandwidth of the system bus from 66MHz to 100MHz to provide substantial improvements to system performance.

The SB686BXC series single board computer with a Celeron processor delivers the best performance in the basic PC. The Celeron processor combines the benefits of P6 architecture and Intel MMX technology to deliver the best balance of performance and price. The Celeron processor provides a maximum bus speed of 66 MHz.

#### SB686BXV and SB686BXVC

The SB686BXV and SB686BXVC single board computers have been enhanced with the Intel 740 Graphics Accelerator for the Accelerated Graphics Port (AGP). The 740 AGP provides the most advanced graphics and video support available. Detailed information about the 740 Graphics Accelerator is available at <a href="http://developer.intel.com/design/graphics/740">http://developer.intel.com/design/graphics/740</a>.

## Year 2000 Compliance

ICS Advent warrants that the SB686BX Series has been tested for Year 2000 compliance. The boards have been verified to "roll over" to the year 2000 properly and to indicate the proper date for the leap year. This warranty applies to the board components only and does not guarantee that improperly written application software will report the year correctly.

Page 1-2 Manual Number: 00431-248-1

# Models Covered by this Manual

The following models include the single board computer with a Pentium III processor:

```

SB686BX3500 – Pentium III processor, 500MHz, 100MHz CPU bus SB686BX3450 – Pentium III processor, 450MHz, 100MHz CPU bus

```

The following models include the single board computer with a Pentium II processor:

```

SB686BX450 – Pentium II processor, 450MHz, 100MHz CPU bus SB686BX400 – Pentium II processor, 400MHz, 100MHz CPU bus SB686BX350 – Pentium II processor, 350MHz, 100MHz CPU bus

```

The following models include the single board computer with a Celeron processor:

```

SB686BXC400 – Celeron Processor, 400MHz, 66MHz CPU bus

SB686BXC366 – Celeron Processor, 366MHz, 66MHz CPU bus

```

The following models include the single board computer with a Pentium III processor and Intel 740 AGP Graphics Accelerator with SVGA video:

```

SB686BXV3500 – Pentium III processor, 500MHz, 100MHz CPU bus SB686BXV3450 – Pentium III processor, 450MHz, 100MHz CPU bus

```

The following models include the single board computer with a Pentium II processor and Intel 740 AGP Graphics Accelorator with SVGA video:

```

SB686BXV450 – Pentium II processor, 450MHz, 100MHz CPU bus SB686BXV400 – Pentium II processor, 400MHz, 100MHz CPU bus SB686BXV350 – Pentium II processor, 350MHz, 100MHz CPU bus

```

The following models include the single board computer with a Celeron processor and Intel 740 AGP Graphics Accelerator:

```

SB686BXVC400 - Celeron Processor, 400MHz, 66MHz CPU bus SB686BXVC366 - Celeron Processor, 366MHz, 66MHz CPU bus

```

# **Chapter 2: Specifications**

This chapter provides the specifications and an illustration of the SB686BX Series single board computer. Unless indicated, the following specifications apply to all models in the SB686BX Series.

# **Processors Supported**

- Intel Pentium III with 512K L2 cache

- Intel Pentium II with 512K L2 cache

- Intel Celeron with 128K L2 cache

# Processor Clock Frequency and Bus Speed

- Pentium III 450MHz or 500MHz internal frequency and bus speed is 100MHz

- Pentium II 350MHz, 400MHz, or 450MHz internal frequency and bus speed is 100MHz

- Celeron 366MHz or 400MHz internal frequency and bus speed is 66MHz

## **Memory Capacity**

- 16MB minimum

- 256MB maximum (non-ECC)

- 512MB maximum (ECC)

# DIMM Support

- 2 banks, gold contacts, 168-pin

- Non-EC/EC/ECC compatible

#### Memory Speed Required

64/72-bit SDRAM (100 MHz)

## BIOS

- Hi-Flex Pentium AMIBIOS, Flash EPROM support, Plug-and-Play compatible

- 2Mb flash upgradeable supporting BIOS upgrade via software

- Full support for Year 2000 and leap-year date functions

#### Chip Set

- Intel 440BX AGPset

- 82443BX Host Bridge Controller (PCI/AGP)

- 82371EB PCI/ISA/IDE Accelerator (PIIX4E)

# Graphics Controller (SB686BXV and SB686BXVC only)

- Intel 740 AGP SVGA 3D accelerated graphics controller

- 8MB high-speed, 64bit SGRAM with 100MHz interface

- Integrated 24-bit 220MHz RAMDAC

- Rear panel DB-15, high density, 15-pin connector, female

- Display resolutions up to 1600 x 1200 (see **Table 2-1**)

Table 2-1: 740 AGP Video Resolutions

| 5 10        | Bits per Pixel (Hz) |                    |                    |  |  |

|-------------|---------------------|--------------------|--------------------|--|--|

| Resolution  | 8-bit Indexed       | 16-bit Indexed     | 24-bit Indexed     |  |  |

| 320 x 200   | 60, 72, 75, 85      | 60, 72, 75, 85     | 60, 72, 75, 85     |  |  |

| 320 x 240   | 60, 72, 75, 85      | 60, 72, 75, 85     | 60, 72, 75, 85     |  |  |

| 512 x 384   | 60, 72, 75, 85      | 60, 72, 75, 85     | 60, 72, 75, 85     |  |  |

| 640 x 350   | 85                  | 85                 | 85                 |  |  |

| 640 x 480   | 60, 72, 75, 85      | 60, 72, 75, 85     | 60, 72, 75, 85     |  |  |

| 800 x 600   | 56, 60, 72, 75, 85  | 56, 60, 72, 75, 85 | 56, 60, 72, 75, 85 |  |  |

| 1024 x 768  | 60, 72, 75, 85      | 60, 72, 75, 85     | 60, 72, 75, 85     |  |  |

| 1280 x 1024 | 60, 72, 75, 85      | 60, 72, 75, 85     | N/A                |  |  |

| 1600 x 1200 | 60, 75              | N/A                | N/A                |  |  |

## EIDE Disk Controller (dual port)

- Four fixed disk drives supported (two each on primary and secondary PCI buses)

- PIO Mode 4 and Ultra DMA/33 support

- Full support for LS-120 HD floppy drive

#### Floppy Diskette Controller (dual port)

Supports 1.44MB and 720K floppy drives, as well as LS-120 HD floppy drives.

#### Serial Ports

- Two RS232, 16C550-compatible, FIFO buffer

- ESD protected to ±15kV

#### Parallel Port

- Single parallel port controller with bidirectional compatibility

- EPP and ECP enhanced port modes

Page 2-2 Manual Number: 00431-248-1

## Keyboard, speaker, and reset port

- Single 8-pin header connector for system interface

- Keyboard power supplied through +5VDC self-healing fuse

#### PS/2 Mouse controller

- Microsoft compatible

- Six-pin mini-DIN connector at rear panel

- Single 8-pin header connector for system interface

- Power supplied through +5VDC self-healing fuse

## Universal Serial Bus (USB)

- Universal Host Controller Interface (UHCI) configuration

- Dual USB connectors at rear panel via separate cable and bracket assembly (optional)

- Power supplied through +5VDC self-healing fuse

# Watchdog Timer

- Reset CPU automatically if CPU stops operating

- Reset CPU automatically if +5VDC varies more than 5%

- Programmable to 100ms, 250ms, or 500ms

- Jumper or software disable/enable

#### Realtime Clock

- Motorola MC146818A compatible

- 256 bytes of battery-backed RAM

- Clock source at 14.318MHz accurate to ±1720Hz

#### CMOS Battery

Onboard lithium 3.0V battery with diode protection circuitry.

#### Supported Operating Systems

- Windows 95, Windows 98–full support.

- Windows NT V4.0 and later, server or workstation—full support.

- QNX V4.24-video support limited to a maximum of 800 x 600 by operating system.

- Red Hat Linux V5.2-video support limited to 80x25 text mode.

Use offboard ISA or PCI video controllers with the following operating systems:

- SCO Unix V5.0 and later.

- SCO UnixWare V2.1 and later.

- Solaris V2.5.1 and later.

- OS/2 V2.0 and later.

## **Operating Environment**

## Temperature

5 to 50°C

## Humidity

5 to 95% RHNC

#### Shock

· 2G, any axis

#### Vibration

0.5G, 10 to 2000Hz, any axis

## Storage Environment

# Temperature

-40 to 85°C

## Humidity

5 to 90% RHNC

#### **MTBF**

110,000 P.O.H. @ 25°C

# **Current Requirements**

• +5V typical current draw: 6.4 – 8.1A

+5V maximum current draw: 14.81–16.93A

+12V maximum current draw: 200mA

Note: 1) +5V current draw is processor dependent.

2) Onboard +3.3 V is regulated down from the +5V source.

# **Agency Approvals**

FCC conformity with:

47 CFR Part 15, Subpart B, Class A

CE conformity with:

EU EMC Directive 89/336/EEC

EU Low Voltage Directive 72/23/EEC

UL/cUL Recognized to

Ul 1950, 2nd Ed: 1993

cUL/CAN/CSA-C22.2 No. 950.93

# Locations of Major Components on the SB686BX Series

Figure 2-1: SB686BX Series Major Components

# **Chapter 3: Major Components**

This section describes the major components, connectors, and layouts on the SB686BX single board computer. As you are reading this chapter refer to **Figure 3-1** for the diagram of the board components and connectors.

## **Features**

# **Bus Support**

The SB686BX single board computer includes the following bus support:

- 8.33 MHz ISA-AT Bus (64mA source with 32mA sink)

- 33MHz PCI 2.1 compliant PCI bus

- Switch-selectable 100MHz or 66MHz GTL+ for FSB

- 100MHz local memory AGP

#### **Onboard Controllers**

The onboard controllers for disk drives, serial ports, and parallel ports are incorporated into the design of the SB686BX single board computer. The SB686BXV also contains the advanced Intel 740 Graphics controller to take advantage of the 440BX chipset AGP port. All onboard controllers can be enabled or disabled through the system BIOS. Unless indicated, the following controllers are present in all models of the SB686BX single board computer.

## Dual EIDE Disk Drive Controller (J4, J7)

The Primary IDE fixed disk drive interface is located at **J4** with the Secondary IDE connector placed at **J7**. Both EIDE connectors are located on the PCI local bus and support dual drives. The interface includes logical block addressing (LBA), PIO mode 4 support, and Ultra DMA/33 allowing up to 33Mb/sec data transfer rate throughput speeds.

# **Dual Diskette Drive Controller (J5)**

The diskette drive controller at **J5** supports up to two drives. The diskette drive can support floppy disk formats from 360K to 2.88MB. Support is also offered for the LS-120 HD format floppy disk drive.

## I/O Ports

The SB686BX(V) single board computer has two serial ports and one parallel port for I/O communications.

## Serial Ports (J9, J16)

The serial ports are located at **J9** and **J16**. They are both compatible with the 16550 UART. The serial port at J9 is extended through a 10-pin header on the board. J16 is extended through a DB-9 connector. Both serial ports are ESD protected to  $\pm 15$ kV on signal lines.

# **Enhanced Parallel Port (J8)**

The SB686BX also includes an enhanced parallel port at **J8**, which is capable of bidirectional communication. The parallel port is extended through a 26-pin header on the board to a bracket-mounted DB-25 connector.

# Watchdog Circuit (U28)-Not Shown

The watchdog circuit, located at **U28** on the back of the SBC, is a hardware timer that resets the CPU if the timer is not refreshed periodically. The circuit uses a trigger pulse provided by the onboard Eprom Flash (ISP1032E) programmable logic device to refresh itself. The watchdog timout period is software programmable to 100ms, 250ms, or 500ms. This timer is enabled by a switch setting on the back of the board. When enabled, the software needs to toggle bit "0" once every preselected millisecond period to prevent the timer from resetting the CPU. The watchdog circuit will also reset the CPU if the +5VDC power input falls below +4.75VDC. The watchdog prefail signal output can be routed to IRQ10 or IRQ11 via jumper to trigger the ISA bus IRQ if the watchdog time I/O space is not written to within half of the timeout period.

# Universal Serial Bus (J12)

The high-speed, high-capacity Universal Serial Bus (USB) is located at **J12** and supports ISA/PCI passive backplanes with up to 6 PCI expansion slots. The USB supports data transfer rates of 12 Mbps(12 million bits per second) and is capable of connecting up to 127 peripheral devices, such as mice, modems, and keyboards. USB also allows Plug-and-Play installation and hot plugging where supported by the operating system. Refer to Chapter 4 for special installation instructions if you purchased the SB686BXV or the SB686BXVC with the Intel 740 AGP Graphics controller and your choice of operating systems is Windows 95. To operate the USB feature you must follow these instructions.

# SB686BX Onboard Controllers (U9, U11)

The SB686BX(V) is designed around the Intel 440BX AGPset. It consists of the Intel 82443BX PCI/AGP controller (PAC) at **U9** and the Intel 82371EB PCI/ISA IDE accelerator (PIIX4E) bridge chip at **U11**.

The 440BX PAC chip is a 492-pin BGA (Ball Grid Array), which interfaces the Pentium II and Pentium III host address and data bus to the local PCI bus and memory section. The PAC chip integrates the main memory controller with support for 3.3V SDRAM DIMM modules with EC, ECC, and non-ECC capabilities. The SB686BX(V) contains two DIMM sockets and is configured as a Small Memory Array, which supports 6 rows for x8 and x16 single sided and dual sided DIMMs. The PAC operates the system bus at 66/100MHz and the PCI bus at 33MHz.

The PIIX4E is the other half of the chipset. It consists of a 324-pin BGA, which is a multifunction PCI device that acts as a PCI-to-ISA bridge function and a PCI-IDE controller. The PIIX4E also contains an enhanced DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, and a real time clock. The battery source for the real time clock is supplied by an industry standard CR2032 3.0 Volt lithium battery.

Page 3-2 Manual Number: 00431-248-1

# Main Memory (J1, J6)

The SB686BX has two dual in-line memory module (DIMM) sockets located at **J1** and **J6**. Minimum memory size is 16MB; maximum memory size is 512MB.

The SB686BX(V) supports the following memory particulars:

- 168-pin DIMMs with gold-plated contacts

- SDRAM (66MHz or 100MHz)

- Non-ECC (64-bit) and EC or ECC (72-bit) memory

- 3.3 Volt memory unbuffered DRAM only

- · Single- or double-sided DIMMs in the following sizes:

| DIMM Size | Non-ECC Configuration | EC or ECC Configuration |

|-----------|-----------------------|-------------------------|

| 16MB      | 2Mbit x 64            | 2Mbit x 72              |

| 32MB      | 4Mbit x 64            | 4Mbit x 72              |

| 64MB      | 8Mbit x 64            | 8Mbit x 72              |

| 128MB     | 16Mbit x 64           | 16Mbit x 72             |

| 256MB     | (ECC only)            | 32Mbit x 72             |

Memory may be installed in one or two sockets and may vary in memory size between sockets.

# Display Controller (U10)

**Note:** The display controller is installed only in the SB686BXV and SB686BXVC models.

The Intel 740 graphics accelerator, located at **U10**, works through the Accelerated Graphics Port (AGP) in the 440BX AGPset. The 740 supports perspective-correct texture mapping, MIP-Mapping, Gouraud shading, alpha-blending, stippling, anti-aliasing, fogging, and Z Buffering. 8MB of high-speed 64-bit SGRAM memory is built in to the SB686BXV and SB686BXVC to provide the utmost in graphics capabilities and speed. In addition, the video controller has a 100MHz interface to deliver video resolutions up to 1600 x 1200 with 256 colors. **Table 2-1** lists the refresh rates and maximum colors available for the supported resolutions.

The analog video is routed through a high density DB15 VGA connector located on the rear bracket at J23. See the section for connector locations and pinouts later in this chapter. Along with the controller, you will receive a set of diskettes containing video display drivers and display-enhancement utilities. The diskettes also contain documentation for installing and configuring the drivers.

# Flash ROM (U30)

The flash ROM used for BIOS and Plug and Play (PnP) functionality in the SB686BX(V) is a 40-pin TSOP (Thin Small Outline Package) 2Mb chipset. It also allows more BIOS-embedded features, such as video. All device programming is managed through the floppy disk drive (see Appendix A for more flash ROM information). In addition, all flash writes are qualified through the use of the onboard PLD (Programmable Logic Device) and Ultra I/O general purpose register to avoid accidental BIOS corruption.

# Onboard PLD (J19)

The onboard PLD is a multifunction in-circuit-programmable 100 pin TQFP from Lattice Semiconductor.

# I/O Port Controller (U12)

A 160-pin ultra I/O controller at **U12** processes much of the I/O functionality of the SB686BX series. The ultra I/O controller is an ISA PnP compatible controller that contains the keyboard and PS/2 mouse controllers, floppy disk controller, UARTs for serial ports, parallel port, and general purpose I/O registers. The PS/2 mouse connector at **J21** is a 6-pin mini-DIN located at the rear bracket. The keyboard (located at **J13**) signals are onboard the SBC connector. Filters have been placed where the mouse and keyboard signals to reduce EMI. The floppy disk connector (**J5**), parallel port connector (**J8**), and COM Port 2 (**J9**) connector all consist of headers located on the SBC. The COM Port 1 (**J16**) connector uses a DB9 located on the rear bracket of the feature card. See the following section for exact connector locations and pinout details.

# Real-Time Clock, CMOS SRAM, and Battery

The real-time clock is compatible with the Motorola MC146818A. This clock provides time-of-day, alarm features, and a multi-century calendar with century rollover. It supports 256 bytes of battery-backed CMOS SRAM in two banks that are reserved for BIOS use.

A lithium coin-cell battery powers the real-time clock and CMOS memory . The battery has an estimated life of seven years. When the computer is on, current from the power supply (3.3V) will extend the life of the battery. The 14.318MHz clock is accurate to  $\pm$  1720Hz or  $\pm$  13 minutes/year at 25°C with 3.3V applied.

**Note:** The time, date, and CMOS values should be defined in the setup program. Also, the CMOS values may be returned to their default settings via the setup program.

Page 3-4 Manual Number: 00431-248-1

# Connectors

The SB686BX and SB686BXV have several rear panel and onboard connectors. Silkscreened numbers identify the connectors and square pads mark each pin 1 to prevent improper connection. All pins that supply power to an external connection are fused for protection.

Note: The # symbol in the following pinouts indicates an active low signal.

## J1: DIMM Memory Socket

168-pin "Small Memory Array" socket to support 6 rows for x8 and x16 single-sided and dual-sided SDRAM Dimms.

#### J2: IDE Hard Drive LED Connector

The J2 connector (2-pin header) provides the IDE hard drive access signal. This connector has a 5V differential to activate any IDE hard drive access LED used in the chassis.

#### J3: Not Used

#### J4: Primary EIDE Hard Drive Connector

The J4 connector (40-pin dual row header) supplies signals from an onboard EIDE controller to interface up to two EIDE hard drives.

| 1  | RESET       | 2  | GND       |

|----|-------------|----|-----------|

| 3  | DATA 7      | 4  | DATA 8    |

| 5  | DATA 6      | 6  | DATA 9    |

| 7  | DATA 5      | 8  | DATA 10   |

| 9  | DATA 4      | 10 | DATA 11   |

| 11 | DATA 3      | 12 | DATA 12   |

| 13 | DATA 2      | 14 | DATA 13   |

| 15 | DATA 1      | 16 | DATA 14   |

| 17 | DATA 0      | 18 | DATA 15   |

| 19 | GND         | 20 | N/C (Key) |

| 21 | DMA Request | 22 | GND       |

| 23 | I/O Write   | 24 | GND       |

| 25 | I/O Read      | 26 | GND           |

|----|---------------|----|---------------|

| 27 | IORDY         | 28 | Cable Select  |

| 29 | DMA ACK       | 30 | GND           |

| 31 | IRQ 14        | 32 | N/C           |

| 33 | Address 1     | 34 | N/C           |

| 35 | Address 0     | 36 | Address 2     |

| 37 | Chip Select 0 | 38 | Chip Select 1 |

| 39 | LED           | 40 | GND           |

#### J5: Floppy Drive Connector

The J5 connector (34-pin dual row header) supplies the signal from an onboard diskette drive controller for one or two diskette drives.

| 1  | GND | 2  | DRVEN0         |

|----|-----|----|----------------|

| 3  | GND | 4  | N/C (Reserved) |

| 5  | GND | 6  | DRVEN1         |

| 7  | GND | 8  | INDEX#         |

| 9  | GND | 10 | FDME0#         |

| 11 | GND | 12 | FDSEL1#        |

| 13 | GND | 14 | FDSEL0#        |

| 15 | GND | 16 | FDME1#         |

| 17 | GND | 18 | DIR#           |

| 19 | GND | 20 | STEP#          |

| 21 | GND | 22 | WRDATA#        |

| 23 | GND | 24 | WRGATE#        |

| 25 | GND | 26 | TRK0#          |

| 27 | GND | 28 | WRPRO#         |

| 29 | GND | 30 | RDDATA#        |

| 31 | GND | 32 | HDSEL#         |

| 33 | GND | 34 | DSKCHG#        |

|    |     |    |                |

The "#" after a signal indicates an active low signal.

## J6: DIMM Memory Socket

168-pin "Small Memory Array" socket to support rows for x8 and x16 single-sided and dual-sided SDRAM Dimms.

## J7: Secondary EIDE Hard Drive Connector

The J7 connector (40-pin dual row header) supplies signals from an onboard EIDE controller to interface up to two EIDE hard drives.

| 1  | RESET         | 2  | GND           |

|----|---------------|----|---------------|

| 3  | DATA 7        | 4  | DATA 8        |

| 5  | DATA 6        | 6  | DATA 9        |

| 7  | DATA 5        | 8  | DATA 10       |

| 9  | DATA 4        | 10 | DATA 11       |

| 11 | DATA 3        | 12 | DATA 12       |

| 13 | DATA 2        | 14 | DATA 13       |

| 15 | DATA 1        | 16 | DATA 14       |

| 17 | DATA 0        | 18 | DATA 15       |

| 19 | GND           | 20 | N/C (Key)     |

| 21 | DMA Request   | 22 | GND           |

| 23 | I/O Write     | 24 | GND           |

| 25 | I/O Read      | 26 | GND           |

| 27 | IORDY         | 28 | Cable Select  |

| 29 | DMA ACK       | 30 | GND           |

| 31 | IRQ 14        | 32 | N/C           |

| 33 | Address 1     | 34 | N/C           |

| 35 | Address 0     | 36 | Address 2     |

| 37 | Chip Select 0 | 38 | Chip Select 1 |

| 39 | LED           | 40 | GND           |

#### J8: Parallel Port Connector

The J8 connector (26-pin dual row header) allows the use of parallel devices, typically printers. Your computer will be delivered with this port already connected to a slot filler bracket for easier access.

| 1 | STROBE#  | 2 | AUTOFEED# |

|---|----------|---|-----------|

| 3 | DATABIT0 | 4 | FAULT#    |

| 5 | DATABIT1 | 6 | INIT#     |

| 7 | DATABIT2 | 8 | SLCTIN#   |

| 9  | DATABIT3 | 10 | GND |

|----|----------|----|-----|

| 11 | DATABIT4 | 12 | GND |

| 13 | DATABIT5 | 14 | GND |

| 15 | DATABIT6 | 16 | GND |

| 17 | DATABIT7 | 18 | GND |

| 19 | ACK#     | 20 | GND |

| 21 | BUSY     | 22 | GND |

| 23 | PERR     | 24 | GND |

| 25 | SELECT   | 26 | N/C |

The "#" after a signal indicates an active low signal.

#### J9: COM2 Connector

The J9 connector (10-pin dual row header) is the second system serial port, which allows the use of serial devices or serial communications. Your SB686BX will be delivered with this port already connected to a slot filler bracket for easier access.

| 1 | CD  | 2  | DSR |

|---|-----|----|-----|

| 3 | RX  | 4  | RTS |

| 5 | TX  | 6  | CTS |

| 7 | DTR | 8  | RI  |

| Q | GND | 10 | N/C |

J10: GND

J11: Not Used

#### J12: USB Port 1 & 2 Connector

The J12 connector (10-pin dual row shrouded header) allows the use of the universal serial bus, port 1 and 2.

| 1 | USB1 +5V | 2  | USB0 +5V       |

|---|----------|----|----------------|

| 3 | USB1 -   | 4  | USB0 -         |

| 5 | USB1 +   | 6  | USB0 +         |

| 7 | USB1 GND | 8  | USB0 GND       |

| 9 | N/C      | 10 | USB Shield GND |

An optional bracket is offered for use with the dual USB port to provide rear panel connections.

## J13: Keyboard Connector

The J13 connector (8-pin header) is the place to connect your keyboard connector that routes to the location on your chassis where you plug in your keyboard.

1 PBRST# 2 GND

3 N/C 4 KBDCLOCK

5 KBDDATA 6 KBDLOCK

7 +5V (Fused) 8 SPKR#

J14: GND

J15: GND

#### J16: COM1 Connector

The J16 connector (*DB9*) is the first system serial port. Typically it provides connection for a serial mouse or for serial communications.

1 CD 2 RX 3 TX 4 DTR 5 GND 6 DSR 7 DTR 8 CTS 9 RI

#### J17: WatchDog Timer Reset Enable

The J17 connector (2-pin header) provides the enable for the watchdog timer reset. The SB686BX boards are delivered with the jumper in the default setting (the jumper is only on pin 1). When you need to enable the watchdog timer reset, you must place the jumper across pins 1 and 2.

J18: Not Used

# J19: PLD ISP Connector Reserved for company use

#### J20: Alternate P/S-2 Mouse Connector

The J20 connector (6-pin header) provides an alternate connection to a P/S-2—type mouse.

1 MDATA 2 N/C 3 GND 4 +5V (fused) 5 MCLOCK 6 Shield GND

#### J21: P/S-2 Connector

The J21 connector (6-pin mini-DIN) allows you to connect a P/S-2 type mouse.

1 MDATA 2 N/C 3 GND 4 +5V (fused) 5 MCLOCK 6 N/C

J22: Not Used

#### J23: VGA Connector

The J23 connector (*HDB15*) supplies the signal from the *optional* video graphics controller to the monitor.

1 RED 2 GREEN BLUE N/C (Reserved) 5 **GND** 6 GND 7 **GND** 8 GND 9 N/C 10 GND 11 N/C 12 DDCDAT 13 HSYNC 14 VSYNC 15 DDCCLK

# **Jumper Connectors**

#### JP1: Fan Tachometer Connector

The JP1 connector is a 2-pin single row friction lock type connector. The SB686BX models are delivered with a fan tachometer for the microprocessor. This tachometer receives its power through the JP6 connector.

1 GND 2 TACH

This connection is used to provide an alarm signal for Industrial Computer Source chassis which provide the monitoring function.

#### JP2: CMOS Setup Jumper

JP2 is 3-pin connector used to clear the CMOS. All SB686BX boards delivered with the jumper in the default setting. Pins 2 and 3 will have the jumper across them in the default setting. When it is necessary to clear the CMOS settings the shut will be applied to pins 1 and 2 as described in chapter 4 (see the section on CMOS Clear).

## JP3: WDT IRQ Select Jumper

JP3 is 3-pin connector used to select the IRQ-10 or IRQ-11. The jumper should be placed on pins 1-2 if you are selecting IRQ-10. If you want to select IRQ-11, place the jumper on pins 2-3.

1 IRQ-10 2 WDT signal

3 IRQ-11

#### JP4: Flash Mode Jumper

The JP4 is 3-pin connector used in the process to update the Flash ROM. All SB686BX boards delivered with the jumper in the default setting. Pins 2 and 3 will have the jumper across them in the the default setting. Do not place the jumper on pins 1 and 2, this is for company use only.

#### JP6: Fan Power Connector

The SB686BX models are delivered with a fan appropriate for the microprocessor. This fan is powered through the JP6 connector (3-pin single row friction lock) with +12VDC.

1 GND 2 +12V

3 TACH

## P1: +5 Volt Input Connector

The P1 connector (6-pin header) is the voltage input connector.

1 +5V 2 +5V 3 +5V 4 GND

5 GND 6 GND

# **Board Layout**

**Figure 3-1** illustrates the SB686BXV single board computer. Standard PICMG dimensions are used for all boards. Notice in particular the connectors listed in the previous section.

Figure 3-1: SB686BX Jumpers and Connections

# Chapter 4: Installation and Configuration

If you purchased a SB686BX Series single board computer with a chassis, the board and its components were tested for you prior to shipment. However, if you upgrade or replace components, this chapter covers the steps necessary to ensure that the new items will work properly with your single board computer.

Upgrading your system may require installing board components (such as the memory), configuring the system (setting DIP switches for component compatibility or to enable functions), connecting the input/output devices, and setting up the operating system. Depending on your system, you may only need to do part of this process, but each part of the computer is interdependent, so please check related topics for compatibility. For example, if you are upgrading your processor from 333 to 450MHz, you must change DIP switch settings for the faster processor speed.

For the location of the components and connectors discussed in this chapter please refer to **Figure 3-1** in the previous chapter.

# Installing the SDRAM DIMM Memory (J1, J6)

One of the user-changeable board components is the Synchronous Dynamic Random Access Memory (SDRAM) at **J1** and **J6**, shown in **Figure 3-1**. Follow the steps below to install the SDRAM correctly.

The SB686BX Series single board computer accepts from 16MB up to 512MB of SDRAM. The two 168-pin SDRAM Dual Inline Memory Module (DIMM) sockets will accept 64- and 72-bit DIMM modules (3.3V memory – unbuffered SDRAM only).

The single board computer will accept only DIMMs with gold-plated contacts. To ensure reliable operation at zero wait states, use only 10ns or faster SDRAM DIMMs for bus speeds less than 100MHz. For 100MHz or higher, use only 8ns or faster SDRAM DIMMs. If both memory DIMM sockets are used, they may be filled with different size memory, but the DIMMs should be made by the same manufacturer and be of the same speed.

**Note:** Before performing the following procedures, remove the board from the backplane and lay it on a flat ESD protected, non-static surface.

#### CAUTION!

DIMM sockets are very durable but can be broken. Use extreme care when removing a DIMM from the socket. Never force a DIMM into a socket and make sure the DIMM is in the correct orientation before installation. Any DIMM sockets broken due to ABUSE, MISHANDLING, or ACCIDENT are not covered under the warranty.

Manual Number: 00431-248-1 Page 4-1

#### **CAUTION!**

Be sure to take proper electrostatic discharge precautions *before* starting any work.

- Move the module release levers (one on each end of the socket) outward, away from the socket (Figure 4-1).

- 2. Place the DIMM so that the two notches on the contact edge line up with the two alignment nodes in the DIMM socket. Insert the DIMM into the socket at a 90-degree angle.

Figure 4-1: DIMM Orientation

Using both hands, press downward and guide the DIMM into the socket. The module release

levers will return to their upright position when the DIMM is completely seated in the socket.

The pegs on the tips of the release levers should align with the notches on both ends of the DIMM

(Figure 4-2).

Figure 4-2: DIMM Installation

Page 4-2 Manual Number: 00431-248-1

# Dual EIDE and Floppy Drive Connections (J4, J7, J5)

The primary EIDE connector is **J4**, and the secondary EIDE connector is **J7**. Both support LBA mode, and each will connect up to two devices. **J5** is the floppy connector. It will also connect up to two devices. The connectors are keyed so the cables will only connect in the correct direction (**Figure 3-1**).

# COM1 and COM2 Dual Serial Ports (J16,J9)

COM1 and COM2, located at **J16** and **J9** respectively (**Figure 3-1**), are dual serial ports set to RS232 standards. The ports use a 16550 compatible dual serial port controller and have 16 byte transmit/receive FIFO buffers. Both ports are ESD protected to  $\pm 15$ kV

# Bus Speed (SW1)

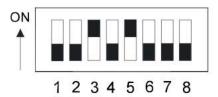

**SW1** on the SB686BX Series allows you to set the bus speed for the CPU, please see **Figure 3-1** for the location of the switch on the circuit board. **Table 4-1** lists the settings for both Celeron, Pentium II, and Pentium III processors. **Figure 4-3** shows a detail of the switch configured for a Pentium II 350MHz processor.

Table 4-1: SW1 Settings

| System Bus              | Processor<br>Speed (MHz) | Switch Settings |     |     |     |     |

|-------------------------|--------------------------|-----------------|-----|-----|-----|-----|

| Frequency<br>Multiplier |                          | 1-1             | 1-2 | 1-3 | 1-4 | 1-5 |

| 11/2                    | Celeron 366MHz           | ON              | N/A | N/A | N/A | N/A |

| 6                       | Celeron 400MHz           | ON              | N/A | N/A | N/A | N/A |

| 7/2                     | Pentium II 350MHz        | OFF             | OFF | ON  | OFF | ON  |

| 4                       | Pentium II 400MHz        | OFF             | ON  | ON  | ON  | OFF |

| 9/2                     | Pentium II 450MHz        | OFF             | OFF | ON  | ON  | OFF |

| 9/2                     | Pentium III 450MHz       | OFF             | N/A | N/A | N/A | N/A |

| 5                       | Pentium III 500MHz       | OFF             | N/A | N/A | N/A | N/A |

**Notes:** 1) Celeron and Pentium III are autosensing and only require a setting of switch **1-1**. This sets the bus speed (66 or 100).

2) Pins 6, 7, and 8 on SW1 are reserved for factory use.

Manual Number: 00431-248-1 Page 4-3

Figure 4-3: SW1 Settings for 350MHz Pentium II Processor

# Watchdog Timer Configuration (J17)

The watchdog timer is embedded in the onboard PLD as described in Chapter 3. The timer can be configured by software using a general-purpose decode register on the Ultra I/O controller. (Refer to Appendix B for information on configuring the watchdog timer via software). You can select one of three timeout periods: 100ms, 250ms, or 500ms.

To enable the timer, you must configure it by software and place a shunt over **J17**. You must use this jumper if you want to use the watchdog timer feature.

To select an optional pre-timeout interrupt, place a shunt on **JP3**. Place the shunt over pins 1 and 2 to select IRQ10 or over pins 2 and 3 to select IRQ11. Program the selected IRQ with the same software used to configure the timer. The pre-timeout interrupt signal triggers if it is not refreshed within half of the specified timeout period. For example, if you select a timeout period of 500ms, the refresh signal must be received within 250ms. Otherwise, the interrupt will be generated.

In addition to its programmable features, the watchdog timer also has a +5VDC monitor. If VCC falls between 4.5VDC and 4.75VDC then a hard reset may occur. If VCC falls below 4.5VDC, a hard reset will definitely be performed.

# Flash BIOS (JP4)

If you upgrade your flash BIOS make sure that the jumper is in place on pins 2 and 3. You should not need to change the jumper settings. When you receive your board, it should already have the jumper on pins 2 and 3, this is the default setting.

- Do not place the jumper on pins 1 and 2. These pins are reserved for factory use.

- To upgrade your flash ROM via floppy, ensure the jumper is over pins 2 and 3. This is the

default setting and it should not be changed.

# **CMOS Clear (JP2)**

JP2 clears the CMOS.

- To clear CMOS, turn off the power and place a shunt over pins 1 and 2 for approximately five seconds.

- To resume normal operation, replace the shunt over pins 2 and 3 and power on the system.

Page 4-4 Manual Number: 00431-248-1

## Windows 95 Installation

If you purchased the SB686BXV or the SB686BXVC with the Intel 740 AGP Graphics controller, you must take an additional step when installing Windows 95. (Of the operating systems listed in Chapter 2, only Windows 95 requires these changes.)

**Note:** Make sure your Windows 95 software includes USB support, and take the extra steps listed below *before* installing your video drivers.

# **USB Supplement**

#### **OSR 2.1**

For OSR 2.1, locate a folder on the CD labeled OTHER/USB. In that folder, locate the README.TXT file. Follow the instructions in the file.

#### **OSR 2.5**

For OSR 2.5, locate a folder on the CD labeled OTHER/UPDATES/USB. In that folder, locate the USB.TXT file. Follow the instructions in the file.

## Intel .INF Update

For best results, obtain the latest Windows 95 .INF update utility for the 440BX chipset. The .INF update allows Windows 95 to recognize and fully utilize the 440BX chipset. The file is available from the Intel website (http://developer.intel.com/design/chipsets/drivers/inf\_update.htm).

# SB686BX Series Current Requirements

The SB686BX Series current requirements vary according to the backplane option selected as shown in **Table 4-2**. See **Table 4-3** for the minimum number of conductors (+5V wires) that must to be connected to **P1** (auxiliary 5V supply) to supply adequate current to operate the single board computer properly.

ISA-only backplanes have three +5V pins on the ISA connector. Each ISA pin is rated for 3 Amps, providing a total of only 9A to any ISA card. Therefore, it is necessary to use the extra power connector on the SB686BX to supply an additional +5V input via HDD power connectors from the system power supply. An accessory power connector is included with your SB686BX Series which provides 3 HDD connectors to adapt to the P1 connector.

The ISA/PCI backplanes are designed with three +5V pins on the ISA connector and 13 +5V pins on the PCI connector. Each ISA pin is rated for 3A while each PCI pin is rated for 1A. This allows for a total of 22A that can be supplied to the SB686BX using the following equation:

$$(3 \text{ ISA pins x } 3A) + (13 \text{ PCI pins x } 1A) = 22A$$

The more power you supply to the SB686BX Series via P1, the less power your system will have to supply via the backplane. If your system is heavily loaded with expansion boards, consider using more connections at P1 than the minimum number specified in **Table 4-3**.

Manual Number: 00431-248-1 Page 4-5

Table 4-2: Power Matrix

| Processor          | Amperes Required |         |  |  |

|--------------------|------------------|---------|--|--|

| Speed              | Maximum          | Typical |  |  |

| Celeron 366MHz     | 15.17            | 7.5     |  |  |

| Celeron 400MHz     | 15.57            | 7.4     |  |  |

| Pentium II 350MHz  | 14.81            | 7.7     |  |  |

| Pentium II 400MHz  | 15.73            | 6.4     |  |  |

| Pentium II 450MHz  | 16.37            | 8.1     |  |  |

| Pentium III 450MHz | 16.19            | 7.2     |  |  |

| Pentium III 500MHz | 16.93            | 7.5     |  |  |

**Table 4-3: Conductor Matrix**

| Processor          | Minimum Number of<br>5V Conductors |         |  |  |

|--------------------|------------------------------------|---------|--|--|

| Speed              | ISA                                | ISA/PCI |  |  |

| Celeron 366MHz     | 1                                  | 0       |  |  |

| Celeron 400MHz     | 1                                  | 0       |  |  |

| Pentium II 350MHz  | 1                                  | 0       |  |  |

| Pentium II 400MHz  | 1                                  | 0       |  |  |

| Pentium II 450MHz  | 2                                  | 0       |  |  |

| Pentium III 450MHz | 1                                  | 0       |  |  |

| Pentium III 500MHz | 1                                  | 0       |  |  |

Page 4-6 Manual Number: 00431-248-1

# **Chapter 5: Maintenance and Troubleshooting**

This chapter provides minimal maintenance and troubleshooting information for your SB686BX single board computer. If you need assistance with these procedures, please call Technical Support at **800-480-0044** (U.S. and Canada) or **858-677-0877** (international).

# FCC Compliance Statement for Class A Devices

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference, and

- This device must accept any interference received, including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and radiates radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his or her own expense.

Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

**Note:** The assembler of a personal computer system may be required to test the system and/or make necessary modifications if a system is found to cause harmful interference or to be non-compliant with the appropriate standards for its intended use.

# How to Remain CE Compliant

The SB686BX Series single board computer is designed to be CE compliant when used in a CE compliant chassis. Maintaining CE compliance also requires proper cable and cabling techniques. Although ICS Advent offers accessories, the customer must ensure that these products are installed with proper shielding to maintain CE compliance. ICS Advent does not offer engineering services for designing cabling systems. In addition, ICS Advent will not retest or recertify systems or components that have been reconfigured by customers.

# Troubleshooting

All components of a computer are interrelated. That is, a "video" problem may be caused by the disk controller. The simplest diagnostic technique involves replacing the suspect card with a new one. If that doesn't fix the problem, remove all cards except the minimum required by the system. Then run the system, replacing each card until the problem is repeated.

**Note:** The assembler of a personal computer system may be required to test the system and/or make necessary modifications if a system is found to cause harmful interference or to be non-compliant with the appropriate standards for its intended use.

#### WARNING!

The following procedures involve working near high voltage. Contact with this voltage can seriously injure you. Accidental shorting of the circuits can damage the computer.

#### CAUTION!

The following procedures involve working with a device that is sensitive to static electricity. Use proper precautions to protect against electrostatic discharge (ESD). Only qualified personnel should attempt these procedures.

#### CPU does not boot, there is no beep, and there is no video.

- A. Ensure that the SB686BX Series single board computer is fully and correctly seated into the backplane.

- B. Turn the power off and clear the CMOS via JP2.

- C. Contact the ICS Advent to receive the latest BIOS flash file. Please refer to Appendix A for BIOS upgrade instructions.

- D. Check the SB686BX Series single board computer to ensure that all jumpers are installed as indicated in Chapter 4.

#### Hard disk drive controller failure on bootup.

- A. If you are using an IDE hard drive to boot, ensure that the power connector and the ribbon cable are properly connected.

- B. Check that the drive is configured properly as master or slave by jumpers on the drive.

- C. Check that the HDD parameters are set up correctly in the CMOS Setup. (You can use auto-detect hard disk to auto-detect the correct HDD parameters.)

# Non Plug-and-Play ISA card is not functioning properly.

A. If this card uses an IRQ, make sure that the particular IRQ is reserved to the 'ISA' bus in PCI/ PnP setup in CMOS.

# When booting, the CPU reports No ROM BASIC.

A. The system cannot find a proper bootable sector on either drive A or C. You need to install an operating system on the hard drive or insert a bootable diskette in the A drive.

# When booting, the System gives eight beeps.

- A. These beeps indicate a video adapter problem. Try the video card in a different slot.

- B. Try a different video card.

- C. If you are installing an external video card, determine if your board has onboard video. If it does, you need to disable the video in the CMOS PCI/PnP setup before installing the external video card.

- D. If the problem persists, clear CMOS and re-flash the BIOS as discussed in the AMI BIOS Manual (Appendix A).

**Note:** If your SB686BX Series single board computer has onboard video and you are using a separate video card, clearing the CMOS enables the onboard PCI video option in CMOS (default setting).

# When booting the system, you hear two beeps.

- A. Two beeps signify a memory error. Re-seat the DIMMs into the DIMM sockets and reboot.

- B. If the problem persists, swap DIMMs from one memory bank to the other. If the problem goes away after the swap, then switch the memory back to the original installation and see if the original error occurs.

- C. If the problem continues to persist, replace the modules with your spare memory modules.

- D. If the problem still persists after installing new memory, then the SB686BX Series board may have faulty DIMM sockets and may need to be returned for repair.

# The system runs very slow.

- A. The system will run significantly slower if the cache memory has been disabled in the Advanced Setup in CMOS. (Cache memory is automatically disabled when you choose the Fail-Safe option in CMOS setup.)

- B. Check that the DIP switch settings are correct for the CPU speed as described in Chapter 4.

# Returns

If you need to return a product to ICS Advent for any reason, the following applies:

- Call Customer Service for a Return Material Authorization (RMA) number. The RMA number must be visible on the outside of the box in which you pack the product. Shipments without an RMA number will not be accepted by Customer Service Receiving.

- Properly pack the product. Put the computer board into an appropriate ESD protective bag and seal to prevent moisture and dirt from entering.

- 3. Provide adequate packaging and use standard ESD precautions. If possible, use the original box and packing in which the product arrived. A minimum of four inches of proper packing material is required around all sides of computer products. Double-thick cardboard is preferred. Do not use styrofoam peanuts or loose fill to pack. Assume the box will be dropped several feet during shipping.

- 4. Do not ship by motor freight. Use a carrier such as Burlington, Airborne, or Federal Express.

Page 5-4 Manual Number: 00431-248-1

# Appendix A AMIBIOS

for the Intel 440BX Chipset for PCI, PnP, and ISA Systems with Flash ROM Support

# User's Guide

Modified for use with the SB686BX Series products from ICS Advent

Based on the 07/15/95 V6.31.00 Core AMIBIOS

Portions of this manual are © 1998, American Megatrends, Inc.

# **Table of Contents**

| Chapter 1: Introduction              | A-   |

|--------------------------------------|------|

| Chapter 2: Standard CMOS Setup       | A-7  |

| Chapter 3: Advanced CMOS Setup       | A-11 |

| Chapter 4: Advanced Chipset Setup    | A-15 |

| Chapter 5: PCI / Plug and Play Setup | A-19 |

| Chapter 6: Peripheral Setup          | A-21 |

# Chapter 1: Introduction

This manual documents the AMIBIOS for the Intel 440BX chipset based on the 07/15/95 V6.31.00 core AMIBIOS. This AMIBIOS is designed for a Pentium II-based ISA computer system with an SMC 932 Super I/O controller. This AMIBIOS also supports IDE on the PCI local bus.

# Plug and Play Support

This AMIBIOS supports the Plug and Play Version 1.0A specification. ESCD (Extended System Configuration Data) write is supported.

# **PCI Bus Support**

This AMIBIOS also supports Version 2.1 of the Intel PCI (Peripheral Component Interconnect) local bus specification. Please see the Intel technical documentation for additional information.

# **DRAM Support**

SDRAM (Synchronous DRAM) is supported.

# Flash ROM Support

Flash ROM support is also included in this AMIBIOS. To reprogram the flash ROM, get an updated BIOS ROM file from ICS Advent. Copy this file to a floppy. Insert the floppy into drive A: and press <Ctrl> <Home> while powering on.

# Supported CPUs

This AMIBIOS supports a single Intel Pentium II CPU.

# System BIOS

The BIOS is the basic input output system used in all IBM® PC-, XT®-, AT®-, and PS/2®-compatible computers. The AMIBIOS is a high-quality example of a system BIOS.

# How Data is Configured

AMIBIOS provides a Setup utility in ROM that is accessed by pressing <Del> at the appropriate time during system boot. Setup configures data in CMOS RAM. The main menu options are described below.

| Setup Options              | Description                                                                                                                  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Standard CMOS<br>Setup     | Sets time, date, hard disk type, types of floppy drives, monitor type, and detects if keyboard is connected (see Chapter 2). |

| Advanced CMOS<br>Setup     | Sets Quick Boot, System Boot Up Sequence, and many other options (see Chapter 3).                                            |

| Advanced Chipset<br>Setup  | Sets chipset-specific options and features (see Chapter 4).                                                                  |

| PCI/Plug and<br>Play Setup | Sets options related to the PCI bus and Plug and Play options (see Chapter 5).                                               |

| Peripheral Setup           | Controls I/O Controller-related options (see Chapter 6).                                                                     |

| Setup Options                              | Description                                                                                                                                                                                             |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto Detect<br>Hard Disks                  | Automatically detects the connected IDE drives.                                                                                                                                                         |

| Change User<br>Password                    | This option is grayed until you change the supervisor password. If the option is available, the default is no user password.                                                                            |

| Change Supervisor<br>Password              | Allows you to set or change a supervisor password that restricts access to the AMIBIOS main menu. The default is no supervisor password, which also means that no user password is required.            |

| Auto Configuration with Optimal Settings   | When you save your settings and exit the main menu, AMIBIOS automatically configures your system to optimal settings. This option is recommended as the most efficient choice for implementing AMIBIOS. |

| Auto Configuration with Fail Safe Settings | When you save your settings and exit the main menu, AMIBIOS automatically configures your system to fail-safe settings.                                                                                 |

| Save Settings<br>and Exit                  | Saves any changes you made from the main menu, exits, and reboots your system with the new settings.                                                                                                    |

| Exit without<br>Saving                     | Exits the main menu and reboots without saving changes to AMIBIOS settings.                                                                                                                             |

| Keys                                       | Function                                                                                                                                                                                                |

| Esc                                        | Exits the main menu and reboots your system without saving changes.                                                                                                                                     |

| F10                                        | Saves your changes, exits, and reboots your system.                                                                                                                                                     |

| $\uparrow$ and $\downarrow$                | Scroll up and down the main menu.                                                                                                                                                                       |

| F2 and F3                                  | Toggle through video color or monochrome options.                                                                                                                                                       |

# Chapter 2: Standard CMOS Setup

Select the AMIBIOS Setup options by choosing Standard Setup from the AMIBIOS Setup main menu. Standard Setup options are described below.

# Floppy Drive A: and/or B:

Move the cursor to these fields via  $\uparrow$  and  $\checkmark$  keys and select the floppy type. The settings are 360 KB 5\\(^1\)4 inch, 1.2 MB 5\(^1\)4 inch, 720 KB 3\(^1\)2 inch, 1.44 MB 3\(^1\)2 inch, 2.88 MB 3\(^1\)2 inch.

# Primary Master, Primary Slave, Secondary Master, and Secondary Slave