## **ACER AMERICA CORPORATION**

## 1100 16/20

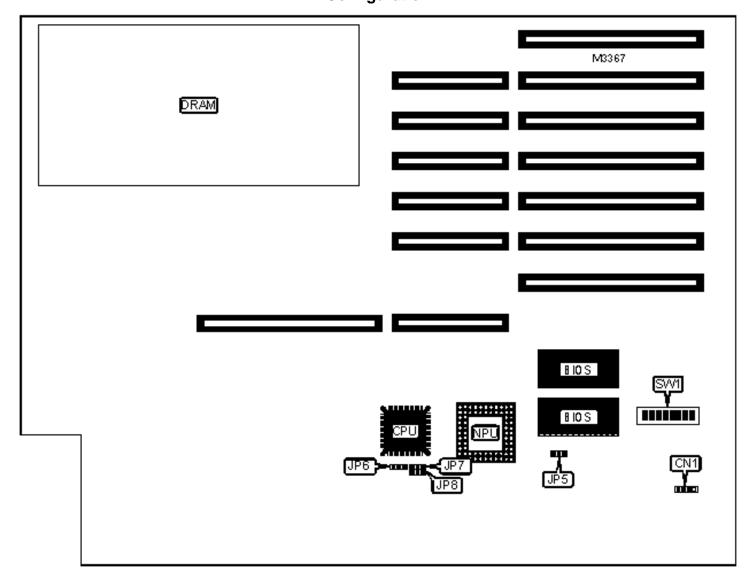

# Configuration

| CONNECTIONS      |          |  |

|------------------|----------|--|

| Purpose          | Location |  |

| External battery | CN1      |  |

|          | USER CONFIGURABLE SETTINGS      |       |          |  |

|----------|---------------------------------|-------|----------|--|

| Function |                                 | Label | Position |  |

|          | Monitor type select MDA/MGA/EGA | SW1/5 | Off      |  |

|          | Monitor type select CGA         | SW1/5 | On       |  |

#### **DRAM CONFIGURATION**

Note: Board is shipped with 2MB. The orientation and bank location is unidentified.

| DRAM SWITCH CONFIGURATION |       |     |  |

|---------------------------|-------|-----|--|

| Setting                   | SW1/8 |     |  |

| Mode 3                    | Off   | On  |  |

| Mode 4                    | Off   | Off |  |

| CPU SPEED SELECTION                                                                     |     |  |  |  |

|-----------------------------------------------------------------------------------------|-----|--|--|--|

| Speed SW1/6                                                                             |     |  |  |  |

| Smart mode                                                                              | On  |  |  |  |

| 16MHz                                                                                   | Off |  |  |  |

| 20MHz                                                                                   | Off |  |  |  |

| Note: If smart mode is used, system will automatically switch from 16MHz/20MHz to 8MHz. |     |  |  |  |

#### **NPU TYPE SELECTION**

| Туре                  | JP6               | JP7               | JP8               |

|-----------------------|-------------------|-------------------|-------------------|

| 80387SX installed     | Pins 1 & 2 closed | Pins 1 & 2 closed | Pins 2 & 3 closed |

| 80387SX not installed | Pins 2 & 3 closed | Pins 2 & 3 closed | Pins 1 & 2 closed |

| BIOS SELECTION |       |       |       |       |       |

|----------------|-------|-------|-------|-------|-------|

| Туре           | JP5   | SW1/1 | SW1/2 | SW1/3 | SW1/4 |

| 27128          | 2 & 3 | On    | On    | Off   | Off   |

| 27256          | 2 & 3 | Off   | Off   | On    | On    |

| 27512          | 1 & 2 | Off   | Off   | On    | On    |

Note: Pins designated should be in the closed position.

# MISCELLANEOUS TECHNICAL NOTE

Note: The location of pin 1 on the jumpers and switch are unidentified.