# <u>Little Board™/386SX-IIA</u>

## **Technical Manual**

PN: 5001031

Revision: C

Ampro Computers, Incorporated 4757 Hellyer Ave.San Jose, CA 95138 Tel (408) 360-0200 FAX (408) 360-0222

http://www.ampro.com

The male PC/104 Bus Headers supplied on this Second Generation Little Board CPU are not compatible with backplanes and cable adapters intended for use with Third Generation Little Boards. Damage to the Little Board will occur if used with these components. Use only Bus Expansion components intended for use with Second Generation products.

## Warning

The DST Cable Adapter and AT Bus backplane supplied with Second Generation Development Chassis, Kits, and Systems are not compatible with Third Generation Little Board CPUs. Damage to the Little Board will occur if used with these components.

## NOTICE

#### **DISCLAIMER**

Ampro Computers, Incorporated makes no representations or warranties with respect to the contents of this manual or of the associated Ampro software products, and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. Ampro shall under no circumstances be liable for incidental or consequential damages or related expenses resulting from the use of this product, even if it has been notified of the possibility of such damages. Ampro reserves the right to revise this publication from time to time without obligation to notify any person of such revisions. If errors are found, please contact Ampro at the address listed on the title page of this document.

## **TRADEMARKS**

The Ampro logo is a registered trademark, and Ampro, Little Board, StackPlane, MiniBackplane, MiniModule, and CoreModule are trademarks of Ampro Computers, Inc. All other marks are the property of their respective companies.

## **TECHNICAL SUPPORT**

Technical support is available from 8:00 AM to 5:00 PM, Pacific time.

- Technical support telephone number: 800 966-5200.

(Please have the product you wish to discuss at hand when you call.)

- E-mail address: techsupport@ampro.com

- Ampro technical support Bulletin Board (BBS): 408 720-1332

## **REVISION HISTORY**

| Revision | Reason for Change  | Date |

|----------|--------------------|------|

| 1/A      | Initial Release    | 3/96 |

| В        | Production Release | 9/96 |

| С        | Update Figure 2-6  | 6/97 |

## **COPYRIGHT 1996, AMPRO COMPUTERS, INCORPORATED**

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of Ampro Computers, Incorporated.

## Little Board/386SX-IIA

## **PREFACE**

This manual is for integrators and programmers of systems based on the Ampro Little Board/386SX-IIA single board system. It contains information on hardware requirements and interconnection, and details of how to program the system.

There are four chapters and one appendix, organized as follows:

**Chapter 1**—Introduction. General information pertaining to the Little Board/386SX-IIA, its features, and specifications.

**Chapter 2**—Hardware Configuration. A description of how to configure and connect the Little Board/386SX-IIA for use with a variety of onboard and external devices. Included are tables listing the pinouts of each of the board's connectors, board jumpering, Configuration Memory initialization with the SETUP function, and considerations and specifications regarding peripheral devices.

**Chapter 3**—Software Configuration. An overview of the system features, configuration options, and utilities that are available under the Disk Operating System (PC-DOS, MS-DOS, or DR DOS), including system setup guidelines.

**Chapter 4**—Advanced Topics. Detailed technical information on Little Board/386SX-IIA onboard hardware and peripheral interfaces.

## **TABLE OF CONTENTS**

|     | apter 1 - Introduction                                  |    |

|-----|---------------------------------------------------------|----|

|     | GENERAL DESCRIPTION                                     |    |

|     | LITTLE BOARD/386SX-IIA FEATURES                         |    |

| 1.3 | LITTLE BOARD/386SX-IIA SPECIFICATIONS                   | 3  |

|     |                                                         |    |

|     | apter 2 - Hardware Configuration                        |    |

| 2.1 | INTRODUCTION                                            |    |

|     | 2.1.1 Interface Connectors                              |    |

|     | 2.1.2 Jumper Configuration Options                      | 3  |

|     | 2.1.3 SETUP Options                                     |    |

| 2.2 | DC POWER                                                | 4  |

|     | 2.2.1 Power Requirements                                | 5  |

|     | 2.2.2 Powerfail Options                                 |    |

|     | 2.2.3 Backup Lithium Battery Considerations             | 7  |

|     | 2.2.4 Cooling Requirements                              |    |

| 2.3 | ONBOARD DEVICE OPTIONS AND CONFIGURATION                | 7  |

|     | 2.3.1 DRAM                                              | 7  |

|     | 2.3.2 Math Coprocessor                                  | 8  |

|     | 2.3.3 Byte-Wide Sockets                                 | 9  |

|     | 2.3.4 Battery-Backed Clock                              |    |

|     | 2.3.5 Using Flash EPROMs.                               | 13 |

|     | 2.3.6 Using SRAMs                                       |    |

|     | 2.3.7 Watchdog Timer Option                             | 15 |

|     | 2.3.8 Video Display Mode                                | 16 |

| 2.4 | PERIPHERAL CONNECTIONS AND CONFIGURATION                |    |

|     | 2.4.1 Utility Connector                                 | 16 |

|     | 2.4.2 Keyboard                                          | 17 |

|     | 2.4.3 Parallel Port                                     | 18 |

|     | 2.4.4 Serial Ports                                      | 20 |

|     | 2.4.5 Floppy Disk Interface                             |    |

| 2.5 | INTEGRATED DEVICE ELECTRONICS (IDE) HARD DISK INTERFACE |    |

|     | 2.5.1 IDE Interface SETUP                               |    |

|     | 2.5.2 IDE Interface Connector                           |    |

| 2.6 | SCSI INTERFACE                                          |    |

|     | 2.6.1 Normal Use of SCSI                                |    |

|     | 2.6.2 The Ampro SCSI BIOS                               |    |

|     | 2.6.3 SCSI Interface Configuration                      | 27 |

| 2.7 | AT EXPANSION BUS                                        |    |

|     | 2.7.1 Onboard MiniModule Header and Bus Expansion       |    |

|     | 2.7.2 Using Standard PC and AT Bus Cards                | 29 |

|     | 2.7.3 Bus Expansion Guidelines                          |    |

|     | 2.7.4 Expansion Bus Connector Pinouts                   | 30 |

|     | 2.7.5 Interrupt and DMA Channel Usage                   | 34 |

|     |                                                         |    |

| Ch  | apter 3 - Software Configuration                        |    |

|     | INTRODUCTION                                            | 1  |

|     | 3.1.1 Conventions                                       | 1  |

| 3.2 | OPERATION WITH DOS                                      | 1  |

|     | 3.2.1 Configuration Options                             |    |

|     | 3.2.2 Little Board/386SX-IIA Utilities Overview         |    |

|     | 3.2.3 The Ampro SETUP Function                          |    |

|     | DESCRIPTION                                   | 3   |

|-----|-----------------------------------------------|-----|

|     | INTERACTIVE MODE OF OPERATION                 | 4   |

|     | 3.2.4 EMS Option                              | .11 |

| 3.3 | USING A PARALLEL PRINTER                      | .11 |

| 3.4 | USING THE SERIAL PORTS                        | .11 |

|     | 3.4.1 Serial Port Initialization              | .11 |

|     | 3.4.2 Serial Console Option                   | .12 |

|     | 3.4.3 Using a Serial Modem                    | .13 |

| 3.5 | USING FLOPPY DRIVES                           | .13 |

|     | 3.5.1 Drive Parameter Setup                   | .13 |

|     | 3.5.2 Single-Floppy Configurations            | .14 |

| 3.6 | USING SCSI HARD DISK DRIVES                   | .14 |

|     | 3.6.1 Drive Parameter Setup                   | .14 |

|     | 3.6.2 Preparation for DOS Use                 | .15 |

| 3.7 | USING IDE HARD DISK DRIVES                    | .15 |

| 3.8 | WATCHDOG TIMER                                | .16 |

|     |                                               |     |

| Ch  | apter 4 - Advanced Topics                     |     |

|     | INTRODUCTION                                  |     |

| 4.2 | OVERALL ARCHITECTURE                          | 1   |

|     | 4.2.1 Standard AT Compatible Functions        | 1   |

|     | 4.2.2 Unique Functions                        | 2   |

|     | 4.2.3 System Memory Map                       | 2   |

|     | 4.2.4 System I/O Map                          |     |

| 4.3 | AT MOTHERBOARD LOGIC                          | 4   |

|     | 4.3.1 CPU                                     | 4   |

|     | 4.3.2 ROM BIOS Socket                         | 4   |

|     | 4.3.3 Powerfail Handling                      | 4   |

|     | 4.3.4 DRAM and System Performance             |     |

|     | 4.3.5 Interrupt Controllers                   |     |

|     | 4.3.6 DMA Controllers                         | 6   |

|     | 4.3.7 Programmable Timers                     | 7   |

|     | 4.3.8 Keyboard Interface                      |     |

|     | 4.3.9 Speaker Interface                       |     |

|     | 4.3.10 Battery-Backed Clock                   |     |

|     | 4.3.11 AT Expansion Bus                       |     |

| 4.4 | SUPER I/O CONTROLLER                          |     |

|     | 4.4.1 Floppy Disk Controller                  |     |

|     | 4.4.2 Serial Controller                       |     |

|     | 4.4.3 Parallel Controller                     |     |

|     | INTEGRATED DEVICE ELECTRONICS (IDE) INTERFACE |     |

| 4.6 | SMALL COMPUTER SYSTEM INTERFACE (SCSI)        |     |

|     | 4.6.1 SCSI Hard Disk Support                  |     |

|     | 4.6.2 Ampro SCSI BIOS                         |     |

| 4.7 | BYTE-WIDE MEMORY SOCKETS                      |     |

|     | 4.7.1 The Byte-Wide Sockets                   |     |

|     | 4.7.2 Accessing Large Devices                 |     |

|     | 4.7.3 Byte-Wide Socket Signals                |     |

|     | 4.7.4 Write Protection                        |     |

|     | 4.7.5 Flash EPROM Programming                 | .16 |

## Little Board/386SX-IIA

| 4.8 CONFIGURATION EEPROM                                         |          |

|------------------------------------------------------------------|----------|

| 4.10 WATCHDOG TIMER                                              |          |

| THE WITCHESON TRIBLE                                             |          |

| FIGURES                                                          |          |

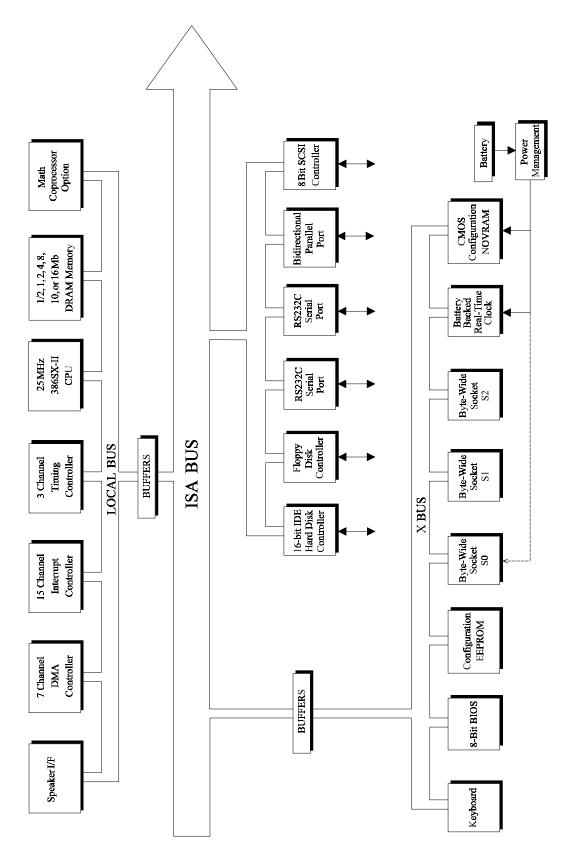

| Figure 1-1 Little Board/386SX-IIA Block Diagram                  |          |

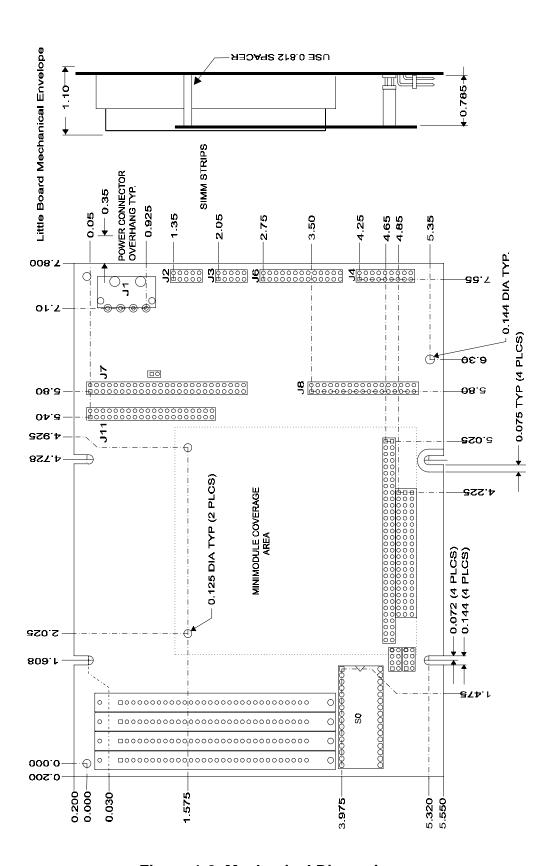

| Figure 1-2 Mechanical Dimensions                                 |          |

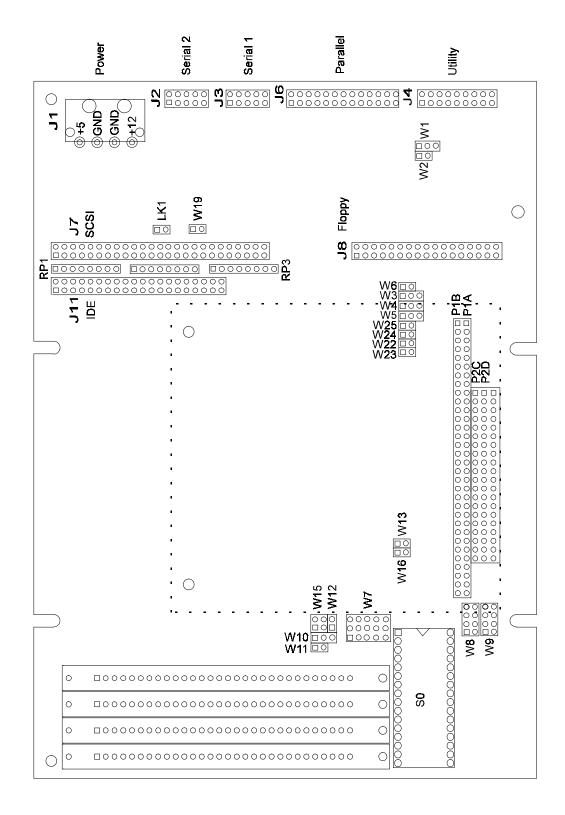

| Figure 2-1 Connector and Jumper Locations                        |          |

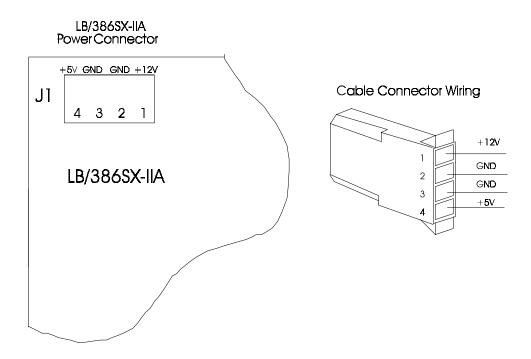

| Figure 2-2 Power Connector Wiring                                |          |

| Figure 2-3 Using a 28-Pin Device in a 32-Pin Socket              |          |

| Figure 2-4 EPROM Jumpering for SO                                |          |

| Figure 2-5 Flash EPROM Jumpering for S0                          |          |

| Figure 2-7 EPROM Jumpering for S1 and S2                         |          |

| Figure 2-8 Flash EPROM Jumpering for S1 and S2                   |          |

| Figure 2-9 Stacking MiniModules on the Little Board/386SX-IIA    |          |

| Figure 2-9 Stacking Willinwoodules on the Little Board/3005A-11A | 29       |

|                                                                  |          |

| TABLES                                                           |          |

| Table 2-1. Connector Usage Summary                               |          |

| Table 2-2. Configuration Jumper Summary                          |          |

| Table 2-3. SETUP Options                                         |          |

| Table 2-4. Power Connector (J1)                                  |          |

| Table 2-5. J1 Mating Connector                                   |          |

| Table 2-6. DRAM Configurations                                   |          |

| Table 2-7. Typical Byte-wide Devices                             |          |

| Table 2-8. Window Size and Address Selection                     |          |

| Table 2-9. Watchdog Timer Configuration                          |          |

| Table 2-10. Video Mode Options                                   |          |

| Table 2-11. Utility Connector (J4)                               |          |

| Table 2-12. J4 and J5 Mating Connector                           |          |

| Table 2-13. Keyboard Connector (J5)                              |          |

| Table 2-14. Parallel Port Connector (J6)                         |          |

| Table 2-16. Parallel Port Address Configuration                  |          |

| Table 2-17. Parallel Port Interrupt Selection                    |          |

| Table 2-18. Serial Port Connectors (J2, J3)                      |          |

| Table 2-19. J2 and J3 Mating Connector                           |          |

| Table 2-20. Supported Floppy Formats                             |          |

| Table 2-21. Floppy Disk Interface Connector (J8)                 |          |

| Table 2-22. J8 Mating Connector                                  |          |

| Table 2-23. IDE Drive Interface Connector (J11)                  |          |

| Table 2-24. J11 Mating Connector                                 |          |

| Table 2-25. SCSI Interface Connector (J7)                        |          |

| Table 2-26. J7 Mating Connector                                  |          |

| Table 2-27A. AT Expansion Bus Connector, A1-A32 (P1A)            |          |

| Table 2-27B. AT Expansion Bus Connector, B1-B32 (P1B)            |          |

| Table 2-27C. AT Expansion Bus Connector, C0-C19 (P2C)            |          |

| Table 2-27D. AT Expansion Bus Connector, D0-D19 (P2D)            | 34       |

| Table 2-28. Interrupt Channel Assignment                         |          |

| Table 2-29. DMA Channel Assignment                               | 35       |

| Table 3-1 Configuration Parameters                               | $\Delta$ |

| Table 3-2. | SETUP Pages                                | 5 |

|------------|--------------------------------------------|---|

|            | Required Commands                          |   |

|            | Little Board/386SX-IIA Memory Map          |   |

| Table 4-2. | Little Board/386SX-IIA I/O Map             | 3 |

|            | Interrupt Channel Assignment               |   |

|            | DMA Channel Assignment                     |   |

|            | Timer Assignment                           |   |

|            | Parallel Port Use                          |   |

|            | Parallel Port Register Bits                |   |

|            | Segment Addressing in Large Memory Devices |   |

|            | Byte-Wide Jumper Pin Signals               |   |

|            | , , ,                                      |   |

## CHAPTER 1

## INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

The Little Board <sup>TM</sup>/386SX-IIA is a high performance, 32-bit 80386SX based AT-compatible single board microcomputer system that requires no more space than a half height 5-1/4 inch disk drive. This unique *single board system* is functionally equivalent to an 80386SX AT motherboard and three or four expansion cards. It runs standard IBM/PC and PC/AT software. This includes disk operating systems such as DOS, UNIX, QNX, VRTX, OS9000, FlexOS, and so forth. It also runs languages such as C, Pascal, Fortran, Basic, and industrial and commercial application software.

The Little Board/386SX-IIA is ideal for embedded applications that require PC/AT software, hardware, and bus compatibility. The Little Board/386SX-IIA also features low power consumption, small size, and high reliability over a wide temperature range. The ability to use EPROM, Flash EPROM, or SRAM as solid state disk drives instead of normal disk drives makes it well suited to harsh environments.

Typical applications for the Little Board/386SX-IIA include:

| Data acquisition and control | Telecommunications    |

|------------------------------|-----------------------|

| Diskless workstations        | Network servers       |

| Portable instruments         | Security systems      |

| Remote data logging          | Machine control       |

| Protocol conversion          | Intelligent terminals |

| Point-of-sale terminals      | Medical instruments   |

The board's dimensions are: 5.75 inches x 8 inches x 1.1 inches. It uses a powerful 25 MHz 80386SX microprocessor, with standard DMA, timers, and interrupt controllers. It accepts 512K to 16M bytes of onboard, parity-checked DRAM. It has a full complement of AT compatible controllers including peripheral controllers for serial, parallel, keyboard, speaker, and floppy disk interfacing. There is a PLCC socket for a math coprocessor. The BIOS features Shadow RAM capability for fast execution of ROM BIOS and video BIOS. Three industry standard system expansion options -- a PC/104 Version 2 bus, a Small Computer System Interface (SCSI), and an Integrated Device Electronics (IDE) interface -- enhance system expandability.

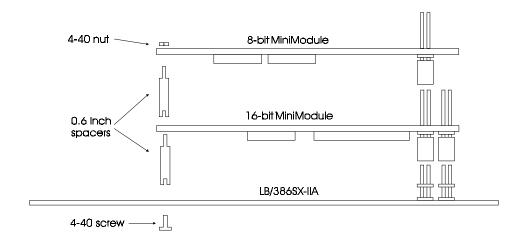

You can easily expand the system by stacking Ampro MiniModule<sup>TM</sup> products on the Little Board/386SX-IIA. They attach directly to the bus interface connector J9. When installed, one onboard MiniModule fits entirely within the board's space envelope. Additional modules increase system thickness by 0.8 inches each. Ampro also offers several methods to add conventional PC and AT expansion cards to the Little Board/386SX-IIA.

The ROM BIOS includes support for SCSI devices. The SCSI BIOS feature allows the use of a variety of hard disks, floppy drives, tape drives, and other SCSI devices. The SCSI BIOS makes system integration, maintenance, and upgrade much easier.

The Little Board/386SX-IIA also provides an interface for one or two Integrated Device Electronics (IDE) hard disk drives. These drives have the hard disk controller built-in. You can easily install an AT hard drive and drive controller by connecting an IDE drive to the IDE interface. Manufacturers offer a large variety of IDE hard disks.

#### Little Board/386SX-IIA

The board provides sockets for EPROM, Flash EPROM or SRAM devices that you can use as one or more bootable DOS compatible Solid State Disk (SSD) drive(s). SSD drives offer improved speed, reliability, and ruggedness, and reduced power consumption and cost compared to conventional magnetic media drives. Ampro's optional SSD support software converts DOS based applications into EPROM format automatically, without special programming. The board has three byte-wide sockets. You can add more with one or more Ampro SSD expansion modules.

Compatibility is a key advantage of the **Little Board/386SX-IIA**. Full AT compatibility allows it to run the thousands of software applications and utility packages developed for the IBM PC and PC/AT. Language compilers, debugging aids, and software support packages for graphics, windowing, multi-tasking, and user interfaces are readily available. There is also a large and growing selection of DOS programs for industrial and commercial applications. These include communications, data acquisition and control, terminal emulation, and protocol conversion, among others.

The Little Board/386SX-IIA is a member of Ampro's growing family of IBM compatible single board systems. The Little Board family offers a broad range of price, performance, and features in a consistent physical and functional format. Thus, as an OEM or system integrator, you can maximize cost effectiveness with Ampro's family of compatible single board systems as the basis of your system design.

## 1.2 LITTLE BOARD/386SX-IIA FEATURES

#### A Complete AT Compatible System on One Board.

- All the functions of a motherboard and 3-4 expansion cards in the space of a half-height 5-1/4 inch disk drive

- Runs standard IBM PC and PC/AT software, including:

- -- Disk Operating Systems

- --Languages (C, Pascal, Fortran, Basic, ...)

- --Industrial and commercial application software

- Standard AT DMA, timers, and interrupt controllers

- Complete onboard system memory: 512K, 1M, 2M, 4M, 8M, 10M, or 16M bytes DRAM, and up to 2M bytes of EPROM, 512K of SRAM, or 1.5M of Flash EPROM

- Complete set of AT-compatible peripheral ports and controllers:

- --Floppy controller supports 250K byte and 500K byte/sec 3-1/2 inch and 5-1/4 inch floppy drives

- --Two RS232C serial ports, parallel printer port, keyboard port, and speaker port

- --Battery-backed real time clock

- -- IDE hard disk interface

- --SCSI controller and BIOS support for SCSI peripherals including hard disks

- **Expansion options:**

- -- Most popular display controllers: VGA, Super VGA, CRT and flat panel

- -- Additional dual-serial/parallel interface

- --Ethernet and Ethernet Twisted Pair LAN interfaces

- --Solid State Disk expansion

- --Future onboard modules available (contact factory)

- Industrialized ROM BIOS, with support for a variety of SCSI devices (hard disk, tape, and so forth) and bootable Solid State Disk

#### **Ideal for Embedded Applications**

- Low power (mostly CMOS):

- --Uses only 5 watts of power with 1M byte of DRAM installed

- --Single supply operation (+5V)

- Wide operating temperature range (0-70° C)

- Reliable:

- --Low component count

- --No backplanes or edgecard connectors required

- Onboard bootable Solid State Disk drive (EPROM/NOVRAM/Flash EPROM) option allows diskless DOS operation

- Same form-factor and mounting dimensions as a 5-1/4 inch disk drive

- Two Industry Standard Expansion Buses

- --AT bus (header) for connection of standard IBM PC, PC/AT, and PC/104 expansion cards

- --SCSI bus for addition of Disk/Tape/Optical drives, Scanners, and other peripheral devices

## 1.3 LITTLE BOARD/386SX-IIA SPECIFICATIONS

#### **CPU**

- 25 MHz 80386SX microprocessor

- Socket for 25 MHz math coprocessor

#### **Onboard Memory**

- 512K, 1M, 2M, 4M, 8M, 10M or 16M bytes DRAM with parity

- Award ROM BIOS with Ampro extensions (with shadowing capability)

- Three 32-pin byte-wide sockets. Two PLCCs, one DIP.

- Flexible addressing and window size

- PLCC usable with:

- --128K to 1M byte EPROMs

- --32K to 512K Flash EPROMs

#### DIP usable with:

- --32K to 1M byte EPROMs

- --32K to 512K byte Flash EPROMs

- --32K to 512K byte SRAMs. Onboard battery makes SRAM storage nonvolatile

- 2K bit serial EEPROM for system parameter storage, with 512 bits for OEM use.

## **AT-Compatible Controllers**

- Standard DMA, interrupt and counter-timer support:

- 7 DMA channels

- 15 interrupt channels

- 3 programmable counter-timers

- Two RS232 serial ports

- 16C550-type UARTs

- 16 byte FIFO buffers

- Parallel printer port

- 8 bidirectional data lines for digital I/O

- IEEE 1284 enhanced mode available

- AT keyboard port

- Speaker port 100 mW

- Standard battery-backed real time clock and CMOS RAM

- AT-compatible 5-1/4 inch and 3-1/2 inch floppy controller:

- 2 drive selects, 1-2 sided, 250/500K byte/sec data rates

- BIOS supports all standard formats (360K /720K /1.2M /1.44M bytes)

#### Little Board/386SX-IIA

Reliable all-digital phase-locked loop and write precompensation Disk change support

#### **SCSI Interface**

- Full ANSI X3.131 (SCSI) compatible

- Uses 53C80 SCSI asynchronous controller

- Up to 400K byte/sec with SCSI BIOS

## **Physical**

- $8.0 \times 5.75 \times 1.1$  inches (5-1/4 disk drive form factor)

- Provision for system expansion with one or more onboard Ampro MiniModules.

- Power required:

- +5V ±5% at 1.07A (1M DRAM)

- 6-layer PCB using latest surface mount technology

- Operating environment:

- --0-70° C (with adequate airflow)

- --5-95% relative humidity (non-condensing)

- Storage temperature: -55° to +85° C

- Weight: 9.6 oz. (272 gm)

Figure 1-1 Little Board/386SX-IIA Block Diagram

**Figure 1-2 Mechanical Dimensions**

## **CHAPTER 2**

## HARDWARE CONFIGURATION

## 2.1 INTRODUCTION

This chapter covers configuration of the Little Board/386SX-IIA and its integration with a variety of onboard and peripheral devices. Standard onboard functions include DRAM, battery-backed real-time clock, and CPU speed control. Options include a math coprocessor socket, three byte-wide device sockets, and onboard expansion capability, including the Ampro MiniModules. Many of the board's functions are software controlled. This manual presumes use of the standard Ampro ROM BIOS. Peripheral devices include keyboards, monitors, printers, modems, floppy and hard disk drives, and other peripherals. It includes data on the board's connector signals and pinouts, external device requirements, interconnection cable wiring, and board configuration.

#### 2.1.1 Interface Connectors

Figure 2-1 shows the location of the interface connectors (J1-J11) and configuration jumpers (W1-W25). Table 2-1 summarizes the use of the connectors. The sections on each interface give connector pinouts, signal definitions, and mating connector part numbers.

Many of the connectors have a key pin removed. Block the corresponding socket to minimize the chance of misaligning the connector. Table 2-1 lists key pins, and Figure 2-1 shows their locations.

| CONNECTOR FUNCTION                            |                       | SIZE   | KEY PIN |

|-----------------------------------------------|-----------------------|--------|---------|

| J1                                            | Power input           | 4-pin  | none    |

| J2                                            | Secondary serial port | 10-pin | 10      |

| J3                                            | Primary serial port   | 10-pin | 10      |

| J4 (*)                                        | Utility               | 12-pin | none    |

| J5 (*)                                        | Keyboard              | 6-pin  | none    |

| J6                                            | Parallel port         | 26-pin | 26      |

| J7                                            | SCSI port             | 50-pin | 25      |

| J8                                            | Floppy drive          | 34-pin | 6       |

| P1A, P1B                                      | AT Bus                | 64-pin | B10     |

| P2C, P2D                                      | AT Bus                | 40-pin | C19     |

| J11 IDE drive interface                       |                       | 40-pin | 20      |

| (*) A single 18-pin array comprises J4 and J5 |                       |        |         |

**Table 2-1. Connector Usage Summary**

Figure 2-1 Connector and Jumper Locations

The I/O connectors are dual-row headers for use with flat ribbon (IDC) or discretely wired connectors. You can use a specialized connector or PC board assembly. You might do this to eliminate cables, meet packaging requirements, add EMI filtering, or customize your installation in other ways. The PC/AT expansion bus appears on two connectors (J9 and J10). You can expand the system with onboard MiniModules, or use conventional or custom expansion hardware, including solutions available from Ampro.

## 2.1.2 Jumper Configuration Options

The Little Board/386SX-IIA requires no special jumpering for standard AT operation. You can connect the peripherals and operate it immediately. The only jumpers you need be concerned with are those that configure the byte-wide sockets for the devices you use.

The jumper arrays are designated W1, W2, and so forth. A square solder pad identifies pin 1 of each array. Table 2-2 is a summary of jumper use. A slash (1/2) means to short the indicated pins.

| JUMPER<br>GROUP | FUNCTION                           | DEFAULT                |

|-----------------|------------------------------------|------------------------|

| W1              | Watchdog Timer output selection    | OFF                    |

| W2              | Power Fail NMI enable              | OFF                    |

| W3              | EPP/ECP DACK* select               | OFF                    |

| W4              | EPP/ECP DRQ select                 | OFF                    |

| W5              | Parallel Port IRQ selection (IRQ7) | 1/2                    |

| W6              | Floppy Drive DRQ2 enable           | ON                     |

| W7              | Byte-wide S0 config. (128K SRAM)   | 4/5, 7/10, 8/11, 13/14 |

| W8              | Byte-wide S1 config. (+12V Flash)  | 3/4, 5/6               |

| W9              | Byte-wide S2 config. (+12V Flash)  | 3/4, 5/6               |

| W10             | Battery backed S0 (no backup)      | 2/3                    |

| W11             | Battery backed S0 (no battery)     | OFF                    |

| W12             | SCSI enable                        | ON                     |

| W13             | +12V Flash programming power       | OFF                    |

| W15             | BIOS Chip selection (U24/U28 BIOS) | 1/2, 3/4               |

| W16             | BIOS Vpp enable                    | OFF                    |

| W19             | SCSI Terminator power              | OFF                    |

| W22             | SCSI Terminal Count                | OFF                    |

| W23             | SCSI DRQ3                          | ON                     |

| W24             | SCSI DACK3*                        | ON                     |

| W25             | SCSI IRQ5                          | OFF                    |

**Table 2-2. Configuration Jumper Summary**

## 2.1.3 SETUP Options

To configure the board, install the appropriate jumpers, and run SETUP. The SETUP function, included in the ROM BIOS and on the Little Board/386SX-IIA Utilities diskette, stores the configuration parameters in a 2 Kbit nonvolatile EEPROM and in the battery backed CMOS RAM in the real time clock. These two memories comprise the Configuration Memory. During the boot process, the ROM BIOS initializes system parameters based on the contents of these memories. The contents of the CMOS RAM (except time and date) are also stored in the EEPROM. Even without battery power, the SETUP parameters are saved.

You can enter SETUP two ways. One is a hot-key entry (pressing CTRL-ALT-ESC at the same time) just prior to boot. The other is through SETUP.COM, a program on the utilities diskette. You can initiate SETUP from the command line by entering SETUP <ENTER> with the utilities diskette in the default floppy drive. Use of SETUP is covered in detail in Chapter 3.

Table 2-3 lists the user accessible functions controlled by the Configuration Memory.

Floppy drive quantity and type DOS date and time Hard disk drive quantity and type Video controller mode and type Memory size and configuration Halt on errors option BIOS and video BIOS shadowing CPU speed options Enable/Disable Ampro extended BIOS Enable/disable serial ports Enable/Disable parallel port Enable/disable floppy interface Enable/Disable IDE interface Mono/color video jumper Byte-wide socket sizes and locations Byte-wide default at power up Enable/disable serial boot loader Watchdog timer timeout selection Enable/disable hot-key SETUP function Enable/disable SCSI hard disk services Hard disk DOS mapping Default boot device selection **Extended Serial Console configuration** Serial Console installation

**Table 2-3. SETUP Options**

Using the SETUP program, you can load system setup parameters from a disk file. This is useful when configuring production systems.

## 2.2 DC POWER

The pinout of the power connector, J1, is identical with the power connectors on almost all 5-1/4 inch disk drives. See Figure 2-1 and Figure 2-2. Refer to Table 2-4 for power connections and mating connector information, and Figure 2-2 for typical connector wiring.

## **CAUTION**

Be sure the power plug is wired correctly before applying power to the board! See Figure 2-2.

| PIN | SIGNAL | FUNCTION        |  |

|-----|--------|-----------------|--|

| 1   | +12VDC | +12VDC ±5%      |  |

| 2   | Ground | Ground return   |  |

| 3   | Ground | Ground return   |  |

| 4   | +5VDC  | +5VDC ±5% input |  |

Table 2-4. Power Connector (J1)

| CONNECTOR<br>TYPE | MATING CONNECTOR                          |  |

|-------------------|-------------------------------------------|--|

| DISCRETE WIRE     | AMP HOUSING 1-480424-0<br>AMP PIN 60619-1 |  |

Table 2-5. J1 Mating Connector

## 2.2.1 Power Requirements

The Little Board/386SX-IIA requires only +5 VDC ( $\pm 5\%$ ) for operation. The  $\pm 9$  volts for the RS232 ports is generated onboard. However, if you use +12 volt Flash EPROMS, you must supply them with 12 volts during programming. Consult the documentation for your Flash EPROMs for their programming current and voltage requirements.

The exact power requirements of the Little Board/386SX-IIA depend on several factors: the functions present on the board (quantity of DRAM, byte-wide memory devices, math coprocessor); SCSI bus termination; CPU speed; and the peripherals connected. For example, AT keyboards draw their power from the board. MiniModules or other expansion products connected to the AT expansion bus may draw their power through the Little Board/386SX-IIA power connector. A fully populated Little Board/386SX-IIA with 1 Mbyte DRAM, but with no math coprocessor or expansion modules installed, draws about 1.07 Amp (5.35 watts). The SCSI bus terminators draw about 800 milliwatts. Remove them unless you use the SCSI port.

Figure 2-2 Power Connector Wiring

If you use a switching power supply, be sure it regulates properly with this load. If not, consult the manufacturer about additional loading, or use a linear power supply or batteries.

## 2.2.2 Powerfail Options

The Little Board/386SX-IIA includes power failure monitoring. Configuring the board for the power failure options involves jumper arrays W2 and W11. If you short W2, the powerfail circuitry is enabled. When the supply voltage falls below 4.7 volts, the logic produces a non-maskable interrupt (NMI). The BIOS detects the NMI and displays the message "Power Fail NMI" on the screen. You have two options at this point. One is to mask the NMI and continue. The other is to reboot the system. If you want another response to the NMI, provide your own NMI handler and patch the NMI interrupt vector address to install it. This is covered in Chapter 4. If you don't want the power fail NMI, leave W2 open.

If the supply voltage falls below 4.5 volts, the logic initiates a hardware reset (the same as if the Reset button were pressed). This reset remains asserted for about 100 mS after the voltage returns to above 4.5 volts.

Jumper arrays W10 and W11 determine whether backup battery power is routed to byte-wide socket S0 during a power failure. To enable Battery Backup, set jumpers W10 (1/2) and W11 ON. To disable Battery Backup set W10 (2/3) and W11 OFF. With the first jumper setting (with jumper W11 ON and W10 (1/2)), the power monitor circuit switches the power supply for byte-wide socket S0 from the +5 volt power supply (Vcc) to the backup battery. This effectively makes an SRAM in S0 into non-volatile RAM (NOVRAM). However, if you use an EPROM or Flash EPROM in S0, set W11 to OFF and W10 (2/3). With this setting the power supply to S0 is always Vcc, and battery power is not wasted.

While Battery Backup is enabled, the chip select for S0 is held off while power is below 4.7 volts. This is to prevent writing bad data to S0 when the voltage is low.

## 2.2.3 Backup Lithium Battery Considerations

## **CAUTION**

Lithium batteries can explode if mistreated. Do not attempt to recharge a Lithium battery. See manufacturers instructions for proper disposal of used batteries. Be careful not to overheat the battery when changing it.

With only the real time clock drawing current, this battery should last 10 years. If it supplies only the clock, replace the battery every ten years as a routine maintenance procedure.

If the battery supports an SRAM, calculate battery life and replace the battery as necessary. To calculate battery life, add the current drawn by the SRAM and the current the clock draws (1 uA) and divide the 750 milliamphour battery rating by the sum. Then, multiply the result of that calculation by the duty cycle of the battery, that is, the percentage of time the system is off and the battery is supplying the current.

Here is the formula for calculating battery life:

$$\frac{750 \text{ milliamp - hours}}{1\mu A + \text{SRAM backup current}} \times \text{Duty Cycle}$$

## 2.2.4 Cooling Requirements

Although this is a low power system, it is important to provide adequate air flow for cooling. If you use a math coprocessor, system cooling becomes even more important. The CPU, DRAM, and math coprocessor draw most of the power and generates most of the heat.

## 2.3 ONBOARD DEVICE OPTIONS AND CONFIGURATION

This section includes the configuration and installation of onboard devices and options including the DRAM and the byte-wide memory devices, the math coprocessor, the serial ports, the parallel port and the floppy, SCSI, and IDE controllers. It includes system expansion with MiniModules and conventional expansion boards.

## 2.3.1 DRAM

The board has positions for four single in-line memory modules (SIMMs). You need not install memory in all four positions. Use either 256 Kb x 9, 1 Mb x 9, or 4 Mb x 9 SIMM modules, depending on the amount of memory desired. Table 2-6 gives possible DRAM configurations.

#### NOTE

System performance depends on DRAM configuration. For maximum speed, install enough DRAM for shadowing.

One way to improve system performance is to use shadowing. When the system operates directly from ROM, it accesses an 8-bit device at 8 MHz. Shadowing is the copying of the ROM contents to RAM where they are accessed as 16-bit wide data and at normal system speed. Shadowing the system BIOS or the video BIOS substantially enhances system performance. Shadowing is possible with 1M byte of onboard DRAM or more. See Table 2-6 for a summary of memory configuration.

| MEMORY                                             | BANK 0 (U1/2) | BANK 1 (U3/4) | SHADOW |

|----------------------------------------------------|---------------|---------------|--------|

| SIZE                                               | SIMMs         | SIMMs         |        |

| 512 K                                              | 256 K         | None          | No     |

| 1 M                                                | 256 K         | 256 K         | Yes    |

| 2 M                                                | 1 M           | None          | Yes    |

| 4 M                                                | 1 M           | 1 M           | Yes    |

| 8 M                                                | 4 M           | None          | Yes    |

| 16 M                                               | 4 M           | 4 M           | Yes    |

| All memory must have access times of 70 nS or less |               |               |        |

**Table 2-6. DRAM Configurations**

The Little Board/386SX-IIA can directly address 16M bytes of system RAM. This is limited by the microprocessor and the PC/AT bus specification. You can locate memory on the board or on the AT expansion bus. In most cases it is preferable to add onboard memory with SIMMs. This is because access to RAM located on the bus is slower than the onboard memory due to memory configuration and to the wait states added to bus operations.

Onboard memory is allocated as follows:

In a 512K byte system, all the memory is mapped to the DOS region 00000h to 7FFFFh.

In larger systems, the first 640K bytes of DRAM are assigned to the DOS region 00000h to 9FFFFh, leaving 384K bytes of the first 1M byte unused. You can *only* use that 384K bytes to shadow ROM BIOS and video BIOS.

The remaining memory is mapped to extended memory starting at the 1 megabyte boundary, 100000h.

The BIOS measures the amount of memory installed and displays it on the first page of SETUP. Saving SETUP automatically saves the amount of memory in the Configuration Memory. If you change the amount of memory installed, you must run SETUP again to save the new information in the Configuration Memory.

Some programs are designed to use *expanded* or *EMS* memory. You can convert extended memory into expanded memory. MS-DOS and DR DOS include utilities that conform to the LIM 4.0 specification for EMS memory.

## 2.3.2 Math Coprocessor

You can install an 80387SX or equivalent floating point math coprocessor in U6. The coprocessor must be rated for the same speed as the CPU. The coprocessor operates in synchronous mode, using the same clock as the CPU. A 25 MHz 80387SX may be used

## NOTE

Some math coprocessors dissipate up to 1 watt. Be sure to provide adequate clearance for air flow. The coprocessor socket and the silkscreening show how to install the coprocessor. Be careful to align the device correctly to prevent damage.

## 2.3.3 Byte-Wide Sockets

The Little Board/386SX-IIA has three onboard byte-wide memory sockets. One is a 32-pin DIP, and the other two are 32-pin PLCC (Plastic Leaded Chip Carrier) sockets. All of these sockets accept a variety of EPROM and Flash EPROM devices. The DIP socket (S0) also accepts SRAMs and nonvolatile RAM (NOVRAM) devices. You can make an SRAM in S0 non-volatile with the connection of battery backup power by shorting W11-2/3. You can use these devices for simple program storage, BIOS extensions, or as Solid State Disk (SSD) drives. Table 2-7 shows some byte-wide devices and in which sockets you can use them.

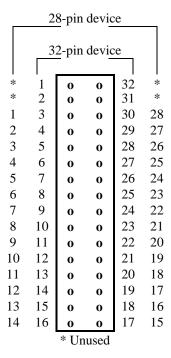

You can use either 28- or 32-pin devices in S0. If you use a 28-pin device, install it so device pin 1 is in socket pin 3 and so forth. See Figure 2-3.

## NOTE

When a byte-wide device is enabled, the memory address space it uses is unavailable for other devices. You must disable the byte-wide sockets in SETUP before you can use the memory space for other purposes.

Figure 2-3 Using a 28-Pin Device in a 32-Pin Socket

| DEVICE TYPE           | SIZE          | PART NUMBER | USABLE IN  |  |  |

|-----------------------|---------------|-------------|------------|--|--|

|                       | NORMAL EPROMS |             |            |  |  |

| EPROM32               | 32 Kbyte      | 27C256      | S0         |  |  |

| EPROM64               | 64 Kbyte      | 27C512      | S0         |  |  |

| EPROM128              | 128 Kbyte     | 27C010      | S0, S1, S2 |  |  |

| EPROM256              | 256 Kbyte     | 27C020      | S0, S1, S2 |  |  |

| EPROM512              | 512 Kbyte     | 27C040      | S0         |  |  |

| EPROM1024             | 1024 Kbyte    | 27C080      | S0         |  |  |

| PAGE ADDRESSED EPROMS |               |             |            |  |  |

| PPROM64               | 64 Kbytes     | 27513       | S0         |  |  |

|                       | STATIC RAMS   |             |            |  |  |

| SRAM32                | 32 Kbytes     | 43256       | S0         |  |  |

| SRAM128               | 128 Kbytes    | 628128      | S0         |  |  |

| SRAM512               | 512 Kbytes    | 434000      | S0         |  |  |

| FLASH EPROMS          |               |             |            |  |  |

| EPROM128              | 128 Kbytes    | 28F010      | S0, S1, S2 |  |  |

| EPROM256              | 256 Kbytes    | 28F020      | S0, S1, S2 |  |  |

Maximum access time for byte-wide devices is 250 nS.

**Table 2-7. Typical Byte-wide Devices**

After installing the devices, use SETUP to specify the size and starting address of each one, and which device the BIOS enables upon system initialization. Table 2-8 gives the possible sizes and address ranges for the byte-wide devices.

## **Direct Program Access**

Application software can access the memory devices in S0, S1 and S2 if the program knows about them. To access a byte-wide socket you must enable it individually with a BIOS call to access the device. See Chapter 4 for more details on this BIOS call.

| WINDOW  | ADDRESS      |

|---------|--------------|

| DISABLE | N/A          |

| 64K     | D0000-DFFFFh |

| 64K     | E0000-EFFFFh |

| 128K    | D0000-EFFFFh |

Table 2-8. Window Size and Address Selection

The system can run its entire application from memories in the byte-wide sockets, instead of from disk drives. This technique, known as a ROM BIOS extension, is discussed in Ampro Application Note AAN-8702.

Using the byte-wide sockets can adversely affect system performance. The system can only access one byte-wide device at a time. Also, byte-wide devices are slow as it is operation from 8-bit memory at slow speed. You can improve performance substantially by copying the ROM contents to RAM and running the software directly from RAM.

#### Solid State Disk (SSD) Drives

Using the Ampro Solid State Disk (SSD) Support Software, you can configure a Little Board/386SX-IIA system to boot, operate, and store data using one or more EPROM and/or SRAM solid-state drives under DOS control. You need no custom programming. With the Ampro SSD support software, the byte-wide sockets can serve as individual SSD drives, or a single larger drive. You can use SSD drives in addition to, or instead of normal floppy and hard disk drives. You can increase system SSD capacity by adding one or more of Ampro's SSD expansion modules.

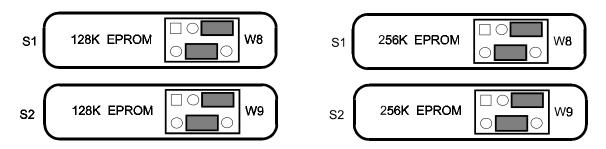

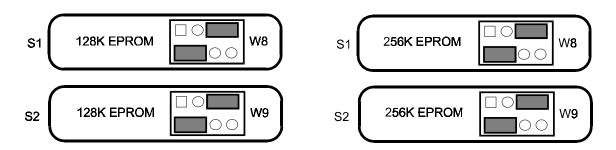

#### **Byte-Wide Socket Configuration**

You must jumper the byte-wide sockets for the devices you install in them. Jumper arrays W7, W10, and W11 configure S0. Array W8 configures S1. Array W9 configures S2. Figures 2-4 to 2-8 list supported memory devices and their jumper settings. See Chapter 4 for a description of the byte-wide socket signals that correspond to each jumper pin. Besides jumpering each socket, you must use SETUP to select which one the BIOS will enable on power up.

## 2.3.4 Battery-Backed Clock

An AT compatible battery-backed real time clock (with CMOS RAM) is standard on the Little Board/386SX-IIA. The clock is powered by a 3.6 volt 1/2 AA Lithium battery soldered to the board. The battery is rated at 750 milliamp-hours. As the clock draws about 5 uA, this battery will support the clock for over ten years.

The factory initializes the real time clock date and time and various parameters in the Configuration Memory for a standard configuration. The factory also sets the date and time, but it may not be set for your time zone. Use the Ampro SETUP utility to change these values as needed (see Chapter 3).

| EPROM<br>(Typical Devices)                            | Pins           | Jumper Diagram           |

|-------------------------------------------------------|----------------|--------------------------|

| 8K EPROM 27C64<br>16K EPROM 27C128<br>8K EEPROM 28C64 | 28             | W11 W10 W7  1 0 3  13 15 |

| 32K EPROM 27C256                                      | 28             | W11 W10 W7 1 0 3 0 0 15  |

| 64K EPROM 27C512                                      | 28             | W11 W10 W7 1 0 3 13 0 15 |

| 128K EPROM 27C010                                     | 32             | W11 W10 W7 3 13 13 15    |

| 256K EPROM 27C020                                     | 32             | W11 W10 W7 3 13 13 15    |

| 512K EPROM 27C040                                     | 32             | W11 W10 W7 3 13 15       |

| 1M EPROM 27C080                                       | 32             | W11 W10 W7 3 13 15       |

| NOTE: W10 and W11 conf                                | igure S0 only. |                          |

Figure 2-4 EPROM Jumpering for S0

## 2.3.5 Using Flash EPROMs

Flash programming power for +12V Flash devices is provided by the external power supply. You need to insure that the +12V supply meets the voltage specifications for programming the +12V Flash device. Programming power is switched under software control so that it is applied only during the actual programming process (to prevent accidental corruption of the data). A utility for programming supported Flash devices is included on the utility disk that is provided with the LB/386SX-II Development Kit.

Some Flash EPROMs draw current through their chip select lines (or other pins) when powered down. If you install a Flash EPROM in socket S0, make sure the jumper on W11 is removed and the jumper on W10 is on 2/3 to prevent premature discharge of the on-board backup battery.

| Flash EPRO<br>Typical Devic                                                                |                                      | Pins       | Jumper Diagram             |

|--------------------------------------------------------------------------------------------|--------------------------------------|------------|----------------------------|

| 32K 5V Flash EPROM                                                                         | 29C256                               | 28         | W11 W10 W7 1 0 3 13 0 15   |

| 32K 5V Flash EPROM                                                                         | 28C256                               | 28         | W11 W10 W7  1 0 3  13 0 15 |

| 64K 5V Flash EPROM<br>128K 5V Flash EPROM<br>256K 5V Flash EPROM<br>512K 5V Flash EPROM    | 29F512<br>29F010<br>29F020<br>29F040 | 32         | W11 W10 W7 1 0 3 13 0 15   |

| 32K 12V Flash EPROM<br>64K 12V Flash EPROM<br>128K 12V Flash EPROM<br>256K 12V Flash EPROM | 28F256<br>28F512<br>28F010<br>28F020 | 32         | W11 W10 W7 3 13 15         |

| NOTE: W10 and W11 conf                                                                     | figure S0 only                       | <i>'</i> . |                            |

Figure 2-5 Flash EPROM Jumpering for S0

## 2.3.6 Using SRAMs

If you install an SRAM in socket S0, you can provide backup power from the battery when power is off by shorting W11 and W10-1/2.

Battery backup is provided for S0 only.

#### Little Board/386SX-IIA

The external battery power is combined with the internal battery using low forward voltage drop Schottky diodes. The 750 milliamp-hour battery provides sufficient current for the onboard real-time clock for a 10 year life, but if you are going to battery-back-up a device in S0, Ampro recommends that you calculate the battery lifetime.

#### Note

Some byte-wide devices draw battery backup current through their chip select lines when power is off. When using memory devices that do not require battery backup power, remove the jumper on W11 and set W10 to 2/3. This prevents the backup battery from being drained prematurely.

| Турі                                  | SRAM<br>cal Device                      | s                  | Pins     | Jumper Diagram           |

|---------------------------------------|-----------------------------------------|--------------------|----------|--------------------------|

| 32K SRAM<br>32K NOVRAM                | 43256<br>Dallas<br>Benchmarq            | DS1235Y<br>BQ4013Y | 28<br>32 | W11 W10 W7 1 0 3 13 0 15 |

| 128K SRAM<br>512K SRAM<br>512K NOVRAM | 628128<br>628512<br>Dallas<br>Benchmarq | DS1650Y<br>BQ4015Y | 32       | W11 W10 W7 3 13 15       |

**NOTE:** W11 and W10 are shown configured for NOVRAMs. To configure W11 and W10 for SRAM battery backup (on S0), install a jumper on W11 and move the jumper on W10 to 1/2. See text for details.

Figure 2-6 SRAM and NOVRAM Jumpering for S0

Figure 2-7 EPROM Jumpering for S1 and S2

Figure 2-8 Flash EPROM Jumpering for S1 and S2

## 2.3.7 Watchdog Timer Option

A unique feature of the onboard clock circuitry is a watchdog timer. You can program this timer to generate an interrupt or reset signal if the programmed time interval expires before the timer is reinitialized. Use SETUP to select the time interval. The options are: Disable, 30 seconds, 60 seconds, and 90 seconds.

The watchdog timer will not work while the system is booting either PC DOS or MS DOS. However, the WATCHDOG utility provided will work normally once the system is booted. Use DR DOS if you require the watchdog timer to operate while the system is booting.

The watchdog timer uses the standard alarm feature of the real time clock. In a standard AT, the alarm output is connected to IRQ8. On the Little Board/386SX-IIA you can connect the alarm output to I/O Channel Check (-IOCHCK) or Reset with W1. I/O Channel Check is the bus signal that triggers a non-maskable interrupt (NMI). Reset is a hard reset signal, the same as pressing the Reset button. For the watchdog timer to generate I/O Channel Check, short W1-1/2. For Reset, short W1-2/3. To disable the watchdog timer, leave W1 open, and select *Disable* in SETUP. See Table 2-9.

If you enable the Watchdog timer in SETUP, but do not install a jumper on W1, IRQ8 turns off the interrupt and the system is unaffected. If you select I/O Channel Check, the timer will generate a message on the screen. If you select Reset, no interrupt handler is required.

| SELECTION | W1   |

|-----------|------|

| Disabled  | Open |

| -IOCHCK   | 1/2  |

| RESET     | 2/3  |

Table 2-9. Watchdog Timer Configuration

## 2.3.8 Video Display Mode

No matter what type of video controller you use -- an onboard MiniModule or a board on the AT expansion bus -- you have to use SETUP to establish the powerup (or reset) video state as color or monochrome. Table 2-10 shows which setting to use for various video modes.

| VIDEO MODE               | SETUP OPTIONS |                   |  |

|--------------------------|---------------|-------------------|--|

|                          | VIDEO         | MONO/COLOR JUMPER |  |

| Mono (MDA or Hercules)   | MONO          | MONO              |  |

| Mono (EGA, or VGA)       | EGA/VGA       | COLOR             |  |

|                          | COLOR 40      |                   |  |

| Color (CGA, EGA, or VGA) | COLOR 80      | COLOR             |  |

|                          | EGA/VGA       |                   |  |

**Table 2-10. Video Mode Options**

When using an EGA or VGA controller for monochrome, set the MONO/COLOR Jumper on the second SETUP screen to "COLOR". When using an EGA or VGA controller in monochrome or CGA mode, set the video controller type on the first SETUP screen to "EGA/VGA".

Be sure to set any appropriate switches or jumpers on the video display controller for the video mode you use. Refer to your video controller's technical manual.

## 2.4 PERIPHERAL CONNECTIONS AND CONFIGURATION

This section covers the interface requirements of the external devices. It provides information on interface and device characteristics, connector pinouts, mating connector part numbers, signal definitions, jumper configuration, and Configuration Memory setup.

## 2.4.1 Utility Connector

Five functions appear on a single 12 pin connector at J4. These are the speaker, external Reset, Power Indicator LED, auxiliary power connections, and a Power Good status input signal. Table 2-11 shows the pinout and signal definitions of the Utility Connector. Connectors J4 and J5 appear on a single 18-pin header array to facilitate use of a single connector for both.

| PIN | SIGNAL NAME | FUNCTION                              |  |  |

|-----|-------------|---------------------------------------|--|--|

| 1   | Speaker +   | Audio signal                          |  |  |

| 2   | Speaker -   | Ground                                |  |  |

| 3   | Ground      | To one side of Reset button           |  |  |

| 4   | Reset       | To other side of Reset button         |  |  |

| 5   | LED Cathode | Ground return                         |  |  |

| 6   | LED Anode   | Current source (+5V through 330 ohms) |  |  |

| 7   | Ground      | Ground return                         |  |  |

| 8   | +12V power  | Connected to J9 pin B9                |  |  |

| 9   | -5V power   | Connected to J9 pin B5                |  |  |

| 10  | -12V power  | Connected to J9 pin B7                |  |  |

| 11  | Ground      | Ground return                         |  |  |

| 12  | POWERGOOD   | Power supply status                   |  |  |

Table 2-11. Utility Connector (J4)

| CONNECTOR TYPE | MATING CONNECTOR                           |           |  |

|----------------|--------------------------------------------|-----------|--|

| RIBBON         | ЗМ                                         | 3473-7010 |  |

| DISCRETE WIRE  | MOLEX HOUSING 22-55-2101<br>PIN 16-02-0103 |           |  |

Table 2-12. J4 and J5 Mating Connector

## Speaker

The board supplies about 100 milliwatts for a speaker on pins 1 and 2 of the Utility Connector. A transistor amplifier buffers the speaker signal. Use a small general purpose 2 or 3 inch permanent magnet speaker with an 8 ohm voice coil. Refer to an AT technical reference manual for custom speaker programming information.

#### **Pushbutton Reset**

Two pins (3 and 4) of the Utility Connector provide connections for an external normally open momentary switch to manually reset the system. Pin 4 is the Reset (active low) input, and pin 3 is the logic ground.

#### **Power Indicator LED**

Two pins (5 and 6) of the Utility Connector provide connections for an external power indicator LED. This output sources 15 mA (+5V through 330 ohms). Pin 5 goes to the LED's cathode and pin 6 to its anode.

#### **AT Bus Power Options**

You can use 4 pins (7, 8, 9, and 10) of the Utility Connector in two ways. You can connect +12V, -5V, and -12V to them to supply power to the board instead of using J1. Or you can power the board from J1 and use these pins to source power to plug-in expansion cards, or other devices in the system.

## 2.4.2 Keyboard

You can connect an AT (*not* PC) keyboard to the keyboard port. The first five pins (1-5) of connector J5 provide this function. Normally, AT keyboards include a cable that terminates in a male 5-pin DIN plug for

connection to an AT. Table 2-13 gives the keyboard connector pinout and signal definitions, and includes corresponding pin numbers of a normal AT DIN keyboard connector.

You can connect pin 6 of J5 to a keyboard inhibit switch. If you ground this pin, the system ignores keyboard inputs. You can use this with key switches for system security.

| J5 PIN | SIGNAL NAME      | DIN PIN |

|--------|------------------|---------|

| 1      | Keyboard clock   | 1       |

| 2      | Keyboard data    | 2       |

| 3      | Key pin          | N/A     |

| 4      | Ground           | 4       |

| 5      | Keyboard power   | 5       |

| 6      | Keyboard inhibit | N/A     |

Table 2-13. Keyboard Connector (J5)

## 2.4.3 Parallel Port

The Little Board/386SX-IIA includes an AT compatible parallel port at J6. Table 2-14 gives this connector's pinout and signal definitions. You can use a flat ribbon cable between the header and a female DB25 connector. The table also gives the connections from the header pins to the DB25 connector.

You can use the parallel port either as a standard PC/AT printer port, or as a bidirectional data bus. Refer to Chapter 4 for information on bidirectional use of this port.

## NOTE

For maximum reliability, keep the cable between the board and the device it drives to 10 feet or less in length.

| SIGNAL<br>NAME | FUNCTION            | IN/OUT | J6<br>PIN | DB25<br>PIN | Drive (mA)<br>(LOW/HIGH) |

|----------------|---------------------|--------|-----------|-------------|--------------------------|

| Data 0         | LSB of printer data | I/O    | 3         | 2           |                          |

| Data 1         | :                   | I/O    | 5         | 3           |                          |

| Data 2         | :                   | I/O    | 7         | 4           |                          |

| Data 3         | :                   | I/O    | 9         | 5           | 24/12                    |

| Data 4         | :                   | I/O    | 11        | 6           |                          |

| Data 5         | :                   | I/O    | 13        | 7           |                          |

| Data 6         | :                   | I/O    | 15        | 8           |                          |

| Data 7         | MSB of printer data | I/O    | 17        | 9           |                          |

| -ERROR         | Printer error       | IN     | 4         | 15          |                          |

| SEL OUT        | Printer selected    | IN     | 25        | 13          |                          |

| PAPER          | Out of paper        | IN     | 23        | 12          | N/A                      |

| -ACK           | Character accepted  | IN     | 19        | 10          |                          |

| BUSY           | Cannot receive data | IN     | 21        | 11          |                          |

| -STROBE        | Output data strobe  | OUT    | 1         | 1           |                          |

| -AUTOFD        | Autofeed            | OUT    | 2         | 14          | 24/0.5                   |

| -INIT          | Initialize printer  | OUT    | 6         | 16          |                          |

| -SEL IN        | Selects printer     | OUT    | 8         | 17          |                          |

| N/A            | Key pin             | N/A    | 26        |             |                          |

| GROUND         | Signal ground       | N/A    | 10,12,    | 18-25       |                          |

|                |                     |        | 14,16,    |             | N/A                      |

|                |                     |        | 18,20,    |             |                          |

|                |                     |        | 22,24     |             |                          |

Table 2-14. Parallel Port Connector (J6)

| CONNECTOR TYPE | MATING CONNECTOR                           |

|----------------|--------------------------------------------|

| RIBBON         | 3M 3473-7010                               |

| DISCRETE WIRE  | MOLEX HOUSING 22-55-2101<br>PIN 16-02-0103 |

**Table 2-15. J6 Mating Connector**

## **Printer Port Configuration**

With SETUP, you can configure the parallel port as the primary port (LPT1), the secondary port (LPT2), or disabled. Table 2-16 lists the parallel port addresses for the primary and secondary port.

| SELECTION | I/O ADDR. |

|-----------|-----------|

| Primary   | 378-37Fh  |

| Secondary | 278-27Fh  |

Table 2-16. Parallel Port Address Configuration

Normally, DOS assigns the name LPT1 to the primary parallel port, and LPT2 to the secondary parallel port (if present). However, DOS scans for both choices (primary and secondary) and if it only finds a secondary port, it assigns LPT1 to that one. Configure the parallel port for the primary assignment shown in Table 2-16, unless the system includes another primary parallel port.

#### Parallel Port Interrupt

Interrupts are seldom used with parallel ports. When they are, the convention is to use IRQ7 with the primary port (LPT1) and IRQ5 with the secondary port (LPT2). You can select the interrupt with W24. Table 2-17 shows the options.

| SELECTION    | W5   |

|--------------|------|

| No Interrupt | OPEN |

| IRQ5         | 2/3  |

| IRQ7         | 1/2  |

**Table 2-17. Parallel Port Interrupt Selection**

#### **Bidirectional Parallel Port Use**

You can use the parallel printer port as a standard AT printer port, or you can use it for general purpose programmable I/O. You can create interfaces for specialized devices with the port's input and output handshake signals, and its 8-bit bidirectional data lines. You might use it for writing data to LCD display panels, scanning custom keyboards, and so forth.

The bidirectional feature is controlled by software. Refer to Chapter 3 for typical system software configuration information, and to Chapter 4 for hardware details regarding nonstandard uses of this interface.

#### **IEEE 1284 Mode Use**

You can set the parallel port to EPP or ECP mode. Jumpers W3 and W4 select the DMA channel. To select DMA channel 1 set jumpers W3 and W4 to (1/2). To select DMA channel 3 set the jumpers to (2/3)

#### 2.4.4 Serial Ports

The Little Board/386SX-IIA provides two standard RS232 serial ports at J2 and J3. Table 2-18 gives the connector pinout and signal definitions for J2 and J3. In addition, the table gives the pins each signal must be wired to for compatibility with DB25 and DB9 connectors. The serial port pinout is arranged so that you can use a flat ribbon cable between the header and a standard DB9 connector. Normally PC serial ports use male DB connectors.

Both ports support software selectable standard baud rates up to 19.2K bits/second (limited by the RS232C specification), 5-8 data bits, and 1, 1.5, or 2 stop bits. The serial ports appear at the standard port addresses of 3F8-3FFh (primary port) and 2F8-2FFh (secondary port), using interrupts IRQ4 and IRQ3, respectively.

You can use the serial ports for printers, modems, terminals, remote hosts, or other RS232C serial devices. Many devices, such as printers and modems, require handshaking in one or both directions. Consult the documentation for the device(s) you use for information about handshaking and other interface considerations.

Unique to Ampro is ROM BIOS support for using a serial console (keyboard and display) in place of the conventional video controller, monitor, and keyboard. See Chapter 3 for details about the serial console option.

Connector J3 is the primary serial port. The ROM BIOS supports it as the DOS COM1 device. The secondary serial port is J2. The ROM BIOS supports it as the COM2 device. It is possible to disable either or both serial ports with SETUP. If you disable the primary port and enable the secondary port, and there is no other primary port in the system, then the secondary port is installed as COM1 by DOS.

| PIN | SIGNAL<br>NAME | FUNCTION            | IN/OUT | DB25<br>PIN | DB9<br>PIN |

|-----|----------------|---------------------|--------|-------------|------------|

| 1   | DCD            | Data Carrier Detect | IN     | 8           | 1          |

| 2   | DSR            | Data Set Ready      | IN     | 6           | 6          |

| 3   | RXD            | Receive Data        | IN     | 3           | 2          |

| 4   | RTS            | Request To Send     | OUT    | 4           | 7          |

| 5   | TXD            | Transmit Data       | OUT    | 2           | 3          |

| 6   | CTS            | Clear to Send       | IN     | 5           | 8          |

| 7   | DTR            | Data Terminal       | OUT    | 20          | 4          |

| 8   | RI             | Ring Indicator      | IN     | 22          | 9          |

| 9   | GND            | Signal Ground       |        | 7           | 5          |

| 10  | N/A            | Key pin             |        |             |            |

Table 2-18. Serial Port Connectors (J2, J3)

| CONNECTOR TYPE | MATING CONNECTOR           |  |

|----------------|----------------------------|--|

| RIBBON         | 3M 3473-7010               |  |

| DISCRETE WIRE  | MOLEX HOUSING 22-55-2101 N |  |

|                | PIN 16-02-0103             |  |

Table 2-19. J2 and J3 Mating Connector

## 2.4.5 Floppy Disk Interface

The onboard floppy disk controller and ROM BIOS support one or two floppy disk drives in any of the standard DOS formats shown in Table 2-20.

| CAPACITY | DRIVE SIZE | TRACKS | DATA RATE |

|----------|------------|--------|-----------|

| 360K     | 5-1/4 inch | 40     | 250 KHz   |

| 1.2M     | 5-1/4 inch | 80     | 500 KHz   |

| 720K     | 3-1/2 inch | 80     | 250 KHz   |

| 1.44M    | 3-1/2 inch | 80     | 500 KHz   |

Table 2-20. Supported Floppy Formats

#### **Floppy Drive Considerations**

Nearly any type of soft-sectored, single or double-sided, 40 or 80 track, 5-1/4 inch or 3-1/2 inch floppy disk drive is usable with this interface. Using higher quality drives improves system reliability. Here are some considerations about the selection, configuration, and connection of floppy drives to the Little Board/386SX-IIA.

- **Drive Interface** -- The drives must be compatible with the board's floppy disk connector signal interface, as described below. Any standard PC or AT compatible 5-1/4 inch or 3-1/2 inch floppy drive will work fine.

- **Drive Quality** -- Use high quality, DC servo, direct drive motor floppy disk drives.

- **Drive Combinations** -- Any combination of supported drives can be used.

- **Drive Select Jumpering** -- Both drives must be jumpered to the second drive select. Use a floppy cable with conductors 10-16 twisted between the two drives. This is standard practice in PC and AT compatible systems.

- **Drive Termination** -- Resistive terminations should be installed only on the drive connected to the last interface cable connector (farthest from the board).

- **Head Load Jumpering** -- When using drives with a Head Load option, jumper the drive for head load with motor on rather than head load with drive select.

- **Drive Mounting** -- If you mount the Little Board directly on a disk drive, place a thin metal shield between the disk drive and the CPU board, to reduce the possibility of electromagnetic interactions.

- **Dual Capacity Drives** -- The Little Board/386SX-IIA's ROM BIOS allows dual-capacity use of 1.2M byte and a 1.44M byte high density drives: that is, 360 Kbyte diskettes can be read on a 1.2 megabyte drive, and 720 Kbyte diskettes read on a 1.44 megabyte drive. However, don't write to low density diskettes on the high density drive, as incomplete erasure may occur.

## Floppy Interface Configuration

In SETUP, specify the number and type of floppy drives connected to the system. See Chapter 3.

If you don't use the floppy interface, disable it in SETUP, and by removing the jumper from W6. This frees DRQ2 for use by other devices.

#### Floppy Interface Connector

Table 2-21 shows the pinout and signal definitions of the floppy disk interface connector, J8. The pinout of J8 meets the AT standard for floppy drive connectors.

| PIN  | SIGNAL NAME | FUNCTION         | IN/OUT |

|------|-------------|------------------|--------|

| 2    | -RPM/-RWC   | Speed/Precomp    | OUT    |

| 4    | N/A         | (Not used)       | N/A    |

| 6    | N/A         | Key pin          | N/A    |

| 8    | -IDX        | Index Pulse      | IN     |

| 10   | -MO1        | Motor On 1       | OUT    |

| 12   | -DS2        | Drive Select 2   | OUT    |

| 14   | -DS1        | Drive Select 1   | OUT    |

| 16   | -MO2        | Motor On 2       | OUT    |

| 18   | -DIRC       | Direction Select | OUT    |

| 20   | -STEP       | Step             | OUT    |

| 22   | -WD         | Write Data       | OUT    |

| 24   | -WE         | Write Enable     | OUT    |

| 26   | -TRK0       | Track 0          | IN     |

| 28   | -WP         | Write Protect    | IN     |

| 30   | -RDD        | Read Data        | IN     |

| 32   | -HS         | Head Select      | OUT    |

| 34   | -DCHG       | Disk Change IN   |        |

| 1-33 | (all odd)   | Signal grounds   | N/A    |

Table 2-21. Floppy Disk Interface Connector (J8)

| CONNECTOR TYPE | MATING CONNECTOR                           |

|----------------|--------------------------------------------|

| RIBBON         | 3M 3473-7034                               |

| DISCRETE WIRE  | MOLEX HOUSING 22-55-2341<br>PIN 16-02-0103 |

Table 2-22. J8 Mating Connector

# 2.5 INTEGRATED DEVICE ELECTRONICS (IDE) HARD DISK INTERFACE

The Little Board/386SX-IIA provides an interface for one or two Integrated Device Electronics (IDE) hard disk drives. These drives have the hard disk controller built-in. The IDE interface appears at connector J11, a 40-pin, dual-row connector. Table 2-23 shows the interface signals and pin outs for the IDE interface connector. The Ampro ROM BIOS allows you to use both IDE and SCSI drives on the same system.

## **NOTE**

For maximum reliability, keep all IDE drive cables less than 18 inches long.

### 2.5.1 IDE Interface SETUP

Use SETUP to specify one or two hard disk drives and their drive type connected to the IDE interface. The section on SETUP covers this in detail. This interface is only for IDE drives. To use conventional MFM or

RLL drives you must install an appropriate hard disk controller on the AT bus. Use the same section of SETUP for IDE or conventional drive installations.

# 2.5.2 IDE Interface Connector

Table 2-23 shows the pinout and signal definitions of the IDE interface connector, J11. Table 2-24 gives the part numbers of two mating connectors.

| PIN | SIGNAL NAME | FUNCTION                 | IN/OUT |

|-----|-------------|--------------------------|--------|

| 1   | -HOST RESET | Reset signal from host   | OUT    |

| 2   | GND         | Ground                   | OUT    |

| 3   | HOST D7     | Data bit 7               | I/O    |

| 4   | HOST D8     | Data bit 8               | I/O    |

| 5   | HOST D6     | Data bit 6               | I/O    |

| 6   | HOST D9     | Data bit 9               | I/O    |

| 7   | HOST D5     | Data bit 5               | I/O    |

| 8   | HOST D10    | Data bit 10              | I/O    |

| 9   | HOST D4     | Data bit 4               | I/O    |

| 10  | HOST D11    | Data bit 11              | I/O    |

| 11  | HOST D3     | Data bit 3               | I/O    |

| 12  | HOST D12    | Data bit 12              | I/O    |

| 13  | HOST D2     | Data bit 2               | I/O    |

| 14  | HOST D13    | Data bit 13              | I/O    |

| 15  | HOST D1     | Data bit 1               | I/O    |

| 16  | HOST D14    | Data bit 14              | I/O    |

| 17  | HOST D0     | Data bit 0               | I/O    |

| 18  | HOST D15    | Data bit 15              | I/O    |

| 19  | GND         | Ground                   | OUT    |

| 20  | KEY         | Keyed pin                | N/C    |

| 21  | RSVD        | Reserved                 | N/C    |

| 22  | GND         | Ground                   | OUT    |

| 23  | -HOST IOW   | Write strobe             | OUT    |

| 24  | GND         | Ground                   | OUT    |

| 25  | -HOST IOR   | Read strobe              | OUT    |

| 26  | GND         | Ground                   | OUT    |

| 27  | RSVD        | Reserved                 | N/C    |

| 28  | HOST ALE    | Address latch enable     | OUT    |

| 29  | RSVD        | Reserved                 | N/C    |

| 30  | GND         | Ground                   | OUT    |

| 31  | HOST IRQ14  | Drive interrupt request  | IN     |

| 32  | -HOST IO16  | Send/receive 16-bit data | IN     |

| 33  | HOST A1     | Drive address 1          | OUT    |

| 34  | -HOST PDIAG | Pass diagnostic          | IN     |

| 35  | HOST AD0    | Drive address 0          | OUT    |

| 36  | HOST AD2    | Drive address 2          | OUT    |

| 37  | -HOST CS0   | Chip select              | OUT    |

| 38  | -HOST CS1   | Chip select              | OUT    |

| 39  | SLV/ACT     | Drive active/drive slave | N/A    |

| 40  | GND         | Ground                   | OUT    |

**Table 2-23. IDE Drive Interface Connector (J11)**

| CONNECTOR TYPE | MATING CONNECTOR                           |

|----------------|--------------------------------------------|

| RIBBON         | 3M 3417-7040                               |

| DISCRETE WIRE  | MOLEX HOUSING 22-55-2401<br>PIN 16-02-0103 |