≯

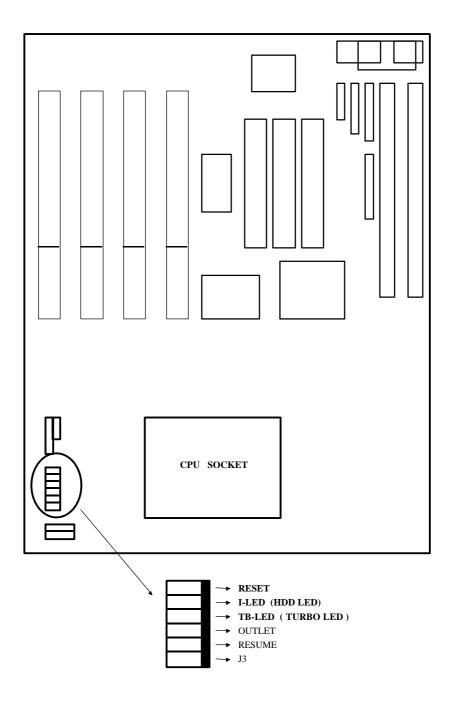

Mainboard Layout Display Type Select JW1 JW2 JW3 JW4 JW4 PS2\_MS PS2\_KB W83787F/ 7871F/877F AT\_KB SL4 SL2 SL3 2 Password Power Connector Clear S\_IDE F SIMM2 SIMMI FDD Select Serial Port1 Secondary IDE [] J1 BIOS COMI COM2 BANKO BANK1 Port2 P PC13 PCI2 Primary IDE PCII PCI Bus Clock Select 81S SL7 SL6 SL5 JCK PCI Bus Clock Select VT82C505 VT82C416MV M1 M2 KBLOCK 12 1 M3 RNA >M4 JS3 JS2 JS1 JS6 JS5 JS4 M5 CPU JPW1⊟ JPW2 VT82C496G SOCKET >M6 M7 > M9 M8

> NOTE : When plugging your CPU into the CPU (ZIF) socket, make sure that the pin 1 matches that of the CPU socket.

1-3

#### PIO3 LED PIN-OUT

## **Mainboard Settings**

Chapter 2

The 486-PIO-3 has several user-adjustable jumpers on the board that allow you to configure your system to suit your requirements. This chapter contains information on the various jumper settings on your mainboard.

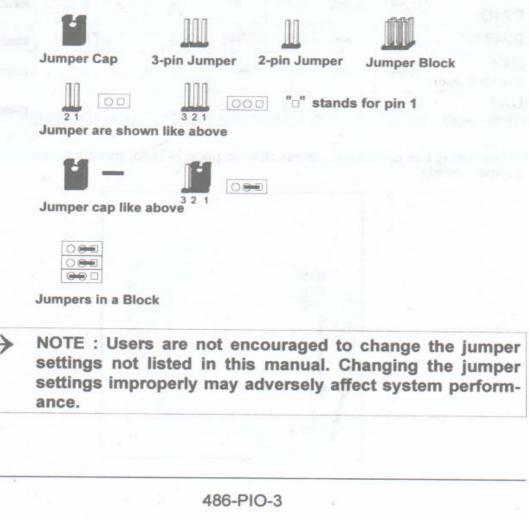

### Jumpers

Jumpers are used to select the operation modes for your system. Some jumpers on the board have three metal pins with each pin representing a different function. To "set" a jumper, a black cap containing metal contacts is placed over the jumper pin/s according to the required configuration. A jumper is said to be "shorted" when the black cap has been placed on one or two of its pins. The types of jumpers used in this manual are shown below:

### CPU Jumper Settings: JC1, JC2, JC3, JC4, JC5, RNA, RNC, RNI

Intel : 486SX/DX/DX2; DX4 ODP; P24S; P24D; P24T; IntelDX4 -(Double-Speed: A80486DX4-XX\*, Triple-Speed: A80486DX4-XX\*)

|                       | JC1 | JC2      | JC3 | JC4        | JC5 | RNA | RNC | RNI         |

|-----------------------|-----|----------|-----|------------|-----|-----|-----|-------------|

| 486SX                 |     | <b>@</b> | 00  | 000        |     | 1   | 1   | 1<br>0 BP4R |

| 486DX/DX2<br>P24S     |     | 0 🖛      | 00  |            | 00  |     |     | 011 8P4R    |

| DX4 ODP<br>P24D       | 0   | 0.       | 00  | 0.         | 00  |     |     | 0 SP4R      |

| P24T                  | 0   | 0        | 00  | 0          | ()  |     |     | 0 8P4R      |

| DX4<br>(Double-Speed) | 0   | 0 🐜      | 00  | <b>@##</b> | 00  |     |     | 00 8P4R     |

| DX4<br>(Triple-Speed) | 0   | 0        | 00  | 0          | 00  |     |     | 011 8P4R    |

\* When using this processor, please refer to page 2-11 for more information about jumper setting.

### AMD : 486DX2 -(A80486DX2-XXV8T\*, A80486DX2-XXNV8T\*); 486DX4 -(A80486DX4-100NV8T\*, A80486DX4-XXSV8B\*, Am486DX4-100V8T\*); AMD-X5\*

|                    | JC1 | JC2     | JC3         | JC4      | JC5 | RNA           | RNC      | RNI      |

|--------------------|-----|---------|-------------|----------|-----|---------------|----------|----------|

| 486DX2             | 0.  | 0.      | ( <b>**</b> | 000      | 00  | 1<br>0 * 8P4R | 1        | 1        |

| Enhanced<br>486DX2 | 0   | 0.000   | 00          | <b>.</b> | 00  |               | <u> </u> | 011 8P4R |

| 486DX4             | 0   | 0       | 00          | 000      | 00  | 0 8P4R        |          | 1.80     |

| Enhanced<br>486DX4 | 0   | 0.      | 0 🗆         | 0.       | 00  |               |          | 01) 8P4R |

| AMD-X5             | 0   | 0 (111) | 00          | ()       | 00  |               |          | 0 BP4R   |

\* When using this processor, please refer to page 2-11 for more information about jumper setting.

UMC : U5S/U5SD/U5SLV -(U5SX-SUPERXX, U5SD-SUPERXX, U5SLV-SUPERXX\*); Cyrix : Cx486DX/DX2/DX4 -(Cx486DX-XXGP, Cx486DX-VXXGP\*, Cx486DX2-XXGP, Cx486DX2-VXXGP\*, Cx486DX4-100\*);

5x86 -

(5x86-100\*, 5x86-120\*)

|                     | JC1      | JC2 | JC3 | JC4 | JC5 | RNA           | RNC      | RNI       |

|---------------------|----------|-----|-----|-----|-----|---------------|----------|-----------|

| U5SD                | 0        | 0 🖛 | 00  | 000 | 00  | 1<br>0 + 8P4R | 1        | 1         |

| U5S<br>U5SLV        | <b>.</b> |     | 00  | 000 | 00  | 011 8P4R      |          | 0         |

| Cx486DX<br>Cx486DX2 | 0        | 0.  | 00  | 000 | 00  |               | 0++ 8P4R | a         |

| Cx486DX4<br>5x86    | 0 🗪      | 0.  | 00  | 0 9 | 00  |               |          | □0() 8P4R |

\* When using this processor, please refer to page 2-11 for more information about jumper setting.

## Low-Voltage CPU Jumper Setting

| CPU<br>Voltage<br>Type | Jumper<br>Setting        | CPU M                                                                                                                    | Nodel                                                          |                 |

|------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------|

| 3.3V                   | JPW1 00000<br>JPW2 000   | UMC -<br>U5SLV-SUPERXX                                                                                                   | AMD -<br>AMD-X5                                                | CHU -           |

| 3.45V                  | JPW1 INC.<br>JPW2 OOO    | AMD -<br>A80486DX4-100NV8T<br>A80486DX2-XXNV8T<br>A80486DX4-XXSV8B<br>INTEL 486 -<br>A80486DX4-75<br>Cyrix -<br>5x86-100 | A80486DX2-<br>Am486DX2-<br>Am486DX4-<br>A80486DX4-<br>5x86-120 | XXV8T<br>100V8T |

| 3.6V                   | JPW1 000<br>JPW2 000     | Cyrix -<br>Cx486DX-VXXGP                                                                                                 |                                                                |                 |

| 4.0V                   | JPW1 000<br>JPW2 000     | Cyrix -<br>Cx486DX2-V80GP                                                                                                | 10-10-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1-1                        |                 |

| CN_3V                  | 1 0 2<br>3 9 4           | For 3.3V, 3.45V, 3.6V<br>and 4.0V CPUs                                                                                   |                                                                |                 |

| 21/64                  | 1 <b>1</b><br>3 <b>3</b> | For 5V CPUs (Default)                                                                                                    |                                                                |                 |

|                        | CN_3V                    | JPW1,<br>JPW2                                                                                                            |                                                                |                 |

|                        |                          |                                                                                                                          |                                                                |                 |

|                        |                          |                                                                                                                          |                                                                |                 |

CPU Clock Jumper Setting

|             | 50 MHz<br>DX-50 | 40 MHz<br>DX-40<br>DX2-80 | 33.3 MHz (Default)<br>SX-33<br>DX-33<br>DX2-66<br>DX4-100<br>X5-133 | 25 MHz<br>SX-25<br>DX-25<br>SX2-50<br>DX2-50<br>DX2-50<br>DX4-75 |

|-------------|-----------------|---------------------------|---------------------------------------------------------------------|------------------------------------------------------------------|

| JK1         |                 | 0                         |                                                                     |                                                                  |

| JK2         |                 | 0                         |                                                                     | 0                                                                |

| <b>JK</b> 3 |                 |                           |                                                                     |                                                                  |

| JK4         | 0               | 0                         |                                                                     | 0                                                                |

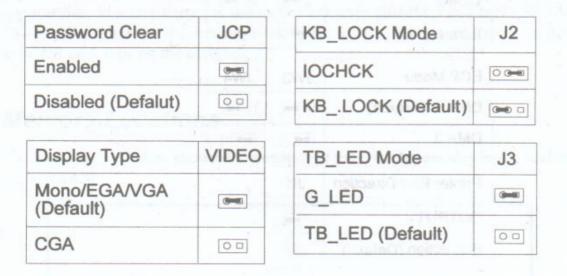

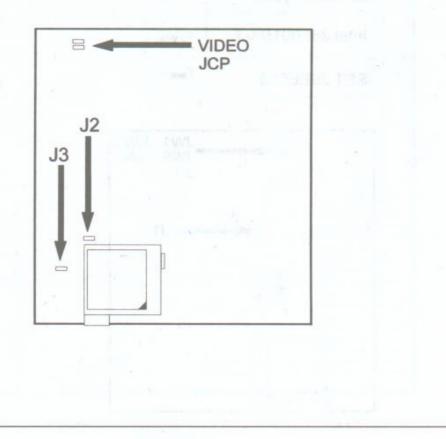

Password Clear: JCP Display Type Select: VIDEO KB\_LOCK Mode Select: J2 TB\_LED Mode Select: J3

486-PIO-3

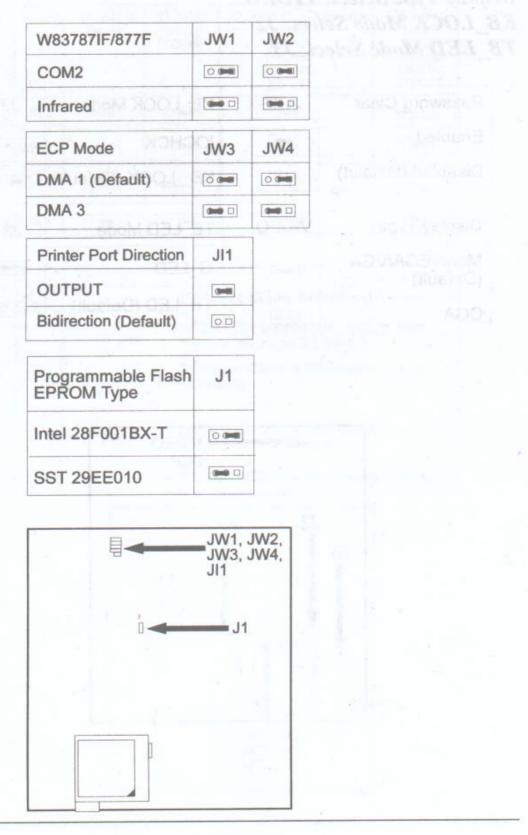

### W83787F/787IF Controller: JW1, JW2, JW3, JW4, JI1, J1

486-PIO-3

## **Chapter 3**

# **System Memory**

The 486-PIO-3 can be equipped with the necessary memory for running all your applications. Memory comes in the form of DRAM (SIMMs) and cache SRAM. This chapter describes these two types of memory and gives instructions on how to install each type on the mainboard.

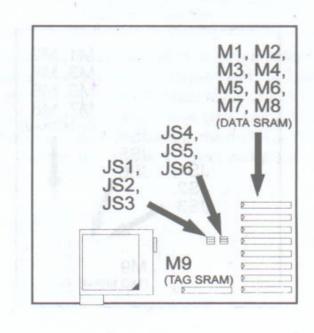

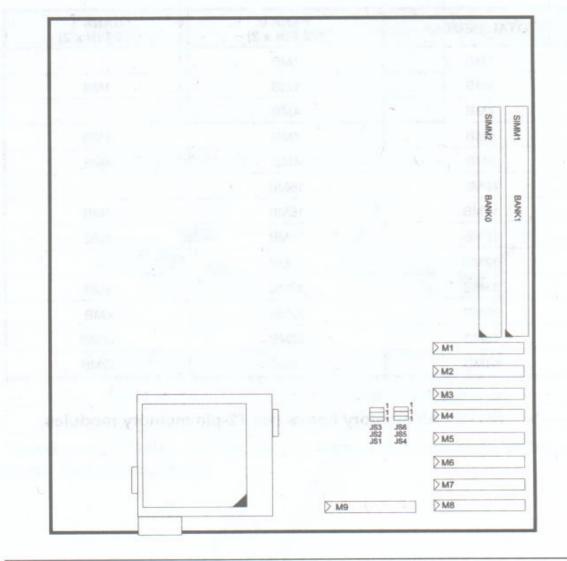

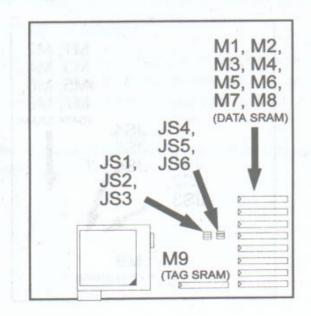

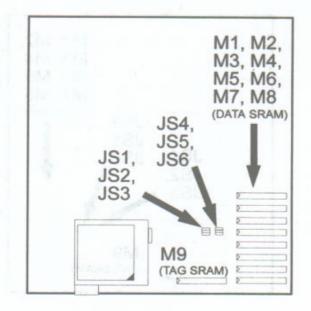

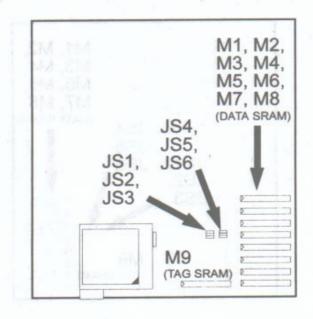

## **Memory Locations**

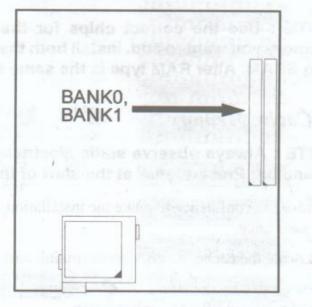

The board layout below shows the locations of the DRAM memory banks and the cache SRAM:

### Installing DRAM

#### SIMM Banks

The 486-PIO-3 can accommodate onboard memory from 1 to 64MB using SIMMs (Single-In-Line Memory Modules, one SIMM shown below.) The mainboard has two memory banks — Bank 0 and Bank 1. Each bank has two SIMM sockets which can accept either a 1, 4, 16 or 32MB SIMM in each socket.

### **DRAM** Configuration

Memory may be installed as suggested in the following table. It does not matter to start the installation from Bank 0 or Bank 1.

| TOTAL MEMORY | BANK 0<br>(72-PIN x 2) | BANK 1<br>(72-PIN x 2) |  |

|--------------|------------------------|------------------------|--|

| 1MB          | 1MB                    |                        |  |

| 2MB          | 1MB                    | 1MB                    |  |

| 4MB          | 4MB                    |                        |  |

| 5MB          | 4MB                    | 1MB                    |  |

| 8MB          | 4MB                    | 4MB                    |  |

| 16MB         | 16MB                   | 194                    |  |

| 17MB         | 16MB                   | 1MB                    |  |

| 20MB         | 16MB                   | 4MB                    |  |

| 32MB         | 32MB                   |                        |  |

| 33MB         | 32MB                   | 1MB                    |  |

| 36MB         | 32MB                   | 4MB                    |  |

| 48MB         | 32MB                   | 16MB                   |  |

| 64MB         | 32MB                   | 32MB                   |  |

NOTE : All memory banks use 72-pin memory modules.

### **Installation Instructions**

NOTE : Always observe static electricity precautions. See "Handling Precautions" at the start of this manual.

1. Locate the SIMM banks on the mainboard.

2. Insert the SIMM edge connector onto the socket.

3. Carefully push the SIMM down and back into the socket until the retaining clips of the socket snap, holding the SIMM in place. The holes in the SIMM should match the pins on the socket's retaining clips.

To remove the SIMM/s, pull the retaining latch on both ends of the socket and reverse the procedure above.

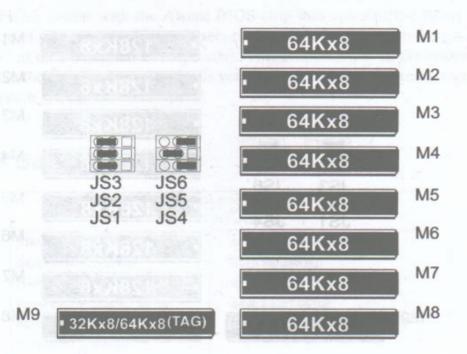

## **Cache Memory**

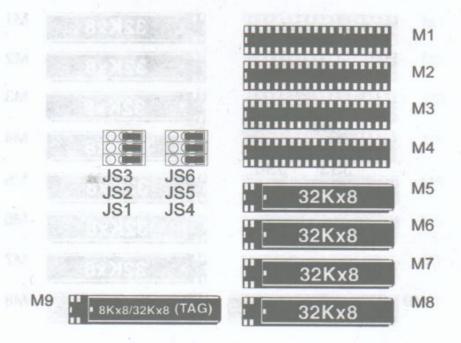

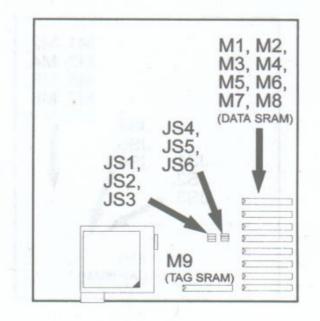

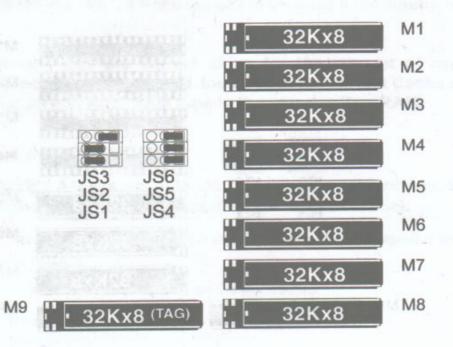

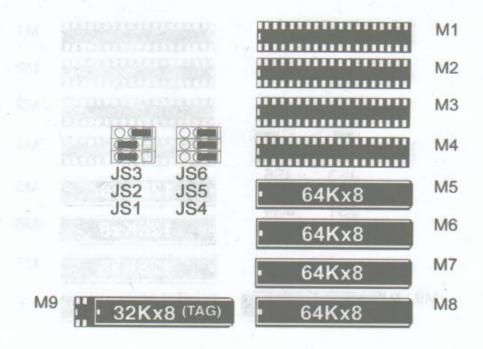

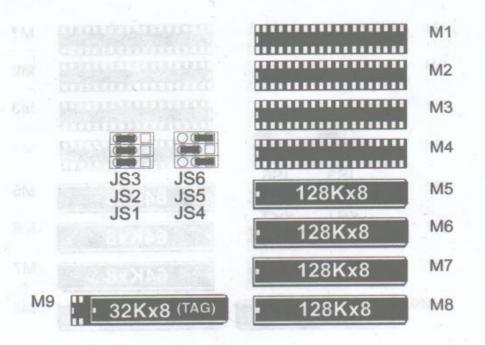

The 486-PIO-3 can accept cache SRAM of 128K/256K/512K/1MB in DIP packages. Every time the CPU wants to write data to the external memory, if the location in SRAM is a "hit", it writes this data to the cache RAM directly, not to the DRAM.

NOTE : Use the correct chips for the amount of cache memory you want to add. Install both the correct Cache and Tag SRAM. Alter RAM type is the same as Tag RAM.

### **Installing Cache Memory**

≯

NOTE : Always observe static electricity precautions. See "Handling Precautions" at the start of this manual.

If you do not have the confidence to make the installation, better consult a service technician for assistance.

- 1. Locate the cache memory on the mainboard.

- 2. Be guided by the Cache SRAM settings depending on your desired SRAM configuration.

Correct orientation of the chip is necessary for the cache to operate properly. Normally, the chips have either a curved notch or a dot. This marker on the chip must be matched to the marker on the socket for correct alignment.

Install the chips individually as follows:

- 3. Align the chip with the marker on the socket. Press the chip onto the socket, ensuring that the pins on the chip are aligned with the corresponding connections on the socket.

- 4. Press the chip completely into the socket so that the pins are properly seated.

128KB Cache SRAM

#### 256KB Cache SRAM

512KB Cache SRAM

512KB Cache SRAM (The Alternative Insertion)