| Processor              |

|------------------------|

| Processor Speed        |

| Chip Set               |

| Video Chip Set         |

| Maximum Onboard Memory |

| Maximum Video Memory   |

| Cache                  |

| BIOS                   |

| Dimensions             |

| I/O Options            |

| •                      |

CX M1/AM K5/Pentium 75/90/100/120/133/150/166/180/200MHz Intel None 128MB (EDO supported) None 256/512KB AMI/Award 305mm x 210mm 32-bit PCI slots (4), floppy drive interface, green PC connector, IDE interfaces (2), parallel port, PS/2 mouse port, serial ports (2), cache slot, IR connectors (2), USB connectors (2), ATX power connector, remote power switch None

**NPU Options**

... continued from previous page

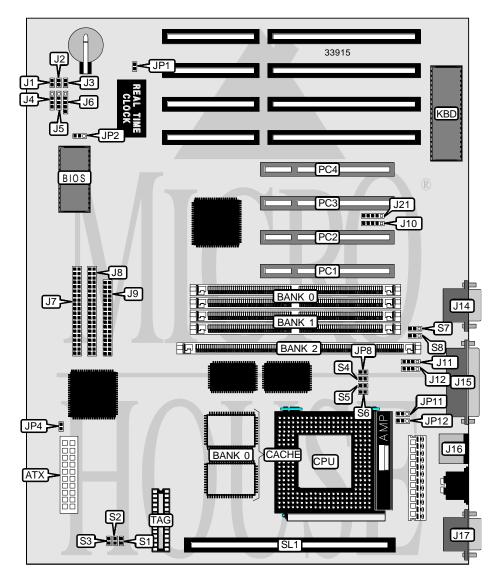

| CONNECTIONS            |          |                     |           |  |  |  |  |

|------------------------|----------|---------------------|-----------|--|--|--|--|

| Purpose                | Location | Purpose             | Location  |  |  |  |  |

| ATX power connector    | ATX      | USB connector 1     | J11       |  |  |  |  |

| Reset switch           | J1       | USB connector 2     | J12       |  |  |  |  |

| Green PC connector     | J2       | Serial port 2       | J14       |  |  |  |  |

| Green PC LED           | J3       | Parallel port       | J15       |  |  |  |  |

| Speaker                | J4       | PS/2 mouse port     | J16       |  |  |  |  |

| IDE interface LED      | J5       | Serial port 1       | J17       |  |  |  |  |

| Power LED & keylock    | Je       | IR connector (fast) | J21       |  |  |  |  |

| IDE interface 2        | J7       | Remote power switch | JP4       |  |  |  |  |

| IDE interface 1        | J8       | 32-bit PCI slots    | PC1 - PC4 |  |  |  |  |

| Floppy drive interface | 19       | Cache slot          | SL1       |  |  |  |  |

| IR connector           | J10      |                     |           |  |  |  |  |

| USER CONFIGURABLE SETTINGS     |     |                   |  |  |  |  |

|--------------------------------|-----|-------------------|--|--|--|--|

| Function Label Position        |     |                   |  |  |  |  |

| í CMOS memory normal operation | JP1 | Open              |  |  |  |  |

| CMOS memory clear              | JP1 | Closed            |  |  |  |  |

| Flash BIOS voltage select 12v  | JP2 | Pins 1 & 2 closed |  |  |  |  |

| Flash BIOS voltage select 5v   | JP2 | Pins 2 & 3 closed |  |  |  |  |

| DIMM/DRAM CONFIGURATION |             |             |             |  |  |  |  |  |

|-------------------------|-------------|-------------|-------------|--|--|--|--|--|

| Size                    | Bank 0      | Bank 1      | Bank 2      |  |  |  |  |  |

| 8MB                     | None        | None        | (1) 1M x 64 |  |  |  |  |  |

| 8MB                     | (2) 1M x 32 | None        | None        |  |  |  |  |  |

| 16MB                    | (2) 1M x 32 | (2) 1M x 32 | None        |  |  |  |  |  |

| 16MB                    | (2) 2M x 32 | None        | None        |  |  |  |  |  |

| 16MB                    | None        | None        | (1) 2M x 64 |  |  |  |  |  |

| 24MB                    | (2) 2M x 32 | (2) 1M x 32 | None        |  |  |  |  |  |

| 24MB                    | None        | (2) 1M x 32 | (1) 2M x 64 |  |  |  |  |  |

| 32MB                    | None        | (2) 4M x 32 | None        |  |  |  |  |  |

| 32MB                    | None        | None        | (1) 4M x 64 |  |  |  |  |  |

| 32MB                    | (2) 2M x 32 | (2) 2M x 32 | None        |  |  |  |  |  |

| 32MB                    | None        | (2) 2M x 32 | (1) 2M x 64 |  |  |  |  |  |

| 40MB                    | (2) 4M x 32 | (2) 1M x 32 | None        |  |  |  |  |  |

| 40MB                    | None        | (2) 1M x 32 | (1) 4M x 64 |  |  |  |  |  |

| 40MB                    | None        | (1) 4M x 64 | (1) 1M x 64 |  |  |  |  |  |

| 48MB                    | (2) 2M x 32 | (2) 4M x 32 | None        |  |  |  |  |  |

| 48MB                    | None        | (2) 2M x 32 | (1) 4M x 64 |  |  |  |  |  |

| 48MB                    | None        | (2) 4M x 32 | (1) 2M x 64 |  |  |  |  |  |

| 64MB                    | (2) 8M x 32 | None        | None        |  |  |  |  |  |

| 64MB                    | None        | None        | (1) 8M x 64 |  |  |  |  |  |

| 64MB                    | None        | (2) 4M x 32 | (1) 4M x 64 |  |  |  |  |  |

| 72MB                    | (2) 8M x 32 | (2) 1M x 32 | None        |  |  |  |  |  |

... continued from previous page

|                         | DIMM/DRAM CONF               | IGURATION (CON'T) |             |

|-------------------------|------------------------------|-------------------|-------------|

| Size                    | Bank 0                       | Bank 1            | Bank 2      |

| 72MB                    | None                         | (2) 1M x 32       | (1) 8M x 64 |

| 72MB                    | None                         | (2) 8M x 32       | (1) 1M x 64 |

| 80MB                    | (2) 8M x 32                  | (2) 2M x 32       | None        |

| 80MB                    | None                         | (2) 8M x 32       | (1) 2M x 64 |

| 80MB                    | None                         | (2) 2M x 32       | (1) 8M x 64 |

| 96MB                    | (2) 8M x 32                  | (2) 4M x 32       | None        |

| 96MB                    | None                         | (2) 8M x 32       | (1) 4M x 64 |

| 96MB                    | None                         | (2) 4M x 32       | (1) 8M x 64 |

| 128MB                   | (2) 4M x 32                  | (2) 4M x 32       | None        |

| Note: Board accepts EDO | memory. Banks 0 & 1 are inte | erchangeable.     |             |

| DRAM VOLTAGE CONFIGURATION |                   |                   |  |  |  |  |

|----------------------------|-------------------|-------------------|--|--|--|--|

| Voltage S7 S8              |                   |                   |  |  |  |  |

| 3.3v                       | Pins 2 & 3 closed | Pins 2 & 3 closed |  |  |  |  |

| 5v                         | Pins 1 & 2 closed | Pins 1 & 2 closed |  |  |  |  |

| CACHE CONFIGURATION |              |                        |                    |  |  |  |

|---------------------|--------------|------------------------|--------------------|--|--|--|

| Size Bank 0 SL1 TAG |              |                        |                    |  |  |  |

| 256KB               | (2) 32K x 32 | Not installed          | (1) 8K/16K/32K x 8 |  |  |  |

| 512KB               | (2) 32K x 32 | 256KB module installed | (1) 8K/16K/32K x 8 |  |  |  |

| CPU SPEED SELECTION (CYRIX, IMISC610) |                    |                |        |       |           |        |           |  |

|---------------------------------------|--------------------|----------------|--------|-------|-----------|--------|-----------|--|

| CPU speed                             | Clock speed        | Multiplier     | JP11   | JP12  | <b>S1</b> | S2     | <b>S3</b> |  |

| 120MHz                                | 50MHz              | 2x             | 2&3    | 1&2   | Closed    | Closed | Open      |  |

| 133MHz                                | 66MHz              | 2x             | 2&3    | 1&2   | Open      | Closed | Open      |  |

| 150MHz                                | 60MHz              | 2x             | 2&3    | 1 & 2 | Closed    | Open   | Open      |  |

| 166MHz                                | 66MHz              | 2x             | 2&3    | 1&2   | Open      | Open   | Open      |  |

| 200MHz                                | 55MHz              | 2x             | 2&3    | 1 & 2 | Open      | Open   | Closed    |  |

| Note: Pins desig                      | nated should be in | the closed pos | ition. |       |           |        |           |  |

Note: Pins designated should be in the closed position.

| CPU SPEED SELECTION (AMD, IMISC610) |                    |                  |        |      |           |        |           |

|-------------------------------------|--------------------|------------------|--------|------|-----------|--------|-----------|

| CPU speed                           | Clock speed        | Multiplier       | JP11   | JP12 | <b>S1</b> | S2     | <b>S3</b> |

| 75MHz                               | 50MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Closed | Open      |

| 90MHz                               | 60MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Open   | Open      |

| 100MHz                              | 66MHz              | 1.5x             | 1&2    | 1&2  | Open      | Open   | Open      |

| 120MHz                              | 60MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Open   | Open      |

| 133MHz                              | 66MHz              | 1.5x             | 1&2    | 1&2  | Open      | Open   | Open      |

| 150MHz                              | 60MHz              | 2x               | 2&3    | 1&2  | Closed    | Open   | Open      |

| 166MHz                              | 66MHz              | 2x               | 2&3    | 1&2  | Open      | Open   | Open      |

| Note: Pins desig                    | nated should be ir | n the closed pos | ition. |      |           |        |           |

... continued from previous page

| CPU SPEED SELECTION (INTEL, IMISC610) |                    |                  |        |      |           |        |            |  |

|---------------------------------------|--------------------|------------------|--------|------|-----------|--------|------------|--|

| CPU speed                             | Clock speed        | Multiplier       | JP11   | JP12 | <b>S1</b> | S2     | <b>S</b> 3 |  |

| 75MHz                                 | 50MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Closed | Open       |  |

| 90MHz                                 | 60MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Open   | Open       |  |

| 100MHz                                | 66MHz              | 1.5x             | 1&2    | 1&2  | Open      | Open   | Open       |  |

| 120MHz                                | 60MHz              | 2x               | 2&3    | 1&2  | Closed    | Open   | Open       |  |

| 133MHz                                | 66MHz              | 2x               | 2&3    | 1&2  | Open      | Open   | Open       |  |

| 150MHz                                | 60MHz              | 2.5x             | 2&3    | 2&3  | Closed    | Open   | Open       |  |

| 166MHz                                | 66MHz              | 2.5x             | 2&3    | 2&3  | Open      | Open   | Open       |  |

| 180MHz                                | 60MHz              | 3x               | 1&2    | 2&3  | Closed    | Open   | Open       |  |

| 200MHz                                | 66MHz              | 3x               | 1&2    | 2&3  | Open      | Open   | Open       |  |

| Note: Pins desig                      | nated should be in | n the closed pos | ition. |      |           |        |            |  |

| CPU SPEED SELECTION (CYRIX, PLL52C61-01) |                                                         |            |      |       |           |        |        |  |

|------------------------------------------|---------------------------------------------------------|------------|------|-------|-----------|--------|--------|--|

| CPU speed                                | Clock speed                                             | Multiplier | JP11 | JP12  | <b>S1</b> | S2     | S3     |  |

| 120MHz                                   | 50MHz                                                   | 2x         | 2&3  | 1&2   | Closed    | Closed | Closed |  |

| 133MHz                                   | 66MHz                                                   | 2x         | 2&3  | 1&2   | Closed    | Closed | Open   |  |

| 150MHz                                   | 60MHz                                                   | 2x         | 2&3  | 1&2   | Closed    | Open   | Open   |  |

| 166MHz                                   | 66MHz                                                   | 2x         | 2&3  | 1 & 2 | Open      | Open   | Open   |  |

| 200MHz                                   | 66MHz                                                   | 2x         | 2&3  | 1&2   | Open      | Closed | Open   |  |

| Note: Pins desig                         | Note: Pins designated should be in the closed position. |            |      |       |           |        |        |  |

CPU SPEED SELECTION (AMD, PLL52C61-01) **CPU** speed **Clock speed** Multiplier JP11 JP12 **S1** S2 **S3** 75MHz 50MHz 1.5x 1&2 1&2 Closed Closed Closed 90MHz 60MHz 1.5x 1&2 1&2 Closed Open Open 100MHz 66MHz 1&2 1.5x 1&2 Open Open Open 120MHz 1&2 60MHz 1.5x 1&2 Closed Open Open 1&2 133MHz 66MHz 1&2 Open Open 1.5x Open 150MHz 60MHz 2x 2&3 1&2 Closed Open Open 166MHz 66MHz 2&3 1&2 Open Open 2x Open Note: Pins designated should be in the closed position.

| CPU SPEED SELECTION (INTEL, PLL52C61-01) |                    |                  |        |      |           |        |            |  |

|------------------------------------------|--------------------|------------------|--------|------|-----------|--------|------------|--|

| CPU speed                                | Clock speed        | Multiplier       | JP11   | JP12 | <b>S1</b> | S2     | <b>S</b> 3 |  |

| 75MHz                                    | 50MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Closed | Closed     |  |

| 90MHz                                    | 60MHz              | 1.5x             | 1&2    | 1&2  | Closed    | Open   | Open       |  |

| 100MHz                                   | 66MHz              | 1.5x             | 1&2    | 1&2  | Open      | Open   | Open       |  |

| 120MHz                                   | 60MHz              | 2x               | 2&3    | 1&2  | Closed    | Open   | Open       |  |

| 133MHz                                   | 66MHz              | 2x               | 2&3    | 1&2  | Open      | Open   | Open       |  |

| 150MHz                                   | 60MHz              | 2.5x             | 2&3    | 2&3  | Closed    | Open   | Open       |  |

| 166MHz                                   | 66MHz              | 2.5x             | 2&3    | 2&3  | Open      | Open   | Open       |  |

| 180MHz                                   | 60MHz              | 3x               | 1&2    | 2&3  | Closed    | Open   | Open       |  |

| 200MHz                                   | 66MHz              | 3x               | 1&2    | 2&3  | Open      | Open   | Open       |  |

| Note: Pins desig                         | nated should be ii | n the closed pos | ition. |      |           |        |            |  |

... continued from previous page

| CPU VOLTAGE SELECTION |        |        |        |        |

|-----------------------|--------|--------|--------|--------|

| Voltage               | JP8    | S4     | S5     | S6     |

| 3.3v (single)         | Closed | Closed | Closed | Closed |

| 3.3v (dual)           | Closed | Open   | Open   | Open   |

| 3.5v (single)         | Open   | Closed | Closed | Closed |