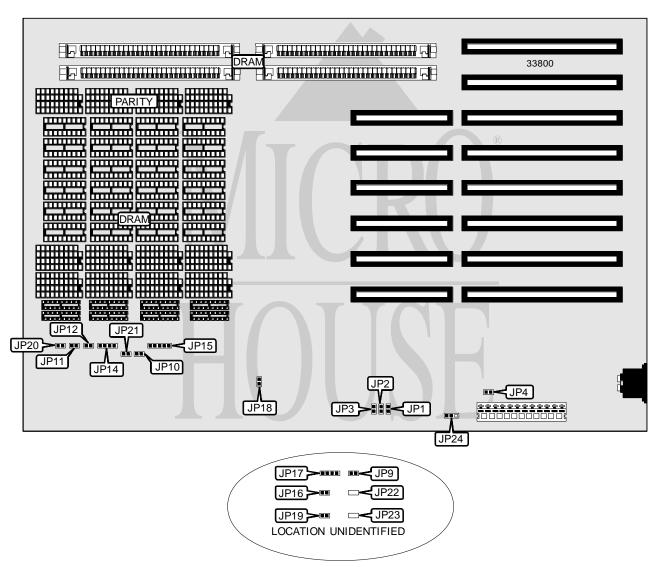

## UNIDENTIFIED VLSI 89402-2

**Processor** 80286 **Processor Speed** 12MHz **Chip Set** VLSI **Video Chip Set** None **Maximum Onboard Memory** 4MB **Maximum Video Memory** None Cache None **BIOS** AMI/Award **Dimensions** 330mm x 218mm

I/O Options None **NPU Options** 80287

Continued on next page. . .

## UNIDENTIFIED VLSI 89402-2

. . . continued from previous page

| CONNECTIONS  |          |                     |          |

|--------------|----------|---------------------|----------|

| Purpose      | Location | Purpose             | Location |

| Turbo LED    | JP10     | Power LED & keylock | JP15     |

| Turbo switch | JP11     | External battery    | JP17     |

| Speaker      | JP14     | Reset switch        | JP21     |

| USER CONFIGURABLE SETTINGS                                    |       |                   |  |

|---------------------------------------------------------------|-------|-------------------|--|

| Function                                                      | Label | Position          |  |

| Monitor type select color                                     | JP4   | Closed            |  |

| Monitor type select monochrome                                | JP4   | Open              |  |

| Turbo enabled                                                 | JP11  | Closed            |  |

| Turbo disabled & switchable through keyboard (CRTL, ALT, +/-) | JP11  | Open              |  |

| ROM wait state select 2 wait states                           | JP9   | Closed            |  |

| ROM wait state select 1 wait state                            | JP9   | Open              |  |

| í Battery type select internal                                | JP16  | Closed            |  |

| Battery type select external                                  | JP16  | Open              |  |

| í BIOS type select 27128                                      | JP18  | Open              |  |

| BIOS type select 27256                                        | JP18  | Closed            |  |

| í Fast mode enabled                                           | JP19  | Closed            |  |

| Fast mode disabled                                            | JP19  | Open              |  |

| Wait state select 0 wait states                               | JP20  | Closed            |  |

| Wait state select 1 wait state                                | JP20  | Open              |  |

| í Factory configured - do not alter                           | JP22  | Unidentified      |  |

| í Factory configured - do not alter                           | JP23  | Unidentified      |  |

| Parity check disabled                                         | JP24  | Pins 1 & 2 closed |  |

| Parity check enabled                                          | JP24  | Pins 2 & 3 closed |  |

| DRAM CONFIGURATION |             |             |              |              |            |

|--------------------|-------------|-------------|--------------|--------------|------------|

| Size               | Bank 0      | Bank 1      | Bank 2       | Bank 3       | Parity     |

| 512KB              | (4) 44256   | None        | None         | None         | (2) 41256  |

| 512KB              | None        | None        | (2) 256K x 9 | None         | None       |

| 640KB              | (4) 44256   | (4) 4464    | None         | None         | None       |

| 1MB                | (4) 44256   | (4) 44256   | None         | None         | (2) 41256  |

| 1MB                | None        | None        | (2) 256K x 9 | (2) 256K x 9 | None       |

| 2MB                | (16) 411000 | None        | None         | None         | None       |

| 2MB                | None        | None        | (2) 1M x 9   | None         | None       |

| 4MB                | (16) 411000 | (16) 411000 | None         | None         | (4) 411000 |

| 4MB                | None        | None        | (2) 1M x 9   | (2) 1M x 9   | None       |

Note: The location of banks 0, 1, 2 & 3 are unidentified. Board also accepts ZIP memory, but the configurations are unidentified.

Continued on next page. . .

## UNIDENTIFIED VLSI 89402-2

. . . continued from previous page

| DRAM JUMPER CONFIGURATION |        |        |        |  |

|---------------------------|--------|--------|--------|--|

| Size                      | JP1    | JP2    | JP3    |  |

| 512KB                     | Closed | Closed | Closed |  |

| 640KB                     | Closed | Open   | Closed |  |

| 1MB                       | Closed | Closed | Open   |  |

| 2MB                       | Closed | Open   | Open   |  |

| 4MB                       | Open   | Closed | Closed |  |

| CPU SPEED SELECTION |        |  |

|---------------------|--------|--|

| Speed               | JP12   |  |

| 6/12MHz             | Open   |  |

| 8/12MHz             | Closed |  |