- Processor Processor Speed Chip Set Video Chip Set Maximum Onboard Memory Maximum Video Memory Cache BIOS Dimensions I/O Options NPU Options

- 80386 20MHz Unidentified None 2MB (on external memory card) None None Unidentified Unidentified External memory card, PS/2 mouse port 80387/3167

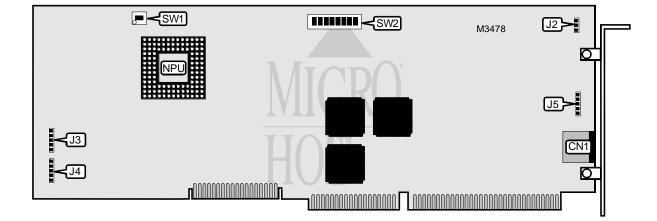

| CONNECTIONS      |          |                              |    |  |  |  |  |  |

|------------------|----------|------------------------------|----|--|--|--|--|--|

| Purpose          | Location |                              |    |  |  |  |  |  |

| PS/2 mouse port  | CN1      | Speaker                      | J4 |  |  |  |  |  |

| External battery | J2       | Auxiliary keyboard connector | J5 |  |  |  |  |  |

| Keylock          | J3       |                              |    |  |  |  |  |  |

Continued on next page...

... continued from previous page

| USER CONFIGURABLE SETTINGS                                          |       |          |  |  |  |  |  |

|---------------------------------------------------------------------|-------|----------|--|--|--|--|--|

| Function                                                            | Label | Position |  |  |  |  |  |

| í Monitor type select color                                         | SW1   | On       |  |  |  |  |  |

| Monitor type select monochrome                                      | SW1   | Off      |  |  |  |  |  |

| í NPU not installed (if Weitek NPU is installed, set switch to off) | SW2/1 | Off      |  |  |  |  |  |

| NPU installed                                                       | SW2/1 | On       |  |  |  |  |  |

| í PS/2 mouse disabled                                               | SW2/2 | Off      |  |  |  |  |  |

| PS/2 mouse enabled                                                  | SW2/2 | On       |  |  |  |  |  |

| í Video ROM copied to RAM                                           | SW2/3 | Off      |  |  |  |  |  |

| Video ROM not copied to RAM                                         | SW2/3 | On       |  |  |  |  |  |

| í Non maskable interrupt generated from fail safe timer disabled    | SW2/4 | Off      |  |  |  |  |  |

| Non maskable interrupt generated from fail safe timer enabled       | SW2/4 | On       |  |  |  |  |  |

| í IRQ10 disabled                                                    | SW2/5 | Off      |  |  |  |  |  |

| IRQ10 enabled                                                       | SW2/5 | On       |  |  |  |  |  |

| í IRQ11 disabled                                                    | SW2/6 | Off      |  |  |  |  |  |

| IRQ11 enabled                                                       | SW2/6 | On       |  |  |  |  |  |

| í IRQ12 disabled                                                    | SW2/7 | Off      |  |  |  |  |  |

| IRQ12 enabled                                                       | SW2/7 | On       |  |  |  |  |  |

| CPU SPEED SELECTION       |       |  |  |  |

|---------------------------|-------|--|--|--|

| Speed                     | SW2/8 |  |  |  |

| 8MHz (auto speed select)  | Off   |  |  |  |

| 20MHz (high speed select) | On    |  |  |  |

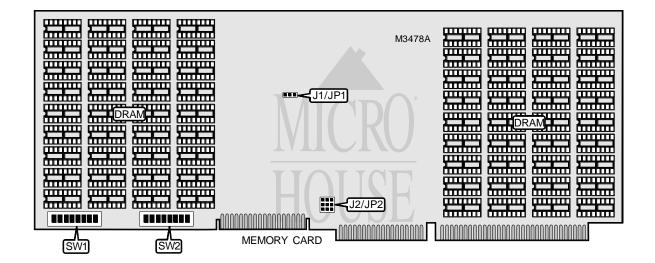

| USER CONFIGURABLE SETTINGS      |        |                   |  |  |  |  |

|---------------------------------|--------|-------------------|--|--|--|--|

| Function                        | Label  | Position          |  |  |  |  |

| Wait state select 0 wait states | J1/JP1 | Pins 1 & 2 closed |  |  |  |  |

| Wait state select 1 wait states | J1/JP1 | Pins 2 & 3 closed |  |  |  |  |

Continued on next page. . .

... continued from previous page

| DRAM CONFIGURATION                       |             |             |  |  |  |  |  |

|------------------------------------------|-------------|-------------|--|--|--|--|--|

| Size                                     | Bank 0      | Bank 1      |  |  |  |  |  |

| 1MB                                      | (36) 411000 | None        |  |  |  |  |  |

| 2MB                                      | (36) 411000 | (36) 411000 |  |  |  |  |  |

| Note: The location of banks 0 & 1 are up | identified  | •           |  |  |  |  |  |

Note: The location of banks 0 & 1 are unidentified.

| DRAM JUMPER CONFIGURATION |                                 |  |  |  |  |

|---------------------------|---------------------------------|--|--|--|--|

| Size J2/JP2               |                                 |  |  |  |  |

| 1MB                       | Pins 2 & 3, 5 & 6, 8 & 9 closed |  |  |  |  |

| 2MB                       | Pins 1 & 2, 4 & 5, 7 & 8 closed |  |  |  |  |

| DRAM SWITCH CONFIGURATION (ONE 2MB BOARD INSTALLED) |       |       |       |       |       |       |       |       |

|-----------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Setting                                             | SW1/1 | SW1/2 | SW1/3 | SW1/4 | SW1/5 | SW1/6 | SW1/7 | SW1/8 |

| Set for first 2MB boundary                          | On    |

| Setting                                             | SW2/1 | SW2/2 | SW2/3 | SW2/4 | SW2/5 | SW2/6 | SW2/7 | SW2/8 |

| Locate 256KB at end of second MB of space.          | On    | Off   | On    | On    | On    | On    | On    | On    |

| DRAM SWITCH CONFIGURATION (TWO 2MB BOARDS INSTALLED)       |       |       |       |       |       |       |       |       |

|------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Setting                                                    | SW1/1 | SW1/2 | SW1/3 | SW1/4 | SW1/5 | SW1/6 | SW1/7 | SW1/8 |

| Set for first 2MB boundary<br>(board 1)                    | On    |

| Set for first 2MB boundary<br>(board 2)                    | Off   | On    | On    | On    | On    | On    | On    | Off   |

| Setting                                                    | SW2/1 | SW2/2 | SW2/3 | SW2/4 | SW2/5 | SW2/6 | SW2/7 | SW2/8 |

| Locate 256KB at end of<br>second MB of space. (board<br>1) | On    | On    | Off   | On    | On    | On    | On    | On    |

| Not the first MB in the<br>system (board 2)                | Off   |

Continued on next page. . .

| DRA                                                       | DRAM SWITCH CONFIGURATION (THREE 2MB BOARDS INSTALLED) |       |       |       |       |       |       |       |

|-----------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Setting                                                   | SW1/1                                                  | SW1/2 | SW1/3 | SW1/4 | SW1/5 | SW1/6 | SW1/7 | SW1/8 |

| Set for first 2MB boundary<br>(board 1)                   | On                                                     | On    | On    | On    | On    | On    | On    | On    |

| Set for first 2MB boundary<br>(board 2)                   | Off                                                    | On    | On    | On    | On    | On    | On    | Off   |

| Set for third 2MB boundary<br>(board 3)                   | On                                                     | Off   | On    | On    | On    | On    | On    | Off   |

| Setting                                                   | SW2/1                                                  | SW2/2 | SW2/3 | SW2/4 | SW2/5 | SW2/6 | SW2/7 | SW2/8 |

| Locate 256KB at end of<br>sixth MB of space. (board<br>1) | On                                                     | Off   | Off   | On    | On    | On    | On    | On    |

| All switches off (board 2)                                | Off                                                    | Off   | Off   | Off   | Off   | Off   | Off   | Off   |

| All switches off (board 3)                                | Off                                                    | Off   | Off   | Off   | Off   | Off   | Off   | Off   |

| DRAM SWITCH CONFIGURATION (FOUR 2MB BOARDS INSTALLED) |       |       |       |       |       |       |       |       |

|-------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Setting                                               | SW1/1 | SW1/2 | SW1/3 | SW1/4 | SW1/5 | SW1/6 | SW1/7 | SW1/8 |

| Set for first 2MB boundary                            | On    |

| (board 1)                                             |       |       |       |       |       |       |       |       |

| Set for first 2MB boundary<br>(board 2)               | Off   | On    | On    | On    | On    | On    | On    | Off   |

| Set for third 2MB boundary<br>(board 3)               | On    | Off   | On    | On    | On    | On    | On    | Off   |

| Set for third 2MB boundary                            | Off   | Off   | On    | On    | On    | On    | On    | Off   |

| (board 4)                                             |       |       |       |       |       |       |       |       |

| All switches off (board 4)                            | N/A   |

| Setting                                               | SW2/1 | SW2/2 | SW2/3 | SW2/4 | SW2/5 | SW2/6 | SW2/7 | SW2/8 |

| Locate 256KB at end of                                | On    | On    | On    | Off   | On    | On    | On    | On    |

| eighth MB of space. (board                            |       |       |       |       |       |       |       |       |

| 1)                                                    |       |       |       |       |       |       |       |       |

| All switches off (board 2)                            | Off   |

| All switches off (board 3)                            | Off   |

| All switches off (board 4)                            | Off   |

... continued from previous page