## **EFA CORPORATION** 4MAHL, 4DMU-50AHL

CX486SX/CX487SX/80486SX/80486DX/ODP486SX/80486DX2 **Processor**

**Processor Speed** 20/25/33/40/50(internal)/50/66(internal)MHz

**Chip Set UMC** Max. Onboard DRAM 64MB

Cache 32/64/128/256KB

**BIOS** AMI

**Dimensions** 330mm x 218mm

32-bit VESA local bus slots (2), floppy drive interface, I/O Options

game port, IDE interface (2), parallel port, serial ports (2)

**NPU Options**

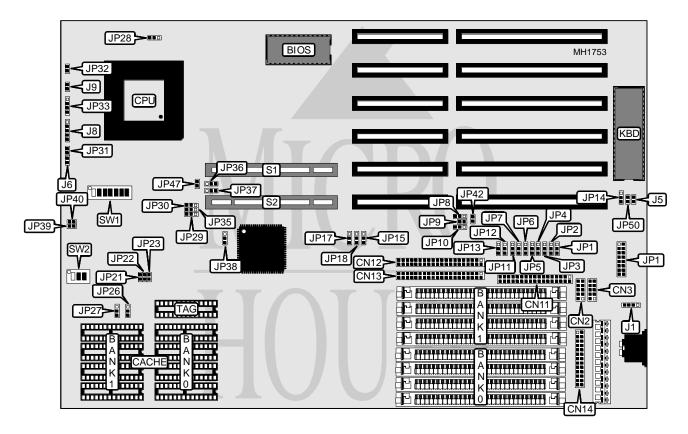

| CONNECTIONS                            |          |                            |          |  |  |

|----------------------------------------|----------|----------------------------|----------|--|--|

| Purpose                                | Location | Purpose                    | Location |  |  |

| Serial port 2                          | CN2      | Power LED & keylock        | J8       |  |  |

| Serial port 1                          | CN3      | Reset switch               | 19       |  |  |

| Floppy drive interface                 | CN11     | Game port                  | JP1      |  |  |

| IDE interface                          | CN12     | Turbo switch               | JP31     |  |  |

| AT bus hard drive interface            | CN13     | Turbo LED                  | JP32     |  |  |

| Parallel port                          | CN14     | Speaker                    | JP33     |  |  |

| External battery                       | J1       | 32-bit VESA Local bus slot | S1       |  |  |

| Hard drive LED (AT12)                  | J6       | 32-bit VESA Local bus slot | S2       |  |  |

| AT bus hard drive LED                  | J7       |                            |          |  |  |

| Note: The exact location of J7 is unkn | iown.    |                            |          |  |  |

Continued on next page . . .

## **EFA CORPORATION** 4MAHL, 4DMU-50AHL

. . . continued from previous page

| USER CONFIGURABLE SETTINGS                                      |                      |                   |  |  |

|-----------------------------------------------------------------|----------------------|-------------------|--|--|

| Function                                                        | Jumper               | Position          |  |  |

| í HDD I/O CHRDY# disabled                                       | J5                   | Open              |  |  |

| HDD I/O CHRDY# enabled                                          | J5                   | Closed            |  |  |

| í Game port enabled                                             | JP1                  | pins 1 & 2 closed |  |  |

| Game port disabled                                              | JP1                  | pins 2 & 3 closed |  |  |

| í IDE interface disabled                                        | JP3                  | pins 2 & 3 closed |  |  |

| IDE interface enabled                                           | JP3                  | pins 1 & 2 closed |  |  |

| í Floppy drive interface enabled                                | JP4                  | pins 1 & 2 closed |  |  |

| Floppy drive interface disabled                                 | JP4                  | pins 2 & 3 closed |  |  |

| í AT bus IDE interface or HDC enabled                           | JP6                  | pins 2 & 3 closed |  |  |

| AT bus IDE interface or HDC disabled                            | JP6                  | pins 1 & 2 closed |  |  |

| í Factory configured - do not alter                             | JP8                  | Closed            |  |  |

| í Factory configured - do not alter                             | JP9                  | Open              |  |  |

| í Factory configured - do not alter                             | JP10                 | N/A               |  |  |

| í AD12 local bus IDE HDD enabled                                | JP14                 | pins 2 & 3 closed |  |  |

| AD12 local bus IDE HDD disabled                                 | JP14                 | pins 1 & 2 closed |  |  |

| í Factory configured - do not alter                             | JP15                 | pins 2 & 3 closed |  |  |

| í Factory configured - do not alter                             | JP17                 | pins 2 & 3 closed |  |  |

| í Factory configured - do not alter                             | JP18                 | pins 2 & 3 closed |  |  |

| 80486SX enabled                                                 | JP28                 | pins 1 & 2 closed |  |  |

| Other CPU enabled                                               | JP28                 | pins 2 & 3 closed |  |  |

| í Factory configured - do not alter                             | JP29                 | pins 1 & 2 closed |  |  |

| í Factory configured - do not alter                             | JP30                 | pins 1 & 2 closed |  |  |

| í Factory configured - do not alter                             | JP35                 | pins 1 & 2 closed |  |  |

| í Factory configured - do not alter                             | JP39                 | Open              |  |  |

| í Factory configured - do not alter                             | JP40                 | Open              |  |  |

| í Factory configured - do not alter                             | JP41                 | Open              |  |  |

| í Factory configured - do not alter                             | JP42                 | Open              |  |  |

| í Factory configured - do not alter                             | JP50                 | N/A               |  |  |

| Note: JP28 is only configurable when you have a 80486SX PQFP mo | ounted on the mainbo | ard.              |  |  |

| The exact location of JP41 is unknown.                          |                      |                   |  |  |

| SERIAL PORT CONFIGURATION |                   |                   |  |  |  |

|---------------------------|-------------------|-------------------|--|--|--|

| Port 1 (CN3)              | JP7               | JP5               |  |  |  |

| í COM1                    | Pins 1 & 2 closed | pins 1 & 2 closed |  |  |  |

| COM3                      | Pins 2 & 3 closed | pins 1 & 2 closed |  |  |  |

| Disabled                  | N/A               | pins 2 & 3 closed |  |  |  |

| SERIAL PORT CONFIGURATION |                   |                   |  |  |  |

|---------------------------|-------------------|-------------------|--|--|--|

| Port 2 (CN2)              | JP11              | JP13              |  |  |  |

| í COM2                    | Pins 1 & 2 closed | pins 1 & 2 closed |  |  |  |

| COM4                      | Pins 2 & 3 closed | pins 1 & 2 closed |  |  |  |

| Disabled                  | N/A               | pins 2 & 3 closed |  |  |  |

Continued on next page  $\dots$

## **EFA CORPORATION** 4MAHL

. . . continued from previous page

| PARALLEL PORT CONFIGURATION |                   |                   |  |  |  |

|-----------------------------|-------------------|-------------------|--|--|--|

| Port                        | JP2               | JP12              |  |  |  |

| í LPT2                      | pins 1 & 2 closed | pins 1 & 2 closed |  |  |  |

| LPT3                        | pins 2 & 3 closed | pins 1 & 2 closed |  |  |  |

| Disabled                    | N/A               | pins 2 & 3 closed |  |  |  |

| DRAM CONFIGURATION |              |              |  |  |

|--------------------|--------------|--------------|--|--|

| Size               | Bank 0       | Bank 1       |  |  |

| 1MB                | (4) 256K x 9 | NONE         |  |  |

| 1MB                | NONE         | (4) 256K x 9 |  |  |

| 2MB                | (4) 256K x 9 | (4) 256K x 9 |  |  |

| 4MB                | (4) 1M x 9   | NONE         |  |  |

| 4MB                | NONE         | (4) 1M x 9   |  |  |

| 5MB                | (4) 1M x 9   | (4) 256K x 9 |  |  |

| 5MB                | (4) 256K x 9 | (4) 1M x 9   |  |  |

| 8MB                | (4) 1M x 9   | (4) 1M x 9   |  |  |

| 16MB               | (4) 4M x 9   | NONE         |  |  |

| 16MB               | NONE         | (4) 4M x 9   |  |  |

| 17MB               | (4) 4M x 9   | (4) 256K x 9 |  |  |

| 17MB               | (4) 256K x 9 | (4) 4M x 9   |  |  |

| 20MB               | (4) 4M x 9   | (4) 1M x 9   |  |  |

| 20MB               | (4) 1M x 9   | (4) 4M x 9   |  |  |

| 32MB               | (4) 4M x 9   | (4) 4M x 9   |  |  |

| 64MB               | (4) 16M x 9  | NONE         |  |  |

| 64MB               | NONE         | (4) 16M x 9  |  |  |

| CACHE CONFIGURATION    |             |             |             |  |  |

|------------------------|-------------|-------------|-------------|--|--|

| Size Bank 0 Bank 1 TAG |             |             |             |  |  |

| 64KB                   | (4) 8K x 8  | (4) 8K x 8  | (1) 8K x 8  |  |  |

| 128KB                  | (4) 32K x 8 | NONE        | (1) 8K x 8  |  |  |

| 256KB                  | (4) 32K x 8 | (4) 32K x 8 | (1) 32K x 8 |  |  |

| CACHE JUMPER CONFIGURATION |                                                         |        |        |            |            |

|----------------------------|---------------------------------------------------------|--------|--------|------------|------------|

| Size                       | JP21                                                    | JP22   | JP23   | JP26       | JP27       |

| 32KB                       | Open                                                    | Open   | Open   | Open       | pins 2 & 3 |

| 64KB                       | Open                                                    | Open   | Closed | Open       | pins 1 & 2 |

| 128KB                      | Open                                                    | Closed | Closed | pins 1 & 2 | pins 2 & 3 |

| 256KB                      | Closed                                                  | Closed | Closed | pins 2 & 3 | pins 1 & 2 |

| Note: Pins desig           | Note: Pins designated should be in the closed position. |        |        |            |            |

Continued on next page . . .

## **EFA CORPORATION** 4MAHL

. . . continued from previous page

|               | CPU TYPE CONFIGURATION |       |       |       |       |       |       |

|---------------|------------------------|-------|-------|-------|-------|-------|-------|

| Туре          | SW1/1                  | SW1/2 | SW1/3 | SW1/4 | SW1/5 | SW1/6 | SW1/7 |

| CX486SX       | On                     | Off   | On    | Off   | On    | Off   | Off   |

| CX487SX       | On                     | Off   | On    | Off   | On    | Off   | Off   |

| CX486S        | Off                    | Off   | Off   | On    | Off   | Off   | Off   |

| 80486SX       | Off                    | Off   | Off   | On    | Off   | Off   | Off   |

| 80486DX(PQFP) | On                     | Off   | On    | Off   | On    | On    | On    |

| 80486DX       | On                     | Off   | On    | Off   | On    | Off   | Off   |

| ODP486SX      | On                     | On    | Off   | Off   | On    | Off   | Off   |

| 80486DX2      | On                     | Off   | On    | Off   | On    | Off   | Off   |

|                                     | CPU TYPE CONFIGURATION (CONT.) |                   |

|-------------------------------------|--------------------------------|-------------------|

| Speed                               | JP47                           | JP49              |

| CX486SX                             | N/A                            | pins 1 & 2 closed |

| CX487SX                             | N/A                            | N/A               |

| CX486SX + CX487SX                   | Closed                         | pins 2 & 3 closed |

| CX486S                              | Open                           | pins 1 & 2 closed |

| 80486SX                             | Open                           | pins 1 & 2 closed |

| 80486DX(PQFP)                       | Open                           | pins 1 & 2 closed |

| 80486DX                             | Open                           | pins 1 & 2 closed |

| ODP486SX                            | Open                           | pins 1 & 2 closed |

| 80486DX2                            | Open                           | pins 1 & 2 closed |

| Note: The exact location of JP49 is | s unknown.                     |                   |

|         | CPU SPEED CONFIGURATION |       |       |                   |  |  |  |

|---------|-------------------------|-------|-------|-------------------|--|--|--|

| Speed   | SW2/1                   | SW2/2 | SW2/3 | JP48              |  |  |  |

| 20MHz   | Off                     | Off   | Off   | pins 2 & 3 closed |  |  |  |

| 25MHz   | On                      | Off   | Off   | pins 2 & 3 closed |  |  |  |

| 33MHz   | On                      | On    | On    | pins 2 & 3 closed |  |  |  |

| 40MHz   | On                      | On    | Off   | pins 1 & 2 closed |  |  |  |

| 50i MHz | On                      | Off   | Off   | pins 1 & 2 closed |  |  |  |

| 50MHz   | Off                     | Off   | On    | pins 1 & 2 closed |  |  |  |

| 66i MHz | On                      | On    | On    | pins 1 & 2 closed |  |  |  |

| VESA WAIT STATE/BUS SPEED CONFIGURATION |               |                   |                   |                   |  |

|-----------------------------------------|---------------|-------------------|-------------------|-------------------|--|

| Speed Wait states JP36 JP37 JP38        |               |                   |                   |                   |  |

| <=33MHz                                 | 0 wait states | pins 1 & 2 closed | pins 1 & 2 closed | pins 1 & 2 closed |  |

| > 33MHz                                 | 1 wait state  | pins 2 & 3 closed | pins 2 & 3 closed | pins 2 & 3 closed |  |