# Intel B440FX DP Server Server Board Set

Technical Product Specification

intel

Released Revision 2.7 Order Number 282968-001 October 4, 1996

The B440FX DP Server baseboard may contain design defects or errors known as errata. Characterized errata that may cause the B440FX DP Server baseboard's behavior to deviate from published specifications are documented in the B440FX DP Server Specification Update.

#### **Revision History**

| Revision    | Revision History                                                             | Date  |

|-------------|------------------------------------------------------------------------------|-------|

| Rev 0.9-2.6 | Preliminary releases of the B440FX DP Server Technical Product Specification | 7/96  |

| Rev 2.7     | Preliminary release of the B440FX DP Server Technical Product Specification  | 10/96 |

This product specification applies only to standard B440FX DP Server board with BIOS identifier DA0. Information in this version of the summary applies to the BIOS 1.00.03 DA0. Different versions of the BIOS may look and behave differently.

Changes to this specification will be published in the B440FX DP Server Board Specification Update before being incorporated as a revision to this document.

NOTE: If printing this document from an electronic file, use a PostScript printer with the appropriate PostScript print driver to insure the drawings print clearly.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Technical updates should be obtained by calling Intel Literature or writing:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call in North America 1-800-879-4683, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, Japan (fax only) 81-0-120-478-832, other Countries **0**8-296-9333

† Third-party brands and trademarks are the property of their respective owners.

Copyright © 1996, Intel Corporation. All rights reserved

# $\operatorname{int}_{\mathbf{e}}$

# TABLE OF CONTENTS

| 1. PRODUCT OVERVIEW                                    | 9  |

|--------------------------------------------------------|----|

| 1.1 Related Documentation                              | 9  |

| 2. BOARD SET DESCRIPTION                               |    |

| 2.1 Functional Architecture                            | 10 |

| 2.2 Processor Board                                    |    |

| 2.2.1 PMC and DBX                                      |    |

| 2.3 Processor Subsystem                                |    |

| 2.3.1 Pentium Pro processor                            |    |

| 2.3.2 Processor Bus Termination/Regulation/Power       |    |

| 2.3.3 Processor Vccp Power                             |    |

| 2.3.4 APIC Bus                                         |    |

| 2.3.5 Processor and PCI Clock Generation               |    |

| 2.3.6 Processor Board Controller                       |    |

| 2.4 PCI Bridge and Memory Subsystem                    |    |

| 2.4.1 PCI Host Bridge                                  |    |

| 2.4.2 Memory Controller                                |    |

| 2.4.3 DRAM Array                                       | 14 |

| 2.5 Brittany Connector Interface                       |    |

| 2.6 Baseboard                                          |    |

| 2.6.1 PCI I/O Subsystem                                |    |

| 2.6.2 ISA I/O Subsystem                                |    |

| 2.6.3 Server Management Subsystem                      |    |

| 2.6.4 Primary PCI I/O Subsystem (PCI-0)                |    |

| 2.6.5 PCI-0 Arbitration                                |    |

| 2.6.6 PCI-to-ISA/IDE Subsystem                         |    |

| 2.6.7 I/O APIC and Interrupt Mapping                   | 23 |

| 2.6.8 Super I/O Subsystem                              |    |

| 2.7 Secondary PCI Subsystem (PCI-1)                    |    |

| 2.7.1 PCI-1 Arbitration                                |    |

| 2.7.2 SCSI Subsystem                                   |    |

| 2.7.3 PCI Videa                                        |    |

| 2.7.4 Network Interface Controller (NIC)               |    |

| 2.8 Server Management                                  | 41 |

| 2.8.1 Baseboard Management Microcontroller (BMC)       |    |

| 2.8.2 Front Panel Microcontroller (FPC)                |    |

| 2.8.3 I <sup>2</sup> C Isolation Buffers               |    |

| 2.8.4 Processor Board Management Microcontroller (PBC) |    |

# $\operatorname{int}_{e}$

| 2.8.5 Distributed Integrated Server Management Interface Chip (DISMIC) | 43 |

|------------------------------------------------------------------------|----|

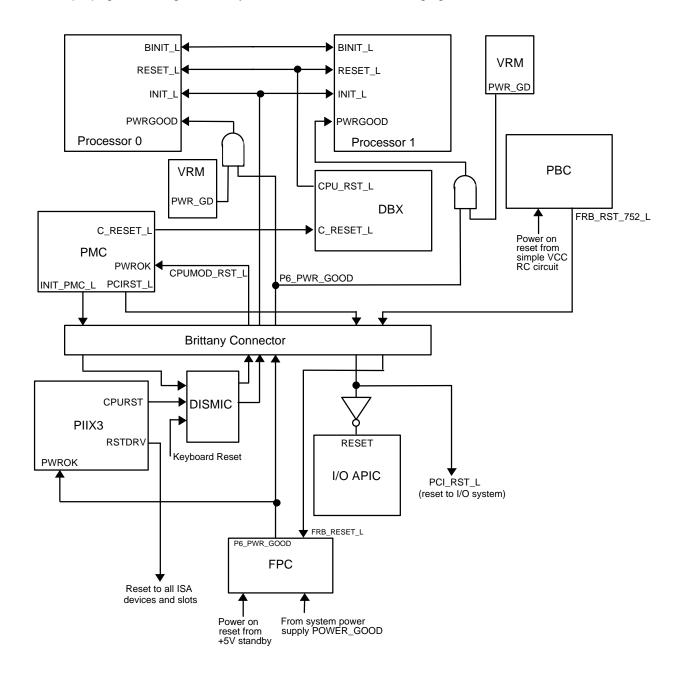

| 2.9 System Reset Control                                               | 43 |

| 2.9.1 Power-up Reset                                                   | 43 |

| 2.9.2 Programmed Reset                                                 | 43 |

| 2.9.3 Soft Reset                                                       | 43 |

| 2.9.4 Reset Signal Flow                                                | 44 |

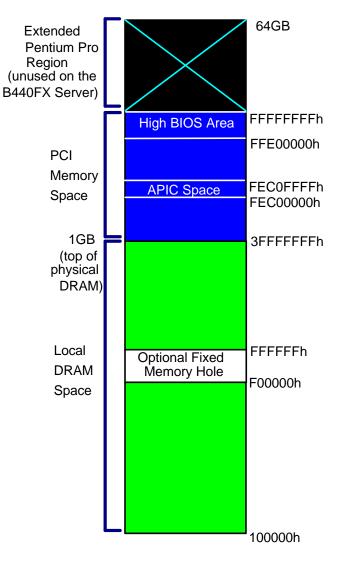

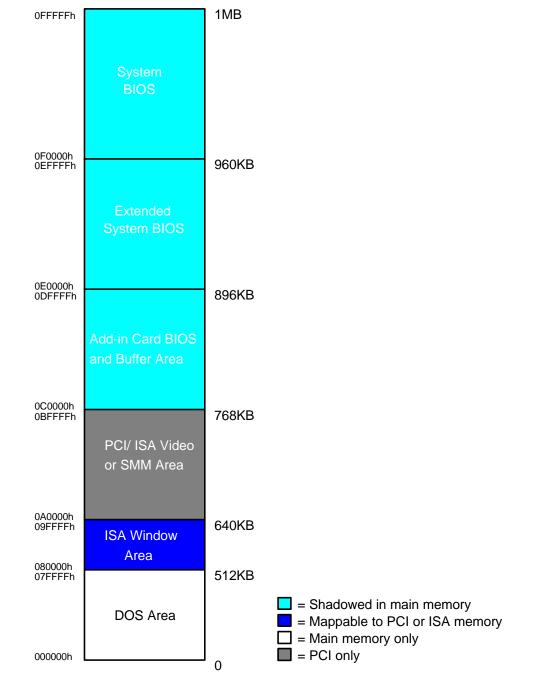

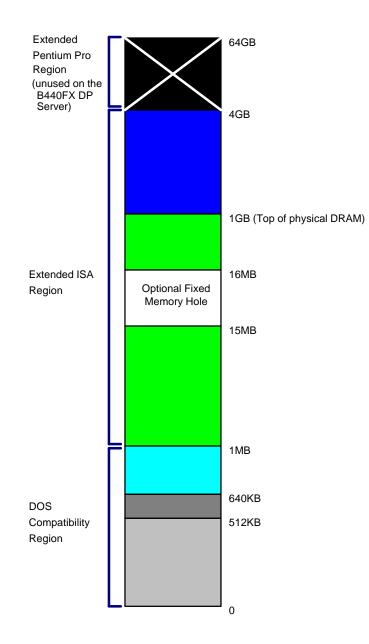

| 3. MEMORY AND OTHER RESOURCE MAPPINGS                                  |    |

| 3.1 Memory Maps                                                        |    |

| 3.2 I/O Map                                                            | 48 |

| 3.3 PCI Map                                                            | 51 |

| 3.4 DMA Channels                                                       | 51 |

| 3.5 Interrupts                                                         | 53 |

| 3.6 BIOS Map                                                           | 55 |

| 3.7 CMOS Map                                                           |    |

| 3.8 NVRAM Map                                                          |    |

| 4. BIOS & CONFIGURATION                                                |    |

| 4.1 System BIOS                                                        |    |

| 4.1.1 Security Features                                                | 60 |

| 4.1.2 Auto-configuration Features                                      | 63 |

| 4.1.3 Reliability Features                                             | 64 |

| 4.1.4 Multiple Language Support                                        | 64 |

| 4.1.5 I <sup>2</sup> C Diagnostic Bus                                  | 64 |

| 4.1.6 Intel MPS 1.4 Support                                            |    |

| 4.1.7 Flash Update Utility                                             | 65 |

| 4.2 Configuration Utilities                                            | 70 |

| 4.2.1 Configurable Options                                             | 71 |

| 4.3 Error Sources and Types                                            | 81 |

| 4.3.1 Error Handlers                                                   | 81 |

| 4.4 BIOS Setup                                                         |    |

| 4.4.1 When to Run Setup                                                | 83 |

| 4.4.2 What can be changed                                              |    |

| 4.5 Setup Utility Operation                                            |    |

| 4.5.1 Setup Command Screen                                             |    |

| 4.5.2 Menu Navigation                                                  |    |

| 4.6 System Configuration Utility (SCU)                                 |    |

| 4.6.1 When to Run the SCU                                              |    |

| 4.6.2 Where the SCU Gets Information                                   |    |

| 4.6.3 Checking the Configuration at Power-on                           |    |

| 4.6.4 How to Use the SCU                                               |    |

# $\operatorname{int}_{\mathbf{e}}$

| 4.6.5 Configuring the System                               |     |

|------------------------------------------------------------|-----|

| 4.7 SCSISelect Utility                                     |     |

| 4.7.1 To Start up SCSISelect                               |     |

| 5. ERROR MESSAGES AND BEEP CODES                           |     |

| 5.1 BIOS Beep Codes                                        |     |

| 5.2 POST Codes and Countdown Codes                         |     |

| 5.2.1 Recovery Port-80 Codes and Countdown Codes Displayed |     |

| 5.2.2 Standard Port-80 Codes and Countdown Codes Displayed | 100 |

| 5.3 POST Error Codes and Messages                          |     |

| 6. BOARD SET SPECIFICATIONS                                |     |

| 6.1 Absolute Maximum Ratings                               | 108 |

| 6.2 Electrical Specifications                              |     |

| 6.2.1 Power Connection                                     | 108 |

| 6.2.2 Power Consumption                                    |     |

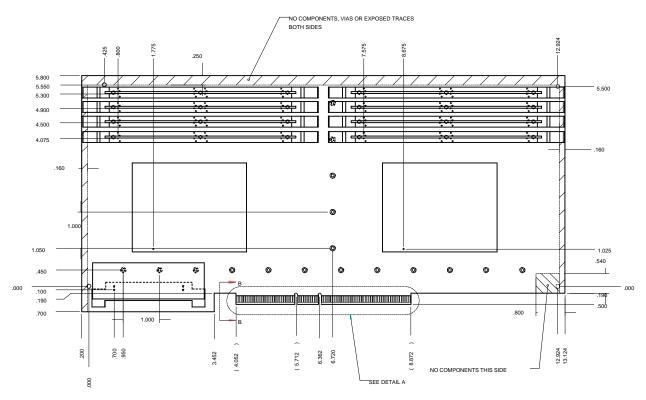

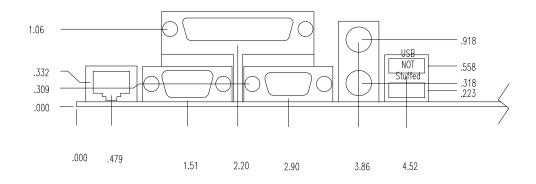

| 6.3 Mechanical Specifications                              | 111 |

| 6.3.1 PCI and ISA Connectors                               |     |

| 6.3.2 Brittany Connector                                   | 114 |

| 6.4 Temperature Requirements                               | 115 |

| 6.5 Shock and Vibration Requirements                       | 115 |

| 6.6 Reliability                                            |     |

| 6.6.1 Mean Time Between Failure - MTBF                     | 115 |

| 6.7 Sample System Environmental Testing                    |     |

| 7. SUPPORTED ENVIRONMENTS                                  |     |

| 7.1 Supported Operating Systems                            |     |

| 7.1.1 B440FX DP Server will not support NetWare 4.1 SMP    | 118 |

| 7.2 Supported Adapters                                     | 118 |

| 7.2.1 PCI Hard Disk Controllers                            |     |

| 7.2.2 ISA Hard Disk Controllers                            |     |

| 7.2.3 PCI Network Interface Cards                          |     |

| 7.2.4 ISA Ethernet Network Interface Cards                 | 120 |

| 7.2.5 PCI Token Ring Network Interface Cards               |     |

| 7.2.6 Server Management Cards                              |     |

| 7.2.7 PCI Video Adapters                                   |     |

| 7.3 Supported Drivers                                      |     |

| 7.4 Memory and Processor Upgrades                          | 121 |

| 7.4.1 Memory                                               |     |

| 7.4.2 Processors                                           |     |

| 7.4.3 Video DRAM                                           |     |

# $\operatorname{int}_{e}$

| 8. CONNECTOR PINOUTS                    | 126 |

|-----------------------------------------|-----|

| 9. APPENDIX A - PRODUCT CODES           | 151 |

| 9.1 Boards                              |     |

| 9.2 System                              |     |

| 9.2.1 Packing lists (Balboa Systems)153 |     |

| 10. APPENDIX B - CUSTOMER SUPPORT       | 157 |

| 10.1 Faxback                            |     |

| 10.2 Windows Help Files                 |     |

| 10.3 Intel Application Support157       |     |

| 10.3.1 Hotline                          |     |

| 10.3.2 BBS 158                          |     |

| 10.3.3 Internet                         |     |

## **FIGURES**

| Figure 2-1 B440FX DP Server Functional Block Architecture | . 10 |

|-----------------------------------------------------------|------|

| Figure 2-2 B440FX DP Server Processor Board Layout        | 11   |

| Figure 2-3 Processor Subsystem Block Diagram              |      |

| Figure 2-4 DIMMs and DRAM Row Boundaries                  | . 15 |

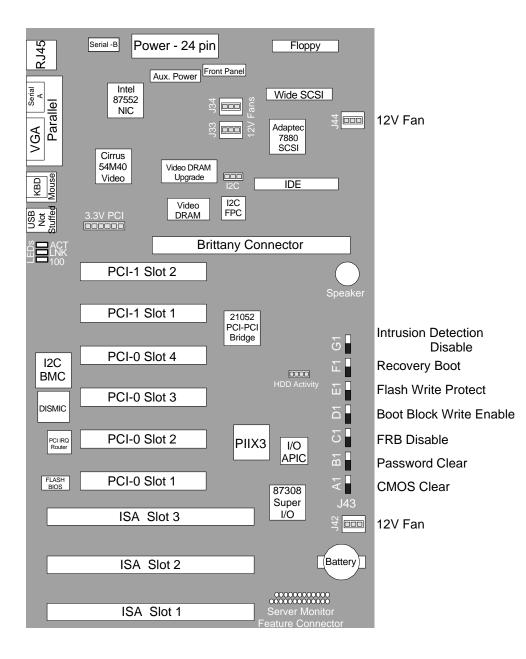

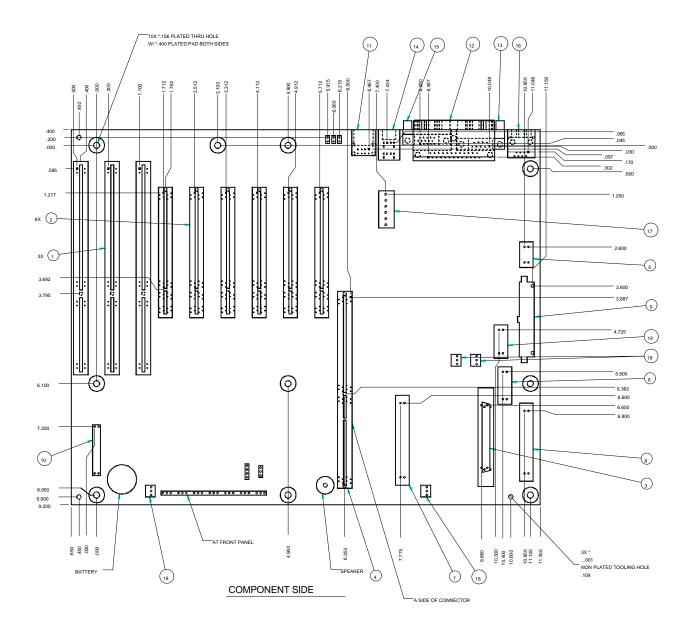

| Figure 2-5 B440FX DP Server Baseboard Layout              | . 17 |

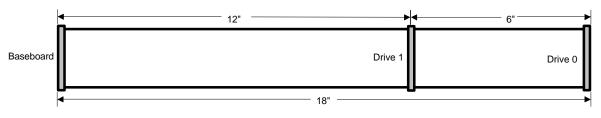

| Figure 2-6 IDE Cable Requirements                         |      |

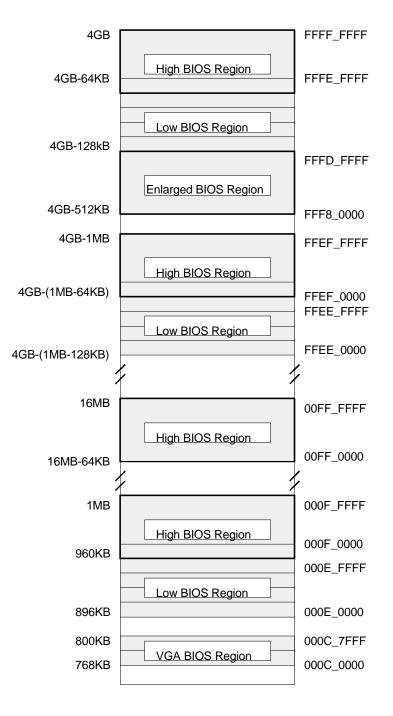

| Figure-2-7 Flash Memory Map                               |      |

| Figure 2-8 PCI Interrupt Routing                          |      |

| Figure 2-9 Interrupt Connections                          |      |

| Figure 2-10 Embedded SCSI PCI Signals                     |      |

| Figure 2-11 SCSI Bus Signals                              |      |

| Figure 2-12 Network Controller Subsystem                  |      |

| Figure 2-13 Embedded NIC PCI Signals                      |      |

| Figure 2-14 NIC Status LEDs                               |      |

| Figure 2-15 B440FX DP Server Management Architecture      |      |

| Figure 2-16 System Reset Flow                             |      |

| Figure 3-1 Extended Memory Map                            |      |

| Figure 3-2 DOS Compatible Memory Regions                  |      |

| Figure 3-3 Pentium Pro Memory Address Space               | . 47 |

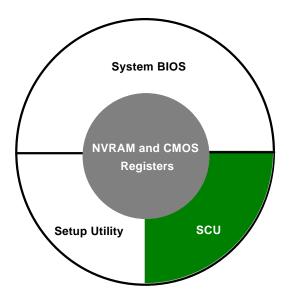

| Figure 4-1 B440FX DP Server BIOS Architecture             |      |

| Figure 6-1 Processor Board Mechanical Diagram             |      |

| Figure 6-2 Baseboard Mechanical Diagram                   |      |

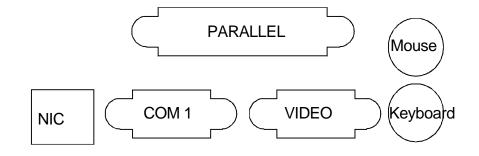

| Figure 6-3 I/O Connector Map                              |      |

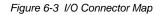

| Figure 6-4 I/O Connector Mechanical Diagram               |      |

| Figure 6-5 Brittany Connector Edge Connector              |      |

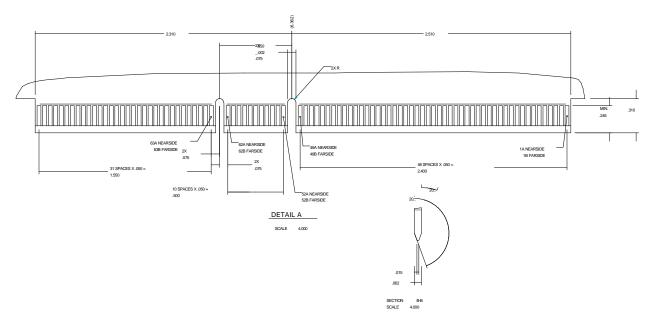

| Figure 8-1 IDE Cable Requirements                         |      |

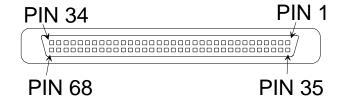

| Figure 8-2 Wide SCSI Connector                            |      |

| Figure 8-3 SMM Feature Connector Layout                   | 143  |

|                                                           |      |

## TABLES

| Table 2-1 PCI-0 Arbitration Connections               |     |

|-------------------------------------------------------|-----|

| Table 2-2 PCI Interrupt Sharing                       |     |

| Table 2-3 Interrupt Definitions                       |     |

| Table 2-4 PCI-1 Arbitration Connections               |     |

| Table 2-5 Embedded SCSI Supported PCI Commands        |     |

| Table 2-6 Video Chip Supported PCI Commands           |     |

| Table 2-7 Standard VGA Modes                          |     |

| Table 2-8 Extended VGA Modes                          |     |

| Table 3-1 I/O Map                                     |     |

| Table 3-2 PCI Configuration IDs and Device Numbers    |     |

| Table 3-3 DMA Channel Mapping                         |     |

| Table 3-4 Interrupt Mapping                           |     |

| Table 3-5 Flash Map Summary                           |     |

| Table 3-6 CMOS Map Summary                            |     |

| Table 3-7 NVRAM Map                                   |     |

| Table 4-1 Security Features Operating Model           |     |

| Table 4-2 User Binary Area Scan Point Definitions     |     |

| Table 4-3 Configurable Options (part 1) Error! Book   |     |

| Table 4-4 Configurable Options (part 2)               |     |

| Table 4-5 Configurable Options (part 3)               |     |

| Table 5-1 Beep Codes                                  |     |

| Table 5-2. Port-80h and Countdown Code Definition     |     |

| Table 5-3 Recovery Port-80 Codes                      |     |

| Table 5-4 Standard Port-80 Codes                      |     |

| Table 5-5 POST Error Codes                            |     |

| Table 6-1 Absolute Maximum Ratings                    |     |

| Table 6-2 B440FX DP Server Power Consumption          |     |

| Table 6-3 Sample 330 Watt Power Supply Output Summary |     |

| Table 6-4 System MTBF                                 |     |

| Table 7-1 Supported Operating Systems                 |     |

| Table 7-2 PCI Hard Disk Controllers                   |     |

| Table 7-3 ISA Hard Disk Controllers                   | 121 |

#### B440FX DP Server Technical Product Specification

| Table 7-4 PCI Network Interface Cards                                         | 121 |

|-------------------------------------------------------------------------------|-----|

| Table 7-5 ISA Ethernet Network Interface Cards                                | 122 |

| Table 7-6 PCI Token Ring Network Interface Cards                              | 122 |

| Table 7-7 Server Management Cards                                             | 122 |

| Table 7-8 PCI Video Adapters                                                  |     |

| Table 7-9 Supported Drivers - Ships with Systems                              | 124 |

| Table 7-10 Qualified DIMM Memory                                              | 126 |

| Table 7-11 Supported Processors (Preliminary)                                 | 128 |

| Table 7-12 Video DRAM Vendors                                                 | 128 |

| Table 8-1 Brittany Connector Signal Pinout                                    | 129 |

| Table 8-2 PCI Connector Signal Descriptions                                   |     |

| Table 8-3 PCI Connector Signal Pinout                                         | 134 |

| Table 8-4 PCI - Bus# Configuration IDs                                        | 135 |

| Table 8-5 Add-in Hard Disk Controller Activity Connector Pinout               | 135 |

| Table 8-6 ISA Connector Signal Pinout                                         | 136 |

| Table 8-7 Video Port Connector Pinout                                         | 137 |

| Table 8-8 IDE Connector Pinout                                                | 137 |

| Table 8-9 Keyboard Connector Pinout                                           |     |

| Table 8-10 Wide SCSI Connector Pinout                                         |     |

| Table 8-11 Serial Port Connector Pinout                                       | 140 |

| Table 8-12 Parallel Port Connector Pinout                                     | 142 |

| Table 8-13 Floppy Port Connector Pinout                                       | 142 |

| Table 8-14 Mouse Connector Pinout                                             |     |

| Table 8-15 Server Monitor Module (SMM) Feature Connector Signal Descriptions* | 143 |

| Table 8-16 12V Fan Pinout                                                     | 145 |

| Table 8-17 5V Fan Pinout                                                      | -   |

| Table 8-18 RJ-45 Network Connector Pinout                                     |     |

| Table 8-19 Universal Serial Bus Connector Pinout                              |     |

| Table 8-20 14-pin Auxiliary Power Connector Pinout                            |     |

| Table 8-21 24-pin Main Power Connector Pinout                                 |     |

| Table 8-22 PCI Compliant 3.3V Connector Pinout*                               |     |

| Table 8-23 <sup>2</sup> C Connector Pinout                                    | 148 |

| Table 8-24 Front Panel Connector Pinout                                       |     |

| Table 8-25 Connector Specifications                                           |     |

| Table 8-26 Baseboard Module Jumpers                                           |     |

| Table 8-27 Processor/Memory Module Jumpers                                    |     |

| Table 9-1 Board Product Codes                                                 |     |

| Table 9-2 System Product Codes                                                | 154 |

## **1. PRODUCT OVERVIEW**

The B440FX DP Server is a high performance dual Pentium<sup>®</sup> Pro processor server as well as a high-reliability corporate desktop machine. The baseboard system architecture is based on the Pentium Pro processor and the Intel 82440FX PCIset. The system is partitioned into two modules: a dual Pentium Pro processor/Memory/PCI bridge subsystem (all contained on a processor board) and a baseboard that contains the I/O system and a connection to the processor board. Partitioning the server in this way places all high-speed interconnects on the same board, eliminating the need for connectors. The B440FX DP Server includes the following features:

- Volume server or desktop platform able to support one or two Pentium Pro processors. The system is fully MPS 1.4 compliant with appropriate Pentium Pro extensions. In addition, support (e.g., PCI interrupt to ISA IRQ rerouting) is provided for MP operating systems that may not be fully MPS 1.4 compliant.

- Modular processor/memory card that quickly adapts to processor and memory technology changes.

- System design based on Intel 82440FX PCIset and I/O APIC.

- Support for up to 1GB of memory using 72-bit buffered dual inline memory module (DIMM) devices.

- Primary and secondary PCI segments. The primary PCI bus is compliant with revision 2.1 of the PCI specification. The primary PCI bus, with four expansion slots (one shared with ISA), is provided via the host bridge. The secondary segment, with two slots, is provided via the PCI-to-PCI bridge.

- Three ISA slots (one shared with PCI) and PC Compatibility I/O (serial, parallel, mouse, and keyboard).

- Onboard PCI I/O, including SCSI, IDE, Video, and LAN controllers.

- Server management features, including thermal/voltage and ECC monitoring.

- Flash BIOS support for all of the above.

#### 1.1 Related Documentation

Balboa Chassis Technical Product Specification Columbus II Chassis Technical Product Specification B440FX DP Server Performance Report B440FX DP Server Product Guide Adaptec AIC-7880 SCSI Software Guide BB440FX DP Server system Data Sheet LANDesk Server Manager 2.52 TPS B440FX DP Server Board Specification Update

## 2. BOARD SET DESCRIPTION

### 2.1 Functional Architecture

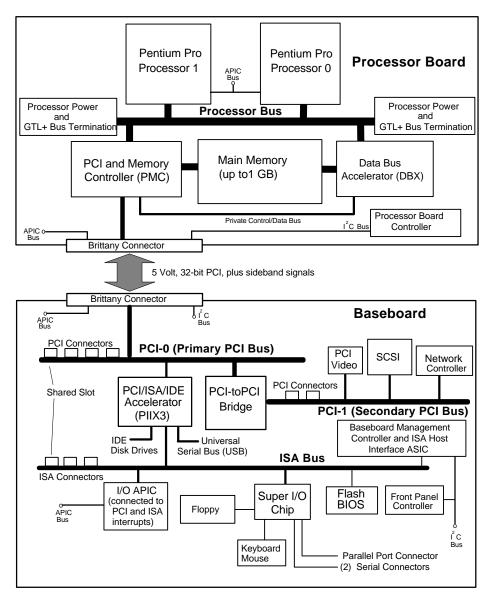

This section provides an overview of the B440FX DP Server, explaining the functional blocks and their relationships to each another. The following diagram shows the functional architecture of the server and the system architecture that it supports. The dotted lines surround the major functional blocks. The top half of the diagram shows the processor board, and the bottom half shows the baseboard.

Figure 2-1 B440FX DP Server Functional Block Architecture

### 2.2 Processor Board

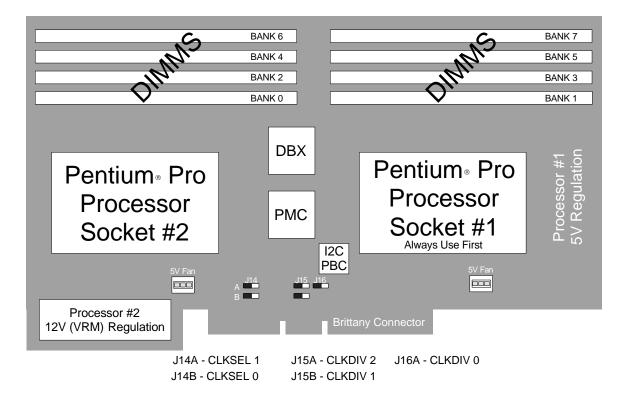

The dual processor module for the B440FX DP Server system consists of two devices: the PCI and Memory Controller (PMC) and the Data Bus Accelerator (DBX). The processor board connects to the baseboard on an interface known as the Brittany connector.

#### 2.2.1 PMC and DBX

Two devices from the Intel 82440FX PCIset, PMC and DBX, form the core of the processor board design. These devices implement the host bridge function between the Pentium Pro processors and PCI I/O system. As the host bridge, they maintain proper ordering of operations by trapping synchronization events and flushing buffers appropriately. The PMC and DBX provide the 32-bit address/64-bit data processor bus interface, which operates at 66MHz (or 60MHz, depending on processor frequency) in the GTL+ signaling environment. The PMC provides a 32-bit PCI interface which operates synchronously in a 5V signaling environment at half the processor bus frequency.

The PMC also acts as memory controller for the system, and the DBX provides the data path to memory. They communicate with each other by using a private control and data bus, which operates independently of transactions on the processor bus and PCI bus. This memory controller supports up to 1GB of ECC memory, using Fast Page Mode (FPM) or Extended Data Out (EDO) DRAMs. ECC can detect and correct single-bit errors and can detect multiple-bit errors.

Figure 2-2 B440FX DP Server Processor Board Layout

### 2.3 Processor Subsystem

The Processor subsystem resides on the plug-in module. It contains the following:

- Dual Pentium Pro processor sockets

- Pentium Pro processor bus, with GTL+ termination and term. power supply

- APIC bus

- Clock generation

- Plug-in 12V DC-to-DC converter for secondary processor (processor 1) Vccp power

- Onboard 5V DC-to-DC converter for the primary processor (processor 0) Vccp power

- Processor board management microcontroller, and I<sup>2</sup>C-based thermal monitor

**NOTE:** If you are using only a single processor, the primary processor must be installed first. When you install the second processor, you must also install a Vccp power module. Both processors must be of the same revision and have identical clock frequencies.

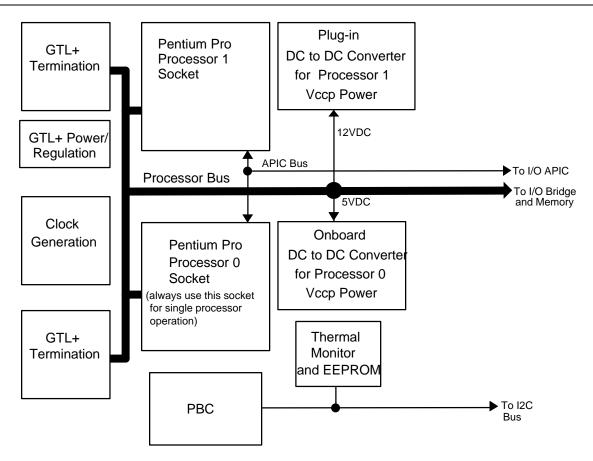

Figure 2-3 Processor Subsystem Block Diagram

#### 2.3.1 Pentium Pro processor

The Pentium Pro processor, housed in a 387-pin dual-cavity PGA package, is the next generation Intel architecture microprocessor. Currently, the package contains two devices: a 5.5 million transistor CPU core with 8KB primary cache, and 15.5 million transistor 256KB secondary cache that communicates with the CPU using a dedicated internal bus. The Pentium Pro external interface is designed to be MP ready. Each processor contains a local APIC section for interrupt handling in the multi-processor and uni-processor environments.

#### 2.3.2 Processor Bus Termination/Regulation/Power

The dual Pentium Pro processors connect to the processor bus. The processors are socketed, allowing the option to install one processor on shipment and upgrades supplied later. The termination circuitry, required by the processor bus (GTL+) signaling environment, has 1.5V termination power.

#### 2.3.3 Processor Vccp Power

DC-to-DC converters provide Vccp power for each processor. Processor 0 Vccp power (14A) is derived from the 5V supply using onboard circuitry. Processor 1 power is derived from the 12V supply using a plug-in module. Refer to the latest revision of the *VRM 8 Data Sheet* for more information.

#### 2.3.4 APIC Bus

Interrupt notification and generation for the Pentium Pro processors is done using an independent path between local APICs in each processor and an I/O APIC located on the baseboard. This simple bus consists of two data bits and a clock line. Refer to "I/O APIC" later in this chapter for more information.

#### 2.3.5 Processor and PCI Clock Generation

All buses on the B440FX DP Server operate using synchronous clocks. The processor bus (66MHz or 60MHz) and the PCI bus (33MHz or 30MHz) clocks are synthesized by circuitry from the processor module from a master clock on the baseboard. The PCI bus clock is sent back to the baseboard for replication and distribution. One copy of the PCI clock is returned to the processor board for use by the PMC.

Two frequency select signals, CLK\_SEL[1::0], control the frequency of the master host clock. To minimize the skew between the various host and PCI clocks, multiple copies of tightly controlled host clocks and PCI clocks are generated on the processor board. In the B440FX DP Server implementation, one copy of the PCI clock is sent to the baseboard for replication by a phase lock loop clock buffer chip, with feedback to the processor module for the PMC. This scheme gives multiple tightly controlled host and PCI clocks with a controlled skew between the host and PCI clocks.

#### 2.3.6 Processor Board Controller

A microcontroller directly monitors voltages and error signals on the processor(s). The I<sup>2</sup>C interface on the controller supports two onboard thermal monitor devices, one of which contains an EEPROM for non-volatile storage of vital information.

intel

### 2.4 PCI Bridge and Memory Subsystem

All high-speed interconnections between the processor bus, PCI host bridge, and system memory are contained on the processor board. The PCI host bridge, the memory controller, and DIMM sites are all found in this subsystem.

#### 2.4.1 PCI Host Bridge

The PCI host bridge consists of two of the 208-pin PQFP devices in the Intel 82440FX PCIset:: the PMC (control part) and the DBX (data part). These two devices coordinate operations over an independent private bus. The PCI host bridge supports one or two Pentium Pro processors at a processor bus frequency of up to 66 MHz, with 32-bit addressing, optimized 4-deep in-order and request queue (IOQ), multi-processing support, dynamic deferred transaction support, and USWC support. The host bridge translates address and data operations from the GTL+ signaling environment on the processor bus to a PCI Rev. 2.1 compliant, 5V signaling environment.

The PCI interface provides greater than 100 MB/s data streamlining for PCI to DRAM accesses, while supporting concurrent Pentium Pro and PCI transactions to main memory. This is accomplished using extensive data buffering with processor-to-DRAM and PCI-to-DRAM write data buffering and write-combining support for processor-to-PCI burst writes. In addition to the host and PCI to ISA bridge functions, five PCI masters can be supported.

#### 2.4.2 Memory Controller

The PMC performs the function of memory controller for the B440FX DP Server. Total memory from 16MB to 1GB of DIMM DRAM is supported, with the DBX providing a 72-bit non-interleaved pathway to main memory. The memory controller supports FPM and EDO DRAMs.

ECC can detect and correct single-bit errors (SED/SEC), detect all double-bit errors, and detect some multiple-bit errors (DED). Only memory ECC is supported; the B440FX DP Server does not support ECC on processor signals or parity checking. On power-up, ECC is disabled.

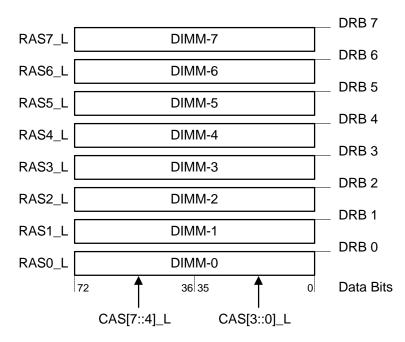

### 2.4.3 DRAM Array

The memory controller can automatically detect and initialize the memory array, depending upon the type, size, and speed of installed DIMM devices. 8, 16, 32, 64, and 128 MB DIMMs are supported. Memory is partitioned as eight banks of DRAM, one bank per installed DIMM, each providing 72 bits of non-interleaved memory (64-bit main memory plus ECC). The PMC provides a row address strobe (RASx\_L) for each bank, and column address strobes (CASx\_L) for all data bits. DIMM sockets should be populated in sequence (DIMM-0 is first and DIMM-7 is last). Installed memory is automatically sized and allocated by the PMC. The following figure shows the correspondence between installed DIMMs, PMC RASn\_L signals, and DRAM row boundary (DRB) register values.

**NOTE:** If 4 or fewer DIMMs are installed, faster memory timing is available: x-2-2-2 for EDO devices, x-3-3-3 for FPM devices. With 5 to 8 DIMMs, memory timing is x-3-3-3 for EDO and x-4-4-4 for FPM.

Figure 2-4 DIMMs and DRAM Row Boundaries

### 2.5 Brittany Connector Interface

The Brittany connector interface connects the processor board to the baseboard. It operates as a standard 5V PCI connection, and it works with the Pentium Pro host bus at half frequency. The interface is a modified 33MHz 5V PCI implementation, with sideband signals specific to the B440FX DP Server (or subsequent) baseboard designs. Included among the sideband signals are I/O APIC and I<sup>2</sup>C buses. The I/O APIC bus minimizes interrupt latency time by providing a direct pathway from the I/O APIC device on the baseboard to the local APIC(s) in the processor(s). The I<sup>2</sup>C bus provides an independent communications path for onboard diagnostics and server management.

The edge connector resembles a 64-bit PCI card.

### 2.6 Baseboard

The baseboard contains a PCI and ISA I/O system with several embedded devices for video, network, and disk control. It provides server management, hardware support monitoring, interrupt control (I/O APIC and standard PC), and it connects to the processor board via the Brittany connector.

The baseboard consists of the following major components:

### 2.6.1 PCI I/O Subsystem

PCI is the primary I/O bus for The B440FX DP Server . There are two PCI bus segments, PCI-0 and PCI-1; they are compliant with revision 2.1 of the PCI specification and operate at up to 33 MHz. PCI-0 is the primary PCI segment, lying directly beneath the PMC. The PCI-1 connects to the PCI-0 using a PCI-to-PCI bridge in a hierarchical bus structure. Unlike previous Intel SSPD server designs that have provided the two PCI segments as peers of each other, the B440FX DP Server uses independent arbitration and data buffering to run the two hierarchical PCI segments concurrently with the processor bus and with each other. However, there are functional differences in the way PCI configuration cycles are handled. According to PCI architecture, the PCI-to-PCI bridge effectively extends the electrical capacity of PCI-0, providing an extensive amount of embedded functionality on a single PCI bus.

#### 2.6.2 ISA I/O Subsystem

The ISA I/O subsystem on the B440FX DP Server provides three ISA slots. The ISA bus supports an embedded I/O APIC and Flash BIOS. A National Semiconductor Super I/O† chip resides on the ISA bus and supports direct connection of the keyboard, mouse, floppy drive, and standard parallel and serial ports.

#### 2.6.3 Server Management Subsystem

The B440FX DP Server system offers server management features that are implemented using three separate microcontrollers and one ASIC.

# int<sub>el</sub>®

Figure 2-5 B440FX DP Server Baseboard Layout

#### 2.6.4 Primary PCI I/O Subsystem (PCI-0)

All I/O for the B440FX DP Server, including PCI and PC-compatible, is directed through PCI-0. Unlike other Intel SSPD server products, which provide two PCI segments as peers in the PCI hierarchy, the B440FX DP Server architecture defines PCI-0 as the primary PCI segment and uses PCI-1 as its secondary (subordinate) PCI bus.

In addition to the PCI-to-PCI bridge device (described later), PCI-0 supports the following embedded devices and connectors:

Four 120-pin PCI expansion slot connectors (one physically shared with an ISA slot)

PIIX3 PCI-to-ISA bridge and IDE controller subsystem

Each device under a PCI bridge has its IDSEL signal connected to one bit out of AD[31::16], which acts as a chip select on the PCI bus segment. This determines a unique PCI device ID value for use in configuration cycles.

#### 2.6.5 PCI-0 Arbitration

PCI-0 supports six PCI masters (slots 1 - 4, PIIX3, and PCI-to-PCI bridge). These six PCI masters use resources supplied by the PMC to arbitrate for PCI access.

| PMC Signals       | Device            |

|-------------------|-------------------|

| PHOLD_L / PHLDA_L | PIIX3             |

| REQ4_L / GNT4_L   | PCI-to-PCI Bridge |

| REQ3_L / GNT3_L   | PCI-0 Slot 4      |

| REQ2_L / GNT2_L   | PCI-0 Slot 3      |

| REQ1_L / GNT1_L   | PCI-0 Slot 2      |

| REQ0_L / GNT0_L   | PCI-0 Slot 1      |

#### Table 2-1 PCI-0 Arbitration Connections

#### 2.6.6 PCI-to-ISA/IDE Subsystem

The PCI/ISA/IDE Accelerator, also known as PIIX3, is a multi-function PCI device integrated into the Intel 82440FX PCIset. There are three distinct PCI controllers on the PIIX3: PCI-to-ISA bridge, and PCI-based fast IDE interface. Each function within the PIIX3 has its own set of registers, which when configured, appear to the system as distinct hardware controllers sharing the same PCI bus interface.

This 208-pin QFP device provides the gateway to all PC-compatible I/O devices and features. The B440FX DP Server architecture uses the following PIIX3 functional blocks:

- PCI interface

- ISA bus interface

- IDE interface

- Universal Serial Bus (USB) interface (not currently implemented on the B440FX DP Server).

- System reset control

- ISA-compatible interrupt control and PCI interrupt steering

- PC-compatible timer/counters and DMA controllers

- Baseboard plug and play support

- System power management features

Following are descriptions of five of these functional blocks.

#### 2.6.6.1 PCI Interface

The PIIX3 fully implements a 32-bit PCI master/slave interface, in accordance with the *PCI Local Bus Specification, Rev. 2.1.* On the B440FX DP Server, the PCI interface operates at up to 33 MHz, using the 5V signaling environment.

#### 2.6.6.2 ISA Interface

Operating at up to 8.33 MHz, the PIIX3 provides an ISA bus interface that supports three ISA connectors, Flash memory, the National Super I/O chip, and baseboard management microcontroller ISA interface ASIC.

#### 2.6.6.3 IDE Interface

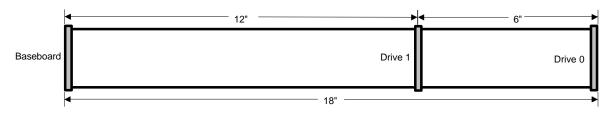

The PIIX3 acts as a PCI-based fast IDE controller. It supports PIO and bus master IDE operations, Mode 4 timings, transfer rates to 22MB/s, buffering for PCI/IDE burst transfers, and master/slave IDE mode. The PIIX3 also supports two IDE channels (primary and secondary) that support two drives each (drives 0 and 1). The B440FX DP Server supports only the primary IDE channel, providing one 40 pin (2 x 20) IDE connector. For the pinout, see Chapter 8.

For proper IDE operation, cable length is specified as shown in the following figure. If no drives are present on an IDE channel, the cable must be removed. If only one drive is installed, it must appear at the end of the cable.

Figure 2-6 IDE Cable Requirements

#### 2.6.6.4 USB Interface

The PIIX3 contains a USB controller with two USB ports. The USB controller moves data between main memory and two devices hooked to the USB connector. An interrupt signal is internally ORed with a PCI interrupt (PCI\_INTA) for use in USB transactions. Software is required to manage the USB interface. The B440FX DP Server provides a stacked dual-USB connector interface on the baseboard, as defined by the *USB Specification, Revision 0.9.* However, the B440FX DP Server does not currently support USB.

#### 2.6.6.5 Compatibility Interrupt Control

The PIIX3 provides the functionality of two 82C59 PIC devices for ISA-compatible interrupt handling. The PIIX3 also supports PCI interrupt steering to the I/O APIC, which is controlled using PCI configuration registers. For a complete discussion of interrupt handling on the B440FX DP Server, refer to "I/O APIC" later in this chapter.

#### 2.6.6.6 ISA I/O Subsystem

The ISA bus interface on the PIIX3 device supports the following connectors and devices:

- Three ISA connector slots, one physically shared with PCI-0 slot 4

- Flash memory for BIOS ROM and extensions

- Intel I/O APIC

- National 87308VUL Super I/O Super I/O chip, for which the B440FX DP Server supports the following:

- \* Two PC-compatible serial ports

- \* Enhanced parallel port

- \* Floppy controller

- \* Keyboard/mouse port

- \* Plug and Play features

- \* Real-time Clock (RTC)

- \* General Purpose I/O (GPIO) bits used in server management and miscellaneous functions

### 2.6.6.7 ISA Connectors

The B440FX DP Server provides three ISA expansion slots that follow the pinout shown in Chapter 8. The ISA slot 3 is shared physically with PCI-0 slot 1.

#### 2.6.6.8 Flash ROM

An 8-bit flash memory (Intel 28F004BV) provides 512K x 8 of BIOS and non-volatile storage space, partitioned as shown in the following figure. The Flash device is directly addressed as 8-bit ISA memory.

Figure-2-7 Flash Memory Map

#### 2.6.6.9 Flash Update Utility Requirements

You may load flash memory from a floppy disk; a Flash update utility is required (FMUP.EXE).

#### 2.6.7 I/O APIC and Interrupt Mapping

The PIIX3 provides compatibility interrupt control and PCI interrupt steering, which is sufficient for uni-processor PC-compatible operation. However, the B440FX DP Server provides the Intel 82093AA I/O APIC device for interrupt handling when using an operating system that supports multi-processing operation. An APIC bus from the I/O APIC to local APICs in each Pentium Pro processor and APIC support built into the PIIX3 minimizes interrupt latency time from compatibility interrupt sources in single and dual processor operation.

**NOTE**: An ISA IRQ for any PCI device is still allocated, so that an operating system can boot from the device. The multi-processing operating systems will switch the IRQ routing from the PIC to IOAPIC after the HAL / MP kernel is loaded.

#### 2.6.7.1 PCI Interrupt Routing

Many multi-processing operating systems are unable to handle interrupts from PCI slots and devices as pure PCI interrupts (via inputs 16-23 of the I/O APIC). Instead, they expect PCI interrupts to be delivered as ISA IRQs. In some cases, multi-processing operating systems want some interrupts delivered by the PC-compatible PIC in the PIIX3, and others by the I/O APIC (mixed mode). Some device drivers check whether the device is operating using one of the traditional IRQ interrupts, and if not (when the PCI interrupt is connected directly to the I/O APIC), the driver fails to install or run properly. The PIIX3 performs internal PCI to IRQ interrupt steering so that PCI interrupts can be delivered to the PIC. However, the PCI interrupt steering feature is unidirectional, which means that it cannot be used to redirect PCI interrupts to the I/O APIC inputs.

For these reasons, the B440FX DP Server provides an external PCI to IRQ rerouter that can either be programmed to pass PCI interrupts to inputs 16-19 of the I/O APIC, or can be programmed to deliver a specific PCI interrupt to an ISA IRQ. A PCI interrupt (PCI\_INTA\_L, PCI\_INTB\_L, PCI\_INTC\_L, or PCI\_INTD\_L) can be individually rerouted to one of these IRQ lines: IRQ3, IRQ4, IRQ5, IRQ6, IRQ7, IRQ9, IRQ10, IRQ11, IRQ12, IRQ14, or IRQ15.

#### 2.6.7.1.1 PCI Interrupt Sharing (Slot Routing)

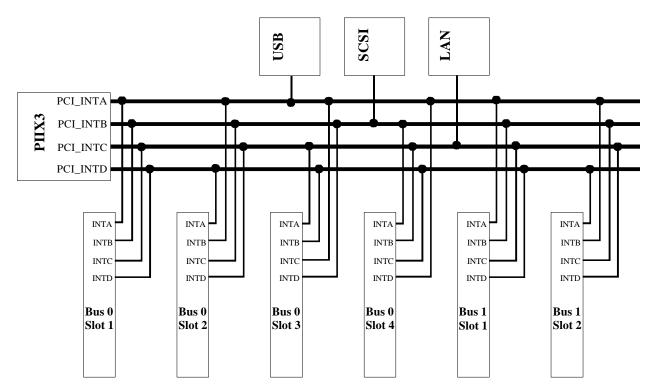

The PIIX3 has four PCI interrupts, INTA through INTD. The table and figure that follow depict the routing of these interrupts to the various PCI devices and slots within the B440FX DP Server baseboard. This information is supplied in the event that a non-PCI 2.1 compliant adapter is used which exhibits problems sharing interrupts.

B440FX DP Server Technical Product Specification

# $\operatorname{int}_{\mathbf{e}}$

|              | PIIX3    | PIIX3    | PIIX3    | PIIX3    |

|--------------|----------|----------|----------|----------|

|              | PCI_INTA | PCI_INTB | PCI_INTC | PCI_INTD |

| PCI-1 Slot 2 | INTD     | INTA     | INTB     | INTC     |

| PCI-1 Slot 1 | INTA     | INTB     | INTC     | INTD     |

| PCI-0 Slot 4 | INTB     | INTC     | INTD     | INTA     |

| PCI-0 Slot 3 | INTC     | INTD     | INTA     | INTB     |

| PCI-0 Slot 2 | INTD     | INTA     | INTB     | INTC     |

| PCI-0 Slot 1 | INTA     | INTB     | INTC     | INTD     |

| Onboard USB  | Х        |          |          |          |

| Onboard SCSI |          | х        |          |          |

| Onboard LAN  |          |          | Х        |          |

Figure 2-8 PCI Interrupt Routing

#### 2.6.7.2 Compatibility Interrupt Mapping

The PIIX3 and National 87308VUL Super I/O contain configuration registers that determine which interrupt source will map to a specific IRQ line. The PIIX3 controls INTx to IRQ mapping, and the National 87308VUL Super I/O controls which embedded function or device will map to an IRQ.

#### 2.6.7.3 NMI and SMI\_L Control

The Server Management SMI\_L control logic presents error signals from various sources on the B440FX DP Server that normally produce an NMI to the I/O APIC as SMI\_L. This logic is contained in the ASIC that provides the ISA interface for the baseboard server management controller. That logic, in combination with baseboard server management features, controls how NMI and SMI\_L are asserted under various fatal error conditions.

#### 2.6.7.4 APIC Bus

The APIC bus that connects the I/O APIC with local APIC(s) in the Pentium Pro processor(s) consists of an APIC clock and two bi-directional data signals (PICD[1::0]). Interrupts are broadcast on the APIC bus as messages conforming to an APIC protocol defined by the register interface embedded in each processor. Multi-processor tables in APIC memory space determine how messages and associated interrupt events are defined to the processors.

#### 2.6.7.5 Interrupt Connections

The following figure illustrates the interrupt connections on the B440FX DP Server between the PIIX3, National 87308VUL Super I/O, and I/O APIC devices.

# $\operatorname{int}_{e}$

Figure 2-9 Interrupt Connections

#### 2.6.7.6 Interrupt Sources

The following table recommends the logical interrupt mapping of interrupt sources on the B440FX DP Server. The actual interrupt map is defined using configuration registers in the PIIX3 and National 87308VUL Super I/O. The I/O redirection registers in the I/O APIC are provided for each interrupt signal, which define hardware interrupt signal characteristics for APIC messages sent to local APIC(s). The information in this table can be used to determine how to program each interrupt.

Table 2-3 Interrupt Definitions

| Interrupt      | Description                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR           | Processor interrupt                                                                                                                                                                                                              |

| NMI            | NMI from DISMIC to processor                                                                                                                                                                                                     |

| IRQ0/<br>MIRQ0 | Baseboard interrupt request 0, connected to input 2 of the I/O APIC. NOTE: For proper operation, the BIOS must set the "IRQ0 enable" bit in PIIX3 register 70h during initialization.                                            |

| IRQ1           | Keyboard                                                                                                                                                                                                                         |

| IRQ3           | Serial port A or B interrupt from National 87308VUL Super I/O device, user-configurable.                                                                                                                                         |

| IRQ4           | Serial port A or B interrupt from National 87308VUL Super I/O device, user-configurable.                                                                                                                                         |

| IRQ5           | Parallel port                                                                                                                                                                                                                    |

| IRQ6           | Floppy disk                                                                                                                                                                                                                      |

| IRQ7           | Parallel port                                                                                                                                                                                                                    |

| IRQ8_L         | RTC                                                                                                                                                                                                                              |

| IRQ9           |                                                                                                                                                                                                                                  |

| IRQ10          |                                                                                                                                                                                                                                  |

| IRQ11          |                                                                                                                                                                                                                                  |

| IRQ12          | Mouse interrupt from National 87308VUL Super I/O                                                                                                                                                                                 |

| IRQ14          | Compatibility IDE interrupt from primary channel IDE devices 0 and 1                                                                                                                                                             |

| IRQ15          |                                                                                                                                                                                                                                  |

| MIRQ1          | Additional IDE interrupt from secondary channel IDE devices 0 and 1 (no secondary IDE channel on B440FX DP Server)                                                                                                               |

| PCI_INTA_L     | PCI Interrupt signal A from PIIX3. Wired to PCI-0 slot 1 INTA_L, PCI-0 slot 2 INTD_L, PCI-0 slot 3 INTC_L, PCI-0 slot 4 INTB_L, PCI-1 slot 1 INTA_L, and PCI-1 slot 2 INTD_L. This interrupt is also used by the USB controller. |

| PCI_INTB_L | PCI Interrupt signal B from PIIX3. Wired to PCI-0 slot 1 INTB_L, PCI-0 slot 2 INTA_L, PCI-0 slot 3 INTD_L, PCI-0 slot 4 INTC_L, PCI-1 slot 1 INTB_L, and PCI-1 slot 2 INTA_L. This interrupt is also used by the SCSI controller.    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_INTC_L | PCI Interrupt signal C from PIIX3. Wired to PCI-0 slot 1 INTC_L, PCI-0 slot 2 INTB_L, PCI-0 slot 3 INTA_L, PCI-0 slot 4 INTD_L, PCI-1 slot 1 INTC_L, and PCI-1 slot 2 INTB_L. This interrupt is also used by the Network controller. |

| PCI_INTD_L | PCI Interrupt signal D from PIIX3. Wired to PCI-0 slot 1 INTD_L, PCI-0 slot 2 INTC_L, PCI-0 slot 3 INTB_L, PCI-0 slot 4 INTA_L, PCI-1 slot 1 INTD_L, PCI-1 slot 2 INTC_L.                                                            |

| SMI_L      | System Management Interrupt. General-purpose error indicator from a control PAL that provides an SMI_L from non-traditional error sources (PERR_L, SERR_L, and others).                                                              |

#### 2.6.8 Super I/O Subsystem

The National Semiconductor 87308VUL Super I/O device contains all of the necessary circuitry to control two serial ports, one IEEE 1284-compatible parallel port, a floppy disk, and a PS/2-compatible keyboard and mouse. The B440FX DP Server provides connector interfaces for all of the above. The B440FX DP Server employs a configuration of the 87308VUL Super I/O chip referred to as Plug and Play (PnP) baseboard mode, which provides an appropriate set of default values for all registers on power-up, at a base address that differs from full ISA PnP compliance. Hardware strapping of the 87308VUL signal pins, pulled high or low on the baseboard, determines the operating mode and base address of the device on power-up, as shown in the following table. The 87308VUL Super I/O also provides general-purpose I/O (GPIO) bits that power up as inputs. Some of these bits are used by server management hardware, and must be properly configured by the BIOS.

#### 2.6.8.1 Serial Ports

One of the two 9-pin D-Sub connectors (Serial port A), along with the VGA connector (described later in this chapter), is stacked under the parallel port connector. The Serial port B connector, which is an optional item, appears as bulkhead mounted. The baseboard supplies a 10 pin header for cabling serial B to the bulkhead.

Each serial port can be set to one of four different COMx ports, and can be enabled separately. When enabled, each port can be programmed to generate edge or level sensitive interrupts. When disabled, serial port interrupts are available to add-in cards.

#### 2.6.8.2 Parallel Port

The National 87308VUL Super I/O provides one IEEE 1284-compatible (ECP/EPP) 25-pin bi-directional parallel port. Hardware strapping enables the parallel port, and sets the port address and interrupt. When disabled, the interrupt is available to add-in cards.

The 25/15 pin connector stacks the parallel port connector over the VGA and Serial A connectors. The pinout is shown in Chapter 8.

#### 2.6.8.3 Floppy Port

The FDC on the National 87308VUL Super I/O is functionally compatible with 82077SL, 82077AA, and 8272A floppy disk controllers. The baseboard provides the 24 MHz clock and termination resistor package. All other FDC functions are integrated into the National 87308VUL Super I/O chip including PLL separator and 16-byte FIFO. The pinout for floppy connector on the baseboard can be found in Chapter 8.

#### 2.6.8.4 Keyboard and Mouse Connectors

The keyboard and mouse connectors are mounted within a single housing. Both connectors are functionally equivalent and the system will recognize the keyboard or the mouse regardless of the connector.

## 2.7 Secondary PCI Subsystem (PCI-1)

The DECchip 21152 PCI-to-PCI bridge device extends the electrical capacity of PCI-0 to form a secondary PCI segment referred to as PCI-1. All PCI transactions on PCI-0 that fall within specified address ranges are forwarded to PCI-1 by the 21152. The 21152 is a 3.3V CMOS, 160-pin, PQFP. For a complete functional specification of the PCI-to-PCI bridge device, refer to the *DECchip 21152 PCI-to-PCI Bridge Data Sheet*

PCI-1 contains the following embedded devices and PCI expansion connectors:

- Adaptec 7880† SCSI host adapter

- Intel 82557 PCI Fast Ethernet controller

- Cirrus Logic CL-GD54M40† VGA controller

- Two PCI expansion slots

#### 2.7.1 PCI-1 Arbitration

PCI-1 supports four PCI masters: slot 1, slot 2, SCSI chip, and network controller. The video chip is a PCI slave which never requires bus mastering, it therefore does not need to arbitrate for PCI-1 access. The four PCI masters, however, must arbitrate for PCI access using resources supplied by the PCI-to-PCI bridge.

| DEC 21052 Arbiter Signals | Device       |

|---------------------------|--------------|

| REQ3_L / GNT3_L           | 82557 chip   |

| REQ2_L / GNT2_L           | SCSI         |

| REQ1_L / GNT1_L           | PCI-1 Slot 2 |

| REQ0_L / GNT0_L           | PCI-1 Slot 1 |

Table 2-4 PCI-1 Arbitration Connections

#### 2.7.2 SCSI Subsystem

The PCI-1 provides an embedded Adaptec AIC-7880 SCSI host adapter. The AIC-7880 contains a double-speed SCSI controller and full-featured PCI bus master interface in a 160-pin PQFP. The AIC-7880 can support 8- or 16-bit Fast SCSI, providing 10MB/s or 20MB/s throughput, or double-speed SCSI that can burst data at 20MB/s or 40MB/s. Sustained throughput may vary depending upon the number and type of SCSI devices connected to the SCSI bus. As a PCI 2.0 bus master, the AIC-7880 supports burst data transfers on PCI up to the maximum rate of 133MB/s using the on-chip 256 byte FIFO.

#### 2.7.2.1 Adaptec 7880 PCI Signals

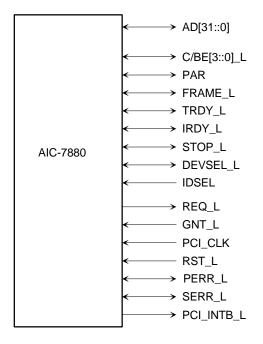

The Adaptec AIC-7880 supports all of the required PCI 2.0 32-bit PCI signals including the PERR\_L and SERR\_L functions. Full PCI parity is maintained on the entire data path through the chip. The device also takes

advantage of PCI interrupt signaling capability, which is hardwired to PCI\_INTB\_L on the B440FX DP Server. The figure below shows the PCI signals supported by the AIC-7880.

Figure 2-10 Embedded SCSI PCI Signals

#### 2.7.2.2 Adaptec AIC-7880 Supported PCI Commands

The AIC-7880 supports the PCI commands listed in the following table:

|               |                       | AIC-7880 Support |        |

|---------------|-----------------------|------------------|--------|

| C/BE [3:0] _L | Command Type          | Target           | Master |

| 0000          | Interrupt Acknowledge | No               | No     |

| 0001          | Special Cycle         | No               | No     |

| 0010          | I/O Read              | Yes              | No     |

| 0011          | I/O Write             | Yes              | No     |

| 0110          | Reserved              | No               | No     |

| 0101          | Reserved              | No               | No     |

| 0110          | Memory Read           | Yes              | Yes    |

Table 2-5 Embedded SCSI Supported PCI Commands

| 0111 | Memory Write                 | Yes | Yes |

|------|------------------------------|-----|-----|

| 1000 | Reserved                     | No  | No  |

| 1001 | Reserved                     | No  | No  |

| 1010 | Configuration Read           | Yes | No  |

| 1011 | Configuration Write          | Yes | No  |

| 1100 | Memory Read Multiple         | **  | Yes |

| 1101 | Dual Address Cycle           | No  | Yes |

| 1110 | Memory Read Line             | **  | Yes |

| 1111 | Memory *Write and Invalidate | *   | Yes |

\* Defaults to Memory Write

\*\* Defaults to Memory Read

The extensions to memory commands (Memory Read Multiple, Memory Read Line, and Memory Write and Invalidate) work with the cache line size register to give the cache controller advance knowledge of the minimum amount of data to expect. The decision to use either the Memory Read Line or Memory Read Multiple command is determined by a bit in the configuration space command register for this device.

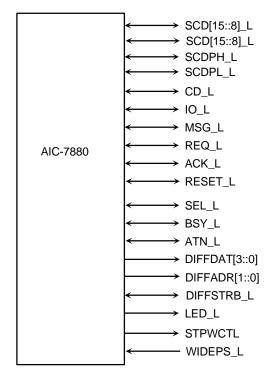

#### 2.7.2.3 SCSI Interface

The AIC-7880 offers 8-bit or 16-bit SCSI operation at data transfer rates of 10, 20, or 40MB/s (although sustained transfer rates may vary depending on the number and type of SCSI devices connected to the SCSI bus). It also offers active negation outputs, controls for external differential transceivers, a disk activity output, and a SCSI terminator power-down control. Active negation outputs reduce the chance of data errors by driving both polarities of the SCSI bus, avoiding indeterminate voltage levels and common-mode noise on long cable runs. The SCSI output drivers can directly drive a 48 mA single-ended SCSI bus with no additional drivers. Synchronous SCSI can handle up to 15 REQs.

#### 2.7.2.3.1 SCSI Bus

The SCSI data bus is 8- or 16-bits wide with odd parity generated per byte. Its control signals are the same for either width. To accommodate 8-bit devices on a 16-bit wide SCSI bus, the AIC-7880 assigns the highest arbitration priority to the low byte of the 16-bit word. This way, 16-bit targets can be mixed with 8-bit if the 8-bit devices are placed on the low data byte. For 8-bit mode, the unused high data byte is self-terminated and need not be connected. During chip power-down, all inputs are disabled to reduce power consumption.

Figure 2-11 SCSI Bus Signals

For more information on the functional architecture of this device, refer to the Adaptec AIC-7880 PCI Bus Master Single-chip SCSI Host Adapter Data Book For the pinout, see Chapter 8.

#### 2.7.3 PCI Video

The B440FX DP Server uses the next generation of integrated video controller and support circuitry: Cirrus Logic CL-GD54M40 32-bit VGA Graphics Accelerator chip containing an SVGA video controller, Clock Generator, and 80 MHz RAMDAC in a 160-pin PQFP. One 256K x 16 DRAM chip provides 512KB of 60ns video memory, and can be expanded to 1MB for improved performance and more video modes. The CL-GD54M40 supports up to 1280 x 1024 resolution and up to 64K colors.

This SVGA subsystem supports analog VGA monitors, single and multi-frequency, interlaced and non-interlaced, up to 87 Hz vertical retrace frequency. The connector is a standard 15-pin VGA connector.

The CL-GD54M40 supports the following PCI commands:

|             |                             | CL-GD54M40 Support |        |

|-------------|-----------------------------|--------------------|--------|

| C/BE_L[3:0] | Command Type                | Target             | Master |

| 0000        | Interrupt Acknowledge       | No                 | No     |

| 0001        | Special Cycle               | No                 | No     |

| 0010        | I/O Read                    | Yes                | No     |

| 0011        | I/O Write                   | Yes                | No     |

| 0110        | Reserved                    | No                 | No     |

| 0101        | Reserved                    | No                 | No     |

| 0110        | Memory Read                 | Yes                | No     |

| 0111        | Memory Write                | Yes                | No     |

| 1000        | Reserved                    | No                 | No     |

| 1001        | Reserved                    | No                 | No     |

| 1010        | Configuration Read          | Yes                | No     |

| 1011        | Configuration Write         | Yes                | No     |

| 1100        | Memory Read Multiple        | No                 | No     |

| 1101        | Dual Address Cycle          | No                 | No     |

| 1110        | Memory Read Line            | No                 | No     |

| 1111        | Memory Write and Invalidate | No                 | No     |

#### Table 2-6 Video Chip Supported PCI Commands

#### 2.7.3.1 Video Modes

TheCL-GD54M40 provides all standard IBM VGA modes. With 512KB of video memory, the standard B440FX DP Server goes beyond standard VGA support. The following tables show all supported video modes using 512KB and 1MB of video memory. An additional 512KB is user-installable. The tables also show the standard and extended modes that the chip supports, including the number of colors, palette size (e.g., 16 colors out of 256K colors), resolution, pixel frequency, and scan frequencies.

| Mode(s)<br>in Hex | Bits<br>Per<br>Pixel | Colors (number<br>/palette size) | Resolution | Pixel Freq.<br>(MHz) | Horiz.<br>Freq. (KHz) | Vert.<br>Freq. (Hz) |

|-------------------|----------------------|----------------------------------|------------|----------------------|-----------------------|---------------------|

| 0, 1              | 4                    | 16/256K                          | 360 X 400  | 14                   | 31.5                  | 70                  |

| 2, 3              | 4                    | 16/256K                          | 720 X 400  | 28                   | 31.5                  | 70                  |

| 4, 5              | 4                    | 4/256K                           | 320 X 200  | 12.5                 | 31.5                  | 70                  |

| 6                 | 4                    | 2/256K                           | 640 X 200  | 25                   | 31.5                  | 70                  |

| 7                 | 4                    | Mono                             | 720 X 400  | 28                   | 31.5                  | 70                  |

| D                 | 4                    | 16/256K                          | 320 X 200  | 12.5                 | 31.5                  | 70                  |

| E                 | 4                    | 16/256K                          | 640 X 200  | 25                   | 31.5                  | 70                  |

| F                 | 4                    | Mono                             | 640 X 350  | 25                   | 31.5                  | 70                  |

| 10                | 4                    | 16/256K                          | 640 X 350  | 25                   | 31.5                  | 70                  |

| 11                | 4                    | 2/256K                           | 640 X 480  | 25                   | 31.5                  | 60                  |

| 12                | 4                    | 16/256K                          | 640 X 480  | 25                   | 31.5                  | 60                  |

| 12+               | 4                    | 16/256K                          | 640 X 480  | 31.5                 | 37.5                  | 75                  |

| 13                | 8                    | 256/256K                         | 320 X 200  | 12.5                 | 31.5                  | 70                  |

Table 2-7 Standard VGA Modes

# $\operatorname{int}_{\mathbf{e}}$

| Mode(s)<br>in Hex | BPP | Colors                | Resolution | Pixel Freq.<br>(MHz) | Horiz.<br>Freq. (KHz) | Vert.<br>Freq.<br>(Hz) |

|-------------------|-----|-----------------------|------------|----------------------|-----------------------|------------------------|

| 14, 55            | 8   | 16/256K               | 1056 X 400 | 41.5                 | 31.5                  | 70                     |

| 54                | 8   | 16/256K               | 1056 X 350 | 41.5                 | 31.5                  | 70                     |

| 58, 6A            | 8   | 16/256K               | 800 X 600  | 40                   | 37.8                  | 60                     |

| 58, 6A            | 8   | 16/256K               | 800 X 600  | 49.5                 | 46.9                  | 75                     |

| 5C                | 8   | 256/256K              | 800 X 600  | 36                   | 35.2                  | 56                     |

| 5C                | 8   | 256/256K              | 800 X 600  | 40                   | 37.9                  | 60                     |

| 5C                | 8   | 256/256K              | 800 X 600  | 49.5                 | 46.9                  | 75                     |

| 5D                | 8   | 16/256K (interlaced)  | 1024 X 768 | 44.9                 | 35.5                  | 87                     |

| 5D                | 8   | 16/256K               | 1024 X 768 | 65                   | 48.3                  | 60                     |

| 5D                | 8   | 16/256K               | 1024 X 768 | 75                   | 56                    | 70                     |

| 5D                | 8   | 16/256K               | 1024 X 768 | 78.7                 | 60                    | 75                     |

| 5F                | 8   | 256/256K              | 640 X 480  | 25                   | 31.5                  | 60                     |

| 5F                | 8   | 256/256K              | 640 X 480  | 31.5                 | 37.5                  | 75                     |

| 60*               | 8   | 256/256K (interlaced) | 1024 X 768 | 44.9                 | 35.5                  | 87                     |

| 60*               | 8   | 256/256K              | 1024 X 768 | 65                   | 48.3                  | 60                     |

| 60*               | 8   | 256/256K              | 1024 X 768 | 75                   | 56                    | 70                     |

| 60*               | 8   | 256/256K              | 1024 X 768 | 78.7                 | 60                    | 75                     |

| 64*               | 16  | 64K                   | 640 X 480  | 25                   | 31.5                  | 60                     |

| 64*               | 16  | 64K                   | 640 X 480  | 31.5                 | 37.5                  | 75                     |

| 65*               | 16  | 64K                   | 800 X 600  | 36                   | 35.2                  | 56                     |

| 65*               | 16  | 64K                   | 800 X 600  | 40                   | 37.8                  | 60                     |

| 65*               | 16  | 64K                   | 800 X 600  | 49.5                 | 46.9                  | 75                     |

| 66*               | 16  | 32K Direct/256 Mixed  | 640 X 480  | 25                   | 31.5                  | 60                     |

| 66*               | 16  | 32K Direct/256 Mixed  | 640 X 480  | 31.5                 | 37.5                  | 75                     |

## Table 2-8 Extended VGA Modes

# $\operatorname{int}_{\mathbf{e}}$

| 67* | 16 | 32K Direct/256 Mixed | 800 X 600   | 40   | 37.8 | 60 |

|-----|----|----------------------|-------------|------|------|----|

| 67* | 16 | 32K Direct/256 Mixed | 800 X 600   | 49.5 | 46.9 | 75 |

| 6C* | 16 | 16/256K (interlaced) | 1280 X 1024 | 75   | 48   | 87 |

\* Requires 1MB video memory option.

# 2.7.4 Network Interface Controller (NIC)

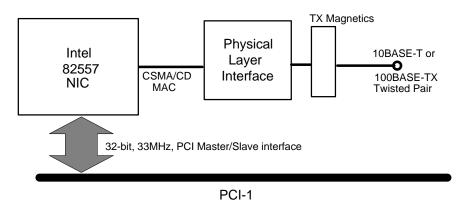

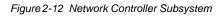

The baseboard supports a 10Base-T/100Base-TX network subsystem based on the Intel 82557<sup>™</sup> Fast Ethernet PCI bus controller. The National DP838040<sup>+</sup> and DP83223<sup>+</sup> devices, along with other discrete components, provide the physical layer interface. The following diagram illustrates the architecture of the network controller subsystem:

The 82557 is a highly integrated PCI LAN controller in a 160-pin QFP package for 10 or 100Mbps fast ethernet networks. As a PCI bus master, the 82557 can burst data at up to 132MB/s. This high-performance bus master interface can eliminate the intermediate copy step in receive and transmit frame copies, resulting in faster frame processing. The network operating system communicates with the 82557 using a memory-mapped I/O interface, PCI\_INTC\_L, and two large receive and transmit FIFOs. These prevent data overruns or underruns while waiting for access to the PCI bus, and enable back-to-back frame transmission within the minimum 960ns inter-frame spacing. The following figure shows the PCI signals supported by the 82557.

Figure 2-13 Embedded NIC PCI Signals

## 2.7.4.1 Supported Network Features

The 82557 contains an IEEE MII compliant interface to the components necessary to implement a IEEE 802.3 100Base-TX network connection. The B440FX DP Server supports the following features of the 82557 controller:

- Glueless 32-bit PCI bus master interface (direct drive of bus), compatible with PCI Bus Specification, revision 2.1

- Chained memory structure similar to the Intel 82596<sup>™</sup>, with improved dynamic transmit chaining for enhanced performance

- Programmable transmit threshold for improved bus utilization

- Early receive interrupt for concurrent processing of receive data

- On-chip counters for network management

- Autodetect and autoswitching for 10Mbps or 100Mbps network speeds

- Support for both 10Mbps and 100Mbps networks, full or half duplex-capable, with back-to-back transmit at 100Mbps

The 82557 connects to the National DP83840 and DP83223 components which provide the physical layer for the LAN controller. In addition, a magnetic component is provided that terminates to the 100Base-TX connector interface. Also included is support to enable the National DP83840 to switch between 10Mbps and 100Mbps operation. A flash device stores the network ID.

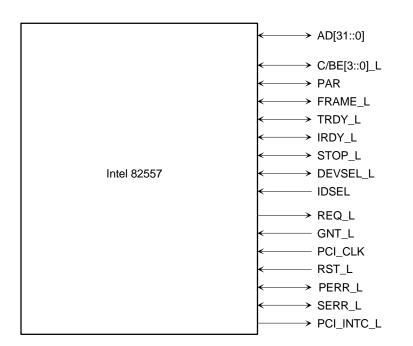

# 2.7.4.2 NIC Status LEDs

The National DP83840 drives LEDs to indicate the transmit/receive activity on the LAN, a valid link to the LAN, and 10/100Mbps operation. The location and function of each LED is shown in the following figure.

Figure 2-14 NIC Status LEDs

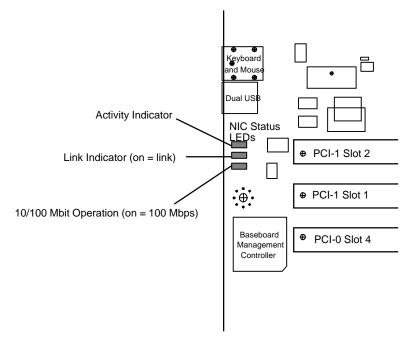

# 2.8 Server Management

The B440FX DP Server Management features are implemented using the following three microcontrollers and one ASIC:

- Baseboard Management Microcontroller (BMC)

- Front Panel Microcontroller (FPC)

- Processor Board Controller (PBC)

- Distributed Integrated Server Management Interface Chip (DISMIC)

Figure 2-15 B440FX DP Server Management Architecture

# 2.8.1 Baseboard Management Microcontroller (BMC)

The BMC is an 8051-compatible microcontroller located on the baseboard. It monitors baseboard power supply and SCSI termination voltages by using an onboard Analog to Digital Converter (ADC). It checks the status of the fan failure and the front panel NMI request and monitors system temperature sensors using the I<sup>2</sup>C-based intelligent management bus. When any monitored parameter is outside defined thresholds, the BMC generates SMI\_L. The BMC also provides general-purpose I/O (GPIO) functions, and acts as the primary communications gateway to the FPC, PBC, and DISMIC by providing support routines for I<sup>2</sup>C and ISA communications.

An EEROM associated with the secondary baseboard temperature sensor contains the Chassis ID, Baseboard ID, Power State, and Baseboard Temperature during power-off conditions. These values are managed by the BMC via  $I^2C$ .

## 2.8.2 Front Panel Microcontroller (FPC)

The FPC, located on the baseboard, manages system power on/off control, system reset, chassis intrusion monitoring, and an external I<sup>2</sup>C interface. The device is powered from the +5V standby power supply, enabling it to stay alive when system power is off. The FPC controls main power to the baseboard and processor board, and is responsible for monitoring all sources of power control both on and off the baseboard, including the Front Panel, Server Manager module, PIIX3, and RTC power control signals.

# 2.8.3 I<sup>2</sup>C Isolation Buffers

Isolation buffers, between the temperature sensors on the baseboard and the rest of the I<sup>2</sup>C bus, keep the bus alive even though the main +5V power supply is unavailable. This allows the FPC to communicate with its I <sup>2</sup>C EEROM (in the secondary baseboard temperature sensor) at all times.

### 2.8.4 Processor Board Management Microcontroller (PBC)

The PBC monitors processor voltage levels, determines DIMM configuration, monitors processor thermal trip and internal error signals, and manages two I<sup>2</sup>C thermal sensors located near each processor.

Fault Resilient Booting (FRB) is managed by the PBC, which controls the ability to boot using either processor in the event of a catastrophic processor failure. On power-up, a timer starts within the PBC that can only be stopped by a healthy processor using the GPIO bit, FRB\_TMRHLT\_L, on the 87308VUL Super I/O chip. If processor 0 fails to halt the FRB timer before time-out, the microcontroller asserts STOP\_FLUSH to the processor and asserts FRB\_RST\_L for 10ms. When the system comes out of reset, processor 0 is unable to act as the boot processor allowing the other processor to take over the boot process.

The PBC uses the I<sup>2</sup>C bus for communication with the baseboard, indicating status and error information using a semaphore protocol defined in the *Intelligent Management Bus V1.0 Communications Protocol Specification*. The PBC manages the EEROM associated with the secondary temperature sensor on the processor board which contains the Module ID, Serial Number, and other information that remains intact during power-off.

## 2.8.5 Distributed Integrated Server Management Interface Chip (DISMIC)

The three controllers communicate with each other on the intelligent management bus. Communication between this distributed controller network, the SMI handler, and the Systems Management Software (SMS) is done with the ISA host interface provided by the DISMIC. The DISMIC and BMC act as a bridge between the host server and devices on the intelligent management bus. In addition, the DISMIC provides a mailbox register interface designed to work with SMS and SMI\_L handler code across the ISA interface. The DISMIC also gates and redirects SMI\_L and NMI to generate SERR\_L, and performs other miscellaneous logic functions (e.g. logic control).

# 2.9 System Reset Control

The PIIX3 asserts reset to the host PCI bridge, which propagates reset to the I/O system. The PMC and PIIX3 provide software-controlled reset capability. The FPC, which monitors and controls system power supplies, provides a signal that indicates when power is stable to the system. The reset architecture is designed to accommodate three ways to reset the system:

- Power-up (system) reset

- Programmed (warm) reset

- Soft (keyboard) reset

### 2.9.1 Power-up Reset

Power-up reset occurs on the initial application of power to the system. The FPC manages a P6\_PWR\_GOOD signal that indicates stable power-up reset conditions to the Pentium Pro processor(s). The PBC is held in reset until the P6\_POWER\_GOOD assertion, when processor clocks are started. On power-up reset, all processors in the system perform their internal BIST. A timer begins to run in the FPC that supports a Fault Resilient Booting (FRB) mechanism allowing the system to boot if one processor fails. After successful processor initialization, the PMC is reset, and reset propagates throughout the I/O system, which allows the system to start.

### 2.9.2 Programmed Reset