# Nx586<sup>™</sup> Processor and Nx587<sup>™</sup> Floating Point Coprocessor Databook

PRELIMINARY March 4, 1994

1

1

PROPRIETARY and CONFIDENTIAL COPYING is FORBIDDEN

NexGen<sup>™</sup> Microproducts, Inc. 1623 Buckeye Drive Milpitas, CA 95035

Order # NxDOC-DB001-01-W

#### Copyright © 1993, 1994 by NexGen Microproducts, Inc.

The goal of this databook is to enable our customers to make informed purchase decisions and to design systems around our described products. Every effort is made to provide accurate information in support of these goals. However, representations made by this databook are not intended to describe the internal logic and physical design. Wherever product internals are discussed, the information should be construed as conceptual in nature. No presumptions should be made about the internal design based on this document. Information about the internal design of NexGen products is provided via nondisclosure agreement ("NDA") on a need to know basis.

The material in this document is for information only and is subject to change without notice. NexGen reserves the right to make changes in the product specification and design without reservation and without notice to its users. THIS DOCUMENT DOES NOT CONSTITUTE A WARRANTY OF ANY KIND WITH RESPECT TO THE NEXGEN INC. PRODUCTS, AND NEXGEN INC. SHALL NOT BE LIABLE FOR ANY ERRORS THAT APPEAR IN THIS DOCUMENT.

All purchases of NexGen products shall be subject to NexGen's standard terms and conditions of sale. THE WARRANTIES AND REMEDIES EXPRESSLY SET FORTH IN SUCH TERMS AND CONDITIONS SHALL BE THE SOLE WARRANTIES AND THE BUYER'S SOLE AND EXCLUSIVE REMEDIES, AND NEXGEN INC. SPECIFICALLY DISCLAIMS ANY AND ALL OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING THE IMPLIED WARRANTIES OF FITNESS FOR A PARTICULAR PURPOSE, AGAINST INFRINGEMENT AND OF MERCHANTABILITY. No person is authorized to make any other warranty or representation concerning the performance of the NexGen products. In particular, NexGen's products are not specifically designed, manufactured or intended for sale as components for the planning, design, construction, maintenance, operation or use of any nuclear facility or other ultra-hazardous activity, and neither NexGen nor its suppliers shall have any liability with respect to such use

#### Trademark Acknowledgments

NexGen, Nx586, Nx587, RISC86, NexBus, NxPCI, and NxVL are trademarks of NexGen Microproducts, Inc..

IBM, AT, and PS/2 are registered trademarks of International Business Machines, Inc. Intel is a registered trademark of Intel Corporation. i386, i387, i486 and Pentium are trademarks of Intel Corporation. Tri-state is a registered trademark of National Semiconductor Corporation. VL-Bus is a trademark of Video Electronics Standards Association.

#### Restricted Rights and Limitations

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in technical Data and Computer Software clause at 252.277-7013.

1

## Contents

| Preface                                           | v   |

|---------------------------------------------------|-----|

| Notation                                          | v   |

| Related Publications                              | vii |

|                                                   |     |

| Nx586 Features and Signals                        |     |

| Nx586 Pinouts by Signal Names                     | 4   |

| Nx586 Pinouts by Pin Numbers                      | 6   |

| Nx586 NexBus Signals                              | 10  |

| NexBus Arbitration                                | 10  |

| NexBus Cycle Control                              |     |

| NexBus Cache Control                              | 14  |

| NexBus Transceivers                               | 16  |

| NexBus Address and Data                           | 17  |

| Nx586 L2 Cache Signals                            |     |

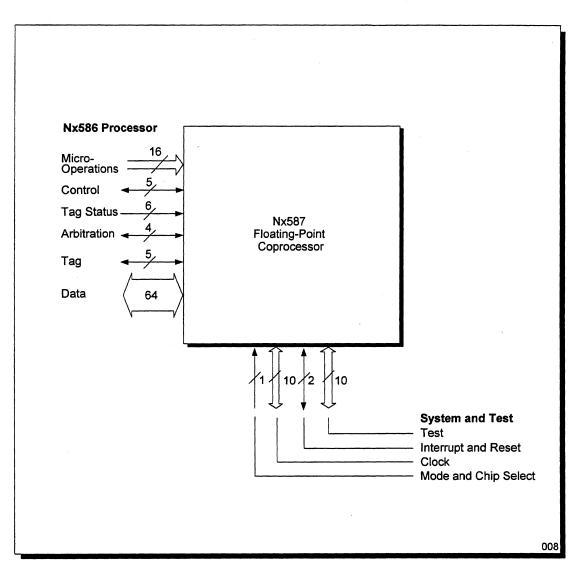

| Floating Point-Coprocessor Bus Signals (on Nx586) | 23  |

| Nx586 System Signals                              |     |

| Nx586 Clock                                       | 26  |

| Nx586 Interrupts and Reset                        | 27  |

| Nx586 Test and Reserved Signals                   | 28  |

| Nx586 Alphabetical Signal Summary                 | 29  |

| Nx587 Features and Signals                        | 33  |

| -                                                 |     |

| Nx587 Pinouts by Signal Names                     |     |

| Nx587 Pinouts by Pin Numbers                      |     |

| Floating Point Coprocessor Bus Signals (on Nx587) |     |

| Nx587 System Signals                              |     |

| Nx587 Clock                                       |     |

| Nx587 Interrupts and Reset                        |     |

| Nx587 Test and Reserved Signals                   |     |

| Nx587 Alphabetical Signal Summary                 | 43  |

PRELIMINARY

1

Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

I

1

1

| Hardware Architecture                                                                                                                                                                                                                                                                                                                                                                                                                               | 45                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Bus Structure                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                   |

| NexBus                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| L2 Cache Bus                                                                                                                                                                                                                                                                                                                                                                                                                                        | ·····                |

| Floating-Point Coprocessor Bus                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| Operating Frequencies                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| Internal Architecture                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| Storage Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| Transaction Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| Cache and Memory Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |

| Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| Cache Coherency                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| State Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| Invalid State                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |

| Shared State                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| Exclusive State                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| Modified State                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      |

| Clock Generation                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

| Bus Operations                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69                   |

| Bus Operations                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69                   |

| Accesses on the Level-2 Cache Bus                                                                                                                                                                                                                                                                                                                                                                                                                   | 69<br>70             |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase                                                                                                                                                                                                                                                                                                                                                                           | 69<br>70<br>71       |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations                                                                                                                                                                                                                                                                                                                                         | 69<br>70<br>71<br>76 |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations                                                                                                                                                                                                                                                                                                         |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations                                                                                                                                                                                                                     |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence                                                                                                                                                                                                                                                     |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase                                                                                                                                                                                                                                                                                                                                                                           |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations<br>Obtaining Exclusive Use Of Cache Blocks<br>Intervenor Operations<br>Modified Cache-Block Hit During Single-Qword Operations .                                                                  |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase                                                                                                                                                                                                                                                                                                                                                                           |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations<br>Obtaining Exclusive Use Of Cache Blocks<br>Intervenor Operations<br>Modified Cache-Block Hit During Single-Qword Operations .<br>Modified Cache-Block Hit During Four-Qword (Block) Operations |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations<br>Obtaining Exclusive Use Of Cache Blocks<br>Intervenor Operations<br>Modified Cache-Block Hit During Single-Qword Operations .                                                                  |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations<br>Obtaining Exclusive Use Of Cache Blocks<br>Intervenor Operations<br>Modified Cache-Block Hit During Single-Qword Operations .<br>Modified Cache-Block Hit During Four-Qword (Block) Operations |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations<br>Obtaining Exclusive Use Of Cache Blocks<br>Intervenor Operations<br>Modified Cache-Block Hit During Single-Qword Operations.<br>Modified Cache-Block Hit During Four-Qword (Block) Opera<br>Electrical Data      |                      |

| Accesses on the Level-2 Cache Bus<br>NexBus Arbitration and Address Phase<br>Single-Qword Memory Operations<br>Cache Line Memory Operations<br>I/O Operations<br>Interrupt-Acknowledge Sequence<br>Halt and Shutdown Operations<br>Obtaining Exclusive Use Of Cache Blocks<br>Intervenor Operations<br>Modified Cache-Block Hit During Single-Qword Operations .<br>Modified Cache-Block Hit During Four-Qword (Block) Opera                        |                      |

#### Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

PRELIMINARY

NexGen, Nx586, Nx587, RISC86, NexBus, NxPCI, and NxVL are trademarks of NexGen Microproducts, Inc. NOTICE: THESE MATERIALS ARE PROPRIETARY TO NEXGEN AND ARE PROVIDED PURSUANT TO A CONFIDENTIALITY AGREEMENT FOR YOUR EVALUATION <u>ONLY</u>. ANY VIOLATION IS SUBJECT TO LEGAL ACTION.

11

ł

# Figures

| Figure 1  | Nx586 Signal Organization                                | 3  |

|-----------|----------------------------------------------------------|----|

| Figure 2  | Nx586 Pin List, By Signal Name                           | 4  |

| Figure 3  | Nx586 Pin List, By Signal Name (continued)               | 5  |

| Figure 4  | Nx586 Pin List, By Pin Name (continued)                  | 6  |

| Figure 5  | Nx586 Pin List, By Pin Number (continued)                | 7  |

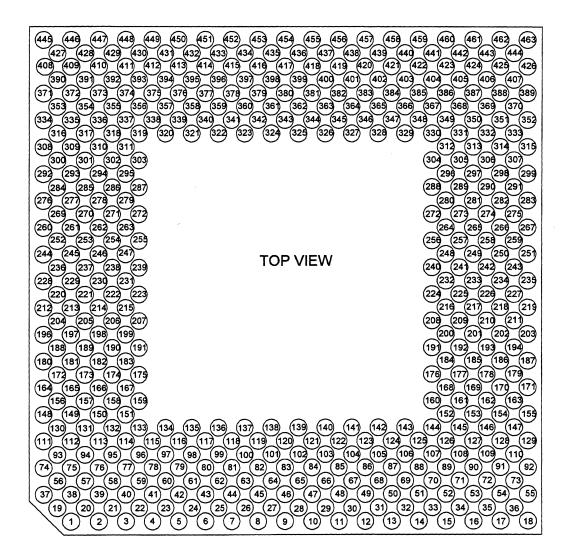

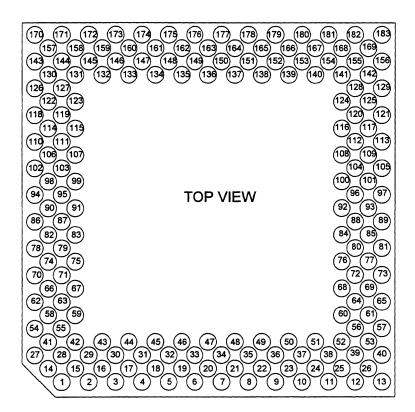

| Figure 6  | Nx586 Pinout Diagram (Top View)                          | 8  |

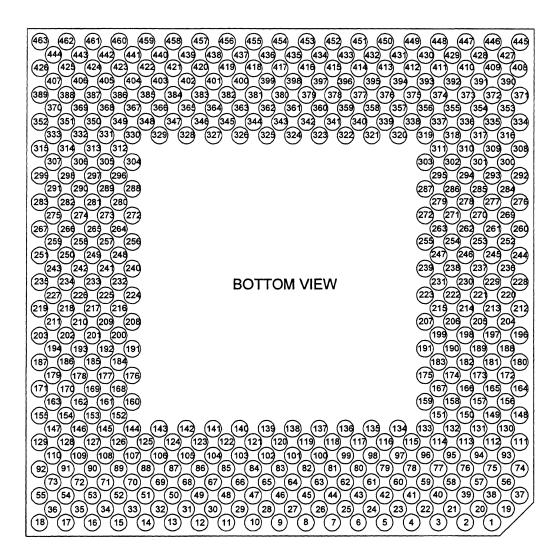

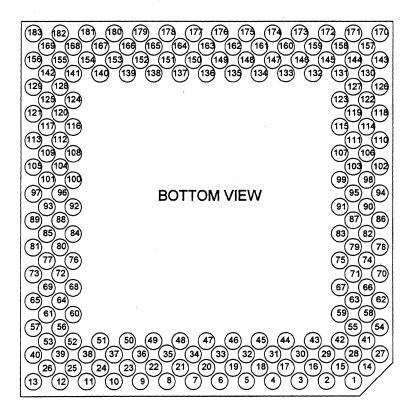

| Figure 7  | Nx586 Pinout Diagram (Bottom View)                       | 9  |

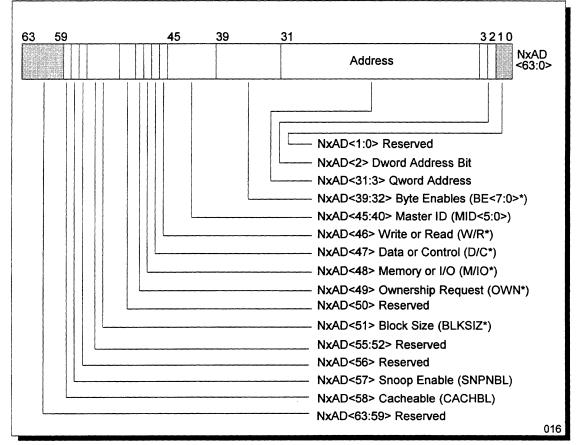

| Figure 8  | NexBus Address and Status Phase                          | 17 |

| Figure 9  | Byte-Enable Usage during I/O Transfers                   | 19 |

| Figure 10 | Byte-Enable Usage during Memory Transfers                | 19 |

| Figure 11 | Bus-Cycle Types                                          |    |

| Figure 12 | Nx587 Signal Organization                                | 34 |

| Figure 13 | Nx587 Pin List, By Signal Name                           | 35 |

| Figure 14 | Nx587 Pin List, By Pin Number                            |    |

| Figure 15 | Nx587 Pinout Diagram (Top View)                          | 37 |

| Figure 16 | Nx587 Pinout Diagram (Bottom View)                       | 38 |

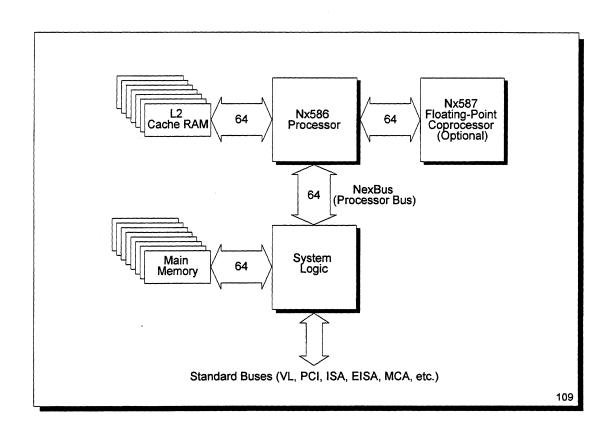

| Figure 17 | Single-Processor System Diagram                          | 46 |

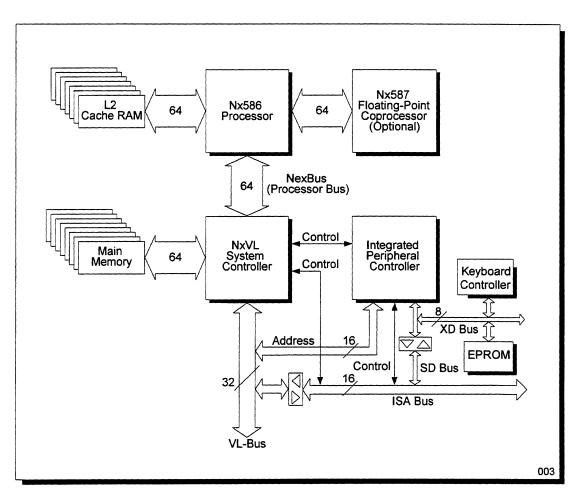

| Figure 18 | NxVL-Based Single-Processor System Diagram               | 47 |

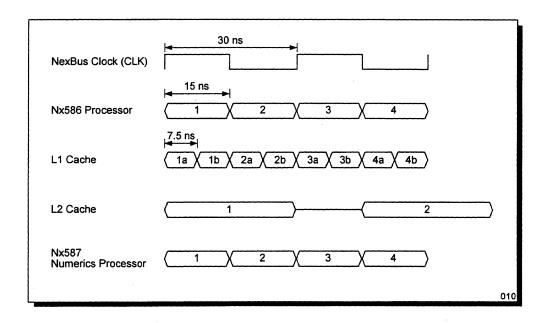

| Figure 19 | Operating Frequencies (66MHz Processor)                  | 50 |

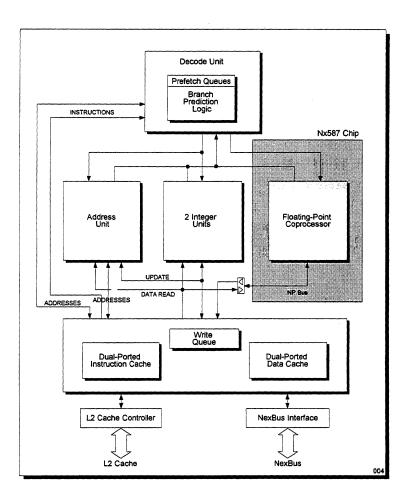

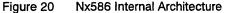

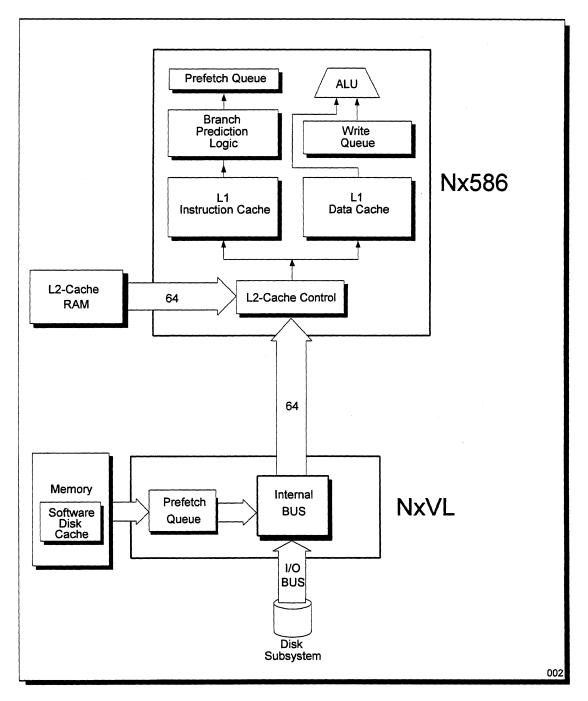

| Figure 20 | Nx586 Internal Architecture                              | 52 |

| Figure 21 | Storage Hierarchy (Reads)                                |    |

| Figure 22 | Storage Hierarchy (Writes)                               | 55 |

| Figure 23 | Cache Characteristics                                    | 57 |

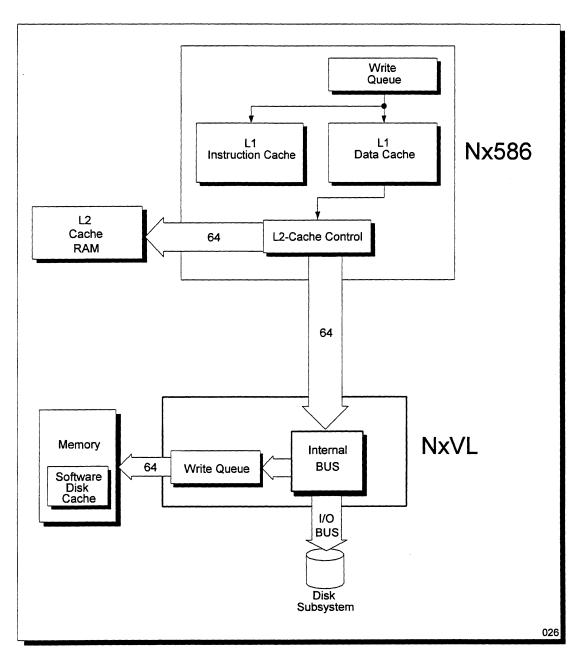

| Figure 24 | Basic Cache-State Transitions                            | 61 |

| Figure 25 | Cache State Controls                                     |    |

| Figure 26 | Bus Snooping                                             | 63 |

| Figure 27 | Clocking Modes                                           |    |

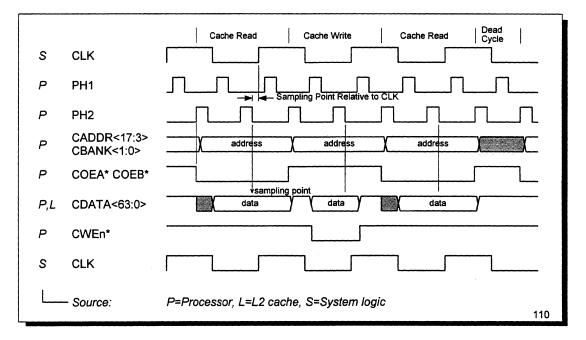

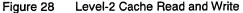

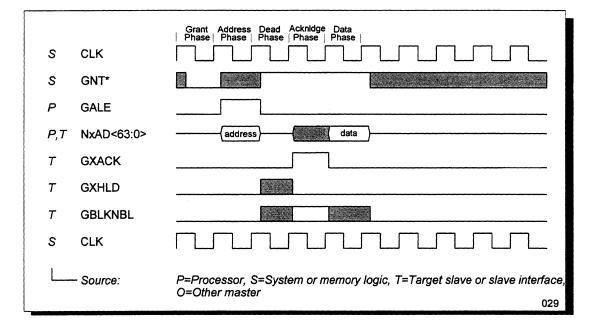

| Figure 28 | Level-2 Cache Read and Write                             |    |

| Figure 29 | Fastest Single-Qword Read                                |    |

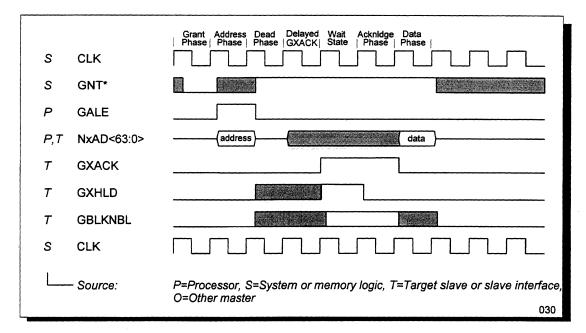

| Figure 30 | Fast Single-Qword Read with a delayed GXACK              | 73 |

| Figure 31 | Single-Qword Read With Wait States using a delayed GXACK | 74 |

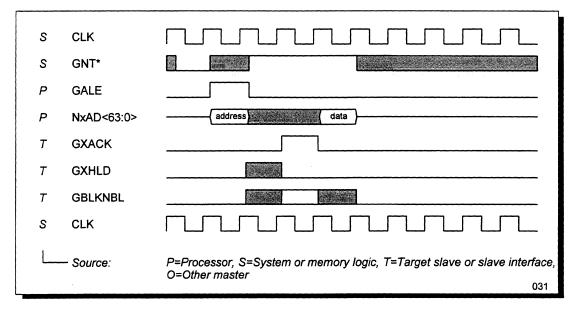

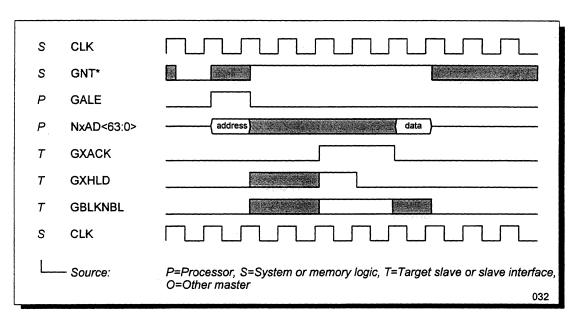

| Figure 32 | Single-Qword Read With Wait States using GXHLD only      |    |

| Figure 33 | Fastest Single-Qword Write                               | 75 |

#### PRELIMINARY

Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

111

1

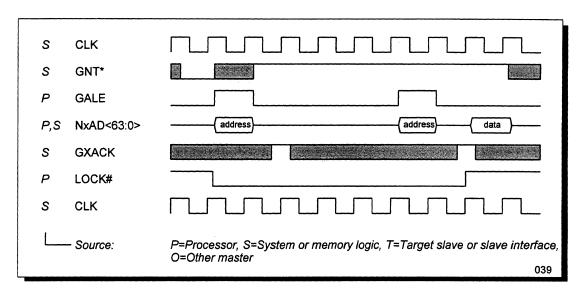

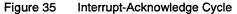

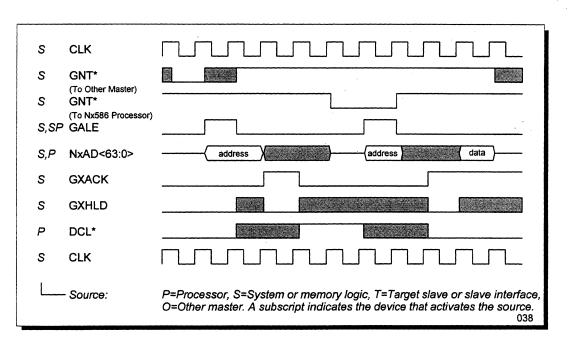

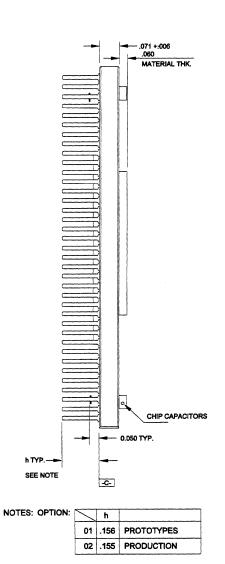

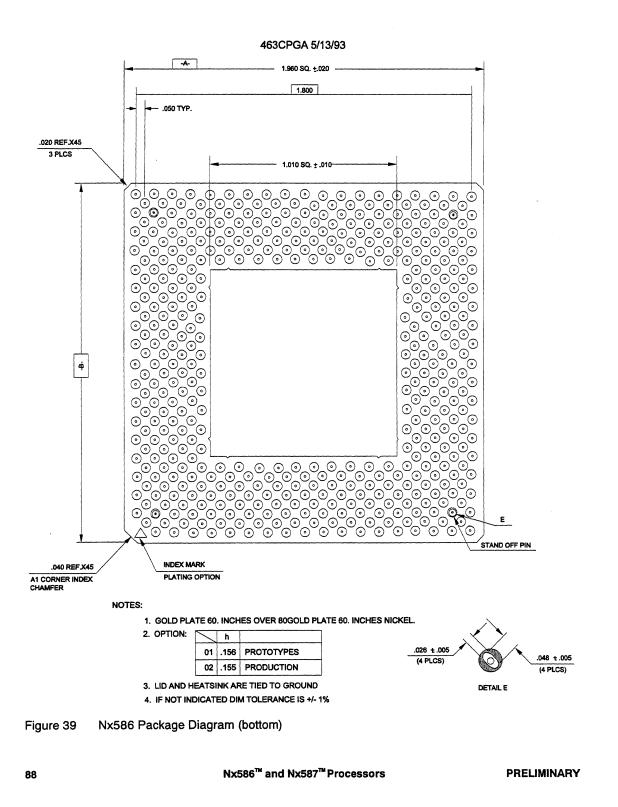

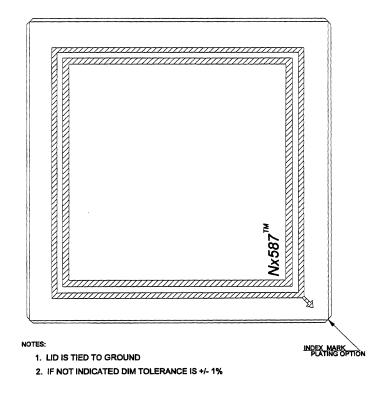

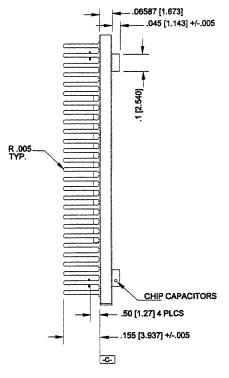

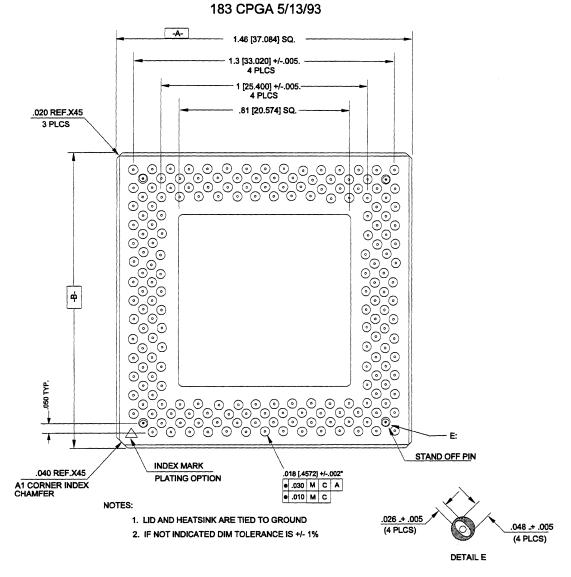

Figure 34 Figure 35 Figure 36 Figure 37 Single-Qword Read Hits Modified Cache Block ...... 82 Figure 38 Figure 39 Figure 39 Figure 40 Figure 41 Figure 42

#### iv

1

Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

PRELIMINARY

NexGen, Nx586, Nx587, RISC86, NexBus, NxPCI, and NxVL are trademarks of NexGen Microproducts, Inc. NOTICE: THESE MATERIALS ARE PROPRIETARY TO NEXGEN AND ARE PROVIDED PURSUANT TO A CONFIDENTIALITY AGREEMENT FOR YOUR EVALUATION <u>ONLY</u>. ANY VIOLATION IS SUBJECT TO LEGAL ACTION.

PRELIMINARY

١

1

Preface

1

## Preface

This databook covers two products: the Nx586<sup>TM</sup> processor (called *the* processor), and the Nx587<sup>TM</sup> floating-point coprocessor. The databook is written for system designers considering the use of these devices in their designs. We assume an experienced audience, familiar not only with system design conventions but also with the x86 architecture. The *Glossary* at the end of the book defines NexGen's terminology, and the *Index* gives quick access to the subject matter.

NexGen's Applications Engineering Department welcomes your questions and will be glad to provide assistance. In particular, they can recommend system parts that have been tested and proven to work with NexGen<sup>™</sup> products.

### Notation

The following notation and conventions are used in this book:

Devices and Bus Names

- Processor or CPU—The Nx586 processor described in this book.

- Floating Point Coprocessor—The Nx587 floating-point coprocessor described in this book.

- NxVL<sup>TM</sup> Systems Logic—The NxVL system controller described in the *NxVL System Controller Databook*.

- NexBus<sup>™</sup> System Bus—The Nx586 processor bus, including its multiplexed address/status and data bus (NxAD<63:0>) and related control signals.

Signals and Timing Diagrams

Active-Low Signals—Signal names that are followed by an asterisk, such as ALE\*, indicate active-low signals. They are said to be "asserted" or "active" in their low-voltage state and "negated" or "inactive" in their highvoltage state.

#### Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

v

- Bus Signals—In signal names, the notation <n:m> represents bits n through m of a bus.

- Reserved Bits and Signals—Signals or bus bits marked "reserved" must be driven inactive or left unconnected, as indicated in the signal descriptions. These bits and signals are reserved by NexGen for future implementations. When software reads registers with reserved bits, the reserved bits must be masked. When software writes such registers, it must first read the register and change only the non-reserved bits before writing back to the register.

- Source—In timing diagrams, the left-hand column indicates the "Source" of each signal. This is the chip or logic that outputs the signal. When signals are driven by multiple sources, all sources are shown, in the order in which they drive the signal. In some cases, signals take on different names as outputs are logically ORed in group-signal logic. In these cases, the signal source is shown with a subscript, where the subscript indicates the device or logic that originally caused the change in the signal.

- Tri-state®—In timing diagrams, signal ranges that are high impedance are shown as a straight horizontal line half-way between the high and low level.

- Invalid and Don't Care—In timing diagrams, signal ranges that are invalid or don't care are filled with a screen pattern.

Data

- Quantities—A word is two bytes (16 bits), a dword or doubleword is four bytes (32 bits), and a qword or quadword is eight bytes (64 bits).

- Addressing—Memory is addressed as a series of bytes on eight-byte (64bit) boundaries, in which each byte can be separately enabled.

- Abbreviations—The following notation is used for bits and bytes:

| Bits  | b | as in "64b/qword" |

|-------|---|-------------------|

| Bytes | В | as in "32B/block" |

| kilo  | k | as in "4kB/page"  |

Mega M as in "1Mb/sec"

Giga G as in "4GB of memory space"

- Little Endian Convention—The byte with the address xx...xx00 is in the least-significant byte position (little end). In byte diagrams, bit positions are numbered from right to left: the little end is on the right and the big end is on the left. Data structure diagrams in memory show small addresses at the bottom and high addresses at the top. When data items are "aligned," bit notation on a 64-bit data bus maps directly to bit notation in 64-bit-wide memory. Because byte addresses increase from right to left, strings appear in reverse order when illustrated according to the little-endian convention.

- Bit Ranges—In a range of bits, the highest and lowest bit numbers are separated by a colon, as in <63:0>.

#### Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

PRELIMINARY

NexGen, Nx586, Nx587, RISC86, NexBus, NxPCI, and NxVL are trademarks of NexGen Microproducts, Inc. NOTICE: THESE MATERIALS ARE PROPRIETARY TO NEXGEN AND ARE PROVIDED PURSUANT TO A CONFIDENTIALITY AGREEMENT FOR YOUR EVALUATION <u>ONLY</u>. ANY VIOLATION IS SUBJECT TO LEGAL ACTION.

vi

1

- Bit Values—Bits can either be set to 1 or cleared to 0.

- Hexadecimal and Binary Numbers—Unless the context makes interpretation clear, hexadecimal numbers are followed by an h, binary numbers are followed by a b, and decimal numbers are followed by a d.

### **Related Publications**

The following books treat various aspects of computer architecture, hardware design, and programming that may be useful for your understanding of NexGen products:

NexGen Products

NxVL System Controller Databook, NexGen, Milpitas, CA, Tel: (408) 435-0202.

x86 Architecture

- John Crawford and Patrick Gelsinger, *Programming the 80386*, Sybex, San Francisco, 1987.

- Rakesh Agarwal, 80x86 Architecture & Programming, Volumes I and II, Prentice-Hall, Englewood Cliffs, NJ, 1991.

General References

John L. Hennessy and David A. Patterson, Computer Architecture, Morgan Kaufmann Publishers, San Mateo, CA, 1990.

#### PRELIMINARY

1

#### Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

vii

ł

1

## **Nx586 Features and Signals**

The NexGen Nx586 processor is an advanced 5th generation 32-bit Superscalar x86 compatible processor that provides market leading performance. The Nx586 along with the Nx587 floating-point coprocessor are the core building blocks of a new class of personal computers. The following are some of the key features of the Nx586 Processor:

- Full x86 Binary Compatibility—Supports 8, 16 and 32-bit data types and operates in real, virtual 8086 and protected modes.

- **Patented RISC86<sup>TM</sup> Superscalar Microarchitecture**—Multiple operations are executed simultaneously during each cycle.

- Multi-Level Storage Hierarchy—Branch prediction, readable write queue, on-chip L1 code and data caches and unified L2 cache.

- Separate on-chip L1 Code and Data Caches—supports on-chip 4-way, 16kByte Code and 16kByte Data caches using MESI Cache Consistency Protocol.

- On-Chip L2 Cache Controller— supporting 4-way, unified, MESI modified write-back cache coherency protocol on 256kB or 1MB of external cache using standard asynchronous SRAMs.

- Patented Branch Prediction Logic—Reduces both control dependencies and branch cycle counts.

- Dual-Port Caches—64-bit reads and writes are serviced in parallel in a single clock cycle.

- Caches Decoupled From Processor Bus—Both the L1 and L2 caches are accessed on separate dedicated buses.

- Two-Phase, Non-Overlapped Clocking—Integrated phase-locked loop bus-clock doubler. Processor operates at twice the system bus frequency.

- Three 64-Bit Synchronous Buses—NexBus (the processor bus), L2 SRAM bus, and Nx587 Floating-Point Coprocessor bus and is fully integrat3d into the processor microarchitecture.

- Optional in Line Floating-Point Coprocessor— Nx587 operates in parallel with the Nx586 pipeline.

- Advanced State-of-the-Art Fabrication Process—0.5 micron CMOS

#### PRELIMINARY

1

#### Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

1

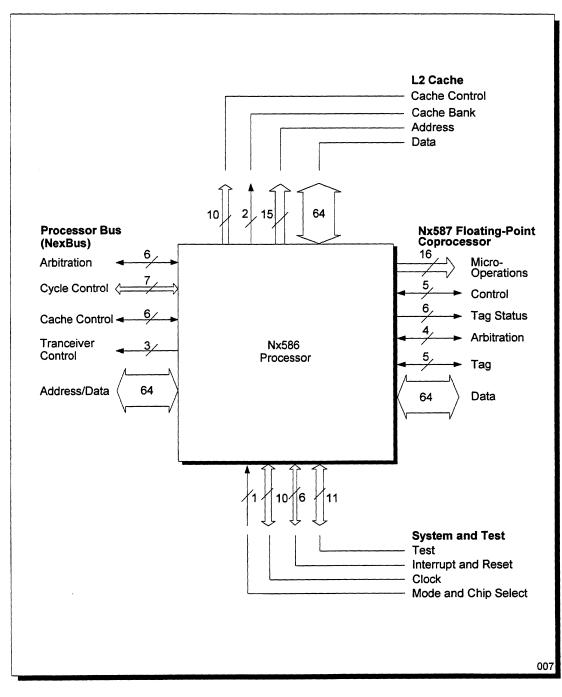

Figure 1 shows the signal organization for the Nx586 processor. The processor supports signals for the NexBus (the processor bus), L2 cache, and the optional Nx587 Floating-Point Coprocessor. Many types of devices can be interfaced to the NexBus, including a backplane, multiple Nx586 processors, shared memory subsystems, high-speed I/O, and industry-standard buses. All signals are synchronous to the NexBus clock (CLK) and transition at the rising edge of the clock with the exception of four asynchronous signals: INTR\*, NMI\*, GATEA20, and SLOTID<3:0>. All bi-directional NexBus signals are floated unless they are needed during specific time periods, as specified in the *Bus Operation* chapter. The normal state for all reserved bits is high.

Two types of NexBus signals deserve special mention:

- Group Signals—There are several group signals on the NexBus, typically denoted by signal names beginning with the letter "G." Active-low signals such as ALE\* are driven by each NexBus device, and the arbiter derives an active-high group signal (such as GALE) and distributes it back to each device. When the NxVL is used, these group signals are generated within the NxVL.

- Central Bus Arbitration—Access to the NexBus is arbitrated by an external NexBus Arbiter. NexBus masters request and are granted access by this Arbiter. For the Nx586 processor, central bus arbitration has the advantage of back-to-back processor access most of the time while supporting fast switching between masters. The NxVL provides the combined functions of NexBus Arbiter, Alternate-Bus Interface (the system-logic interface to other system buses), and memory controller. The NxVL gives the processor backto-back use of the bus when no device on any other system bus needs access.

Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

PRELIMINARY

1

Nx586 Features and Signals

1

Figure 1 Nx586 Signal Organization

PRELIMINARY

1

Nx586<sup>™</sup> and Nx587<sup>™</sup> Processors

3

## **Nx586 Pinouts by Signal Names**

| Dia        | Time        | Circal                 | 0          | Turne      | <u>Oirres</u> (        |            | <b>T</b>   | Olere et                 |                   | 1 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u> </u>                   |

|------------|-------------|------------------------|------------|------------|------------------------|------------|------------|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Pin        | Туре        | Signal                 | Pin        | Туре       | Signal                 | Pin        | Туре       | Signal                   | Pin               | 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Signal                     |

| 449        | 0           | ALE*                   | 125        | 1/0        | CDATA<37>              | 17         |            | NC                       | 279               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<49>                 |

| 18         |             | ANALYZEIN              | 176        | 1/0        | CDATA<38>              | 187        | -          | NC                       | 238               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<50>                 |

| 168        | 0           | ANALYZEOUT<br>AREQ*    | 184<br>203 | 1/0<br>1/0 | CDATA<39>              | 208        | -          | NC                       | 271               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<51>                 |

| 340<br>141 | 0           | CADDR<3>               | 193        | 1/0        | CDATA<40><br>CDATA<41> | 235        | -          | NC<br>NC                 | 270               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<52>                 |

| 123        | ŏ           | CADDR<3>               | 195        | 1/0        | CDATA<41>              | 288<br>256 |            | NC                       | <u>316</u><br>371 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<53><br>NPDATA<54>   |

| 123        | ŏ           | CADDR<5>               | 185        | 1/0        | CDATA<42>              | 143        | -          | NC                       | 284               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<55>                 |

| 32         | ŏ           | CADDR<6>               | 155        | 1/0        | CDATA<43>              | 380        |            | NC                       | 188               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<56>                 |

| 14         | ŏ           | CADDR<7>               | 163        | 1/0        | CDATA<45>              | 436        | 1          | NMI*                     | 222               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<57>                 |

| 33         | ŏ           | CADDR<8>               | 171        | 1/0        | CDATA<46>              | 244        | 1/0        | NPDATA<0>                | 311               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<58>                 |

| 15         | ŏ           | CADDR<9>               | 179        | 1/0        | CDATA<47>              | 254        | 1/0        | NPDATA<1>                | 334               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<59>                 |

| 34         | ō           | CADDR<10>              | 217        | 1/0        | CDATA<48>              | 292        | 1/0        | NPDATA<2>                | 239               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<60>                 |

| 90         | Ō           | CADDR<11>              | 227        | 1/0        | CDATA<49>              | 408        | 1/0        | NPDATA<3>                | 252               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<61>                 |

| 107        | Ō           | CADDR<12>              | 225        | 1/0        | CDATA<50>              | 336        | 1/O        | NPDATA<4>                | 204               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPDATA<62>                 |

| 88         | 0           | CADDR<13>              | 224        | 1/0        | CDATA<51>              | 294        | 1/0        | NPDATA<5>                | 353               | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NPDATA<63>                 |

| 106        | 0           | CADDR<14>              | 201        | I/O        | CDATA<52>              | 286        | 1/0        | NPDATA<6>                | 446               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPIRQ*                     |

| 142        | 0           | CADDR<15>              | 211        | I/O        | CDATA<53>              | 223        | 1/0        | NPDATA<7>                | 337               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPNOERR                    |

| 169        | 0           | CADDR<16>              | 209        | 1/0        | CDATA<54>              | 206        | 1/0        | NPDATA<8>                | 172               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPOUTFTYP<0>               |

| 35         | 0           | CADDR<17>              | 219        | 1/0        | CDATA<55>              | 427        | 1/0        | NPDATA<9>                | 98                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPOUTFTYP<1>               |

| 89         | 0           | CBANK<0>               | 240        | 1/0        | CDATA<56>              | 255        | 1/0        | NPDATA<10>               | 79                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPBUS<0>                |

| 16         | 0           | CBANK<1>               | 251        | 1/0        | CDATA<57>              | 230        | 1/0        | NPDATA<11>               | 116               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPPOPBUS<1>                |

| 100        | 1/0         | CDATA<0>               | 249        | 1/0        | CDATA<58>              | 236        | 1/0        | NPDATA<12>               | 3                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPBUS<2>                |

| 7          | 1/0         | CDATA<1>               | 248        | 1/0        | CDATA<59>              | 183        | 1/0        | NPDATA<13>               | 93                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPBUS<3>                |

| 81         | 1/0         | CDATA<2>               | 232        | 1/0        | CDATA<60>              | 212        | 1/0        | NPDATA<14>               | 164               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPPOPBUS<4>                |

| 136        | 1/0         | CDATA<3>               | 241        | 1/0        | CDATA<61>              | 191        | 1/0        | NPDATA<15>               | 135               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPPOPBUS<5>                |

| 24         | 1/0         | CDATA<4>               | 243        | 1/0        | CDATA<62>              | 390        | 1/0        | NPDATA<16>               | 134               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPPOPBUS<6>                |

| 80         | 1/0         | CDATA<5>               | 233        | 1/0        | CDATA<63>              | 215        | 1/0<br>1/0 | NPDATA<17>               | 21                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPBUS<7>                |

| 6<br>99    | 1/O<br>1/O  | CDATA<6><br>CDATA<7>   | 361<br>452 |            | CKMODE<br>CLK          | 199<br>318 | 1/0        | NPDATA<18><br>NPDATA<19> | 2<br>97           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NPPOPBUS<8><br>NPPOPBUS<9> |

| 99         | 1/0         | CDATA<7>               | 192        | -          | COEA*                  | 262        | 1/0        | NPDATA<19>               | 148               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPPOPBUS<10>               |

| 83         | 1/0         | CDATA<9>               | 138        | -ŏ-        | COEB*                  | 228        | 1/0        | NPDATA<21>               | 74                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NPPOPBUS<11>               |

| 27         | 1/0         | CDATA<10>              | 117        | ŏ          | CWE<0>*                | 295        | 1/0        | NPDATA<22>               | 22                | 1 ŏ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NPPOPBUS<12>               |

| 119        | 1/0         | CDATA<11>              | 137        | ŏ          | CWE<1>*                | 260        | Ϊ/Ο        | NPDATA<23>               | 156               | and the second se | NPPOPBUS<13>               |

| 118        | 1/0         | CDATA<12>              | 120        | ŏ          | CWE<2>*                | 445        | 1/0        | NPDATA<24>               | 23                | Ō                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPBUS<14>               |

| 26         | 1/0         | CDATA<13>              | 140        | ō          | CWE<3>*                | 95         | 1/0        | NPDATA<25>               | 96                | Ō                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPBUS<15>               |

| 82         | 1/0         | CDATA<14>              | 55         | Ō          | CWE<4>*                | 428        | 1/0        | NPDATA<26>               | 37                | Ō                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPTAG<0>                |

| 8          | 1/0         | CDATA<15>              | 177        | 0          | CWE<5>*                | 220        | 1/0        | NPDATA<27>               | 159               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPTAG<1>                |

| 11         | 1/0         | CDATA<16>              | 200        | 0          | CWE<6>*                | 303        | 1/0        | NPDATA<28>               | 56                | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPTAG<2>                |

| 103        | I/O         | CDATA<17>              | 216        | 0          | CWE<7>*                | 310        | 1/0        | NPDATA<29>               | 132               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPPOPTAG<3>                |

| 29         | 1/0         | CDATA<18>              | 359        | 0          | DCL*                   | 268        | I/O        | NPDATA<30>               | 151               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NPPOPTAG<4>                |

| 121        | 1/0         | CDATA<19>              | 330        | 1          | GALE                   | 263        | 1/0        | NPDATA<31>               | 182               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPRREQ                     |

| 139        | 1/0         | CDATA<20>              | 339        |            | GATEA20                | 356        | 1/0        | NPDATA<32>               | 174               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPRVAL                     |

| 28         | 1/0         | CDATA<21>              | 378        | 1          | GBLKNBL                | 196        | 1/0        | NPDATA<33>               | 167               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPSPARE<0>                 |

| 102        | 1/0         | CDATA<22>              | 429        |            | GDCL                   | 302        | 1/0        | NPDATA<34>               | 150               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPSPARE<1>                 |

| 10         | 1/0         | CDATA<23>              | 368        |            | GNT*                   | 300        | 1/0        | NPDATA<35>               | 158               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NPSPARE<2>                 |

| 13         | 1/0         | CDATA<24>              | 113        |            | GREF                   | 287        | 1/0        | NPDATA<36>               | 5                 | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NPTAG<0>                   |

| 105        | 1/0         | CDATA<25>              | 430        | 1          | GSHARE                 | 180        | 1/0        | NPDATA<37>               | 77                | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NPTAG<1>                   |