# **AMD-K6® Processor**

## EMI DESIGN CONSIDERATIONS

**Application Note**

Publication # 22023 Rev: C Amendment/0 Issue Date: April 2000

#### © 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, K6, and combinations thereof, are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## Contents

| Revision Historyix                                                                   |

|--------------------------------------------------------------------------------------|

| Introduction                                                                         |

| Electromagnetic Interference (EMI) 2                                                 |

| Three Basic Elements of EMI2Radiation Transfer2Antennas3                             |

| Emission Strength                                                                    |

| Locating the Source of EMI Using Harmonics7                                          |

| Controlling EMI8                                                                     |

| At the Emitting Source8Shielding the Chassis9Correct Cabling9Filtering I/O Signals10 |

| Components that Influence EMI                                                        |

| Processor                                                                            |

| Chipset and Clock Chip EMI13<br>Spread-Spectrum Clock Generation                     |

| Memory                                                                               |

| AC Power Supply                                                                      |

| Chassis Design                                                                       |

| Components, Cables, and Connectors                                                   |

| Peripherals                                                                          |

| Power Requirements 23                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ground Plane23<br>Other Ground-Related Rules                                                                                                                           |

| Decoupling and Layout Recommendations25"Coffee Cup" Rule25General High-Frequency Decoupling25Controlling Switching-Regulator-Induced EMI26Power Distribution26         |

| Decoupling Capacitance and Placement28Via Inductance.29High-Frequency Decoupling Calculations30Calculating Required Number of Capacitors31Decoupling: Rules of Thumb34 |

| PC Board Layout Guidelines 35                                                                                                                                          |

| Component Placement35                                                                                                                                                  |

| Layout/Routing Rules36                                                                                                                                                 |

| Return Current Paths                                                                                                                                                   |

| Ground Plane Permeability                                                                                                                                              |

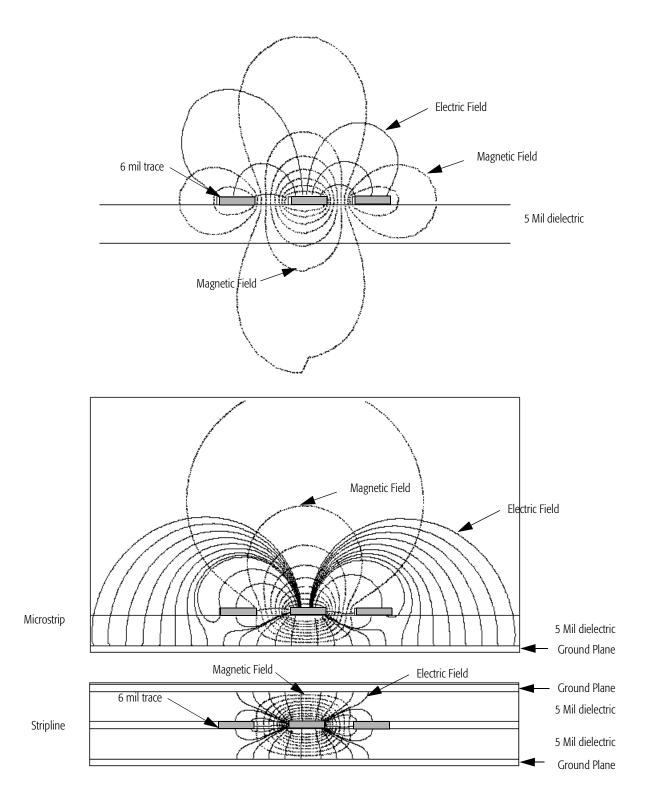

| Microstrip                                                                                                                                                             |

| Stripline                                                                                                                                                              |

| Trace Length Calculation43                                                                                                                                             |

| General Guidelines Summary46                                                                                                                                           |

| Appendix                                                                                                                                                               |

| Termination Strategies.48Kinds of Termination48General Termination Advice48                                                                                            |

| Debug Chart                                                                                                                                                            |

| Crosstalk                                                                                                                                                              |

| Simulation                                                                                                                                                             |

| Shielding Methodology51                                                                                                                                                |

| Transmission Line Effects52                                                                                                                                            |

| Emission Limits                                                                                                                                                        |

| References                                                                                                                                                             |

## **List of Figures**

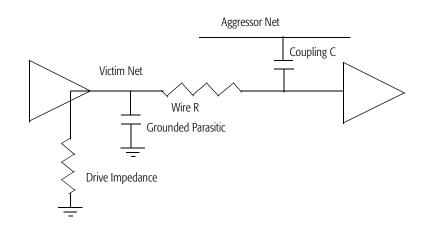

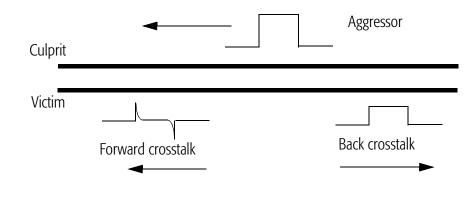

| Figure 1.  | Crosstalk Model                                          |

|------------|----------------------------------------------------------|

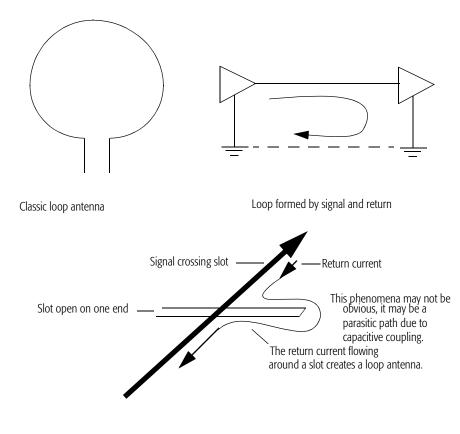

| Figure 2.  | Loop Antennas                                            |

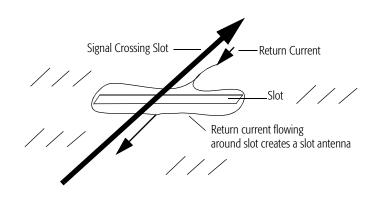

| Figure 3.  | Antenna Formed by a Trace Crossing a Slot5               |

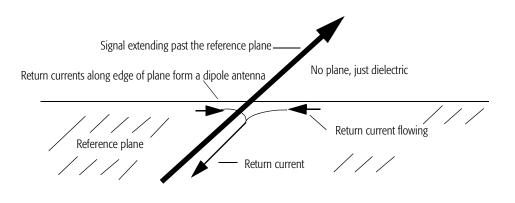

| Figure 4.  | Dipole Antenna                                           |

| Figure 5.  | Waveguide Antenna                                        |

| Figure 6.  | Filtering Techniques10                                   |

| Figure 7.  | Processor Core Power Supply EMI Filter13                 |

| Figure 8.  | Effects of Spread Spectrum Clocking15                    |

| Figure 9.  | Properly Terminating Cables                              |

| Figure 10. | Buried Capacitance24                                     |

| Figure 11. | Power Distribution Model                                 |

| Figure 12. | Suggested Component Placement                            |

| Figure 13. | Via Layout for Low Inductance                            |

| Figure 14. | Decoupling Inductance                                    |

| Figure 15. | X7R Capacitor Impedance versus Frequency31               |

| Figure 16. | Good EMI Structure                                       |

| Figure 17. | Electric Field Concentrations                            |

| Figure 18. | Return Currents                                          |

| Figure 19. | AC Return Path versus DC Return Path                     |

| Figure 20. | Microstrip versus Stripline40                            |

| Figure 21. | Board Stackup for 4-Layer and 6-Layer Boards             |

| Figure 22. | Electric (E) and Magnetic (H) Fields45                   |

| Figure 23. | Crosstalk                                                |

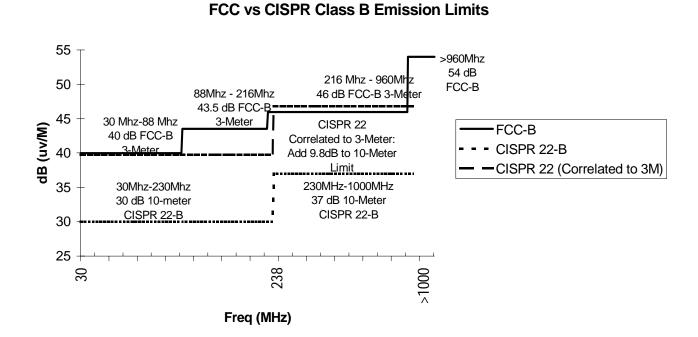

| Figure 24. | Radiated Emissions Standards: Class B, 3 and 10 Meter 52 |

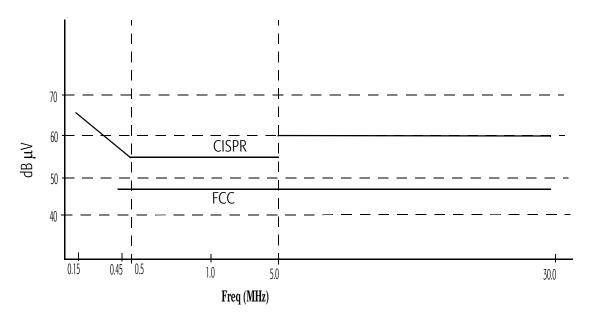

| Figure 25. | Conducted Emissions Standards: Class B53                 |

|            |                                                          |

##

AMD-K6<sup>®</sup> Processor EMI Design Considerations

22023C/0-April 2000

## **List of Tables**

| Table 1. | Bus Frequency / Multiplier / Resultant Core Frequency | 7          |

|----------|-------------------------------------------------------|------------|

| Table 2. | Conductivity and Permeability                         | 19         |

| Table 3. | Representative ESR Values                             | <u>2</u> 9 |

| Table 4. | Inductance Contributions of Components                | 29         |

| Table 5. | Estimates of Maximum Trace Length                     | 18         |

| Table 6. | Fixing Signal Problems                                | 19         |

| Table 7. | Class B Radiated Emissions Standards                  | 53         |

| Table 8. | Class B Conducted Emissions Standards                 | 53         |

##

AMD-K6<sup>®</sup> Processor EMI Design Considerations

22023C/0-April 2000

## **Revision History**

| Date     | Rev | Description                                                                    |  |  |

|----------|-----|--------------------------------------------------------------------------------|--|--|

| Mar 1999 | Α   | Initial published release.                                                     |  |  |

| Feb 2000 | В   | Misc. additional ideas added.                                                  |  |  |

| Apr 2000 | C   | Corrected Example 1 in "Calculating Required Number of Capacitors" on page 31. |  |  |

##

AMD-K6<sup>®</sup> Processor EMI Design Considerations

22023C/0-April 2000

## Application Note

**AMD-K6**<sup>®</sup>

## Processor EMI Design Considerations

## Introduction

The AMD-K6<sup>®</sup> processor family consists of high-performance x86-compatible processors containing more than 8.8 million transistors. The previous generation of AMD-K6 processors used 2.9 V and 3.2 V to power the processor's core circuitry. They were fabricated using AMD's enhanced 0.35- $\mu$ m process technology (CS34EX). The newer generation of processors uses 2.2 V, and is manufactured by the CS44E 0.25- $\mu$ m process. The I/O portion of all the processors operates at the industry-standard 3.3 V.

This application note is intended to guide the board and system designer through developing a layout that meets FCC and CISPR class B regulations. A total systems solution approach is key to achieving an EMI compliant system. Care must be given to the choice of components, PC board (layout), chassis (including power supply), and cables.

This application note focuses on PC board design issues. Other issues will be discussed in more detail in another application note.

The designer should use good high-frequency design practices in order to minimize EMI. It is important to address EMI issues early in the design stage. It is usually more difficult to fix EMI problems late in the design process.

This application note makes many suggestions to reduce EMI. Some may not be usable in the reader's situation, due to space or cost constraints. The designer must decide which techniques to apply.

## **Electromagnetic Interference (EMI)**

Every switching circuit emits electromagnetic radiation other than its intended output. This unintended output becomes electromagnetic interference (EMI) for other nearby circuits. EMI strength is related to the amplitude of the current and voltage. The larger the current or higher the voltage — the stronger, potentially, is the interference.

## **Three Basic Elements of EMI**

The first element of EMI is current from an emitting source, called a culprit. Culprits can be an unterminated line, an impedance discontinuity, an oscillator, a clock, or a switching power supply.

The second element is the transfer method, or coupling media. A coupling can be antenna-to-antenna (radiation), field-to-wire or wire-to-field (crosstalk), or common ground impedance (conduction).

The third element is a receiving element, or victim. A victim can be a radio receiver, a television set, analog sensors, amplifiers, memories, disk drives, and so on.

EMI is an electric or electromagnetic field emitted from a culprit, transferred by coupling media to a victim, where it degrades that signal.

**Radiation Transfer** Currents that generate radiated fields are of two kinds— common mode and differential mode.

**Common Mode.** Common-mode currents are high-frequency current transients generating significant Radio Frequency (RF) potentials due to inductance in the plane or wire. They are present in both the  $V_{CC}$  and ground planes, in both wires of a differential pair, or in both the shield and center wire of a coaxial cable. These currents are very difficult to measure because the ground plane may contain the common-mode signals, so they cannot be measured relative to ground. A common-mode choke is usually the most effective way to filter these unwanted currents.

**Differential Mode.** Differential mode currents are high-frequency current transients in a trace, wire, or plane. They can be measured relative to ground, for instance, between the  $V_{CC}$  plane and ground or between a signal and ground. Differential-mode current can be effectively shielded.

Antennas The second ingredient necessary for radiation is an antenna. Antennas can be cables, slots in a chassis, traces on a PC board, and so on. To understand antenna radiation, imagine running an alternating current through a simple loop of wire (see Figure 2). The magnitude of radiation from the loop varies proportionally to the current. The radiated field intensity is maximal in the plane of the loop.

CrossTalk is induced when a transition on an adjoining signal causes an unintentional signal on the victim net.

Figure 1. Crosstalk Model

Figure 2. Loop Antennas

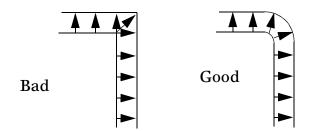

One of the principal techniques for reducing EMI is to build PC boards with signals running over a ground plane. This reduces loop area. The closer the trace is to the ground plane, the smaller the loop. When a trace crosses a break in a plane the loop area is increased (see Figure 3 on page 5).

#### Figure 3. Antenna Formed by a Trace Crossing a Slot

A trace that extends past a reference plane creates a dipole antenna (see Figure 4).

Figure 4. Dipole Antenna

A rectangular metal tube, such as a drive bay, creates a waveguide antenna (see Figure 5).

This box represents a drive bay which can act as a wave guide. The arrows represent EM fields.

#### Figure 5. Waveguide Antenna

#### **Emission Strength**

Emissions are proportional to current, area, and frequency.

If E = electric field (emission), I = current; A = area of loop; r = distance; L = antenna length; and F= frequency, then:

For differential mode: E ~ IAF<sup>2</sup>/r

For common mode: E ~ ILF/r

Emissions are proportional to  $F^2$  for differential mode and proportional to F for common mode. It might seem, therefore, that common mode radiation is easier to deal with than differential mode radiation because the emission increases with F rather than  $F^2$ . In fact, common mode is the more common culprit because in common mode the return current path is usually the earth ground or chassis skin, so the loop area is large and the radiation more serious. In differential mode the return current is in the adjacent wire and the loop area is small.

**High Frequencies** High frequencies radiate more efficiently. Their wavelength is shorter than low frequencies so their waves can pass through smaller holes and can use smaller antennas for a given amount of radiation. Antenna loop area is the single most important attribute that a designer can control. However, because higher frequencies are very directional, they can be easier to shield than lower frequencies.

## **Locating the Source of EMI Using Harmonics**

To determine the source of a radiated peak, divide its measured frequency by 2, 3, 4, and so on, until the frequency matches one of the system frequencies. In a personal computer those frequencies are usually:

| 32 kHz                                                                |

|-----------------------------------------------------------------------|

| 7–8 MHz                                                               |

| 14.31818 MHz                                                          |

| 33.33 MHz                                                             |

| 50 MHz, 60 MHz, 66.66 MHz,<br>75 MHz, 83.3 MHz,<br>95 MHz, or 100 MHz |

| 300 MHz, 350 MHz,<br>333 MHz, 380 MHz,<br>366 MHz, and<br>400 MHz     |

| 50 MHz, 60 MHz, 66.66 MHz,<br>75 MHz, 83.3 MHz,<br>95 MHz, or 100 MHz |

|                                                                       |

Table 1.

Bus Frequency / Multiplier / Resultant Core Frequency

|              | Bus Multiplier (Core Frequency) |     |     |     |     |     |     |     |

|--------------|---------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Bus<br>Speed | 2.5                             | 3.0 | 3.5 | 4.0 | 4.5 | 5.0 | 5.5 | 6.0 |

| 50           |                                 |     |     |     |     |     |     |     |

| 60           |                                 |     |     |     |     |     |     |     |

| 66.6         |                                 | 200 | 233 | 266 | 300 | 333 | 366 | 400 |

| 75           |                                 |     |     |     |     |     |     |     |

| 83.3         |                                 |     |     |     |     |     |     |     |

| 95           |                                 |     | 333 | 380 |     |     |     |     |

| 100          |                                 | 300 | 350 | 400 |     |     |     |     |

AMD-K6<sup>®</sup> Processor EMI Design Considerations

## **Controlling EMI**

|                           | The concepts introduced in this section are explained in more detail in subsequent sections of this application note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                           | Identifying the cause of EMI is usually easy. Fixing the<br>situation is often difficult. Once the EMI source is identified,<br>several remedies are possible. The source can be shielded or<br>filtered. Coupling can be reduced. If loop area is the problem,<br>rethinking the board layout can minimize it. The culprit's<br>rise/fall time might be reduced, eliminating some of the higher<br>harmonics. (Remember a square wave consists of the sum of a<br>fundamental frequency and its odd harmonics. Reducing the<br>edge rate reduces the higher frequency harmonic components.) |  |  |  |  |  |

| At the Emitting<br>Source | The most common EMI source is a clock signal. Clocks are the strongest source of high-frequency current movement in digital circuits. To control emissions due to clocks:                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                           | <ul> <li>Place any pullup resistors used near the driver (source).</li> <li>Pullup resistors at the receiver (destination) increase the loop area.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                           | <ul> <li>Keep clock traces short to minimize lead inductance and<br/>loop area.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                           | <ul> <li>Keep clocks away from I/O lines to prevent coupling.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                           | <ul> <li>Soften clock edges with series termination or resistor-<br/>capacitor (RC) filtering as needed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                           | Use a multilayer printed circuit board (PCB) without cutting<br>the ground plane. Breaks in the ground plane increase printed<br>circuit trace impedance and are also an impedance<br>discontinuity.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                           | Employ careful power-supply decoupling. For instance:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                           | <ul> <li>Decouple each component's V<sub>CC</sub> lead</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                           | <ul> <li>Use low equivalent series resistance (ESR) capacitors</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                           | <ul> <li>Bulk decouple application-specific integrated circuits<br/>(ASICs), processors, and the DC–DC converter input</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                           | <ul> <li>Filter I/O signals with damping resistors and ferrite beads</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                           | <ul> <li>Filter high-frequency components</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

**Shielding the Chassis** Correct PC chassis design is an effective way to control emissions. The PC chassis is a shield for the PC board and the other noise sources in a computer. The shield performance of the chassis is determined by its conductivity and permeability. Conductivity (see "Shielding" on page 18) of the chassis affects its ability to reflect electric fields. Permeability affects its ability to absorb magnetic fields.

Seams and holes in the chassis often leak (radiate) energy and are potentially major EMI culprits. For instance, empty drive bays become slot antennas. Metal or conductive coated plastic filler panels are good solutions for blocking radiation from the drive bays. Be sure the various chassis pieces make electrical contact. A welded chassis is preferred to a riveted chassis because of the better electrical contact between parts.

Avoid a PC chassis with the following characteristics, all of which encourage EMI:

- Oxidized or painted steel pieces

- Non-conductive anodizing aluminum forms

- Long cracks and seams

- Large ventilation holes—both round and slotted

- Few PC board grounding points

A good chassis is key to controlling EMI. A good chassis should be made of steel with spring-metal gaskets or interlocking seams, have a filtered AC power entry, and have metal covers for unused bays or slots. As a general rule, the impedance should be less than 30 milliohms between chassis components. This resistance can be measured with a milliohm meter commonly used to isolate shorted traces on a PC board.

**Correct Cabling** Cabling is another key component that can affect system EMI. Cables may have to contain ferrite beads or be shielded. Connectors may need to be shielded or to have internal filters. When possible, use twisted pair wires so that the field will cancel. Some of the worst EMI offenders are wires that exit the metal frame of the chassis but are inside the exterior cover, such as LEDs, reset switch wires, and the power switch wire.

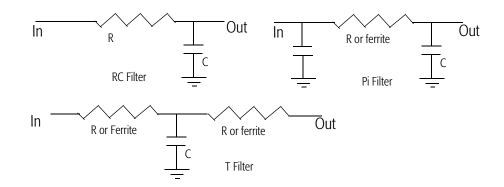

**Filtering I/O Signals** In the event that I/O signals become an unacceptable source of EMI, board layout should be designed to accommodate I/O signal filtering so that the appropriate type of filter can be easily added with a minimal amount of board rework. If the filters are not needed, the inputs and outputs of the filter can simply be shorted. Depending on the function and available board space, different types of filtering can be employed. Often times a capacitor to Frame ground, a simple series resistor, or a capacitor to DC common can solve the problem. Series ferrite beads are effective on signals to the keyboard and serial ports. An RC filter, Pi filter or T filter are often the preferred solution for the parallel port (see Figure 6). Common-mode chokes, most commonly used with networking devices such as Ethernet, can be used on I/O port signals and grounds.

Figure 6. Filtering Techniques

## **Components that Influence EMI**

#### General Component Selection Criteria

Many of the faster technologies used today to implement logical functions induce high current transients which can generate more di/dt noise emitted from a signal. In addition, these larger current transients can degrade signal quality by contributing to signal ringing which can also adversely affect EMI radiation. While selecting slower-speed technologies can alleviate radiation due to these particular sources, it is often not practical because of the requirements of the application, or because the desired function(s) are integrated into higher-level components, thus restricting the designer's choice. The designer is encouraged to request EMI data from the component vendor to assist in making the proper technology choice.

The following components can generate EMI:

- Processor

- Chipset

- Clock chip

- Power supplies: AC-DC and DC-DC

- Chassis

- Memory

- Cables and connectors

- Peripherals

## Processor

The processor can be the source of some EMI problems. It is usually the highest frequency device in a system. It also has a large number of outputs switching.

At these high frequencies, it is important to minimize structures that will produce gain by resonating. Some of these structures are extremely difficult to identify. Others are straightforward. For example, slots and holes in the chassis can act as effective antennas, so look for ways to seal gaps. Empty drive bays are often overlooked culprits. Clock lines going to unpopulated SDRAM sockets should be turned off. Any signal exiting the box via a cable should be filtered. Often the more obscure coupling paths must be debugged by trial and error while measuring the system for radiation.

| Processor, Package,<br>and Heatsink | AMD has done EMI testing on its processors and has minimized<br>their EMI contribution by a combination of on-chip and in-<br>package decoupling capacitors and care in package design.<br>These measures help, but it is still necessary to exercise thought<br>and caution in board and system design. Noise can radiate from<br>the processor lid or heatsink and couple into other components.<br>Even the orientation of the heatsink can influence the amount<br>of radiation.                                                                                                                                                                                                                    |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | The processor package lid can also act as an antenna (it is not<br>grounded). Heatsinks can make an effective antenna. Provide a<br>means to ground the heatsink if needed. Grounding to the<br>chassis (lowest impedance) is usually preferred. However,<br>grounding to the PC board is also effective. Other possible<br>solutions are the SIL-PAD EMI shield from Bergquist or the<br>Flex-Suppressor from Tokin. Either shield is placed between<br>the processor and the heatsink, and absorbs the magnetic field<br>component. (AMD has not used these particular solutions.)                                                                                                                    |

| Frequency Harmonics                 | The second and fourth harmonics usually contain the most<br>energy. Therefore, for a system with a 300-MHz processor, 600<br>MHz and 1200 MHz are often the main problem areas.<br>Harmonics of the bus frequency are also of concern. Bus speeds<br>can be 66.6 MHz, 75 MHz, 83 MHz, 95 MHz, or 100 MHz.<br>Sometimes it is difficult to determine the source of a noise peak<br>as there are several oscillators in a PC. It may be necessary to<br>divide the problem peak frequency by each of the known<br>frequency sources to determine what harmonic of which source<br>is the cause. For example, $475/95 = 5$ , so a $475$ MHz signal is<br>likely the fifth harmonic of a 95 MHz bus signal. |

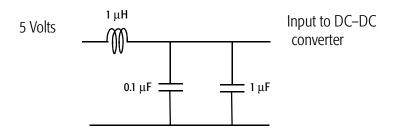

| Core Voltage Filtering              | Adding an EMI filter (see Figure 7 on page 13) at the input to the DC–DC converter generating the core voltage usually helps to decrease EMI. Good high-frequency (0.01 $\mu$ F and 0.001 $\mu$ F) ceramic capacitors across V <sub>CC2</sub> (V <sub>core</sub> ) are important. Be aware of the magnetic saturation current of the inductor chosen. Ensure the DC resistance of the coil is as low as possible. Choosing the wrong inductor can cause a worse problem than not having one.                                                                                                                                                                                                            |

#### Figure 7. Processor Core Power Supply EMI Filter

Remember that radiation efficiency is dependent on the wavelength of the frequency, and higher frequencies radiate better. Filtering these frequencies at the source is the most effective technique for controlling EMI.

VRM Cards Coupling between heatsinks and VRM (Voltage Regulator Module) cards can occur. This coupling can be minimized by orienting the ground plane side of the card towards the processor. If this is impractical the designer may want to add a shield between the VRM card and the processor.

> Ensure the switching regulator's inductor is rated for a higher instantaneous current than needed. (Allow for up to twice the rated current of the power supply.) If the current exceeds its magnetic saturation point, processor harmonic noise will be passed through the inductor to the 5-V plane.

## **Chipset and Clock Chip EMI**

High-frequency clocks can be a major contributor to EMI, so consideration should be given to terminating all clocks on the board. A ferrite bead (surface mounted) or a series resistor installed as close as possible to the source can be included in all clock signals to minimize radiation. Parallel termination—such as a capacitor and resistor in series to ground or a Thevenin pull-up/pull-down resistor—is a better solution if the clock trace is long relative to its rise/fall time (where long is defined as ">(2.5 in/ns) \* T (ns)"). For example, any clock trace longer than 2.5 inches with a rise time of 1.0 ns should be parallel terminated.

To assist with the proper selection of the termination technique, as well as the component value selection, it is

|                                     | recommend that every clock circuit be modeled with an<br>appropriate simulator such as signal integrity tools from<br>Mentor, Cadence, and Viewlogic, or with the classic analog<br>simulator SPICE. IBIS models can be obtained from most<br>component vendors to do these simulations. Most tools focus on<br>signal integrity. However, good signal integrity is a necessary<br>condition for reduced EMI. Current EMI specific tools are not<br>very accurate but can give the designer an idea where problems<br>may exist. |  |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                     | One of the best approaches is to get recommendations from the chip manufacturers, and check if they have any measured data.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                     | Clock chips have clocks going to each SDRAM module. Many clock chips use the I <sup>2</sup> C bus for control. If there are sockets with SDRAM not installed, the clocks to these sockets should be disabled via the I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                 |  |  |  |  |

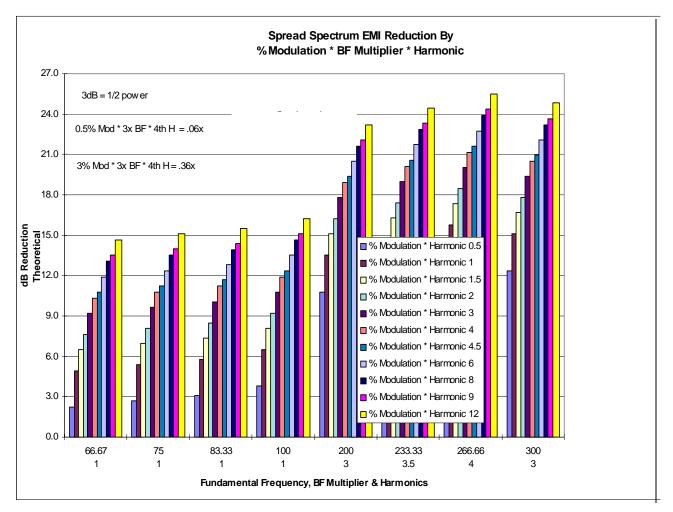

| Spread-Spectrum<br>Clock Generation | Spread-spectrum clock generation (SSCG) is a very useful<br>technique to reduce EMI. It distributes energy over several<br>frequencies rather than concentrating it at one frequency,<br>thereby reducing the EM profile by varying the clock frequency<br>slightly. It is a key technique for high-speed systems, and is<br>especially useful in portable systems because it reduces the<br>shielding required.                                                                                                                 |  |  |  |  |

|                                     | Figure 8 on page 15 shows the effects of SSCG, that is, the theoretical reduction in emissions as a function of frequency and the modulation percentage of the frequency. The reduction in emissions is given by the equation:                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                     | dB reduction = $6.5 + 9\log_{10}P + 9\log_{10}(Freq in MHz)$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                     | where P is defined as the percent reduction in emissions, such that:                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                     | <pre>P = (percent modulation)*(bus frequency multiplier) * (harmonic number)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                     | For example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                     | P = 0.5% Mod * 3 x BF * 4th Harmonic<br>results in a 6% reduction of emissions.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                     | P = 3% Mod * 3 x BF * 4th Harmonic<br>results in a 36% reduction of emissions.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

The benefits of SSCG are more pronounced at higher frequencies.

Figure 8. Effects of Spread Spectrum Clocking

When using SSCG, it is important to verify that other components (Northbridge, SDRAM, etc.) containing PLLs are able to track the frequency change. The AMD-K6 processor PLL is compatible with SSCG, but some motherboards and chipsets may not be.

Many manufacturers of clock chips offer SSCG capability. The following vendors supply spread-spectrum clock chips:

- International Microcircuits Inc. (IMI)

- IC Works

- Integrated Circuit Systems (ICS)

#### Memory

As memory speed increases and buses get wider, the amount of noise generated by memory becomes a significant contribution to total EMI.

The most important consideration for a board designer to minimize EMI due to memory is to have good decoupling near the memory sockets. It is also important to keep the traces from the memory controller to the Dual Inline Memory Module (DIMM) sockets as short as possible.

Sometimes changing from one brand of memory to another can have a pronounced effect. This is partially due to decoupling and layout on the module but can also depend on the brand of DRAM used.

## **AC Power Supply**

Often designers focus on radiated noise, but conductive noise is also an important part of meeting regulatory requirements. Conducted emissions (below 30 MHz) occur through the AC power line. The AC line cord can pick up radiated emissions and pass them down the line. It can also conduct internally generated noise from inside the chassis down the power cable. The best practice is positioning a line filter near the exit point of the line cord.

Some power supplies have an EMI filter built in, but many do not. Choose a power supply that has a built-in EMI filter. This is often overlooked. A good power entry filter is usually the easiest way to meet conductive EMI requirements. In general, power supplies with poor bulk and/or high-frequency decoupling usually fail EMI testing.

## **Chassis Design**

Chassis parts should be in good electrical contact with each other. It is important to keep impedance less than 30 milliohms between chassis parts. Impedance greater than 75 milliohms will lead to EMI problems.

- Covers and fascias leak when not grounded. A chassis design that has wide overlapping cover contacts can have poor impedance contact.

- Be aware of the possibility of long, narrow gaps in the chassis, perhaps caused by a bend in the chassis cover or a long seam. These gaps, although sometimes difficult to see, can become large antennas.

- The effective length of a long gap or seam can be reduced by adding intermediate ground points. Welded seams (impedance less than 30 milliohms) are preferred to riveted seams (impedance greater than 70 milliohms). It is also possible to use grounding metal gaskets on seams.

- Avoid having oxidation or paint at grounding (contact) points. Be aware of paint that may be preventing different chassis pieces from making an electrical connection.

- High contact impedance of ISA/PCI slot covers is very common. Slot covers should not be painted. It is preferred that they be held in place by a screw, not just a clip. The top of the cover should have an angular detent to bite into the chassis when the screw is tightened.

- Large areas of metal plates without any contact area can act like capacitor plates. For example, a metal plate below the motherboard in a tower PC and the side metal cover can act like capacitor plates. The motherboard is grounded only to the closer plate. The chassis design should minimize the impedance between these two pieces by good electrical contact between the two plates at several locations.

AMD-K6<sup>®</sup> Processor EMI Design Considerations

| Apertures in a<br>Chassis | Apertures (vents, holes, seams, screens) in a chassis can cause EMI leakage.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                           | <ul> <li>Apertures radiate at wavelengths equal to or less than their<br/>length. The length of an aperture is inversely proportional to<br/>the leaking resonant frequency.</li> </ul>                                                                                                                                                              |  |  |  |  |  |

|                           | • Small holes and short seams prevent leakage of low frequencies.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                           | • Circles have minimal width for a given area, so round vents are better than slots (which are typically rectangular).                                                                                                                                                                                                                               |  |  |  |  |  |

|                           | • Screens are the best vents because of their small hole size.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                           | <ul> <li>Apertures should be shorter than one tenth of the<br/>wavelength to be shielded. For instance:</li> </ul>                                                                                                                                                                                                                                   |  |  |  |  |  |

|                           | • A 300-MHz frequency has a 1-meter wavelength, so boxes with harmonics less than 300 MHz can have 10-centimeter apertures.                                                                                                                                                                                                                          |  |  |  |  |  |

|                           | • A 5.25-inch drive bay is about a 800-MHz to 900-MHz slot antenna and a 3.5-inch drive bay is about a 1-GHz to 1.2-GHz slot antenna.                                                                                                                                                                                                                |  |  |  |  |  |

| Shielding                 | The relative shielding effectiveness of a chassis can be<br>measured by testing the same motherboard along with its<br>associated components in each chassis being considered. In<br>EMI testing it is important to change only one variable at a<br>time.                                                                                           |  |  |  |  |  |

|                           | For most high-frequency fields, a thin shield is sufficient. Lower<br>frequency magnetic fields, however, need thicker ferrous<br>material as a shield.                                                                                                                                                                                              |  |  |  |  |  |

|                           | The permeability of the chassis material and its thickness affect<br>its ability to be an effective shield. For example, Table 2 shows<br>why a copper-nickel paint is used inside of notebook computers<br>for shielding. Copper has high conductivity, to block electric<br>fields and nickel has high permeability, to absorb magnetic<br>fields. |  |  |  |  |  |

| AMD-K6® | Processor | EMI Design | Considerations |

|---------|-----------|------------|----------------|

|---------|-----------|------------|----------------|

|                                                                                                                                                                                                                                                                                                                                                             | Material | Conductivity <sup>1</sup><br>ज <sub>r</sub> | Permeability²<br>µr |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------|---------------------|

| Copper                                                                                                                                                                                                                                                                                                                                                      |          | 1                                           | 1                   |

| Aluminum                                                                                                                                                                                                                                                                                                                                                    |          | 0.64                                        | 1                   |

| Steel                                                                                                                                                                                                                                                                                                                                                       |          | 0.17                                        | 1000                |

| Nickel                                                                                                                                                                                                                                                                                                                                                      |          | 0.2                                         | 100                 |

| Zinc                                                                                                                                                                                                                                                                                                                                                        |          | 0.3                                         | 1                   |

| Chromium                                                                                                                                                                                                                                                                                                                                                    |          | 0.65                                        | 1                   |

| Tin                                                                                                                                                                                                                                                                                                                                                         |          | 0.15                                        | 1                   |

| Stainless                                                                                                                                                                                                                                                                                                                                                   |          | 0.02                                        | 200                 |

| <b>Notes:</b><br>1. $\sigma_r = conductivity relative to copper (Cu = 1).$<br>$\sigma_{Cu} = 5.8 \times 10^7$ siemens/m<br>2. $\mu_r = permeability relative to copper (Cu = 1).$<br>$\mu_{Cu} = 1 \times 10^{-7}$ henries/m<br>3. $R = resistance. R = 1/\sigma t (\Omega/m^2)$ , where t is thickness and $\sigma$ is actual, not relative, conductivity. |          |                                             |                     |

#### Table 2. Conductivity and Permeability

**Reflection**Reflection is the key mechanism for controlling high<br/>frequencies. The shield provides an impedance mismatch<br/>between the incident wave and the barrier impedance.<br/>Reflection is the dominant effect for far-field measurements.

# AbsorptionAbsorption is the key mechanism for controlling low-frequency<br/>or low-impedance emissions. Absorption requires use of a<br/>permeable material. (See Table 2.) Absorption is the dominant<br/>effect for near-field measurements.

#### Calculating Shielding Effectiveness

To calculate shielding effectiveness, use the following equations:

$$A_{dB} = \frac{8.7\frac{t}{\delta}}{\sqrt{\epsilon_R + 1.41}}$$

$$A_{dB} = 132 t \sqrt{f_{MHz} \sigma_r \mu_r}$$

$A_{dB}$  = Absorption loss (dB)

t = Thickness of shield (mm)

$\delta$  = Skin depth (mm)

$\varepsilon_{\rm R}$  = Dielectric constant

$f_{MHz}$  = Frequency (MHz)

$\sigma_r$  = Conductivity (relative to copper)

$\mu_r$  = Permeability (relative to copper)

## **Components, Cables, and Connectors**

Much of the noise generated within a PC finds its way out through cables (printer, mouse, monitor, network, serial ports etc.). Therefore, it is important that each of these potential sources have appropriate shielding or filtering.

External cables (RS232 serial, parallel printer, mouse, keyboard, USB, 1394, Ethernet, front-panel LEDs, front-panel controls, etc.) are a prime source of radiated emissions. This is especially true at frequencies less than 150 MHz.

Internal cables can also present EMI problems. In particular, floppy and hard drive cables which connect to the drive bays can conduct noise from elsewhere in the system to the bays, which are generally poorly shielded.

There are three ways to deal with cable EMI—shielding, clamping, and filtering. Shielded cables rely on the Faraday principle and require a good earth ground. Proper connection of the shield is imperative. (See Figure 9 on page 21.) Clamping is simple and cheap. Use ferrite rings or clamps to suppress magnetic fields. This is a common approach on monitor cables. Filtering the signal before it enters the cable reduces harmonics. Serial ports, printer ports, and network ports often use this approach.

There are several common filtering techniques—power line filters, RC filters, LC filters (using ferrite beads), and connectors with filters built in. Network cards often have complex filters designed for the specific application. The effectiveness of these filters can vary widely from one manufacturer to another. It is important to qualify each part number from its manufacturer.

As a general rule, limit the bandwidth to five times the data frequency. For example, on a serial port with a frequency of 128 Kbits/sec, set the filter roll-off point at around 640 kHz. Often the roll-off point is chosen to be higher to minimize filter component size.

|                                                   | × | -Back of chassis  |

|---------------------------------------------------|---|-------------------|

| Unacceptable:<br>Drain wire<br>to PCB             |   | To motherboard    |

| Poor:<br>Drain wire<br>to shield                  |   | Inside of chassis |

| Acceptable:<br>Drain wire<br>to outside<br>shield |   |                   |

| Preferred:<br>Circumferential<br>wrap             |   |                   |

#### Figure 9. Properly Terminating Cables

High-speed integrated circuits that incorporate drivers capable of directly driving cables (without the need for additional external buffering) may propagate high-frequency components of the clock that is supplied to this integrated circuit. Therefore, the signals that drive the cable should be filtered to minimize this potential source of radiation. If the I/O designer provides separate power pins to the I/O ring, the board designer can provide separate decoupling on these pins. Alternatively the I/O power supply can be isolated from the main system supply.

## **Peripherals**

Network cards, video cards, hard disk drives, CDROMs and other peripheral devices can all be sources of EMI. Although these devices are not addressed in this application note, they cannot be ignored while seeking to minimize EMI.

## **Power Requirements**

Today's microprocessor systems use several different voltages. Proper decoupling (bypassing) is an essential feature of a board designed for good EMI characteristics.

Good decoupling involves attending to several requirements, such as having a good ground system and minimizing ground loops and return current paths. These topics are addressed below.

## **Ground Plane**

The ground plane is often thought of as an ideal reference, but in reality it is far from ideal, having both inductance and resistance. Numerous holes in the ground plane for vias and connectors make matters worse.

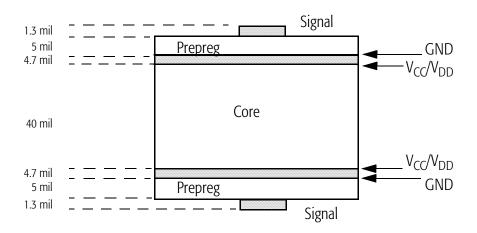

One way to minimize EMI is buried capacitance (see Figure 10 on page 24). This technique places the  $V_{CC}$  and GND planes very close together (1–2 mils), forming a very good high-frequency capacitor and reducing the number of discrete capacitors required.

Another aspect of this technique is that two  $V_{CC}$ -to-GND sandwiches can be used. Benefits of this method include:

- The inductance and impedance of the planes are reduced because there are effectively two planes in parallel.

- Signals on both sides of the board are referenced to a GND.

- The extra voltage plane need not be used for V<sub>CC</sub>, but could be a V<sub>DD</sub> plane.

- Because the signals are always referenced to ground, signals never cross a split in the power plane.

Buried capacitance costs more than conventional techniques. However, the cost is partially offset by the reduced number of high-frequency bypass capacitors needed. Bulk decoupling is still required.

Other Ground-Related Rules **Motherboard Grounding.** Connect the motherboard ground plane to chassis ground in one, and only one, location. There are often two available screw holes approximately 2 inches apart near the rear of the chassis that can provide this ground connection. Relative to the size of the board, either connection may be considered a single-point ground connection. Additional ground connections can be achieved by connecting the motherboard ground plane to chassis ground with 0.01  $\mu$ F capacitors mounted as close as possible to the board I/O connectors (such as the IDE, floppy, serial, and parallel connectors). While this latter method may not always be practical on desktop machines, this can be a useful technique for notebook computers.

External I/O connector shields should be connected to a lowimpedance chassis ground on the board. This is extremely important for network connections.

**Package Grounding.** Each ground pin on a package should be connected to ground by means of its own via. Avoid tying two ground pins on a package together and then to ground.

Adapter Cards. To prevent ground loops in cable shields, an adapter card bracket must not have a DC connection to its ground plane. If the adapter provides an I/O port that connects to an external shielded cable, the adapter ground plane should be connected to the chassis ground of the bracket by means of a  $0.01 \,\mu\text{F}$  capacitor.

Some adapters contain components—such as audio, network, and video adapters—that require more noise immunity than normal, in which case an isolated ground plane should be used for these particular components. This isolated ground should be connected to the adapter ground plane with a "bridge" that crosses the "moat" that isolates the two planes. This bridge is typically routed in a direction as far away as possible from the "noisiest" component(s) on the adapter. To avoid creating ground loops, signals must be routed over the bridge so that the return currents flow under the signal trace (that is, through the bridge). If there are too many signals for this to be practical, return paths can be created by connecting  $0.01\mu$ F capacitors between the two ground planes. One capacitor should be used for every eight signal traces, and the signal traces must be as near as possible to the capacitor.

## **Decoupling and Layout Recommendations**

# **"Coffee Cup" Rule** The coffee cup rule refers to the amount of bulk decoupling distributed around the board. In general there should be approximately 22 μF for every 6–8 square inches of board area. (A coffee cup is about 3 inches in diameter or about 7 square inches.) It is desirable to minimize the distance that charge must travel, so several small capacitors are preferable to a few large ones. For example, one 22-μF capacitor every 7 square inches is preferable to one 100-μF capacitor every 40 square inches.

Adequate bulk decoupling at the power supply connection to the motherboard is also important. Generally from 1000  $\mu$ F to 3000  $\mu$ F is required. These capacitors effectively reduce loop area by supplying charge locally on the board rather than from the more inductive path through the power supply wires.

Requirements of specific devices take precedence over these general rules. Follow the manufacturer's recommendations for a specific device.

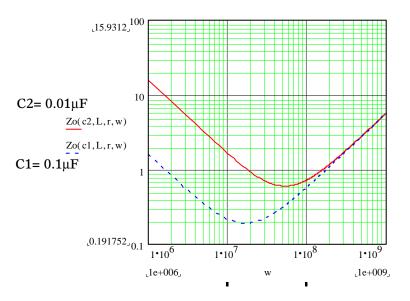

GeneralBecause multi-layer ceramic (MLC) capacitors becomeHigh-Frequencyinductive as frequencies increase (as illustrated by Figure 15 on<br/>page 31) it is important to use both 0.01-µF and 0.001-µF<br/>capacitors as part of a high-frequency solution. The number of<br/>capacitors to use is a function of the type, speed, purpose, and<br/>quantity of the components on the board. An example

|                                                    | calculation is shown in "Calculating Required Number of Capacitors" on page 31.<br>Each component that sources or receives a clock signal greater than 30 MHz should be decoupled with an additional 300 pF capacitor placed as close as possible to the power pin of that component. Larger capacitors, such as 1000 pF, can be used for additional decoupling for components that run at frequencies less than 30 MHz.<br>One or more low-ESR 22 $\mu$ F bulk decoupling capacitors should be used at floppy or fixed disk drive connectors where large DC currents are drawn. Additionally, all +12 V and -12 V loads should be decoupled with MLC capacitors (0.01 $\mu$ F). |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | Any connector pin on the board that supplies power ( $V_{CC}$ or $V_{DD}$ ) should be decoupled with a 0.01 µF MLC capacitor in addition to any bulk decoupling that may be required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Controlling<br>Switching-Regulator-<br>Induced EMI | <ul> <li>The following methods can be used to reduce switching-regulator-induced EMI:</li> <li>Add a ferrite bead in series with diodes.</li> <li>Add a capacitor across rectifier diodes.</li> <li>Use soft-recovery, high-speed diodes.</li> <li>Keep leads short and twist the hot and return wire.</li> <li>Trade off efficiency for noise by slowing down transistor turn-on time. Noise is reduced but some efficiency is lost. Slowing down is done by using an RC circuit to slow down the base drive of the power transistor.</li> </ul>                                                                                                                                |

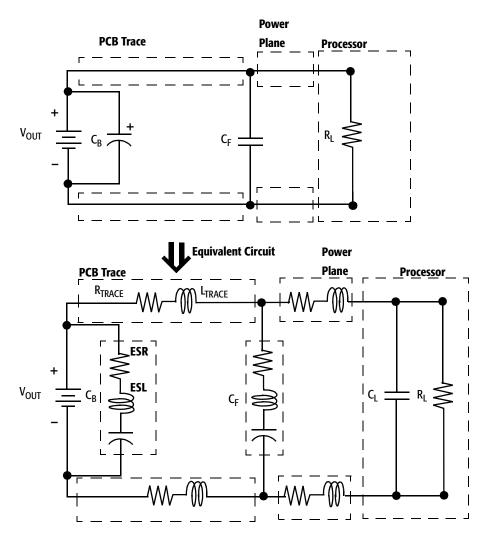

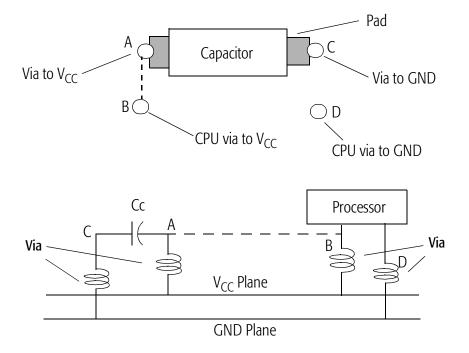

| Power Distribution                                 | In order to maintain a stable voltage supply during fast transients, power planes with high-frequency and bulk decoupling capacitors are required. Figure 11 on page 27 shows a power distribution model for the power supply and the processor. The bulk capacitors ( $C_B$ ) are used to minimize ringing, and the processor decoupling capacitors ( $C_F$ ) are spread evenly across the circuit to maintain stable power distribution.                                                                                                                                                                                                                                       |

|                                                    | The high-frequency decoupling capacitors ( $C_F$ ), which are<br>typically smaller in capacitance and equivalent series<br>inductance (ESL) than the bulk capacitors ( $C_B$ ), maintain the<br>voltage output during average load change until $C_B$ can react.                                                                                                                                                                                                                                                                                                                                                                                                                 |

See "High-Frequency Decoupling Calculations" on page 30 for more information.

See the power supply design application note  $(AMD-K6^{\circledast} Processor Power Supply Design, order# 21103)$  for desktop processor-specific decoupling requirements. See Mobile AMD-K6<sup>®</sup> Processor Power Supply Design, order# 21677 for mobile processor-specific decoupling requirements.

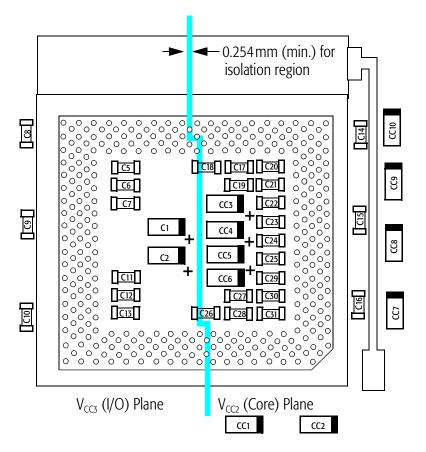

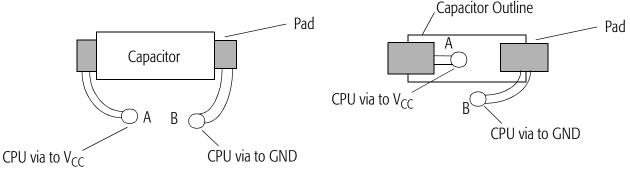

# **Decoupling Capacitance and Placement**

The high-frequency decoupling capacitors (C5 to C31), in Figure 12, should be located as close to the processor power and ground pins as possible. To minimize resistance and inductance in the lead length, it is recommended to use surface mounted capacitors. When possible, use traces to connect capacitors directly to the processor's power and ground pins. In most cases, the decoupling capacitors can be placed in the Socket 7 cavity on the same side of the processor (component side) or the opposite side (bottom side).

Figure 12 shows a suggested component placement for the decoupling capacitors. The split voltage planes should be isolated if they are in the same layer of the circuit board. To separate the two power planes, an isolation region at least 0.254 mm (0.01 in.) wide is recommended. Do not split the ground plane.

Figure 12. Suggested Component Placement

Capacitors from different manufacturers may vary greatly in resistance. Table 3 compares parts of equal capacitance but different manufacturers. It is important to check manufacturer's specifications.

| Capacitance | Manufacturer<br>1 | Manufacturer<br>2 |

|-------------|-------------------|-------------------|

| 470 μF      | 55 mΩ             | 100 m $\Omega$    |

| 270 μF      | 70 m $\Omega$     | 100 m $\Omega$    |

| 100 μF      | 90 mΩ             | 100 m $\Omega$    |

| 68 μF       | 95 mΩ             | 100 m $\Omega$    |

| 47 μF       | 120 m $\Omega$    | 250 mΩ            |

Table 3.Representative ESR Values

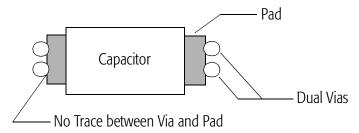

Via Inductance Vias act as inductors. Via inductance can be reduced when using double-sided component assembly. Components can share vias on the top and bottom sides, reducing the effective via inductance. Double-sided assembly is rarely used in desktop systems, so this technique is more commonly used for portable systems.

Parallel vias can also be used to reduce via inductance (see Figure 13). This technique is usually used on bulk decoupling capacitors. The inductance contribution numbers shown in Table 4 indicate that a poor layout can negate the effect of a good component.

Figure 13. Via Layout for Low Inductance

| Table 4. | Inductance | Contributions | of | Components |

|----------|------------|---------------|----|------------|

|----------|------------|---------------|----|------------|

| Component          | Induction              | Comment           |

|--------------------|------------------------|-------------------|

| Capacitor          | 0.6 nH (approximately) | ESL               |

| Via                | 0.7 nH (approximately) | -                 |

| 100 mil long trace | 1.6 nH (approximately) | 10 mil wide trace |

Aluminum electrolytics can be used instead of tantalum capacitors, as long as good-quality, low-ESR parts are used. The biggest problem with aluminum electrolytics is the large decrease in capacitance as they age. Aluminum electrolytics rated for -40 to +105 degrees C generally have better aging characteristics when operated in the 0 to +70 degrees C range.

High-Frequency<br/>DecouplingInductance is also a concern for the high-frequency decoupling<br/>capacitors. Case size can be a significant factor affecting<br/>capacitor inductance. For example, a 0603 case has<br/>significantly more inductance than a 0612 case. AMD<br/>recommends the 0612, 1206, 0805, and 0603 cases in order of<br/>preference (best to worst).

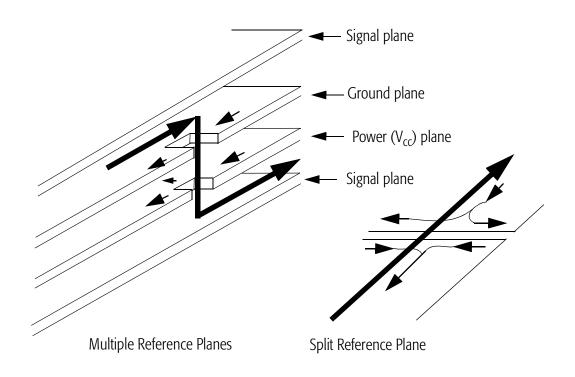

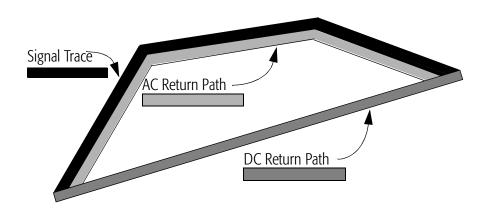

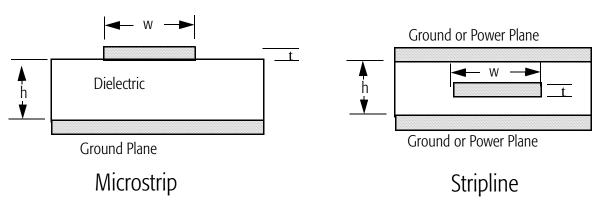

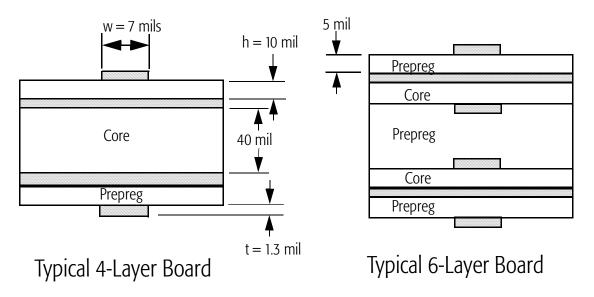

Inductance can also be reduced by directly connecting the capacitor to the power pin of the processor. In order to minimize inductance, the trace must be short and as wide as possible. This technique effectively removes two via inductances between the capacitor and the processor as shown in Figure 14. The dotted line shows that connecting the capacitor directly to the processor eliminates two series inductances. However, this trace also has inductance—if it is too long or too narrow it can be worse than the vias.