# 82420EX PCISET DATA SHEET 82425EX PCI SYSTEM CONTROLLER (PSC) AND 82426EX ISA BRIDGE (IB)

- **Host CPU**

- 25-33 MHz Intel486™ and OverDrive™ Processors

- -L1 Write-Back Support

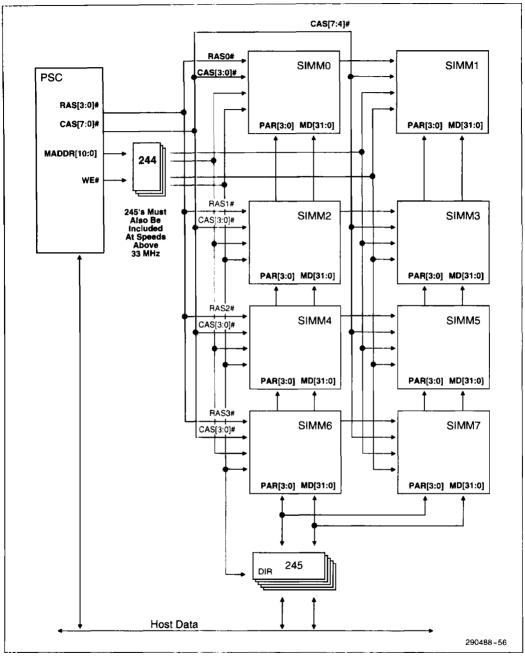

- **Integrated DRAM Controller**

- 1 to 128 MByte Main Memory

- 70 ns Fast Page Mode DRAM SIMMs Supported

- Supports 256 KByte, 1 MByte, and 4 MByte Double and Single Sided SIMMs

- --- Read Page Hit Timing of 3-2-2-2 at 33 MHz

- Burst Mode PCI Master Accesses

- Decoupled Refresh Reduces DRAM Latency

- Five RAS Lines

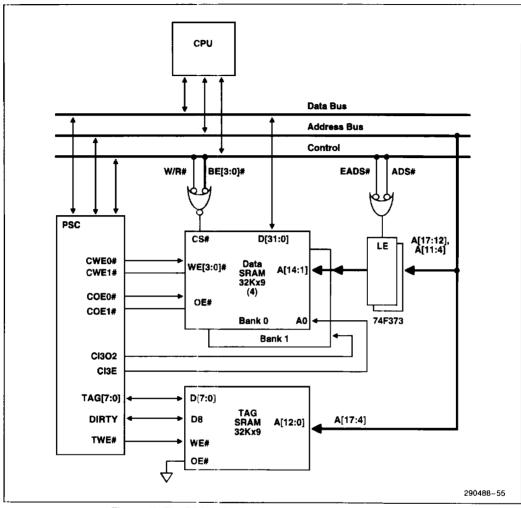

- Integrated L2 Cache Controller

- Write-Back and Write-Through Cache Policies

- Direct Mapped Organization

- -- 64, 128, 256 or 512 KByte Cache

- Programmable Zero Wait-State L2

Cache Read and Write Accesses

- Two Banks Interleaved or a Single Bank Non-Interleaved Operation

- -- No VALID Bit Required

- 25/33 MHz PCI Bus Interface

- Two Bus Masters

- PCI Auto Configuration Support

- **■** Host/PCI Bridge

- Converts Back-to-Back Sequential Memory Writes to PCI Burst Writes

- CPU Memory Write Posting to PCI

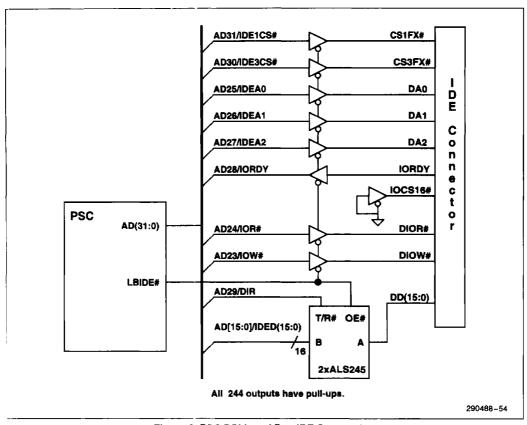

- PCI Local Bus IDE Interface

- Supports Mode 3 Timing

- Programmable Attribute Map for First 1 MByte of Main Memory

- 100% ISA Compatible

- Directly Drives 5 ISA Slots

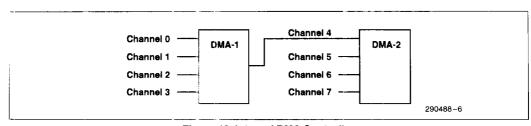

- **Two 8237 DMA Controllers**

- 7 DMA Channels

- 27-bit Addressability

- Compatible DMA Transfers

- One 82C54 Timer/Counter

- System Timer

- Refresh Request

- Speaker Tone

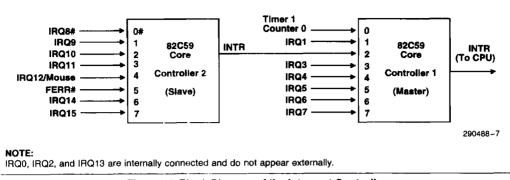

- **Two 82C59 Interrupt Controllers**

- 14 Interrupts

- Edge/Level Sense is Programmable per Channel

- PCI Interrupt Steering for Plug and Play Compatibility

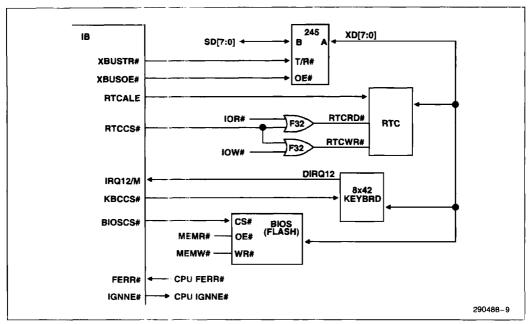

- X-Bus Peripheral Support

- RTC, KBC, BIOS Chip Selects

- Control for Lower X-Bus Transceiver

- Integrates Mouse Interrupt

- Coprocessor Error Reporting

- Non-Maskable Interrupts (NMI)

- PCI System Errors

- Main Memory Parity Errors

- ISA Parity Errors

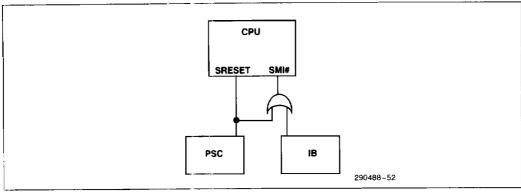

- System Power Management (Intel SMM Support)

- Programmable System Management Interrupt (SMI)—Hardware Events, Software Events, EXTSMI#

- Programmable CPU Clock Control

- Fast On/Off Mode

- Generates System Clocks

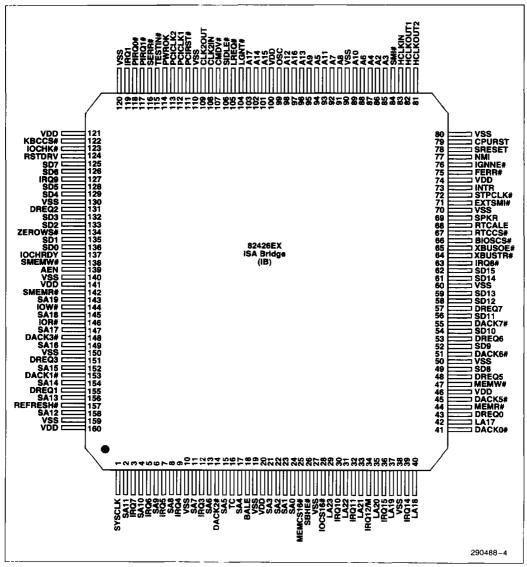

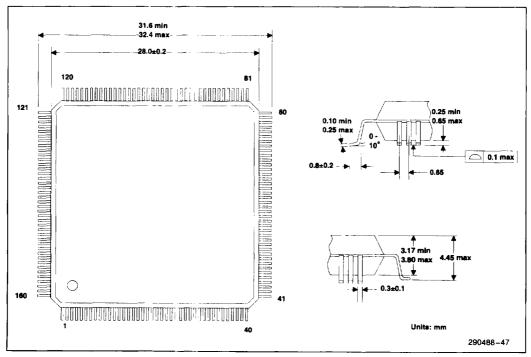

- 160-Pin QFP Package for IB

- 208-Pin QFP Package for PSC

#### 82420EX

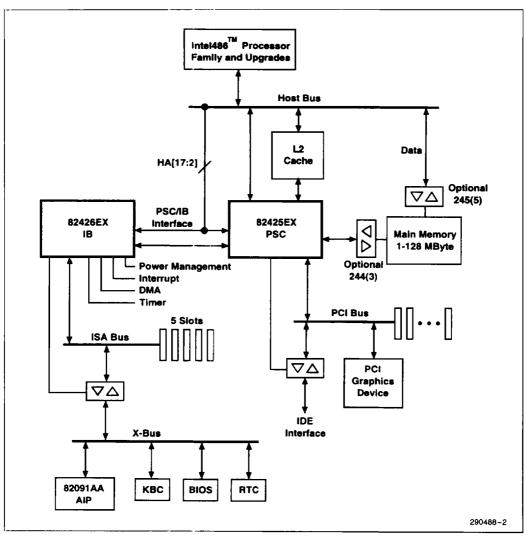

The 82420EX PCIset is the foundation for the **Value Flexible Motherboard** solution for entry-level Intel486<sup>TM</sup> processor-based PCI systems. The Value Flexible Motherboard solution, including 82420EX, Intel486 processor, 82091AA Advanced Integrated Peripherals, 82C42 Keyboard Controller, Flash BIOS, and Plug & Play software, drives PCI into the mainstream. The 82420EX PCIset is a highly integrated solution enabling low cost, small form factor motherboard designs. All Intel486 processors and upgrades are supported, including L1 write-back and Intel SMM power management. PCI Local Bus IDE is incorporated for higher performance IDE at no additional cost.

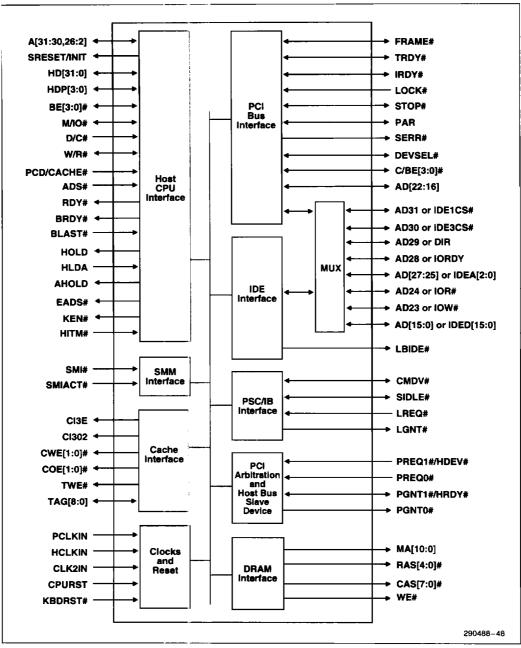

The 82420EX was designed from the ground up for PCI performance. It consists of two components—the 82425EX PCI System Controller (PSC) and the 82426EX ISA Bridge (IB). The PSC integrates the L2 cache controller and the DRAM controller. The cache controller supports both write-through and write-back cache policies and cache sizes from 64 KBytes to 512 KBytes in an interleaved or non-interleaved configuration. The DRAM controller interfaces main memory to the Host Bus and the PCI Bus. The PSC supports a two-way interleaved DRAM organization for optimum performance. Up to ten single-sided SIMMs or four double-sided and two single-sided SIMMs provide a maximum of 128 MBytes of main memory. The PSC provides memory write posting to PCI for enhanced CPU-to-PCI memory write performance. In addition, the PSC provides a high performance PCI Local Bus IDE interface.

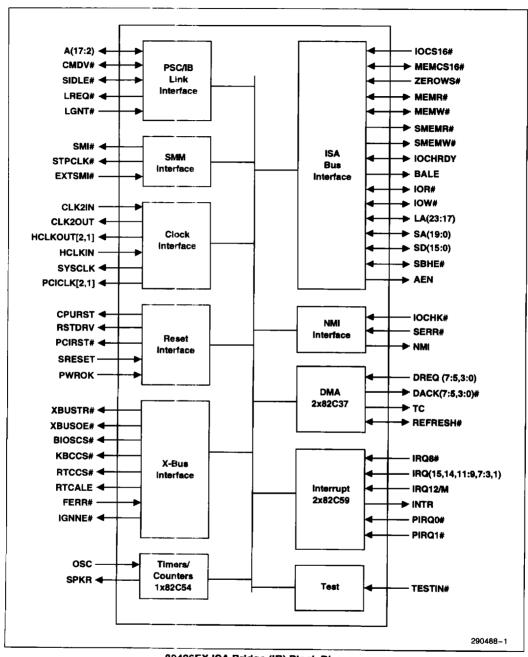

The IB is the bridge between the ISA Bus and Host Bus, and integrates the common I/O functions found in today's ISA-based PC systems—a seven channel DMA controller, two 82C59 interrupt controllers, an 8254 timer/counter, Intel SMM power management support, and control logic for NMI generation. The IB also provides the decode for external BIOS, real time clock, and keyboard controller. Edge/Level interrupts and interrupt steering are supported for PCI plug and play compatibility. The IB integrates the ISA address and data path, reducing TTL and system cost. In addition, the integration of system clock generation logic eliminates the need for external host and PCI clock drivers.

82425EX PCI System Controller (PSC) Block Diagram

82426EX ISA Bridge (IB) Block Diagram

# 82420EX PCISET DATA SHEET 82425EX PCI SYSTEM CONTROLLER (PSC) AND 82426EX ISA BRIDGE (IB)

| CONTENTS                                              | PAGE  |

|-------------------------------------------------------|-------|

| 1.0 PINOUT INFORMATION                                |       |

| 1.1 PSC Pin Assignment                                |       |

| 1.2 IB Pin Assignment                                 | 1-269 |

| 2.0 SIGNAL DESCRIPTION                                |       |

| 2.1 PSC Signals                                       |       |

| 2.1.1 HOST CPU INTERFACE SIGNALS (PSC)                |       |

| 2.1.2 SECONDARY CACHE SIGNALS (PSC)                   |       |

| 2.1.3 PCI SIGNALS (PSC)                               |       |

| 2.1.4 SYSTEM POWER MANAGEMENT (SMM) SIGNALS (PSC)     |       |

| 2.1.5 DRAM CONTROL SIGNALS (PSC)                      |       |

| 2.1.6 PSC/IB LINK INTERFACE (PSC)                     |       |

| 2.1.7 PCI BUS ARBITRATION/HOST BUS SLAVE DEVICE (PSC) | 1-278 |

| 2.1.8 PCI BUS IDE (PSC)                               | 1-279 |

| 2.1.9 CLOCKS AND RESET (PSC)                          |       |

| 2.2 IB Signals                                        |       |

| 2.2.1 ISA INTERFACE SIGNALS (IB)                      | 1-280 |

| 2.2.2 NMI SIGNALS (IB)                                | 1-282 |

| 2.2.3 DMA SIGNALS (IB)                                | 1-282 |

| 2.2.4 TIMER/COUNTER SIGNALS (IB)                      | 1-283 |

| 2.2.5 INTERRUPT CONTROLLER SIGNALS (IB)               |       |

| 2.2.6 X-BUS SIGNALS (IB)                              |       |

| 2.2.7 PSC/IB LINK INTERFACE SIGNALS (IB)              | 1-285 |

| 2.2.8 SYSTEM POWER MANAGEMENT (SMM) SIGNALS (IB)      |       |

| 2.2.9 SYSTEM CLOCK SIGNALS (IB)                       |       |

| 2.2.10 SYSTEM RESET SIGNALS (IB)                      |       |

| 2.2.11 TEST SIGNALS (IB)                              | 1-286 |

| 3.0 REGISTER DESCRIPTION                              | 1-287 |

| 3.1 Register Access                                   | 1-287 |

| 3.2 I/O Control Registers                             |       |

| 3.2.1 CONFADD—CONFIGURATION ADDRESS REGISTER          | 1-294 |

| 3.2.2 CONFDATA—CONFIGURATION DATA REGISTER            |       |

| 3.2.3 TRC—TURBO/RESET CONTROL REGISTER                | 1-295 |

| CONTENTS                                             | PAGE  |

|------------------------------------------------------|-------|

| 3.3 PCI Configuration Registers                      | 1-296 |

| 3.3.1 VID—VENDOR IDENTIFICATION REGISTER             | 1-296 |

| 3.3.2 DID—DEVICE IDENTIFICATION REGISTER             | 1-296 |

| 3.3.3 PCICOM—PCI COMMAND REGISTER                    | 1-296 |

| 3.3.4 DS—DEVICE STATUS REGISTER                      | 1-297 |

| 3.3.5 RID—REVISION IDENTIFICATION REGISTER           | 1-298 |

| 3.3.6 PCICON—PCI CONTROL REGISTER                    | 1-298 |

| 3.3.7 HOSTDEV—HOST DEVICE CONTROL REGISTER           | 1-300 |

| 3.3.8 LBIDE—PCI LOCAL BUS IDE CONTROL REGISTER       | 1-300 |

| 3.3.9 IORT—ISA I/O RECOVERY TIMER REGISTER           | 1-303 |

| 3.3.10 PREV—PART REVISION REGISTER                   | 1-304 |

| 3.3.11 XBCSA—X-BUS CHIP SELECT A REGISTER            | 1-304 |

| 3.3.12 HOSTSEL—HOST SELECT REGISTER                  | 1-306 |

| 3.3.13 DFC—DETURBO FREQUENCY CONTROL REGISTER        | 1-306 |

| 3.3.14 SCC—SECONDARY (L2) CACHE CONTROL REGISTER     | 1-307 |

| 3.3.14.1 L2 Write Timing                             | 1-308 |

| 3.3.15 DRAMC—DRAM CONTROL REGISTER                   | 1-309 |

| 3.3.16 PAM[6:0]—PROGRAMMABLE ATTRIBUTE MAP REGISTERS |       |

| 3.3.17 DRB—DRAM ROW BOUNDARY REGISTERS               | 1-312 |

| 3.3.18 PIRQ1RC/PIRQ0RC—PIRQ ROUTE CONTROL REGISTERS  | 1-313 |

| 3.3.19 DMH—DRAM MEMORY HOLF REGISTER                 | 1-314 |

| 3.3.20 TOM—TOP OF MEMORY                             | 1-314 |

| 3.3.21 SMRAMCON-SMRAM CONTROL REGISTER               | 1-315 |

| 3.3.22 SMICNTL—SMI CONTROL REGISTER                  | 1-317 |

| 3.3.23 SMIEN—SMI ENABLE REGISTER                     | 1-318 |

| 3.3.24 SEE—SYSTEM EVENT ENABLE                       |       |

| 3.3.25 FTMR—FAST OFF TIMER REGISTER                  |       |

| 3.3.26 SMIREQ—SMI REQUEST REGISTER                   |       |

| 3.3.27 CTLTMRL—CLOCK THROTTLE STPCLK# LOW TIMER      |       |

| 3.3.28 CTLTMRHCLOCK THROTTLE STPCLK# HIGH TIMER      | 1-322 |

| 3.4 ISA-Compatible Registers                         |       |

| 3.4.1 DMA REGISTER DESCRIPTION                       |       |

| 3.4.1.1 DCOM—DMA Command Register                    | 1-323 |

| 3.4.1.2 DCM—DMA Channel Mode Register                |       |

| 3.4.1.3 DREQDMA Request Register                     | 1-325 |

| 3.4.1.4 WSMB—Write Single Mask Bit Register          | 1-325 |

| CONTENTS                                                                                | PAGE  |

|-----------------------------------------------------------------------------------------|-------|

| 3.4.1.5 WAMB—Write All Mask Bits Register                                               | 1-326 |

| 3.4.1.6 DS—DMA Status Register                                                          | 1-327 |

| 3.4.1.7 DB&CA—DMA Base And Current Address Registers (8237 Compatible Segment)          | 1-327 |

| 3.4.1.8 DB&CBW—DMA Base And Current Byte/Word Count Registers (8237 Compatible Segment) |       |

| 3.4.1.9 DMLPG—DMA Memory Low Page Registers                                             |       |

| 3.4.1.10 DMHPG—DMA Memory High Page Register                                            |       |

| 3.4.1.11 DCLBP—DMA Clear Byte Pointer Register                                          |       |

| 3.4.1.12 DMCL—DMA Master Clear Register                                                 |       |

| 3.4.1.13 DCLM—DMA Clear Mask Register                                                   | 1-330 |

| 3.4.2 TIMER/COUNTER REGISTER DESCRIPTION                                                | 1-331 |

| 3.4.2.1 TCW—Timer Control Word Register                                                 | 1-331 |

| 3.4.2.2 TMSTAT—Interval Timer Status Byte Format Register                               | 1-335 |

| 3.4.2.3 CAPS—Counter Access Ports Register                                              | 1-336 |

| 3.4.3 INTERRUPT CONTROLLER REGISTER DESCRIPTION                                         | 1-336 |

| 3.4.3.1 ICW1—Initialization Command Word 1 Register                                     | 1-336 |

| 3.4.3.2 ICW2—Initialization Command Word 2 Register                                     | 1-337 |

| 3.4.3.3 ICW3—Initialization Command Word 3 Register                                     | 1-338 |

| 3.4.3.4 ICW3—Initialization Command Word 3 Register                                     | 1-338 |

| 3.4.3.5 ICW4—Initialization Command Word 4 Register                                     | 1-339 |

| 3.4.3.6 OCW1—Operational Control Word 1 Register                                        | 1-340 |

| 3.4.3.7 OCW2—Operational Control Word 2 Register                                        | 1-340 |

| 3.4.3.8 OCW3—Operational Control Word 3 Register                                        | 1-342 |

| 3.4.3.9 ELCR1—Edge/Level Triggered Register                                             | 1-343 |

| 3.4.3.10 ELCR2—Edge/Level Triggered Register                                            | 1-343 |

| 3.4.4 X-BUS REGISTER DESCRIPTION                                                        | 1-343 |

| 3.4.4.1 RIRQ—Reset IRQ[12,1]                                                            | 1-344 |

| 3.4.4.2 CPERR—Coprocessor Error Register                                                | 1-344 |

| 3.4.5 NMI REGISTER DESCRIPTION                                                          | 1-344 |

| 3.4.5.1 NMISC—NMI Status and Control Register                                           | 1-345 |

| 3.4.5.2 NMIERTC—NMI Enable and Real Time Clock Address Register                         | 1-346 |

| 3.4.6 POWER MANAGEMENT REGISTER DESCRIPTION                                             |       |

| 3.4.6.1 APMC—Advanced Power Management Control Port                                     | 1-346 |

| 3.4.6.2 APMS—Advanced Power Management Status Port                                      | 1-347 |

|                                                                                         |       |

| CONTENTS                                       | PAGE  |

|------------------------------------------------|-------|

| .0 FUNCTIONAL DESCRIPTION                      | 1-347 |

| 4.1 Memory and I/O Address Map                 | 1-347 |

| 4.1.1 MEMORY ADDRESS MAP                       | 1-347 |

| 4.1.2 BIOS MEMORY SPACE                        | 1-349 |

| 4.1.3 VIDEO FRAME BUFFER                       | 1-349 |

| 4.1.4 I/O ACCESSES                             | 1-349 |

| 4.1.5 SMRAM: PROTECTED SMM MEMORY BLOCK        | 1-349 |

| 4.2 PSC/IB Link Interface                      | 1-350 |

| 4.3 Host CPU Interface                         | 1-350 |

| 4.3.1 HOST BUS SLAVE DEVICE                    | 1-350 |

| 4.3.2 L1 CACHE SUPPORT                         | 1-351 |

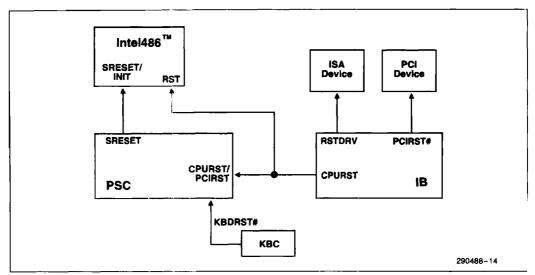

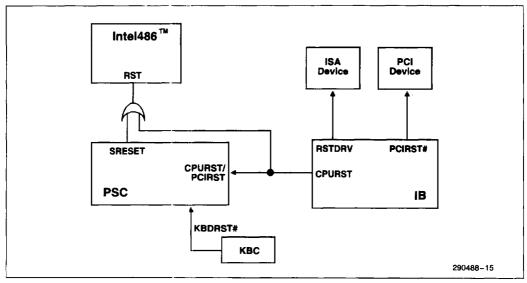

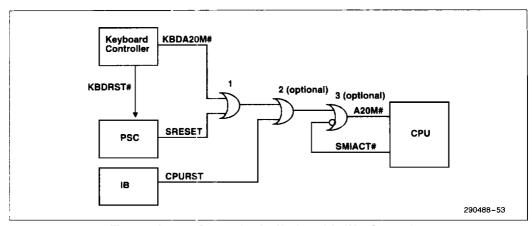

| 4.3.3 SOFT AND HARD RESETS                     | 1-351 |

| 4.3.4 KEYBOARD CONTROLLER (A20)                | 1-353 |

| 4.4 PCI Interface                              | 1-353 |

| 4.4.1 PCI BUS CYCLES SUPPORT                   | 1-354 |

| 4.4.2 HOST TO PCI CYCLES                       | 1-355 |

| 4.4.3 PCI CYCLE TERMINATIONS                   | 1-355 |

| 4.4.4 EXCLUSIVE CYCLES                         | 1-356 |

| 4.4.5 PARITY SUPPORT                           | 1-356 |

| 4.5 PCI Local Bus IDE                          | 1-356 |

| 4.6 ISA Interface                              | 1-358 |

| 4.7 X-Bus                                      | 1-359 |

| 4.7.1 COPROCESSOR ERROR FUNCTION               | 1-360 |

| 4.7.2 MOUSE FUNCTION                           | 1-360 |

| 4.8 System Arbitration                         | 1-360 |

| 4.8.1 SYSTEM ARBITRATION SCHEME                | 1-360 |

| 4.9 DMA Controller                             | 1-361 |

| 4.10 Interval Timer                            |       |

| 4.11 Interrupt Controller                      | 1-362 |

| 4.11.1 PROGRAMMING THE INTERRUPT CONTROLLER    | 1-363 |

| 4.11.2 EDGE AND LEVEL INTERRUPT TRIGGERED MODE | 1-363 |

| 4.11.3 INTERRUPT STEERING                      | 1-364 |

| 4.12 L2 Cache                                  | 1-364 |

| 4.12.1 L2 CACHE SIZES/PERFORMANCE              | 1-364 |

| A 10 2 CACHE OPERATIONS                        |       |

| CONTENTS                                        | PAGE  |

|-------------------------------------------------|-------|

| 4.12.3 CACHE CONSISTENCY                        | 1-365 |

| 4.12.4 INITIALIZING THE L2 CACHE                | 1-366 |

| 4.12.5 CACHE LINE DESCRIPTION                   | 1-366 |

| 4.12.6 L2 CACHE STRUCTURE                       | 1-366 |

| 4.13 DRAM Interface                             | 1-367 |

| 4.13.1 DRAM ADDRESS TRANSLATION                 | 1-368 |

| 4.13.2 DRAM STRUCTURE                           | 1-368 |

| 4.13.3 DRAM SIMM SIZE/DENSITY OPTIONS           | 1-370 |

| 4.13.4 DRAM PAGE MODE                           | 1-370 |

| 4.13.5 PROGRAMMABLE WAIT-STATES                 | 1-371 |

| 4.13.5.1 RAS Precharge                          | 1-371 |

| 4.13.5.2 CAS Read Time                          | 1-371 |

| 4.13.5.3 CAS Write Time                         | 1-371 |

| 4.13.5.4 MA Setup Time                          | 1-371 |

| 4.13.5.5 MA Hold Time                           |       |

| 4.13.6 DRAM PERFORMANCE                         | 1-371 |

| 4.14 Power Management                           | 1-372 |

| 4.14.1 SMM MODE                                 | 1-373 |

| 4.14.2 SMI SOURCES                              |       |

| 4.14.3 SMI (SMI#) AND INTERRUPT (INTR) ORDERING | 1-374 |

| 4.14.4 CLOCK CONTROL                            |       |

| 4.15 Clocks                                     | 1-375 |

| 5.0 DESIGN CONSIDERATIONS                       | 1-376 |

| 6.0 ELECTRICAL CHARACTERISTICS                  |       |

| 6.1 Maximum Ratings                             | 1-376 |

| 6.2 PSC and IB DC Characteristics               | 1-377 |

| 6.3 IB AC Characteristics                       | 1-379 |

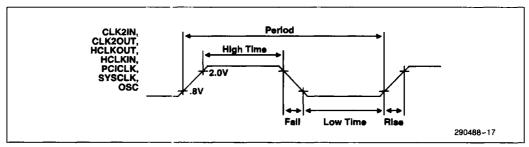

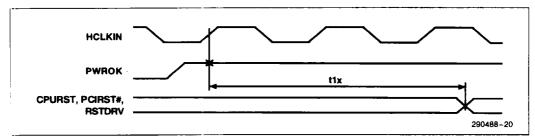

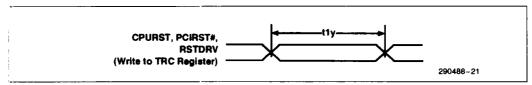

| 6.3.1 CLOCK/RESET TIMINGS                       | 1-379 |

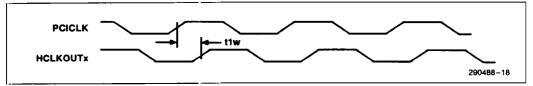

| 6.3.2 PSC/IB LINK INTERFACE TIMINGS             | 1-380 |

| 6.3.3 SYSTEM POWER MANAGEMENT TIMINGS           | 1-380 |

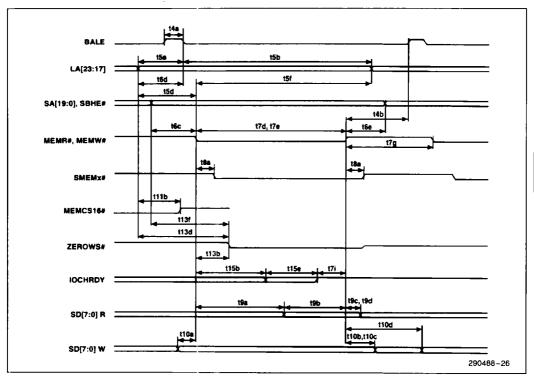

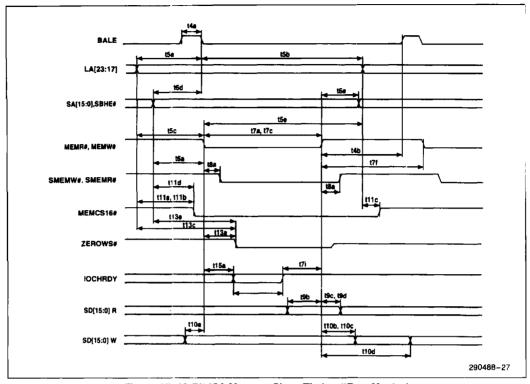

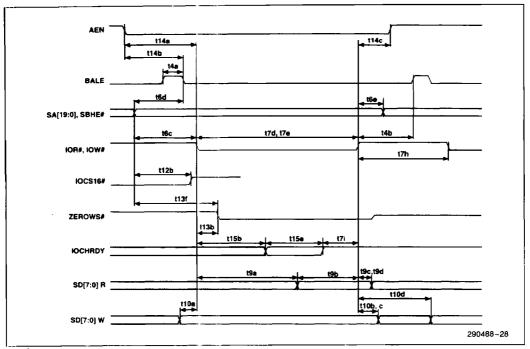

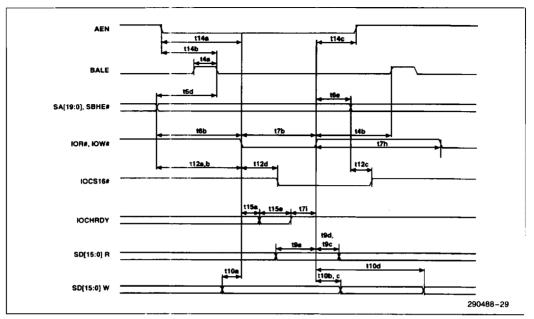

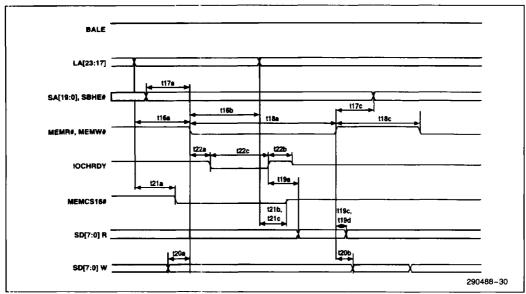

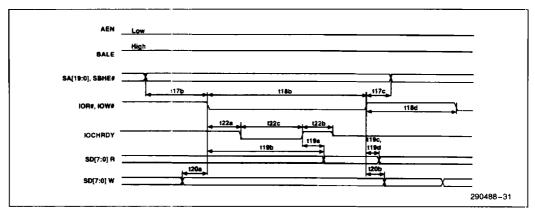

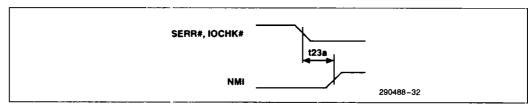

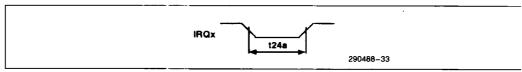

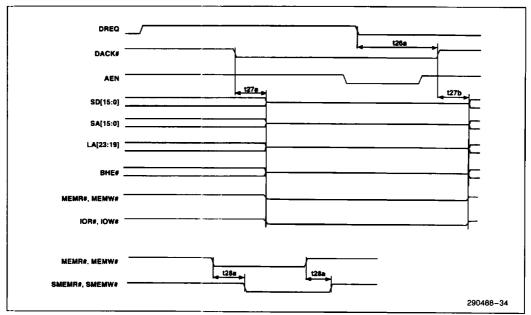

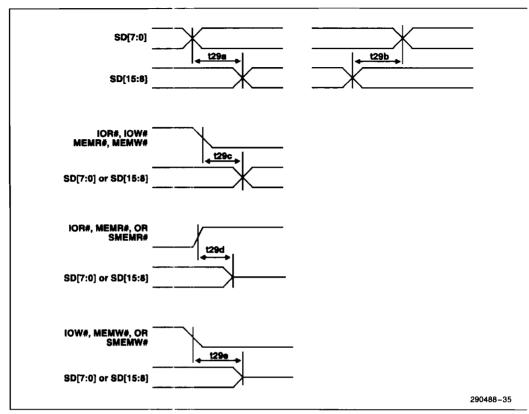

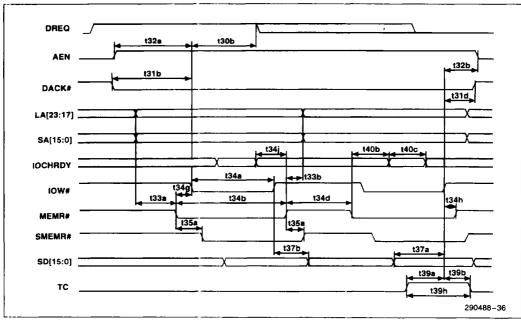

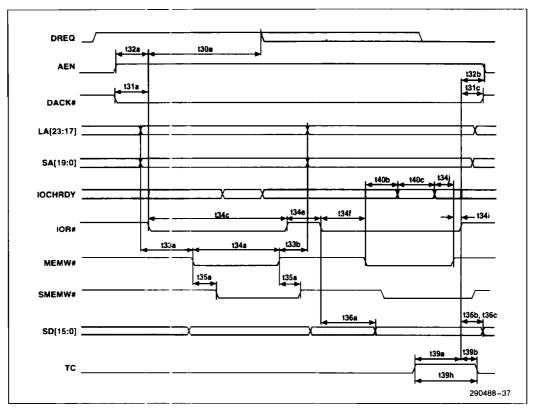

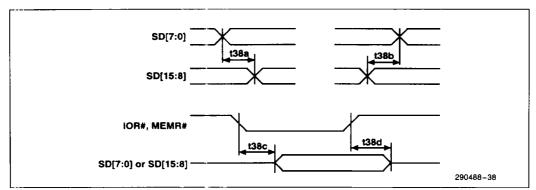

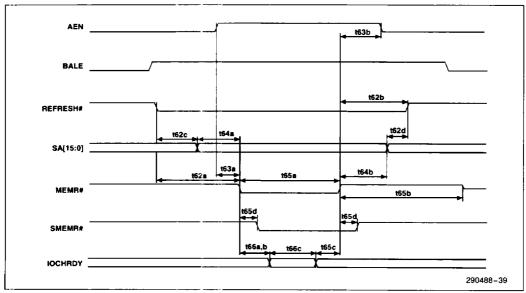

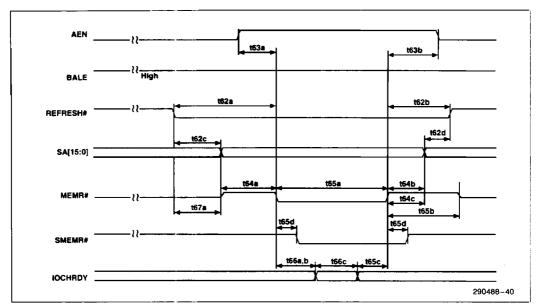

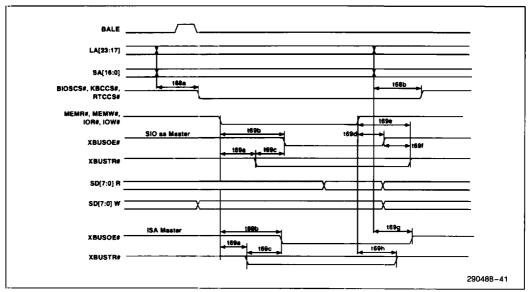

| 6.3.4 ISA BUS AND X-BUS TIMINGS                 | 1-381 |

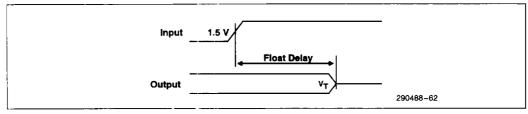

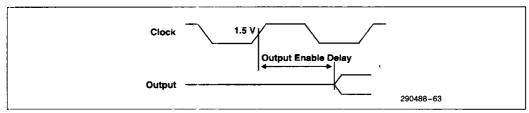

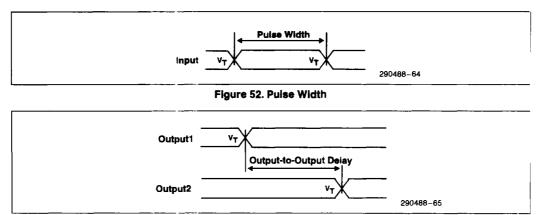

| 6.3.5 AC TEST LOADS                             | 1-390 |

| 6.3.6 AC TIMING WAVE FORMS                      | 1-390 |

| CONTENTS                           | PAGE  |

|------------------------------------|-------|

| 6.4 PSC AC Characteristics         | 1-407 |

| 6.4.1 HOST CLOCK TIMING            | 1-407 |

| 6.4.2 CPU INTERFACE TIMINGS        | 1-407 |

| 6.4.3 SECOND LEVEL CACHE TIMING    | 1-409 |

| 6.4.4 DRAM INTERFACE TIMING        | 1-409 |

| 6.4.5 PCI TIMING                   | 1-410 |

| 6.4.6 PSC/IB LINK INTERFACE TIMING |       |

| 6.4.7 PCI BUS IDE TIMING           | 1-411 |

| 6.4.8 AC TEST LOADS                | 1-411 |

| 7.0 IB AND PSC PACKAGE INFORMATION | 1-414 |

| 7.1 Thermal Characteristics        | 1-415 |

| 8.0 TESTABILITY                    |       |

| 8.1 PSC Testability                | 1-416 |

| 8.1.1 PSC TRI-STATE CONTROL        | 1-416 |

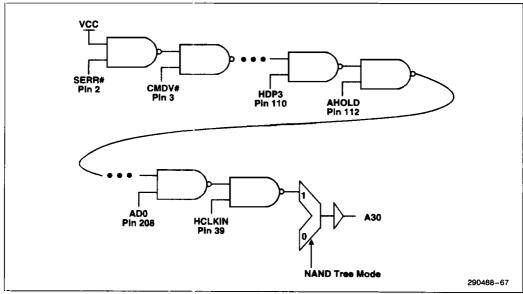

| 8.1.2 PSC NAND TREE                | 1-416 |

| 8.1.3 PSC NAND TREE DIAGRAM        | 1-423 |

| 8.2 IB Testability                 | 1-424 |

| 8.2.1 IB TRI-STATE                 | 1-424 |

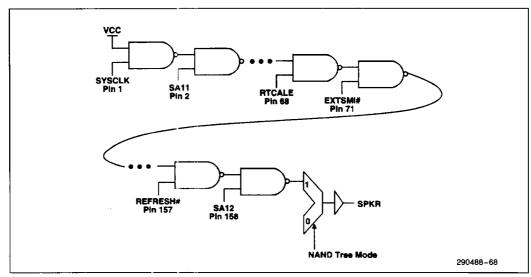

| 8.2.2 IB NAND TREE                 | 1-424 |

| 8.2.3 IB NAND TREE CELL ORDER      |       |

| 8.2.4 IB NAND TREE DIAGRAM         | 1-430 |

| A A DEVICION LICTORY               | 4 400 |

Figure 1. Example System Block Diagram

### 1.0 PINOUT INFORMATION

This section provides the PSC and IB pin assignment and package information. For each device, the pin assignments are listed in both alphabetical and numerical order.

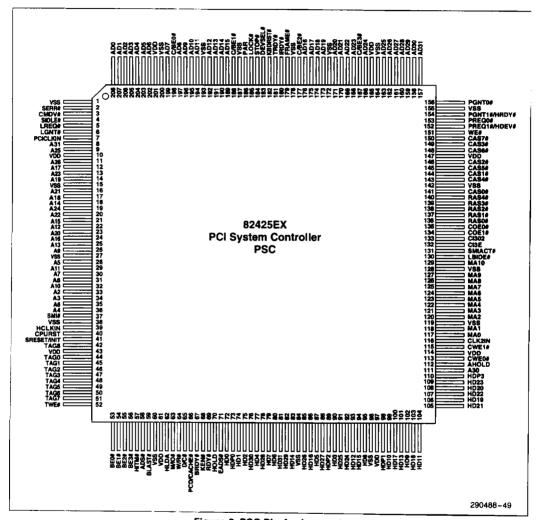

### 1.1 PSC Pin Assignment

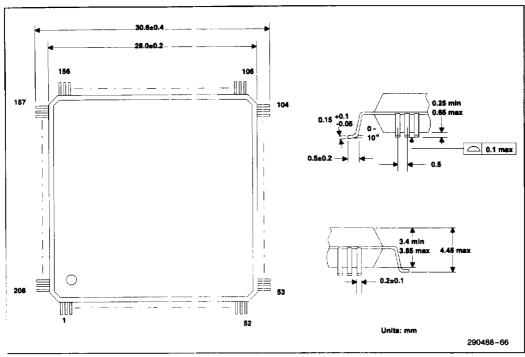

The PSC package is a 208-pin Quad Flatpack (QFP). Figure 2 shows the pin assignment on the package. Tables 1 and 2 list the pin assignments alphabetically and numerically, respectively.

Figure 2. PSC Pin Assignment

Table 1. Alphabetical PSC Pin Assignment List

| Pin Name   | Pin # | 1/0 |  |

|------------|-------|-----|--|

| A2         | 33    | 1/0 |  |

| А3         | 34    | 1/0 |  |

| A4         | 36    | 1/0 |  |

| A5         | 28    | 1/0 |  |

| A6         | 35    | 1/0 |  |

| <b>A</b> 7 | 30    | 1/0 |  |

| A8         | 31    | 1/0 |  |

| A9         | 26    | 1/0 |  |

| A10        | 32    | 1/0 |  |

| A11        | 29    | 1/0 |  |

| A12        | 22    | 1/0 |  |

| A13        | 25    | 1/0 |  |

| A14        | 18    | 1/0 |  |

| A15        | 21    | 1/0 |  |

| A16        | 24    | 1/0 |  |

| A17        | 12    | 1/0 |  |

| A18        | 17    | 1/0 |  |

| A19        | 14    | 1/0 |  |

| A20        | 23    | 1/0 |  |

| A21        | 16    | 1/0 |  |

| A22        | 20    | 1/0 |  |

| A23        | 13    | 1/0 |  |

| A24        | 19    | 1/0 |  |

| A25        | 9     | 1/0 |  |

| A26        | 11    | 1/0 |  |

| A30        | 111   | 1/0 |  |

| A31        | 8     | 1/0 |  |

| AD0        | 208   | 1/0 |  |

| AD1        | 207   | 1/0 |  |

| AD2        | 206   | 1/0 |  |

| AD3        | 205   | 1/0 |  |

| AD4        | 204   | 1/0 |  |

| Pin Name | Pin # | 1/0 |

|----------|-------|-----|

| AD5      | 203   | 1/0 |

| AD6      | 202   | 1/0 |

| AD7      | 199   | 1/0 |

| AD8      | 197   | 1/0 |

| AD9      | 196   | 1/0 |

| AD10     | 195   | 1/0 |

| AD11     | 194   | 1/0 |

| AD12     | 192   | 1/0 |

| AD13     | 191   | 1/0 |

| AD14     | 190   | 1/0 |

| AD15     | 189   | 1/0 |

| AD16     | 176   | 1/0 |

| AD17     | 175   | 1/0 |

| AD18     | 174   | 1/0 |

| AD19     | 173   | 1/0 |

| AD20     | 171   | 1/0 |

| AD21     | 170   | 1/0 |

| AD22     | 169   | 1/0 |

| AD23     | 168   | 1/0 |

| AD24     | 166   | 1/0 |

| AD25     | 163   | 1/0 |

| AD26     | 162   | 1/0 |

| AD27     | 161   | 1/0 |

| AD28     | 160   | 1/0 |

| AD29     | 159   | 1/0 |

| AD30     | 158   | 1/0 |

| AD31     | 157   | 1/0 |

| ADS#     | 58    | ı   |

| AHOLD    | 112   | 0   |

| BE0#     | 53    | 1/0 |

| BE1#     | 54    | 1/0 |

| BE2#     | 55    | 1/0 |

| Pin Name | Pin # | 1/0   |

|----------|-------|-------|

| BE3#     | 56    | 1/0   |

| BLAST#   | 59    |       |

| BRDY#    | 67    | 0     |

| C/BE0#   | 198   | 1/0   |

| C/BE1#   | 188   | 1/0   |

| C/BE2#   | 177   | 1/0   |

| C/BE3#   | 167   | 1/0   |

| CAS0#    | 141   | 0     |

| CAS1#    | 144   | 0     |

| CAS2#    | 146   | 0     |

| CAS3#    | 149   | 0     |

| CAS4#    | 143   | 0     |

| CAS5#    | 145   | 0     |

| CAS6#    | 148   | 0     |

| CAS7#    | 150   | 0     |

| CI3E     | 132   | 0     |

| Cl3O2    | 133   | 0     |

| CLK2IN   | 116   | _     |

| CMDV#    | 3     | 1/0   |

| COE0#    | 135   | 0     |

| COE1#    | 134   | 0     |

| CPURST   | 40    | 1     |

| CWE0#    | 113   | 0     |

| CWE1#    | 115   | 0     |

| D/C#     | 65    | ı     |

| DEVSEL#  | 183   | s/t/s |

| EADS#    | 71    | 0     |

| FRAME#   | 179   | s/t/s |

| HCLKIN   | 39    | 1     |

| HD0      | 72    | 1/0   |

| HD1      | 74    | 1/0   |

| HD2      | 75    | 1/0   |

| Pin Name | Pin # | 1/0 |

|----------|-------|-----|

| HD3      | 90    | 9   |

| HD4      | 77    | 1/0 |

| HD5      | 87    | 9   |

| HD6      | 80    | 9   |

| HD7      | 79    | 9   |

| HD8      | 95    | 9   |

| HD9      | 102   | 9   |

| HD10     | 99    | 1/0 |

| HD11     | 104   | 9   |

| HD12     | 93    | 10  |

| HD13     | 101   | 1/0 |

| HD14     | 83    | 1/0 |

| HD15     | 94    | 1/0 |

| HD16     | 86    | 1/0 |

| HD17     | 100   | 1/0 |

| HD18     | 103   | 20  |

| HD19     | 106   | 1/0 |

| HD20     | 108   | 9   |

| HD21     | 105   | 1/0 |

| HD22     | 107   | 1/0 |

| HD23     | 109   | 1/0 |

| HD24     | 92    | 1/0 |

| HD25     | 91    | 1/0 |

| HD26     | 85    | 1/0 |

| HD27     | 88    | 1/0 |

| HD28     | 78    | 1/0 |

| HD29     | 82    | 1/0 |

| HD30     | 76    | 1/0 |

| HD31     | 81    | 1/0 |

| HDP0     | 73    | 1/0 |

| HDP1     | 98    | 1/0 |

| HDP2     | 89    | 1/0 |

Table 1. Alphabetical PSC Pin Assignment List (Continued)

| Pin Name | Pin # | 1/0   |  |

|----------|-------|-------|--|

| HDP3     | 110   | 1/0   |  |

| HITM#    | 57    | ı     |  |

| HLDA     | 62    | 1     |  |

| HOLD     | 70    | 0     |  |

| IRDY#    | 180   | s/t/s |  |

| KBDRST#  | 182   | 1     |  |

| KEN#     | 68    | 0     |  |

| LBIDE#   | 130   | 0     |  |

| LGNT#    | 6     | 0     |  |

| LOCK#    | 185   |       |  |

| LREQ#    | 5     | 1     |  |

| M/IO#    | 63    | 1/0   |  |

| MA0      | 117   | 0     |  |

| MA1      | 118   | 0     |  |

| MA2      | 120   | 0     |  |

| МАЗ      | 121   | 0     |  |

| MA4      | 122   | 0     |  |

| MA5      | 123   | 0     |  |

| MA6      | 124   | 0     |  |

| MA7      | 125   | 0     |  |

| MA8      | 126   | 0     |  |

| Pin Name       | Pin # | 1/0   | Pin Name | Pin # | 1/0 |   | Pin Name        |

|----------------|-------|-------|----------|-------|-----|---|-----------------|

| HDP3           | 110   | 1/0   | MA9      | 127   | 0   |   | SMIACT#         |

| HI <b>TM</b> # | 57    | ı     | MA10     | 129   | 0   |   | SRESET          |

| HLDA           | 62    | 1     | PAR      | 186   | 1/0 |   | INIT            |

| HOLD           | 70    | 0     | PCD/     | 66    | ı   |   | STOP#           |

| IRDY#          | 180   | s/t/s | CACHE    |       |     |   | TAG0            |

| KBDRST#        | 182   | 1     | PCICLKIN | 7     | 1   |   | TAG1            |

| KEN#           | 68    | 0     | PGNT0#   | 156   | 0   |   | TAG2            |

| LBIDE#         | 130   | 0     | PGNT1#/  | 154   | 1/0 |   | TAG3            |

| _GNT#          | 6     | 0     | HRDY#    |       |     |   | TAG4            |

| LOCK#          | 185   | ı     | PREQ0#   | 153   | 1   |   | TAG5            |

| _REQ#          | 5     | 1     | PREQ1#/  | 152   | _   |   | TAG6            |

| M/IO#          | 63    | 1/0   | HDEV#    |       |     |   | TAG7            |

| MA0            | 117   | 0     | RAS0#    | 136   | 0   |   | TAG8            |

| MA1            | 118   | 0     | RAS1#    | 137   | 0   |   | TRDY#           |

| MA2            | 120   | 0     | RAS2#    | 138   | 0   |   | TWE#            |

| MA3            | 121   | 0     | RAS3#    | 139   | 0   |   | V <sub>DD</sub> |

| MA4            | 122   | 0     | RAS4#    | 140   | 0   | ľ | V <sub>DD</sub> |

| MA5            | 123   | 0     | RDY#     | 69    | 0   |   | V <sub>DD</sub> |

| MA6            | 124   | 0     | SERR#    | 2     | OD  | ľ | V <sub>DD</sub> |

| MA7            | 125   | 0     | SIDLE#   | 4     | 1/0 | Ì | V <sub>DD</sub> |

| MA8            | 126   | 0     | SMI#     | 37    | 1   |   | V <sub>DD</sub> |

|                |       |       |          |       |     | L |                 |

| Pin Name        | Pin # | 1/0   |

|-----------------|-------|-------|

| SMIACT#         | 131   | 1     |

| SRESET/<br>INIT | 41    | 0     |

| STOP#           | 184   | s/t/s |

| TAG0            | 44    | 1/0   |

| TAG1            | 45    | 1/0   |

| TAG2            | 46    | 1/0   |

| TAG3            | 47    | 1/0   |

| TAG4            | 48    | 1/0   |

| TAG5            | 49    | 1/0   |

| TAG6            | 50    | 1/0   |

| TAG7            | 51    | 1/0   |

| TAG8            | 42    | 1/0   |

| TRDY#           | 181   | s/t/s |

| TWE#            | 52    | 0     |

| $V_{DD}$        | 10    | ٧     |

| $V_{DD}$        | 43    | V     |

| V <sub>DD</sub> | 61    | V     |

| $V_{DD}$        | 97    | ٧     |

| $V_{DD}$        | 147   | ٧     |

| Vnn             | 114   | V     |

| Pin Name          | Pin # | 1/0 |

|-------------------|-------|-----|

| V <sub>DD</sub>   | 165   | ٧   |

| $V_{DD}$          | 201   | V   |

| V <sub>SS</sub>   | 1     | ٧   |

| V <sub>SS</sub>   | 15    | ٧   |

| V <sub>SS</sub>   | 27    | V   |

| V <sub>SS</sub> _ | 38    | ٧   |

| V <sub>SS</sub>   | 60    | V   |

| V <sub>SS</sub>   | 84    | ٧   |

| V <sub>SS</sub>   | 96    | V   |

| V <sub>SS</sub>   | 119   | V   |

| V <sub>SS</sub>   | 128   | V   |

| V <sub>SS</sub>   | 142   | V   |

| V <sub>SS</sub>   | 155   | V   |

| V <sub>SS</sub>   | 164   | ٧   |

| V <sub>SS</sub>   | 172   | ٧   |

| V <sub>SS</sub>   | 178   | V   |

| $V_{SS}$          | 187   | V   |

| V <sub>SS</sub>   | 193   | V   |

| V <sub>SS</sub>   | 200   | V   |

| WE#               | 151   | 0   |

| W/R#              | 64    | 1/0 |

Table 2. Numerical PSC Pin Assignment List

| Pin Name          | Pin # | 1/0 |

|-------------------|-------|-----|

| Vss               | 1     | V   |

| SERR#             | 2     | OD  |

| CMDV#             | 3     | 1/0 |

| SIDLE#            | 4     | 1/0 |

| LREQ#             | 5     | 1   |

| _GNT#             | 6     | 0   |

| PCICLKIN          | 7     | 1   |

| A31               | 8     | 1/0 |

| A25               | 9     | 1/0 |

| `v <sub>D</sub> D | 10    | ٧   |

| . <u>426</u>      | 11    | 1/0 |

| <u>.</u> 417      | 12    | 1/0 |

| .A23              | 13    | 1/0 |

| . <b>∆1</b> 9     | 14    | 1/0 |

| 'vss              | 15    | V   |

| A21               | 16    | 1/0 |

| A18               | 17    | 1/0 |

| A14               | 18    | 1/0 |

| A24               | 19    | 1/0 |

| A22               | 20    | 1/0 |

| A15               | 21    | 1/0 |

| A12               | 22    | 1/0 |

| A20               | 23    | 1/0 |

| A16               | 24    | 1/0 |

| A13               | 25    | 1/0 |

| А9                | 26    | 1/0 |

| ٧ <sub>SS</sub>   | 27    | ٧   |

| A5                | 28    | 1/0 |

| A11               | 29    | 1/0 |

| A7                | 30    | 1/0 |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| A8              | 31    | 1/0 |

| A10             | 32    | 1/0 |

| A2              | 33    | 1/0 |

| A3              | 34    | 1/0 |

| A6              | 35    | 1/0 |

| A4              | 36    | 1/0 |

| SMI#            | 37    | ı   |

| V <sub>SS</sub> | 38    | ٧   |

| HCLKIN          | 39    | ı   |

| CPURST          | 40    | ı   |

| SRESET/<br>INIT | 41    | 0   |

| TAG8            | 42    | 1/0 |

| $V_{DD}$        | 43    | ٧   |

| TAG0            | 44    | 1/0 |

| TAG1            | 45    | 1/0 |

| TAG2            | 46    | 1/0 |

| TAG3            | 47    | 1/0 |

| TAG4            | 48    | 1/0 |

| TAG5            | 49    | 1/0 |

| TAG6            | 50    | 1/0 |

| TAG7            | 51    | 1/0 |

| TWE#            | 52    | 0   |

| BE0#            | 53    | 1/0 |

| BE1#            | 54    | 1/0 |

| BE2#            | 55    | 1/0 |

| BE3#            | 56    | 1/0 |

| HITM#           | 57    | -   |

| ADS#            | 58    | _   |

| BLAST#          | 59    |     |

| V <sub>SS</sub> | 60    | V   |

| Pin Name        | Pin # | 1/0      |

|-----------------|-------|----------|

| $V_{DD}$        | 61    | ٧        |

| HLDA            | 62    | Ι        |

| M/IO#           | 63    | 1/0      |

| W/R#            | 64    | 1/0      |

| D/C#            | 65    | ı        |

| PCD/<br>CACHE#  | 66    | 1        |

| BRDY#           | 67    | 0        |

| KEN#            | 68    | 0        |

| RDY#            | 69    | 0        |

| HOLD            | 70    | 0        |

| EADS#           | 71    | 0        |

| HD0             | 72    | 1/0      |

| HDP0            | 73    | 1/0      |

| HD1             | 74    | 1/0      |

| HD2             | 75    | 1/0      |

| HD30            | 76    | 1/0      |

| HD4             | 77    | 1/0      |

| HD28            | 78    | 1/0      |

| HD7             | 79    | 1/0      |

| HD6             | 80    | 1/0      |

| HD31            | 81    | 1/0      |

| HD29            | 82    | 1/0      |

| HD14            | 83    | 1/0      |

| V <sub>SS</sub> | 84    | <b>V</b> |

| HD26            | 85    | 1/0      |

| HD16            | 86    | 1/0      |

| HD5             | 87    | 1/0      |

| HD27            | 88    | 1/0      |

| HDP2            | 89    | 1/0      |

| HD3             | 90    | 1/0      |

| Pin Name          | Pln # | 1/0      |

|-------------------|-------|----------|

| HD25              | 91    | 1/0      |

| HD24              | 92    | 1/0      |

| HD12              | 93    | 1/0      |

| HD15              | 94    | 1/0      |

| HD8               | 95    | 1/0      |

| V <sub>SS</sub>   | 96    | ٧        |

| $V_{DD}$          | 97    | <b>V</b> |

| HDP1              | 98    | 1/0      |

| HD10              | 99    | 1/0      |

| HD17              | 100   | 1/0      |

| HD13              | 101   | 1/0      |

| HD9               | 102   | 1/0      |

| HD18              | 103   | 1/0      |

| HD11              | 104   | 1/0      |

| HD21              | 105   | 1/0      |

| HD19              | 106   | 1/0      |

| HD22              | 107   | 1/0      |

| HD20              | 108   | 1/0      |

| HD23              | 109   | 1/0      |

| HDP3              | 110   | 1/0      |

| A30               | 111   | 1/0      |

| AHOLD             | 112   | 0        |

| CWE0#             | 113   | 0        |

| V <sub>DD</sub> _ | 114   | ٧        |

| CWE1#             | 115   | 0        |

| CLK2IN            | 116   | ı        |

| MA0               | 117   | 0        |

| MA1               | 118   | 0        |

| V <sub>SS</sub>   | 119   | V        |

| MA2               | 120   | 0        |

Table 2. Numerical PSC Pin Assignment List (Continued)

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| МАЗ             | 121   | 0   |

| MA4             | 122   | 0   |

| MA5             | 123   | 0   |

| MA6             | 124   | 0   |

| MA7             | 125   | 0   |

| MA8             | 126   | 0   |

| MA9             | 127   | 0   |

| V <sub>SS</sub> | 128   | ٧   |

| MA10            | 129   | 0   |

| LBIDE#          | 130   | 0   |

| SMIACT#         | 131   | ١   |

| C13E            | 132   | 0   |

| C13O2           | 133   | 0   |

| COE1#           | 134   | 0   |

| COE0#           | 135   | 0   |

| RAS0#           | 136   | 0   |

| RAS1#           | 137   | 0   |

| RAS2#           | 138   | 0   |

| RAS3#           | 139   | 0   |

| RAS4#           | 140   | 0   |

| CAS0#           | 141   | 0   |

| V <sub>SS</sub> | 142   | ٧   |

| Pin Name         | Pin # | 1/0 |

|------------------|-------|-----|

| CAS4#            | 143   | 0   |

| CAS1#            | 144   | 0   |

| CAS5#            | 145   | 0   |

| CAS2#            | 146   | 0   |

| V <sub>DD</sub>  | 147   | ٧   |

| CAS6#            | 148   | 0   |

| CAS3#            | 149   | 0   |

| CAS7#            | 150   | 0   |

| WE#              | 151   | 0   |

| PREQ1#/<br>HDEV# | 152   | i   |

| PREQ0#           | 153   | 1   |

| PGNT1#/<br>HRDY# | 154   | 1/0 |

| V <sub>SS</sub>  | 155   | ٧   |

| PGNT0#           | 156   | 0   |

| AD31             | 157   | 1/0 |

| AD30             | 158   | 1/0 |

| AD29             | 159   | 1/0 |

| AD28             | 160   | 1/0 |

| AD27             | 161   | 1/0 |

| AD26             | 162   | 1/0 |

| AD25             | 163   | 1/0 |

| Vss              | 164   | V   |

| Pin Name         | Pin # | 1/0 | Pin Name        | Pin # | 1/0   |

|------------------|-------|-----|-----------------|-------|-------|

| CAS4#            | 143   | 0   | V <sub>DD</sub> | 165   | >     |

| CAS1#            | 144   | 0   | AD24            | 166   | 1/0   |

| CAS5#            | 145   | 0   | C/BE3#          | 167   | 1/0   |

| CAS2#            | 146   | 0   | AD23            | 168   | 1/0   |

| V <sub>DD</sub>  | 147   | ٧   | AD22            | 169   | 1/0   |

| CAS6#            | 148   | 0   | AD21            | 170   | 1/0   |

| CAS3#            | 149   | 0   | AD20            | 171   | 1/0   |

| CAS7#            | 150   | 0   | V <sub>SS</sub> | 172   | V     |

| WE#              | 151   | 0   | AD19            | 173   | 1/0   |

| PREQ1#/<br>HDEV# | 152   | ŧ   | AD18            | 174   | 1/0   |

| PREQ0#           | 153   | ı   | AD17            | 175   | 1/0   |

| PGNT1#/          | 154   | 1/0 | AD16            | 176   | 1/0   |

| HRDY#            |       |     | C/BE2#          | 177   | 1/0   |

| V <sub>SS</sub>  | 155   | ۷   | V <sub>SS</sub> | 178   | V     |

| PGNT0#           | 156   | 0   | FRAME#          | 179   | s/t/s |

| AD31             | 157   | 1/0 | IRDY#           | 180   | s/t/s |

| AD30             | 158   | 1/0 | TRDY#           | 181   | s/t/s |

| AD29             | 159   | 1/0 | KBDRST#         | 182   | 1     |

| AD28             | 160   | 1/0 | DEVSEL#         | 183   | s/t/s |

| AD27             | 161   | 1/0 | STOP#           | 184   | s/t/s |

| AD26             | 162   | 1/0 | -               |       |       |

| AD25             | 163   | 1/0 | LOCK#           | 185   | ı     |

| V <sub>SS</sub>  | 164   | V   | PAR             | 186   | 1/0   |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| V <sub>SS</sub> | 187   | ٧   |

| C/BE1#          | 188   | 1/0 |

| AD15            | 189   | 1/0 |

| AD14            | 190   | 1/0 |

| AD13            | 191   | 1/0 |

| AD12            | 192   | 1/0 |

| $V_{SS}$        | 193   | ٧   |

| AD11            | 194   | 1/0 |

| AD10            | 195   | 1/0 |

| AD9             | 196   | 1/0 |

| AD8             | 197   | 1/0 |

| C/BE0#          | 198   | 1/0 |

| AD7             | 199   | 1/0 |

| V <sub>SS</sub> | 200   | ٧   |

| $V_{DD}$        | 201   | ٧   |

| AD6             | 202   | 1/0 |

| AD5             | 203   | 1/0 |

| AD4             | 204   | 1/0 |

| AD3             | 205   | 1/0 |

| AD2             | 206   | 1/0 |

| AD1             | 207   | 1/0 |

| AD0             | 208   | 1/0 |

### 1.2 IB Pin Assignment

The IB package is a 160-pin Quad Flatpack (QFP). Figure 3 shows the package pin assignment. Table 3 and Table 4 list the pin assignment alphabetically and numerically, respectively.

Figure 3. IB Pin Assignment

Table 3. Alphabetical IB Pin Assignment List

| Pin Name   | Pin # | 1/0 |

|------------|-------|-----|

| A2         | 86    | 1/0 |

| A3         | 85    | 1/0 |

| A4         | 87    | 1/0 |

| A5         | 94    | 1/0 |

| A6         | 88    | 1/0 |

| <b>A</b> 7 | 92    | 1/0 |

| A8         | 91    | 1/0 |

| A9         | 95    | 1/0 |

| A10        | 89    | 1/0 |

| A11        | 93    | 1/0 |

| A12        | 98    | 1/0 |

| A13        | 96    | 1/0 |

| A14        | 102   | 1/0 |

| A15        | 101   | 1/0 |

| A16        | 97    | 1/0 |

| A17        | 103   | 1/0 |

| AEN        | 139   | 0   |

| BALE       | 18    | 0   |

| BIOSCS#    | 66    | 0   |

| CLK2IN     | 108   | -   |

| CLK2OUT    | 109   | 0   |

| CMDV#      | 107   | 10  |

| CPURST     | 79    | 0   |

| DACK0#     | 41    | 0   |

| DACK1#     | 153   | 0   |

| DACK2#     | 14    | 0   |

| DACK3#     | 148   | 0   |

| DACK5#     | 45    | 0   |

| DACK6#     | 51    | 0   |

| DACK7#     | 55    | 0   |

| Pin Name | Pin # | 1/0 |

|----------|-------|-----|

| DREQ0    | 43    | -   |

| DREQ1    | 155   | _   |

| DREQ2    | 131   | _   |

| DREQ3    | 151   | -   |

| DREQ5    | 48    | _   |

| DREQ6    | 53    | 1   |

| DREQ7    | 57    | Ι   |

| EXTSMI#  | 71    | IS  |

| FERR#    | 75    | _   |

| HCLKIN   | 83    | _   |

| HCLKOUT1 | 82    | 0   |

| HCLKOUT2 | 81    | 0   |

| IGNNE#   | 76    | 0   |

| INTR     | 73    | 0   |

| IOCHK#   | 123   | -1  |

| IOCHRDY  | 137   | 1/0 |

| IOCS16#  | 28    | -1  |

| IOR#     | 146   | 1/0 |

| IOW#     | 144   | 1/0 |

| IRQ1     | 119   | - 1 |

| IRQ3     | 12    | I   |

| IRQ4     | 9     | - 1 |

| IRQ5     | 7     | -   |

| IRQ6     | 5     | 1   |

| IRQ7     | 3     | 1   |

| IRQ8#    | 63    | ı   |

| IRQ9     | 127   | 1   |

| IRQ10    | 30    | ı   |

| IRQ11    | 32    | 1   |

| IRQ12/M  | 34    | 1   |

| Pin #    | 1/0                                                                                                         |

|----------|-------------------------------------------------------------------------------------------------------------|

|          | 1                                                                                                           |

|          | <u> </u>                                                                                                    |

| <u> </u> | 0                                                                                                           |

|          | 1/0                                                                                                         |

|          | 1/0                                                                                                         |

|          | 10                                                                                                          |

|          | $\vdash$                                                                                                    |

|          | 1/0                                                                                                         |

|          | 1/0                                                                                                         |

|          | 1/0                                                                                                         |

| 29       | 1/0                                                                                                         |

| 104      | 1                                                                                                           |

| 105      | 0                                                                                                           |

| 25       | 1/0                                                                                                         |

| 44       | 1/0                                                                                                         |

| 47       | 1/0                                                                                                         |

| 77       | 0                                                                                                           |

| 99       |                                                                                                             |

| 112      | 0                                                                                                           |

| 113      | 0                                                                                                           |

| 111      | 0                                                                                                           |

| 118      | +                                                                                                           |

| 117      | 1                                                                                                           |

| 114      | IS                                                                                                          |

| 157      | 1/0                                                                                                         |

| 124      | 0                                                                                                           |

| 68       | 0                                                                                                           |

| 67       | 0                                                                                                           |

| 24       | 1/0                                                                                                         |

| 23       | 1/0                                                                                                         |

| 22       | 1/0                                                                                                         |

|          | 105<br>25<br>44<br>47<br>77<br>99<br>112<br>113<br>111<br>118<br>117<br>114<br>157<br>124<br>68<br>67<br>24 |

| Pin # | 1/0                                                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21    | 1/0                                                                                                                                                                                    |

| 17    | 1/0                                                                                                                                                                                    |

| 15    | 1/0                                                                                                                                                                                    |

| 13    | 1/0                                                                                                                                                                                    |

| 11    | 1/0                                                                                                                                                                                    |

| 8     | 1/0                                                                                                                                                                                    |

| 6     | 1/0                                                                                                                                                                                    |

| 4     | 1/0                                                                                                                                                                                    |

| 2     | 1/0                                                                                                                                                                                    |

| 158   | 1/0                                                                                                                                                                                    |

| 156   | 1/0                                                                                                                                                                                    |

| 154   | 1/0                                                                                                                                                                                    |

| 152   | 1/0                                                                                                                                                                                    |

| 149   | 1/0                                                                                                                                                                                    |

| 147   | 1/0                                                                                                                                                                                    |

| 145   | 1/0                                                                                                                                                                                    |

| 143   | 1/0                                                                                                                                                                                    |

| 26    | 1/0                                                                                                                                                                                    |

| 136   | 1/0                                                                                                                                                                                    |

| 135   | 1/0                                                                                                                                                                                    |

| 133   | 1/0                                                                                                                                                                                    |

| 132   | 1/0                                                                                                                                                                                    |

| 129   | 1/0                                                                                                                                                                                    |

| 128   | 1/0                                                                                                                                                                                    |

| 126   | 1/0                                                                                                                                                                                    |

| 125   | 1/0                                                                                                                                                                                    |

| 49    | 1/0                                                                                                                                                                                    |

| 52    | 1/0                                                                                                                                                                                    |

| 54    | 1/0                                                                                                                                                                                    |

| 56    | 1/0                                                                                                                                                                                    |

|       | 21<br>17<br>15<br>13<br>11<br>8<br>6<br>4<br>2<br>158<br>156<br>154<br>152<br>149<br>147<br>145<br>143<br>26<br>136<br>135<br>133<br>132<br>129<br>128<br>126<br>125<br>49<br>52<br>54 |

Table 3. Alphabetical IB Pin Assignment List (Continued)

| Pin Name | Pin # | 1/0 |

|----------|-------|-----|

| SD12     | 58    | 1/0 |

| SD13     | 59    | 1/0 |

| SD14     | 61    | 1/0 |

| SD15     | 62    | 1/0 |

| SERR#    | 116   | 1   |

| SIDLE#   | 106   | 1/0 |

| SMEMR#   | 142   | 0   |

| SMEMW#   | 138   | 0   |

| SMI#     | 84    | 0   |

| SPKR     | 69    | 0   |

| Pin Name        | Pin #  | 1/0 |

|-----------------|--------|-----|

| FIII Nairie     | riii w | 17  |

| SRESET          | 78     | 1   |

| STPCLK#         | 72     | 0   |

| SYSCLK          | 1      | 0   |

| TC              | 16     | 0   |

| TESTIN#         | 115    | 1   |

| V <sub>DD</sub> | 20     | >   |

| $V_{DD}$        | 46     | >   |

| $V_{DD}$        | 74     | >   |

| $V_{DD}$        | 100    | >   |

| $V_{DD}$        | 121    | ٧   |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| $V_{DD}$        | 141   | >   |

| $V_{DD}$        | 160   | >   |

| V <sub>SS</sub> | 10    | ٧   |

| V <sub>SS</sub> | 19    | ٧   |

| V <sub>SS</sub> | 27    | ٧   |

| V <sub>SS</sub> | 38    | ٧   |

| V <sub>SS</sub> | 50    | ٧   |

| V <sub>SS</sub> | 60    | ٧   |

| V <sub>SS</sub> | 70    | ٧   |

| V <sub>SS</sub> | 80    | ٧   |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| VSS             | 90    | ٧   |

| V <sub>SS</sub> | 110   | >   |

| V <sub>SS</sub> | 120   | >   |

| V <sub>SS</sub> | 130   | >   |

| V <sub>SS</sub> | 140   | ٧   |

| V <sub>SS</sub> | 150   | >   |

| V <sub>SS</sub> | 159   | >   |

| XBUSOE#         | 65    | 0   |

| XBUSTR#         | 64    | 0   |

| ZEROWS#         | 134   | 1   |

|                 |       |     |

Table 4. Numerical IB Pin Assignment List

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| SYSCLK          | 1     | 0   |

| SA11            | 2     | 1/0 |

| IRQ7            | 3     | _   |

| SA10            | 4     | 1/0 |

| IRQ6            | 5     | _   |

| SA9             | 6     | 1/0 |

| IRQ5            | 7     | 1   |

| SA8             | 8     | 1/0 |

| IRQ4            | 9     | +   |

| V <sub>SS</sub> | 10    | ٧   |

| SA7             | 11    | 1/0 |

| IRQ3            | 12    |     |

| SA6             | 13    | 1/0 |

| DACK2#          | 14    | 0   |

| SA5             | 15    | 1/0 |

| TC              | 16    | 0   |

| SA4             | 17    | 1/0 |

| BALE            | 18    | 0   |

| $V_{SS}$        | 19    | ٧   |

| V <sub>DD</sub> | 20    | ٧   |

| SA3             | 21    | 1/0 |

| SA2             | 22    | 1/0 |

| SA1             | 23    | 1/0 |

| SA0             | 24    | 1/0 |

| MEMCS16#        | 25    | 1/0 |

| SBHE#           | 26    | 1/0 |

| V <sub>SS</sub> | 27    | ٧   |

| IOCS16#         | 28    |     |

| LA23            | 29    | 1/0 |

| IRQ10           | 30    | 1   |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| LA22            | 31    | 1/0 |

| IRQ11           | 32    | _   |

| LA21            | 33    | 1/0 |

| IRQ12/M         | 34    | ·   |

| LA20            | 35    | 1/0 |

| IRQ15           | 36    | 1   |

| LA19            | 37    | 1/0 |

| V <sub>SS</sub> | 38    | ٧   |

| IRQ14           | 39    | 1   |

| LA18            | 40    | 1/0 |

| DACK0#          | 41    | 0   |

| LA17            | 42    | 1/0 |

| DREQ0           | 43    | 1   |

| MEMR#           | 44    | 1/0 |

| DACK5#          | 45    | 0   |

| $V_{DD}$        | 46    | ٧   |

| MEMW#           | 47    | 1/0 |

| DREQ5           | 48    | ı   |

| SD8             | 49    | 1/0 |

| $V_{SS}$        | 50    | ٧   |

| DACK6#          | 51    | 0   |

| SD9             | 52    | 1/0 |

| DREQ6           | 53    | 1   |

| SD10            | 54    | 1/0 |

| DACK7#          | 55    | 0   |

| SD11            | 56    | 1/0 |

| DREQ7           | 57    | 1   |

| SD12            | 58    | 1/0 |

| SD13            | 59    | 1/0 |

| $V_{SS}$        | 60    | V   |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| SD14            | 61    | 1/0 |

| SD15            | 62    | 1/0 |

| IRQ8#           | 63    | 1   |

| XBUSTR#         | 64    | 0   |

| XBUSOE#         | 65    | 0   |

| BIOSCS#         | 66    | 0   |

| RTCCS#          | 67    | 0   |

| RTCALE          | 68    | 0   |

| SPKR            | 69    | 0   |

| V <sub>SS</sub> | 70    | ٧   |

| EXTSMI#         | 71    | 1   |

| STPCLK#         | 72    | 0   |

| INTR            | 73    | 0   |

| $V_{DD}$        | 74    | ٧   |

| FERR#           | 75    | ı   |

| IGNNE#          | 76    | 0   |

| NMI             | 77    | 0   |

| SRESET          | 78    | 1   |

| CPURST          | 79    | 0   |

| V <sub>SS</sub> | 80    | ٧   |

| HCLKOUT2        | 81    | 0   |

| HCLKOUT1        | 82    | 0   |

| HCLKIN          | 83    | I   |

| SMI#            | 84    | 0   |

| A3              | 85    | 1/0 |

| A2              | 86    | 1/0 |

| A4              | 87    | 1/0 |

| A6              | 88    | 1/0 |

| A10             | 89    | 1/0 |

| V <sub>SS</sub> | 90    | ٧   |

| Pin Name        | Pln # | 1/0 |

|-----------------|-------|-----|

| A8              | 91    | 1/0 |

| A7              | 92    | 1/0 |

| A11             | 93    | 1/0 |

| A5              | 94    | 1/0 |

| A9              | 95    | 1/0 |

| A13             | 96    | 1/0 |

| A16             | 97    | 1/0 |

| A12             | 98    | 1/0 |

| osc             | 99    | 1   |

| $V_{DD}$        | 100   | ٧   |

| A15             | 101   | 1/0 |

| A14             | 102   | 1/0 |

| A17             | 103   | 1/0 |

| LGNT#           | 104   | 1   |

| LREQ#           | 105   | 0   |

| SIDLE#          | 106   | 1/0 |

| CMDV#           | 107   | 1/0 |

| CLK2IN          | 108   | - 1 |

| CLK2OUT         | 109   | 0   |

| V <sub>SS</sub> | 110   | V   |

| PCIRST#         | 111   | 0   |

| PCICLK1         | 112   | 0   |

| PCICLK2         | 113   | 0   |

| PWROK           | 114   | I   |

| TESTIN#         | 115   | I   |

| SERR#           | 116   | ı   |

| PIRQ1#          | 117   | 1   |

| PIRQ0#          | 118   | I   |

| IRQ1            | 119   | I   |

| V <sub>SS</sub> | 120   | V   |

Table 4. Numerical IB Pin Assignment List (Continued)

| Pin Name | Pin # | 1/0 |

|----------|-------|-----|

| $V_{DD}$ | 121   | >   |

| KBCCS#   | 122   | 0   |

| IOCHK#   | 123   | 1   |

| RSTDRV   | 124   | 0   |

| SD7      | 125   | 1/0 |

| SD6      | 126   | 1/0 |

| IRQ9     | 127   | 1   |

| SD5      | 128   | 1/0 |

| SD4      | 129   | 1/0 |

| Vss      | 130   | ٧   |

| Pin Name        | Pin # | 1/0 |

|-----------------|-------|-----|

| DREQ2           | 131   | 1   |

| SD3             | 132   | 1/0 |

| SD2             | 133   | 1/0 |

| ZEROWS#         | 134   | ī   |

| SD1             | 135   | 1/0 |

| SD0             | 136   | 1/0 |

| IOCHRDY         | 137   | 1/0 |

| SMEMW#          | 138   | 0   |

| AEN             | 139   | 0   |

| V <sub>SS</sub> | 140   | ٧   |

| Pin Name | Pin # | 1/0 |

|----------|-------|-----|

| $V_{DD}$ | 141   | >   |

| SMEMR#   | 142   | 0   |

| SA19     | 143   | 1/0 |

| IOW#     | 144   | 1/0 |

| SA18     | 145   | 1/0 |

| IOR#     | 146   | 1/0 |

| SA17     | 147   | 1/0 |

| DACK3#   | 148   | 0   |

| SA16     | 149   | 1/0 |

| Vss      | 150   | V   |

| Pin Name                | Pin #      | 1/0      |

|-------------------------|------------|----------|

| DREQ3                   | 151        | Ι        |

| SA15                    | 152        | 1/0      |

| DACK1#                  | 153        | 0        |

| SA14                    | 154        | 1/0      |

| DREQ1                   | 155        | 1        |

| SA13                    | 156        | 1/0      |

| REFRESH#                | 157        | 1/0      |

| SA12                    | 158        | 1/0      |

| V <sub>SS</sub>         | 159        | ٧        |

| V <sub>DD</sub>         | 160        | ٧        |

| SA12<br>V <sub>SS</sub> | 158<br>159 | 1/C<br>V |

### 2.0 SIGNAL DESCRIPTION

This section contains a detailed description of each signal. The PSC signals are presented first, followed by the IB signals. The signals are arranged in functional groups according to their interface.

Note that the "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The following notations are used to describe signal types.

| Signal Type   | Description                                                                                                                                             |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | Input. Standard input-only signal.                                                                                                                      |

| IS            | Input. Schmitt Trigger                                                                                                                                  |

| 0             | <b>Totem Pole Output.</b> Standard active driver.                                                                                                       |

| OD            | Open Drain. Input/Output                                                                                                                                |

| 1/0           | Input/Output. Bi-directional, tri-state pin.                                                                                                            |

| <b>s/t</b> /s | Sustained Tri-state. Active low, tri-state signal with a pullup. Must be driven high for a clock before tri-state. Turn-around time must be maintained. |

### 2.1 PSC Signals

#### 2.1.1 HOST CPU INTERFACE SIGNALS (PSC)

| Name                  | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET/<br>INIT       | 0               | SOFT RESET/INITIALIZE: This is the soft reset output of the PSC and should be connected to the SRESET or INIT input to the CPU, depending on the CPU type.                                                                                                                                                                                                                                                                                |

| A[31:30,<br>26:2]     | 1/0             | HOST ADDRESS: A[31:30,26:2] are used as inputs to the PSC for CPU driven cycles. A[31:30,26:4] are outputs during Snoop cycles. Note that A[29:27] are not driven by the PSC. These signal lines must be externally driven low by either weak pull-down resistors or by driving these lines low when HLDA is active asserted. A[17:2] are also used for PSC/IB Link Interface transfers. These signals are tri-stated after a hard reset. |

| HD[31:0]              | 1/0             | <b>HOST DATA</b> : HD[31:0] are connected to the host CPU data bus. These signals are inputs after a hard reset.                                                                                                                                                                                                                                                                                                                          |

| HDP[3:0]              | I/O             | HOST DATA PARITY: HP[3:0] are bi-directional parity signals for the host data bus. These signals provide parity to the PSC during main memory read cycles. The PSC sends parity information to main memory during non-CPU main memory write cycles. These signals are tri-stated after a hard reset.                                                                                                                                      |

| BE[3:0]#              | 1/0             | BYTE ENABLE: The Byte Enable signals indicate active bytes during read and write cycles. These signals are tri-stated after a hard reset.                                                                                                                                                                                                                                                                                                 |

| M/IO#<br>D/C#<br>W/R# | I/O<br>I<br>I/O | BUS CYCLE DEFINITION (Memory/Input-Output, Data/Code, Write/Read: These signals define the Host Bus cycle. Note that special cycles are identified by BE[3:0] # and A[4:2]. These signals are tri-stated after a hard reset.                                                                                                                                                                                                              |

# 2.1.1 HOST CPU INTERFACE SIGNALS (PSC) (Continued)

| Name           | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCD/<br>CACHE# | ı    | PAGE CACHE DISABLE/CACHE: This multiplexed signal pin has two functions, depending on the type of CPU used. The PCD input signal, when asserted, indicates the current cycle can not be cached in the L2 cache during a cache line fill operation. When PCD is asserted the line will not be cached in L1 or L2.                                                                                                                                                                       |  |

|                |      | The <b>CACHE</b> # signal is active along with the first ADS# until the first RDY# or BRDY#. For line fills, the functionality of the CACHE# signal is identical to that of the PCD signal. During write-back cycles, CACHE# is always asserted at the beginning of the line write-back. The beginning of a write-back cycle is uniquely identified by active ADS#, W/R# and CACHE#. Beginning of the snoop write-back is identified by the ADS#, W/R#, CACHE# and HITM# being active. |  |

| ADS#           | ı    | ADDRESS STATUS: The ADS# input indicates that the bus cycle definition signals (M/IO#, D/C#, W/R#), BE[3:0]#, and A[31:30, 26:2] are available on their corresponding pins.                                                                                                                                                                                                                                                                                                            |  |

| RDY#           | 0    | <b>READY:</b> RDY # indicates that the current non-burst bus cycle is complete. This signal is negated after a hard reset.                                                                                                                                                                                                                                                                                                                                                             |  |

| BRDY#          | 0    | BURST READY: BRDY performs the same function during a burst cycle that RDY # performs during a non-burst cycle. This signal is negated after hard reset.                                                                                                                                                                                                                                                                                                                               |  |

| BLAST#         | 1    | BURST LAST: BLAST # indicates the end of a burst access for CPU-initiated cycles.                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| HOLD           | 0    | <b>HOLD:</b> The PSC asserts HOLD to the CPU to request ownership of the Host Bus. This signal is negated after a hard reset.                                                                                                                                                                                                                                                                                                                                                          |  |

| HLDA           | 1    | <b>HOLDA:</b> HLDA must be asserted by the CPU for the PSC to grant a new master on the PCI or ISA Buses. When HLDA is negated, the CPU is the Host Bus master and the PSC is the PCI Bus master. When HLDA is negated, the PSC is also the master on the PSC/IB link interface.                                                                                                                                                                                                       |  |

| AHOLD          | 0    | ADDRESS HOLD: The AHOLD output signal forces the CPU to float its address bus in the next clock. The PSC asserts this signal in preparation to perform a PSC/IB Interface transfer, when SRESET needs to be asserted, or upon Deturbo logic requests. This signal is negated after a hard reset.                                                                                                                                                                                       |  |

| EADS#          | 0    | <b>EXTERNAL ADDRESS:</b> EADS #, when asserted, indicates that an external address has been driven onto the CPU address lines. This address is used to perform an internal cache snoop cycle. This signal is negated after a hard reset.                                                                                                                                                                                                                                               |  |

| KEN#           | 0    | <b>CACHE ENABLE:</b> KEN #, when asserted, indicates whether the current cycle is cacheable in the CPU internal (L1 or primary) cache. This signal is negated after a hard reset.                                                                                                                                                                                                                                                                                                      |  |

| HITM#          | ı    | HIT MODIFIED: HITM# when asserted, indicates that a hit to a modified data cache has occurred during the snoop cycle. A pull-up is used to keep HITM# negated, when not used.                                                                                                                                                                                                                                                                                                          |  |

### 2.1.2 SECONDARY CACHE SIGNALS (PSC)

| Name          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CI3E<br>CI3O2 | 0    | CACHE INDEX SIGNALS: The Cache Index signals generate the burst sequence required by the CPU during secondary cache accesses. The PSC latches the starting burst address and internally generates subsequent dword addresses for the entire cache line.                                                                                                                                                                                                                                                                                                       |

|               |      | The CI3E signal is always used for cache index bit 3. When used in a bank interleaved configuration, CI3O2 is used to drive cache index bit 3 to the odd bank, and CI3E is used to drive bit 3 to the even bank. When used in non-interleaved mode (only one bank), CI3O2 is used to drive cache index bit 2.                                                                                                                                                                                                                                                 |

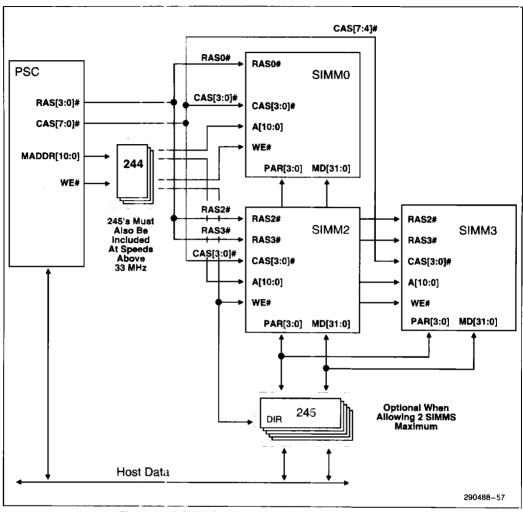

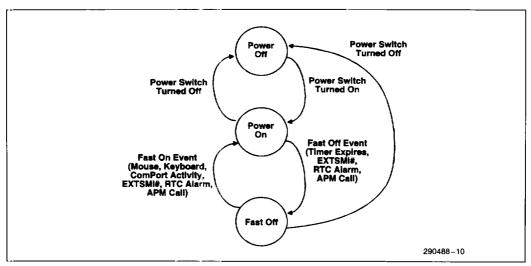

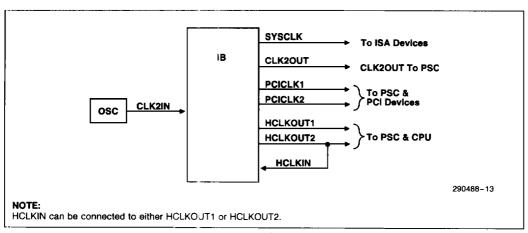

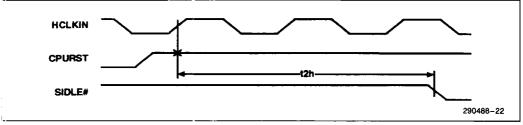

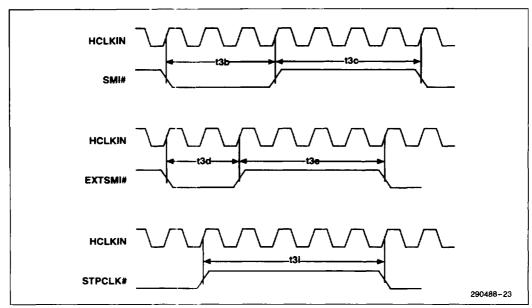

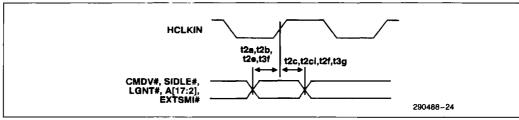

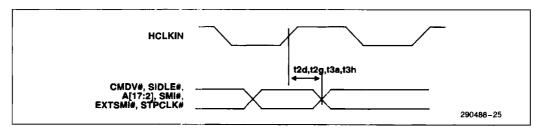

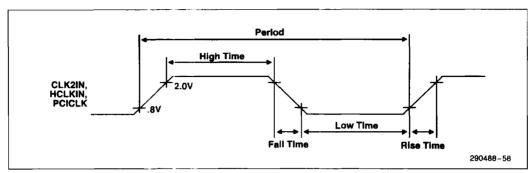

| CWE[1:0]#     | 0    | CACHE WRITE ENABLE: CWE[1:0] # are used to enable single writes and line fills to be written into the L2 cache. CWE0# is driven to all SRAMs in the even bank and CWE1# is driven to all SRAMs in the odd bank. The chip select signals of the SRAMs are asserted based on the byte enable signals and the W/R# signal, which are gated externally. Thus, only the bytes selected by the CPU are written. When programmed for non-interleaved mode, CWE[1:0]# mirror each other and are asserted to both banks. These signals are negated after a hard reset. |