## CHEETAH ET6000 SINGLE CHIP 486 NON CACHE SOLUTION

- \* 100% IBM PC/AT Compatible 1-Chip AT Solution

- \* Designed to work at 16, 20, 25, 33 and 50MHz on a 486SX/DX based system

- \* Fast Burst Mode Memory Manager-Burst Read and 0WS Write

- \* One blocks of non-cacheable memory regions

- \* Up to 64MB DRAM support with Page Mode

- \* Mixing DRAM configurations -256K, 1M and 4M devices

- \* Single ROM BIOS

- \* Shadow RAM option

- \* Software Programmable DRAM Wait States

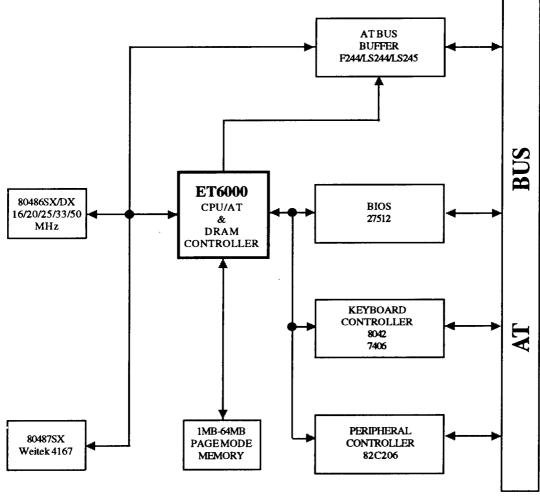

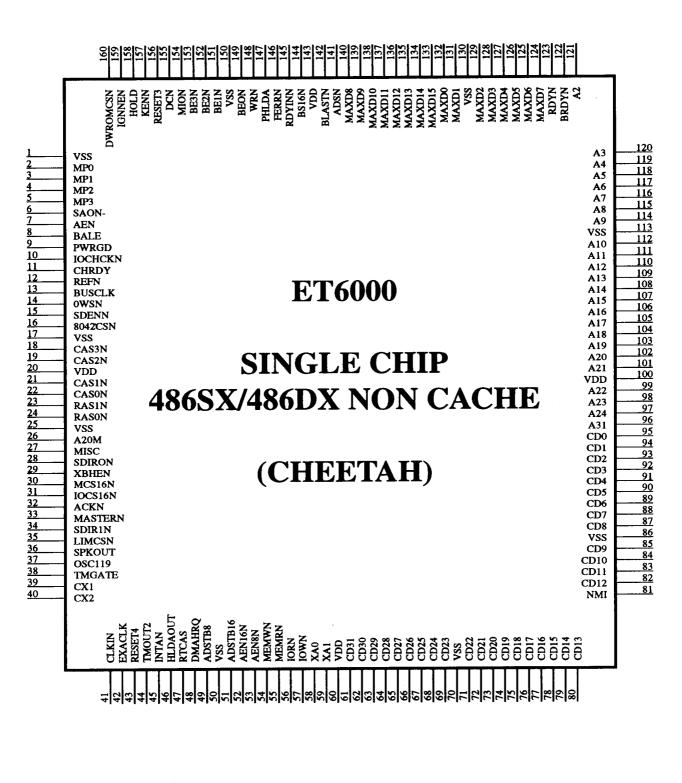

- \* Fast Reset and Gate A20 to Optimize OS/2

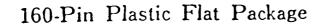

The CHEETAH single chip provides high integration and a low cost solution for a 16, 20, 25, 33, and 50MHz 486/AT based system design. The CHEETAH combined with 82C206 or compatible peripheral controller offers a 100% PC/AT compatible system using less than 10 components plus memory devices. The CHEE-TAH is available in the 160-pin Plastic Quad Flat-pack package. The 1.0u high speed, low power CMOS Technology allows for substantial stability when running at 25, 33, and 50MHz.

- \* Asynchronous AT Bus Clock Generation

- \* Support Intel 80487SX and Weitek 4167 Coprocessor without external PALs

- \* Concurrent Refresh and AT Refresh Option

- \* Hardware and Software Turbo Clock Switching

- \* Local Bus support

- \* Less than 10 components plus memory to implement an unique 486 system

- \* 1.0 Micron Low Power, High Speed CMOS Technology

- \* 160 Pin PQFP package

The CHEETAH includes 486 CPU control, AT Bus Control, Page Mode DRAM Control, Asynchronous AT Bus Clock Generation, data bus conversion logic which performs the conversion necessary between the 8 and 16-bit data paths, and Coprocessor Interface Logic to support Intel 487SX and Weitek 4167.

The Cheetah ET6000 is a highly integrated single chip AT optimized specifically for 486 CPUs. The emphasis of this chip is to reduce the cost requirements of 486 applications, without compromising performance. Fast bursting can be achieved with 80ns DRAMs.

The system cost is also minimized by allowing the use of slow DRAMs. The Burst Mode DRAM control is implemented to enhance system performance. The Cheetah is designed to be 100% compatible with the IBM PC/AT. With its optimized Burst and DRAM design, enhanced features like Shadow RAM BIOS, and Concurrent Refresh; a high performance/low cost 486/AT can be implemented.

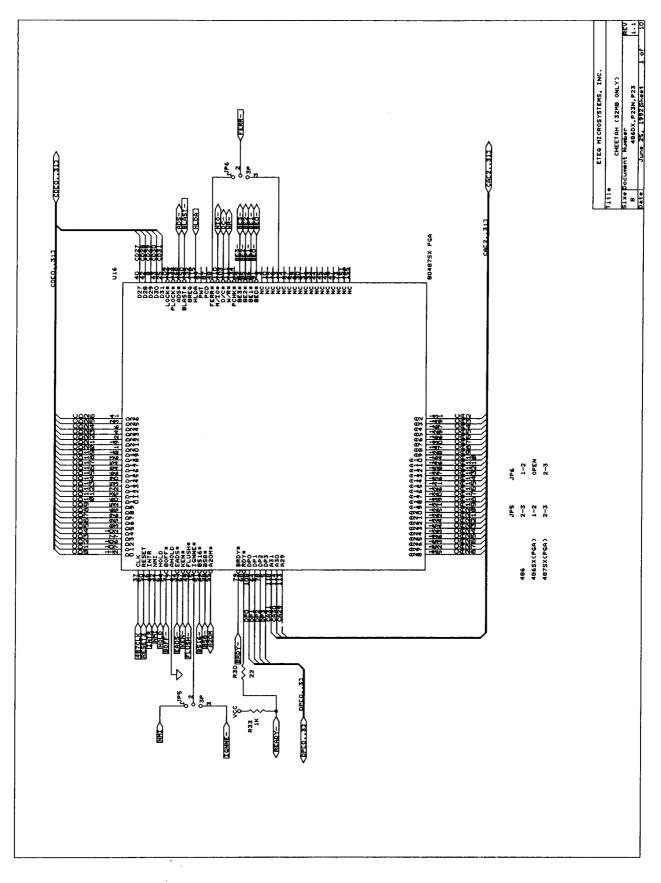

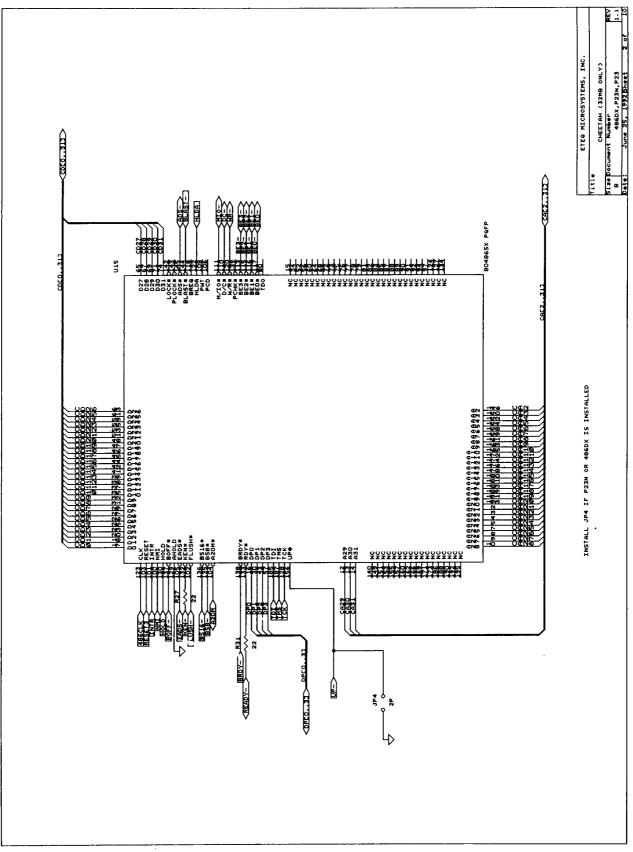

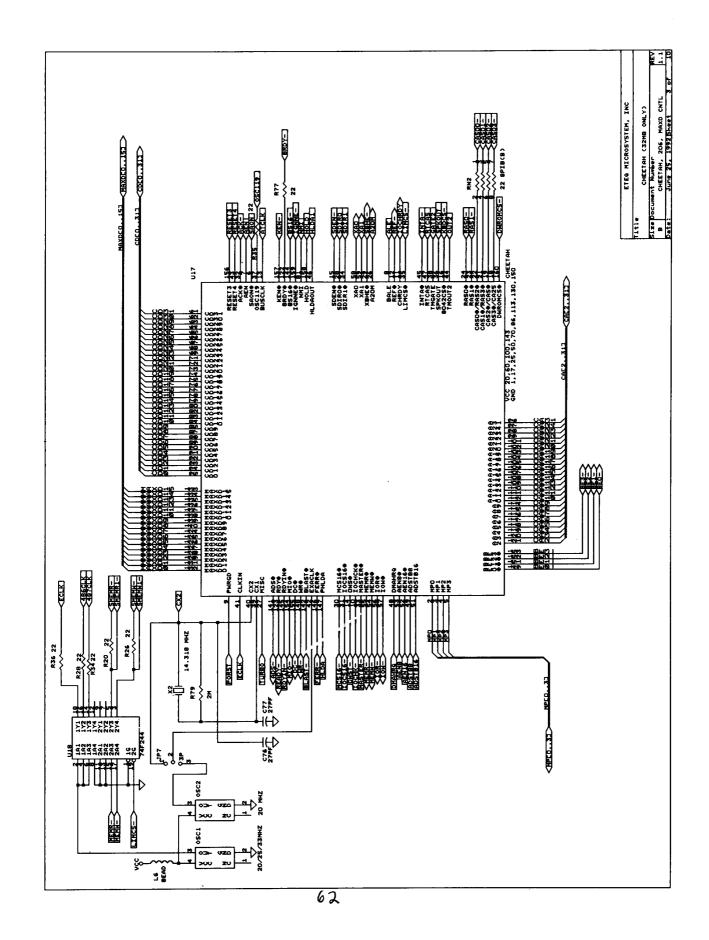

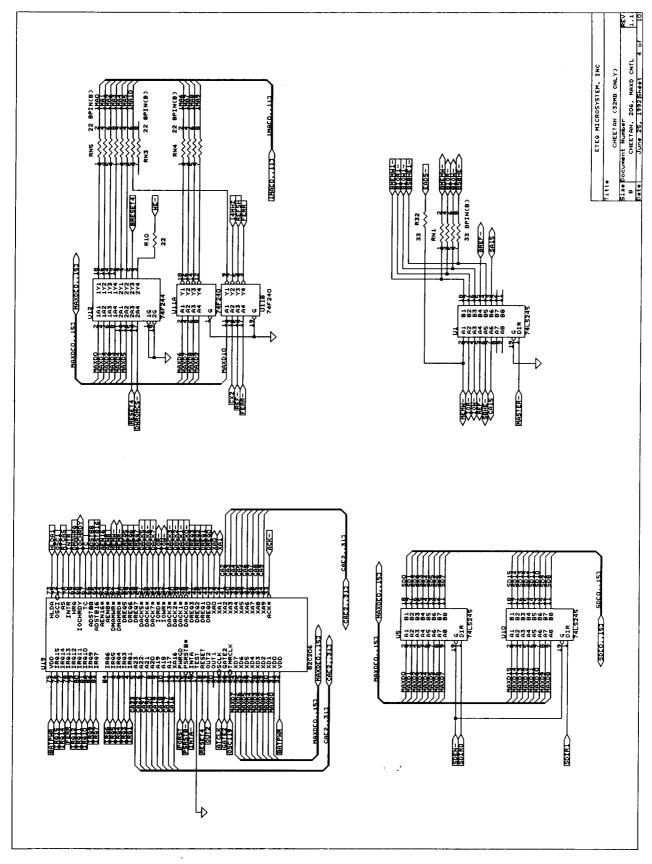

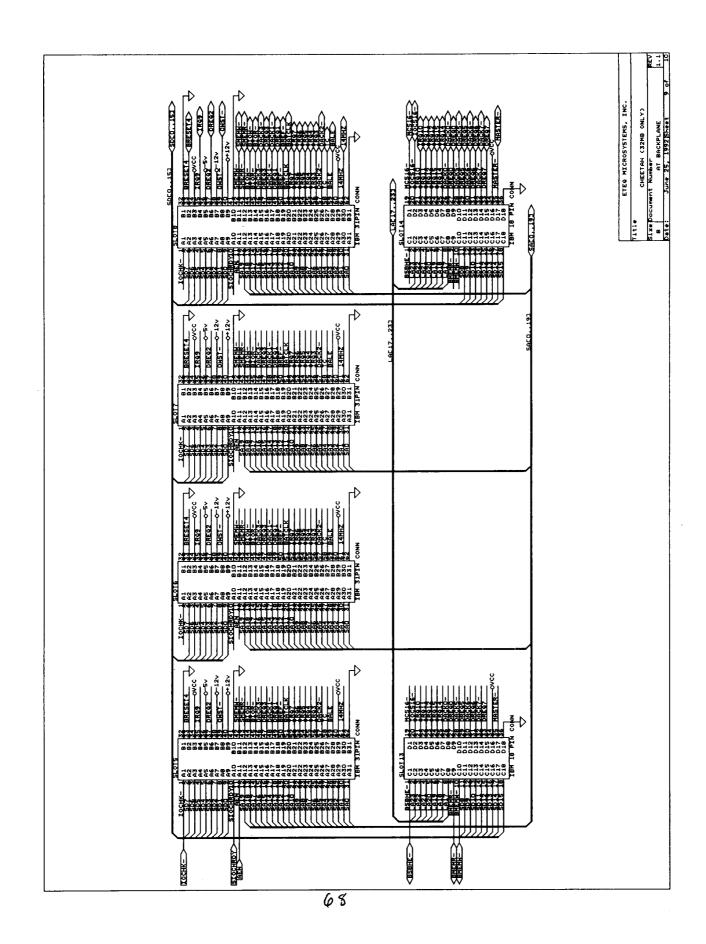

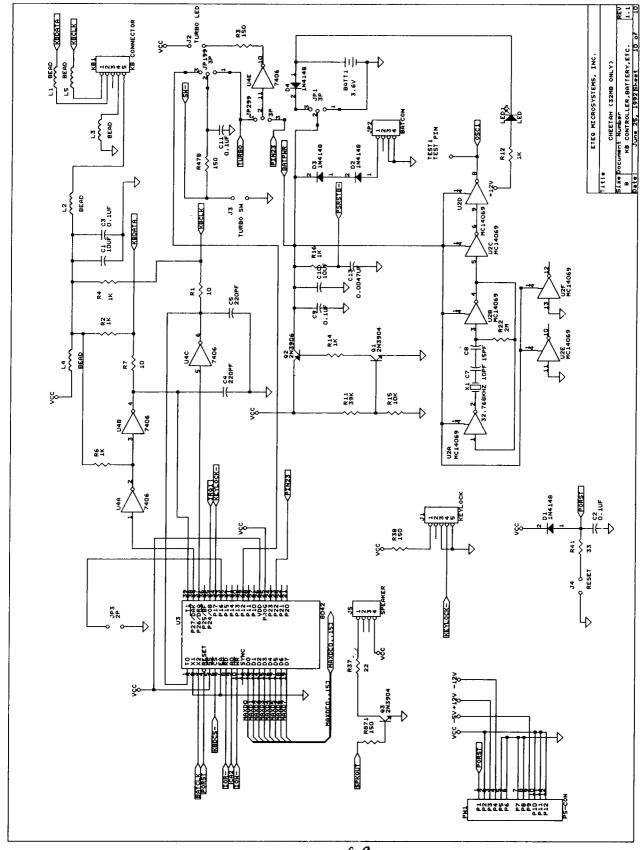

## **Cheetah 486 System Block Diagram**

Rev 0.1 April 1992 Cheetah-486

Confidential

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer

## **ET6000 SINGLE CHIP NON CACHE SOLUTION**

### 1.0 Overview

The CHEETAH provides an efficient cost/performance ratio as a high rate of integration in a 486 based, IBM PC/AT compatible system. It is implemented using 1.0u CMOS Technology and can run at 16MHz, 20MHz, 25MHz, 33MHz and 50MHz of CPU system clock

The ET6000 contains the Memory Controller, AT Bus Controller, CPU Controller, Data Buffer Circuitry. The Burst DRAM Controllers are the main factors affecting the performance/cost ratio of the system.

The ET6000 interfaces directly with the 80486 and implements the state machines required for controlling all bus accesses.

The ET6000 performs all of the data buffering functions required for a 486 based PC/AT compatible personal computer system. The chip routes the data to and from the CPU Data Bus (CD Bus), the MAXD Bus and the ISA Bus (SD Bus) under CPU control.

### **2.0 Functional Description**

The ET6000 has the following function modules:

- \* Reset and Shutdown Logic

- \* CPU and AT Bus Control

- \* Master, DMA and Refresh Arbitration Logic

- \* Port B Register and NMI Logic

- \* OS/2 Optimization Logic (Port 92)

- \* DRAM Controller Logic

- \* DMA and Master Access DRAM Logic

- \* Concurrent Refresh

- \* Shadow RAM

- \* Bus Interface between CD, MAXD and SD Buses

- \* Parity Generation and Checking Logic

- \* Numerical Coprocessor Interface Logic

- \* 14.318MHz and Counter Divided by 12

### 2.1 Reset and Shutdown

The system contains four different resets: RESET1 is derived from the power-good signal at the power supply. Some power supplies have glitches on this signal, therefore, a de-dounce circuit is required before tying it to the RESET1 pin. RESET1 will generate both RE-SET3 (CPU Reset) and RESET4 (System Reset) for power-on initialization. This can only happen at system power-on. RESET2 is generated from the Cheetah ; it triggers RESET3 to reset the CPU either to perform a shutdown or to activate a software reset. It can also be generated by programming the internal register. RE-SET3 is activated for power-on, shutdown and for changing the CPU from protect mode back to real mode. RESET4 is activated when the entire system is reset.

### **2.2 Clock Generation**

The ET6000 uses a single oscillator to generate the CPU clock. The oscillator input should be the same speed of the CPU. Depending upon the external crystal 14.318MHz frequency, the AT Bus Clock is divided by 2 as 7.1MHz. The AT Bus Clock can be changed by adding other external oscillator.

Rev 0.1 April 1992 Cheetah-486

3 —

### 2.3 CPU and AT Bus Control

The CPU starts a cycle by asserting ADS- if the M/IO-, D/C- and W/R- signals plus address code turn out to be a internal local memory, LOCRAM- will assert LOW and the memory cycle begins. Otherwise, an AT Bus cycle will begin. ROM cycle is considered to be an AT Bus cycle because it is fixed at 8MHz and does not vary in relation to the CPU's speed. Therefore, a 200 nanosecond access time ROM will be sufficient. Shadow RAM is supported to increase the performance. Since the CPU is running at its maximum speed, and the AT Bus is running at 8MHz, synchronization is required. DRAM does not need this handshaking because it is running at the same frequency as the CPU, thus, everything is synchronized. For the AT Bus cycle, ALE is where the AT Bus starts and the synchronized CPU ready is where it ends. This synchronization overhead can be significant when the AT Bus cycle is continuously accessed. The ET6000 synchronizes ALE with an option by switching the phase of the AT clock, not the signalitself, therefore, increasing the speed.

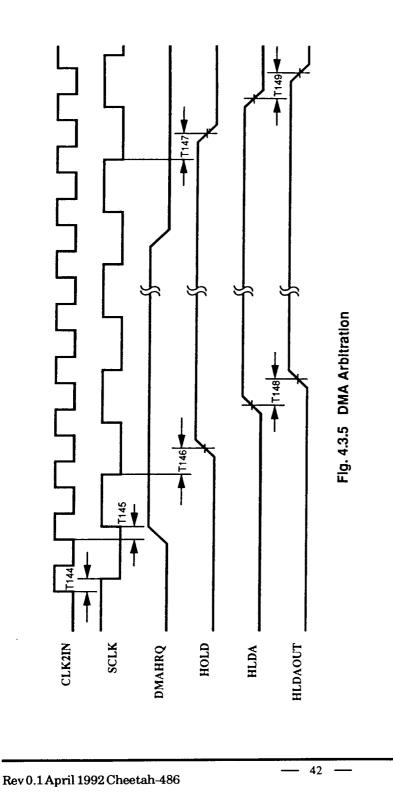

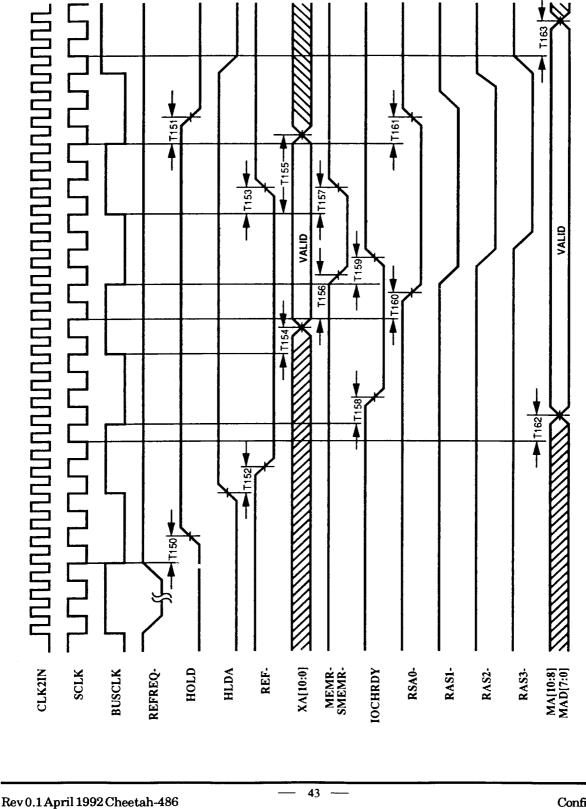

### 2.4 Master, DMA and Refresh

The Master Device uses the same pin as DMA for bus arbitration, and Refresh operates from a different pin so that it is easy to identify. The Master Device or DMA can be identified by the signals AEN8- and AEN16-. When either one is asserted LOW, it is a DMA cycle. The ET6000 supports both AT and Concurrent Refresh. No hold signal is sent back to the CPU in Concurrent Refresh. The AT Bus needs the full time to refresh as DRAMs do not need as much time. The ET6000 keeps track of when CPU to start its next instruction parallel to AT Bus Refresh. If the CPU needs to access the AT Bus, it must wait until refresh is completed.

### 2.5 Port B and NMI

A parity error detected will cause ET6000 to generate NMI to the CPU. NMI can also be generated through software. The ET6000 provides access to the Port B register defined for a PC/AT. The chart below illustrates bitdefinition:

| Bit Definition Chart                    |      |            |                                                                                                                 |

|-----------------------------------------|------|------------|-----------------------------------------------------------------------------------------------------------------|

| Address                                 | Bits | Function   | Description                                                                                                     |

| 61H                                     | 7    | Read Only  | System Memory Parity Check                                                                                      |

|                                         | 6    | Read Only  | IO Channel Check                                                                                                |

| - · · · · · · · · · · · · · · · · · · · | 5    | Read Only  | Timer 2 Output                                                                                                  |

|                                         | 4    | Read Only  | Refresh Detection                                                                                               |

|                                         | 3    | Read/Write | 0: Enable IO Channel Check<br>1: Disable IO Channel Check                                                       |

|                                         | 2    | Read/Write | <ul> <li>0: Enable System Memory<br/>Parity Check</li> <li>1: Disable System Memory<br/>Parity Check</li> </ul> |

|                                         | 1    | Read/Write | Speaker Data                                                                                                    |

|                                         | 0    | Read/Write | Timer 2 Gate                                                                                                    |

4

#### Rev 0:1 April 1992 Cheetah-486

Confidential

## 2.6 OS/2 Optimization

When running OS/2, 8742 needs to be programmed to activate the signal GATE A20 before entering Protected Mode. When it returns from the Protected Mode, some types of software use RESET2 by programming 8742 again. The Keyboard controller is a very slow device, thus, the system is slowed down dramatically. ET6000 supports the fast Gate A20 and Reset keyboard emulation and port 92 to help speed up performance.

### 2.7 DRAM Control Logic

### 2.7.1 Introduction

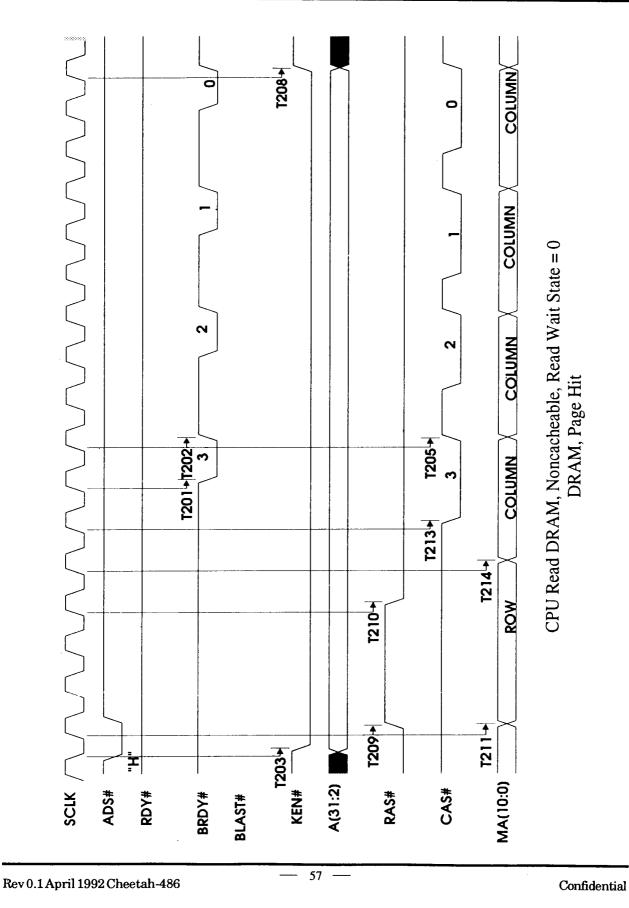

The DRAM Control Logic is designed and optimized for the 486 CPU. The ET6000 features an optimized DRAM memory controller, offering the highest performance for i486 CPU-based systems, while still retaining flexibility to allow the user to tailor the system to meet his/ her needs. Many memory configurations are available with the ET6000. These configurations are accomplished through use of the programmable register set. Slower DRAM devices can be accommodated through configuring the RAS# and CAS# access clocks. The number of clocks from assertion of RAS# to assertion of CAS# can be set to either 1.0 or 1.5 CPU T-states, while the number of clocks for CAS# access time can be either 1.0, 1.5, or 2.0 T-states. In addition, the RAS# precharge time Trp is programmable to either two or three clocks. The DRAM Controller supports up to 4 banks of DRAM with size up to 64MByte and three types of DRAM are supported: 256K, 1M and 4M.

| Bank 0 | Bank 1     | Bank 2          | Bank3      | Total<br>Memory Size | Page Size |

|--------|------------|-----------------|------------|----------------------|-----------|

| 256K   | NONE       | NONE            | NONE       | 1M                   | 2K        |

| 256K   | 256K       | NONE            | NONE       | 2M                   | 4K        |

| 256K   | 256K       | 256K            | NONE       | 3M                   | 6K        |

| 256K   | 256K       | 256K            | 256K       | 4M                   | 8K        |

| 1M     | 256K       | NONE            | NONE       | 5M                   | 6K        |

| 256K   | 256K       | 1M              | NONE       | 6M                   | 8K        |

| 256K   | 256K       | 256K            | 1M         | 7M                   | 10K       |

| 1M     | 1M         | NONE            | NONE       | 8M                   | 8K        |

| 1M     | 1M         | 256K            | NONE       | 9M                   | 10K       |

| 256K   | 256K       | 1M              | 1M         | 10M                  | 12K       |

| 1M     | 1M         | 1M              | NONE       | 12M                  | 12K       |

| 1M     | 1M         | 1M              | 256K       | 13M                  | 14K       |

| 1M     | 1 <b>M</b> | 1M              | 1M         | 16M                  | 16K       |

| IM     | 4M         | NONE            | NONE       | 20M                  | 12K       |

| 1M     | 1M         | 4M              | NONE       | 24M                  | 16K       |

| 1M     | 1M         | 1M              | 4M         | 28M                  | 20K       |

| 4M     | 4M         | NONE            | NONE       | 32M                  | 16K       |

| 4M     | 4M         | 1M              | NONE       | 36M                  | 20K       |

| 256K   | 1M         |                 | 4M         | 37M                  | 22K       |

| 1M     | 1M         | 4M              | 4M         | 40M                  | 24K       |

| 4M     | 4M         | 4M              | NONE       | 48M                  | 24K       |

| 256K   | 4M         | 4M              | 4M         | 49M                  | 26K       |

| 1M     | 4M         | 4M              | 4M         | 52M                  | 28K       |

| 4M     | 4M         |                 | 4M         | 64M                  | 32K       |

|        | Table A    | : Partial Possi | ble DRAM C | Configuration        |           |

#### TABLE A

## 2.7.2 DRAM Sizes/Bank Configuration

For system design flexibility, the ET6000 can support either 256K, 1M, or 4MDRAM's. The amount of DRAM installed, and the size is indicated to the ET6000 by the use of register bits. Bits 3 and 2 at the index register 16H are used to indicate installed banks of DRAM, while bits 1 and 0 at the same register indicate the size of the DRAM's. From the settings of these bits, the CHEETAH internally calculates the bank address mappings and the top of physical memory. The DRAM Banks have to be filled in the following order: Bank0->Bank1->Bank2->Bank3. Possible DRAM bank configurations are shown Table A on page 5.

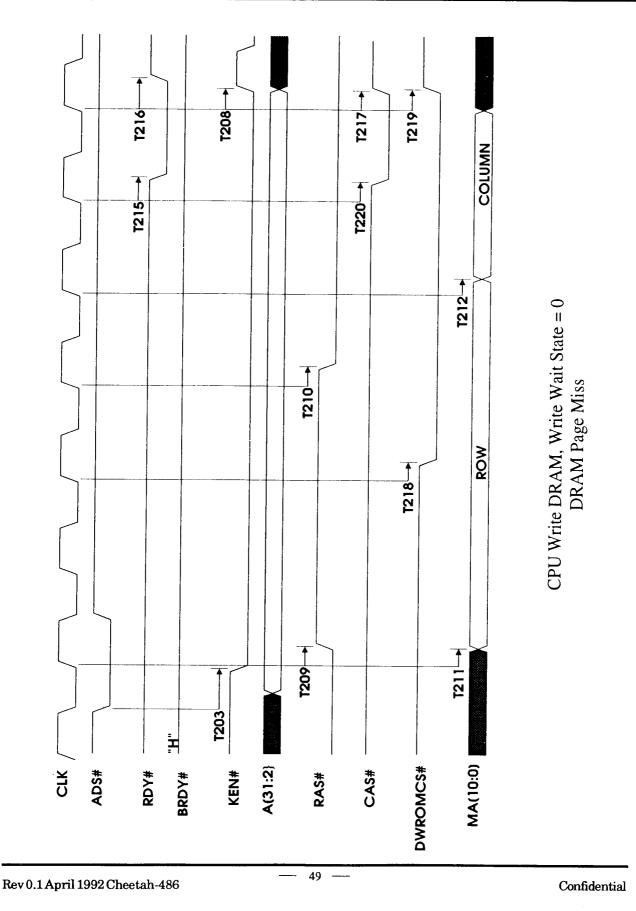

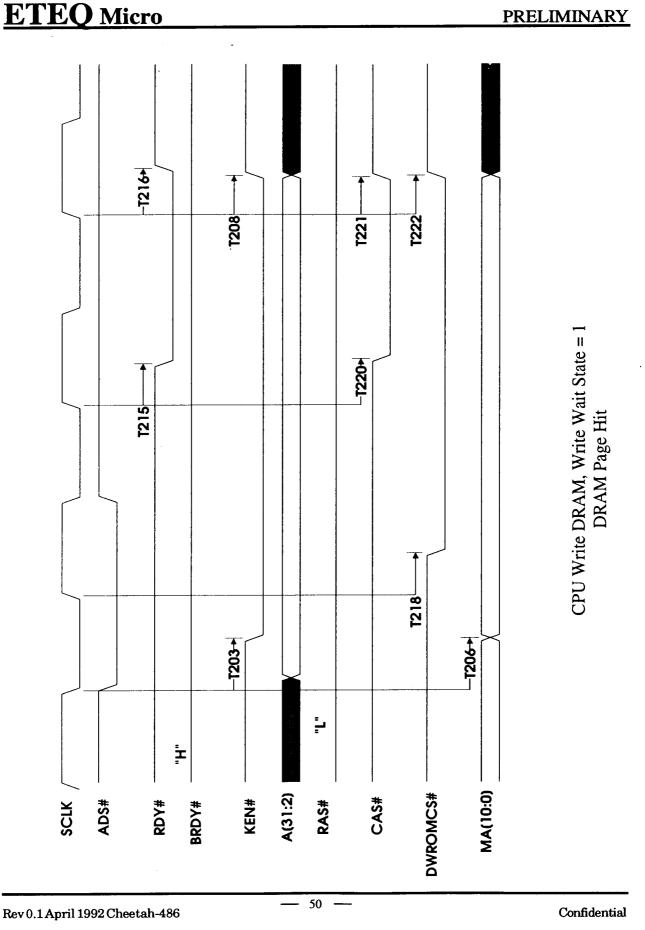

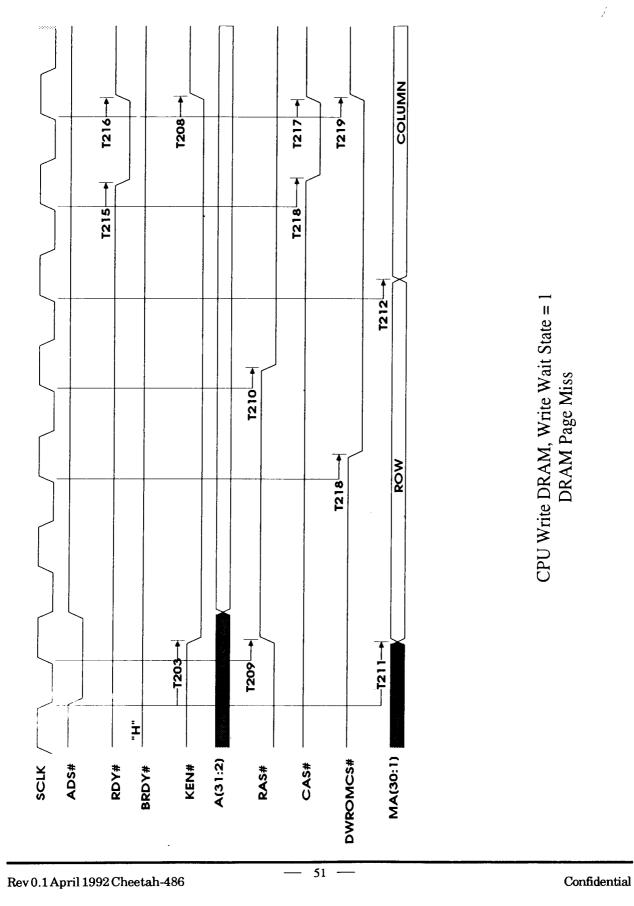

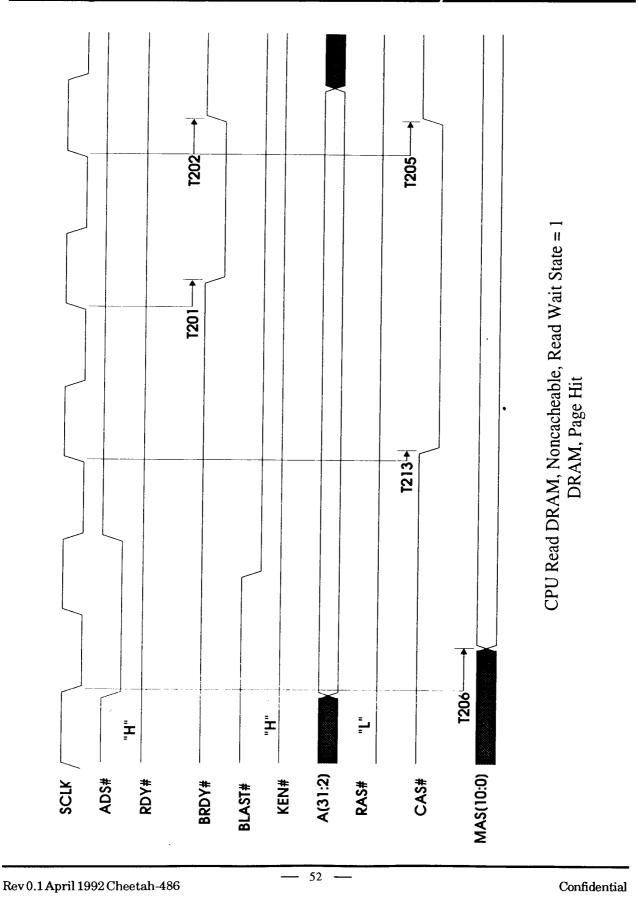

# 2.7.3 DRAM Speed and Wait State

In order to work with different types of DRAM speed, ET6000 supports wait state for memory read cycle as well as memory write cycle. For read cycle, a configuration of 0 to 3 wait state is available: R1WT, R2WT, R3WT. For write cycle, the ET6000 supports: W0WT, W1WT. (See Table B below.)

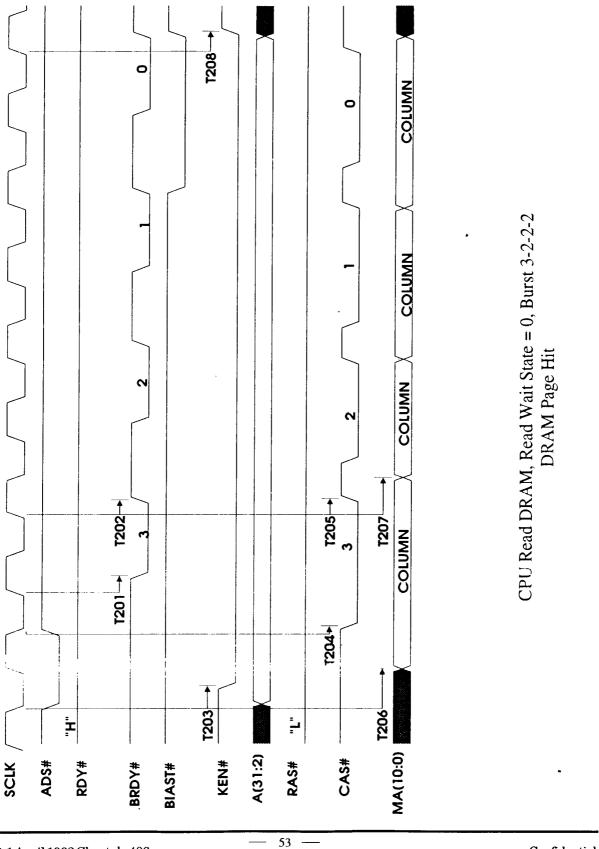

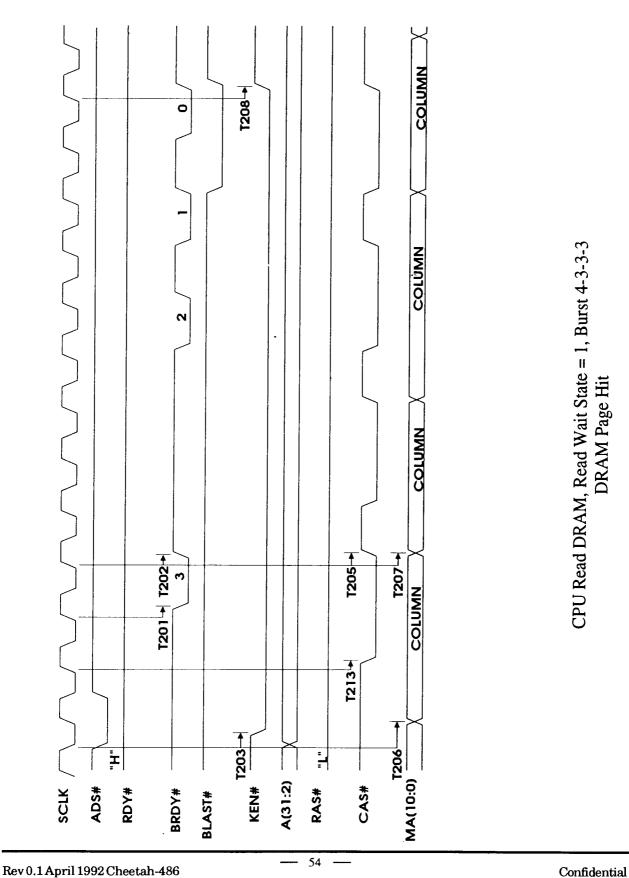

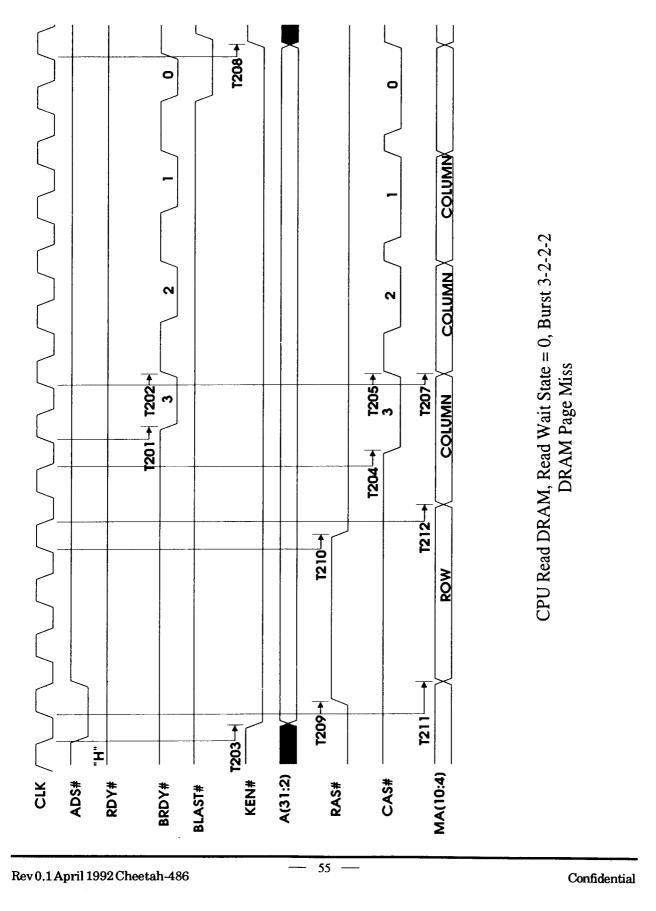

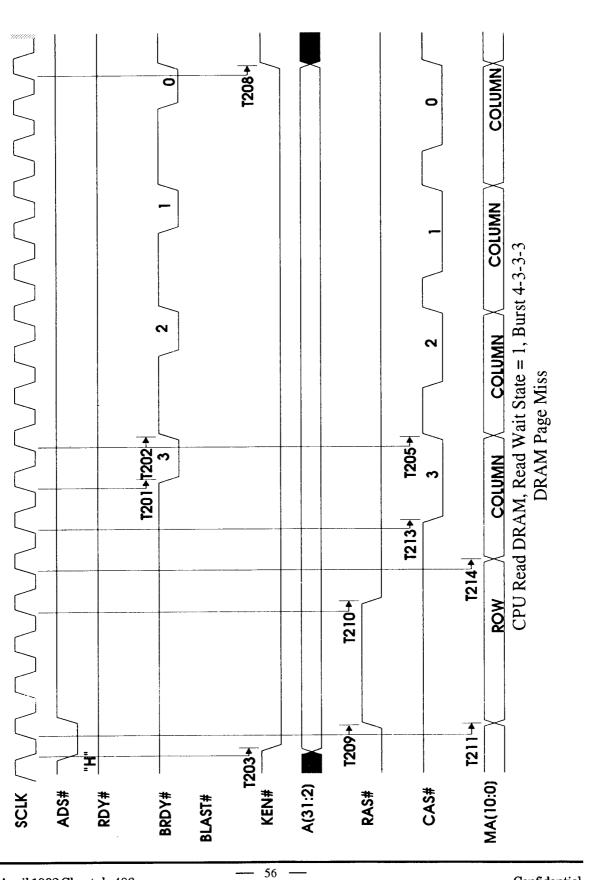

The ET6000 has Burst Mode Memory Manager support 3-2-2-2, 4-3-3-3, 5-4-4-4 DRAM burst cycles to enhance system speed.

## 2.7.4 Row and Column Address

Table C, below, illustrates row/column address for different types of DRAM. For easy debugging, all row and column addresses are continuous, no scramble is needed.

## 2.8 DMA and Master Access DRAM Logic

The DMA Master can access the local DRAM through ET6000. When HLDA1 and MEMR/MEMW become active, a memory read/write cycle will be performed. To guarantee cache coherence, the SRAM data will be updated when a memory write hit occurs.

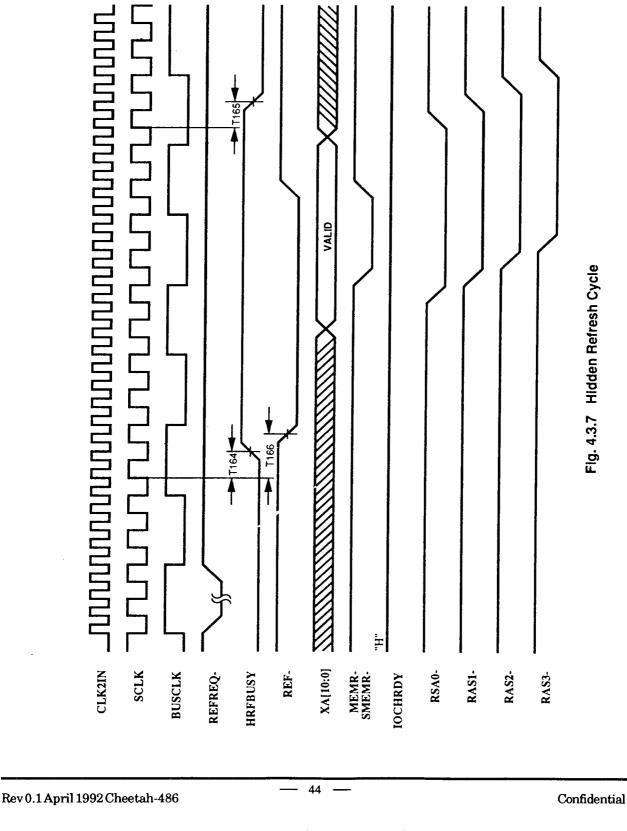

## 2.9 Concurrent Refresh

In order to alleviate refresh penalty, ET6000 supports "Concurrent Refresh" in addition to normal PC Refresh. Traditional PC Refresh will send a HOLD to stop the CPU, Then, after receiving HLDA from the CPU, refresh will begin. Concurrent Refresh can execute the refresh cycle concurrently with the CPU as long as there is no DRAM conflict. (i.e. we enhance performance by allowing refresh to work on the DRAM and the CPU to work on the Cache RAM at the same time.) To quiet refresh noise on the Motherboard, all RAS are staggered during refresh cycle.

| <b>CPU SPEED</b>                                   | DRAM SPEED  | DRAM WAIT STATE |  |

|----------------------------------------------------|-------------|-----------------|--|

| 486-20MHz                                          | 80NS (CMOS) | (W0WS, R0WS)    |  |

| 486-25MHz                                          | 80NS (CMOS) | (W0WS, R1WS)    |  |

| 486-33MHz                                          | 80NS (CMOS) | (W0WS, R1WS)    |  |

| 486-50MHz                                          | 80NS (CMOS) | (W1WS, R2WS)    |  |

| Table B: Wait States / DRAM Speeds for 486 systems |             |                 |  |

| DRAM              | Row                         | Column          |

|-------------------|-----------------------------|-----------------|

| Configuration     | Address                     | Address         |

| 256K Page Mode    | (A19-A11)                   | (A10-A2)        |

| 1M Page Mode      | (A21-A12)                   | (A11-A2)        |

| 4M Page Mode      | (A23-A13)                   | (A12-A2)        |

| Table C : Row / C | olumn Address for Different | t Types of DRAM |

Rev 0.1 April 1992 Cheetah-486

- 6 —

Confidential

## 2.10 Shadow RAM

For those BIOS Call Intensive Application Softwares, it is not efficient to run BIOS Call in low speed ROM. Moving all ROM contents to a high speed DRAM will largely improve the performance of a BIOS Call intensive program.

ET6000 allows all Motherboard ROM and Adapter Card ROM to be shadowed on the Motherboard DRAM as long as they are resident in (C0000-CFFFF), (D0000-DFFFF), (E0000-EFFFF), or (F0000-FFFFF) range. If the Adapter ROM is on the Motherboard, it can still be shadowed.

### 2.11 Bus Interface Between CD, MAXD and SD Bus

The ET6000 Data Buffer provides interface between three distinct buses: the CD Bus, MAXD Bus and the SD Bus. The CD Bus (CD<15:0>) is the CPU Data Bus. The Memory Data Bus connects to the 32-bit wide local DRAM. The MAXD Bus (MD<15:0>) are Memory Address Bus and 16-bit bus for on board I/O devices which use the MD bus. Off board I/O devices would situate on the SD bus (SD<15:0>).

The data conversion can be done on either an 8-bit, 16bit wide bus. The bus size 16(BS16-) feature is supported allowing the 486 to acknowledge the external 16-bit data buses. The 486 will make adjustments for correct transfer of the upper bytes.

### 2.12 Parity Generation and Checking Logic

The ET6000 generates byte-wise even Memory Parity Bits for both the CPU and DMA/Master Write to the local DRAM. The Memory Parity Bits (MP<3:0>) are strobed into the DRAM along with the write data, thus, they are directly connected to the DRAM.

During a local DRAM read cycle, the data and even parity bits are read from the DRAM onto the CD Bus and the MP Bus, respectively. The data is latched internally during the parity checking period. The byte-wise parity errors are gated with byte enable bits (BH0#, BE3#) to generate the latched parity error which would be asserted one system clock later, at the end of the read operation.

As soon as the latch parity error is asserted, it will stay active until cleared by another local DRAM read cycle that does not encounter parity error.

### 2.13 Numerical Coprocessor Interface Logic

The ET6000 Data Buffer supports the floating point errors handled with the i486 microprocessor.

The trailing edge of FERR- will trigger flip-flop to generate the IRQ signal which will be ORed with WTINTR and become interrupt level 13 (IRQ13-). After FERR- is asserted, the interrupt service routine handles the error and then clears the interrupt by executing a dummy write to I/O port F0h. The IGNNEsignal is also activated by this. It allows non-control instructions to be executed prior to the time the FERRsignal is reset by the i486. This is implemented for AT compatibility.

### 2.13 14.318MHz and Divided by 12 Counter

The ET6000 Data Buffer also provides the logic to generate a 14.318MHz OSC signal and a divided by 12OSC119 signal which are used on the system board.

Rev 0.1 April 1992 Cheetah-486

7 -

### **3.0 Configuration Registers**

The ET6000 has internal registers used for system configuration and internal control. These areas are accessed through IO Ports 22H and 23H. Each access to an internal register is accomplished by first, writing its index into Port 22H. This index is then used to gate the

appropriate internal register and the control data is accessed through Port 23H.

There are eighteen configuration registers in ET6000. The definitions of these registers are as follows:

### TABLE D

| Index | Bits | Values and Functions       | Default |

|-------|------|----------------------------|---------|

| 10H   | 0    | RAM at A0000H to BFFFFH    | 0       |

|       |      | 0: AT Bus Cycle            |         |

|       |      | 1: Local Bus Cycle         |         |

|       | 1    | Wait for HALT after KBDRST | 0       |

|       |      | 0: Do not wait for HALT    |         |

|       |      | 1: Wait for HALT           |         |

|       | 2    | Fast Reset Delay           | 0       |

|       |      | 0: Do not use delay        |         |

|       |      | 1: Wait for 2us delay      |         |

|       | 3    | Slow refresh at 95us       | 0       |

|       |      | 0: Disable slow refresh    |         |

|       |      | 1: Enable slow refresh     |         |

|       | 4    | Refresh Selection          | 0       |

|       |      | 0: AT Type Refresh         |         |

|       |      | 1: concurrent Refresh      |         |

|       | 5    | Reserved                   |         |

|       | 7:6  | 00: Turbo / Non-turbo      | 00      |

|       |      | 01: Local device supported |         |

|       |      | 10: Suspend mode           |         |

|       |      | 11: Not allowed            |         |

### System Configuration Register

#### TABLE E

### CACHE Configuration and Non-Cacheable Block Size Register

| Index | Bits | Values and Functions     | Default |  |

|-------|------|--------------------------|---------|--|

| 11H   | 3:0  | Reserved                 |         |  |

|       | 4    | 0: 2 Bank DRAM           | 0       |  |

|       |      | 1: 4 Bank DRAM           |         |  |

|       | 7:5  | Non-Cacheable Block Size | 000     |  |

|       |      | 000: Disabled            |         |  |

|       |      | 001: 512KB               |         |  |

|       |      | 010: 1MB                 |         |  |

|       |      | 011: 2MB                 |         |  |

|       |      | 100: 4MB                 |         |  |

|       |      | 101: 8MB                 |         |  |

|       |      | 110: 16MB                |         |  |

|       |      | 111: 32MB                |         |  |

Rev 0.1 April 1992 Cheetah-486

8 —

## ETEQ Micro

### TABLE F

#### Non-Cacheable Block Address Register

| Index | Bits | Values and Functions             | Default |

|-------|------|----------------------------------|---------|

| 12H   | 0    | Reserved                         | 0       |

|       | 7:1  | Non-Cacheable Address A25 to A19 | 0       |

### TABLE G

### DRAM Bank and Type Configuration Register

| Index  | Bits | Values and Functions | Default |

|--------|------|----------------------|---------|

| 13H    | 1:0  | Bank0 DRAM Type      | 01      |

|        |      | 00: None             |         |

|        |      | 01:256K              |         |

|        |      | 10: 1M               |         |

|        |      | 11: <b>4M</b>        |         |

| ······ | 3:2  | Bank1 DRAM Type      | 00      |

|        |      | 00: None             |         |

|        |      | 01:256K              |         |

|        |      | 10: 1M               |         |

|        |      | 11: <b>4M</b>        |         |

|        | 5:4  | Bank2 DRAM Type      | 00      |

|        |      | 00: None             |         |

|        |      | 01:256K              |         |

| i      |      | 10: 1M               |         |

|        |      | 11: <b>4M</b>        |         |

|        | 7:6  | Bank3 DRAM Type      | 00      |

|        |      | 00: None             |         |

|        |      | 01: 256K             |         |

|        |      | 10: 1M               |         |

|        |      | 11:4M                |         |

## ETEO Micro

### TABLE H

### **DRAM Configuration Register**

| Index | Bits | Values and Functions             | Default |

|-------|------|----------------------------------|---------|

| 14H   | 0    | Write Cycle Wait States          | 1       |

|       |      | 0: 0WS                           |         |

|       |      | 1: 1WS                           |         |

|       | 2:1  | Read Cycle Wait States           | 01      |

|       |      | 00: 0WS                          |         |

|       |      | 01: 1WS                          |         |

|       |      | 10: 2WS                          |         |

|       |      | 11: 3WS                          |         |

|       | 3    | RAS precharge time               | 1       |

|       |      | 0: 1.5 SYSCLK (not for 33MHz and |         |

|       |      | 50MHz)                           |         |

|       |      | 1: 2.5 SYSCLK                    |         |

|       | 4    | RAS to CAS time                  | 1       |

|       |      | 0: 1 SYSCLK (not for R0WS)       |         |

|       |      | 1: 2 SYSCLK                      |         |

|       | 5    | 0: Disable ROMCS at memory range | 0       |

|       |      | C0000-DFFFF                      |         |

|       |      | 1: Enable ROMCS at memory range  |         |

|       |      | C0000-DFFFF                      |         |

|       |      | (NOTE: if C0000-DFFFF is enabled |         |

|       |      | for ROMCS, then memory address   |         |

|       |      | cannot be SHADOWED)              |         |

|       | 6    | 0: Enable on-board memory range  | 0       |

|       | -    | 512K-640K                        |         |

|       |      | 1: Disable on-board memory range |         |

|       |      | 512K-640K                        |         |

|       | 7    | 0: Enable on-board memory range  | 0       |

|       | ,    | 15M-16M                          | -       |

|       |      | 1: Disable on-board memory range |         |

|       |      | 15M-16M                          |         |

## ETEQ Micro

### TABLE I

Shadow RAM Configuration Register

| Index                                 | Bits | Values and Functions                   | Default |

|---------------------------------------|------|----------------------------------------|---------|

| 15H                                   | 0    | RAM at C0000H-CFFFFH                   | 0       |

|                                       |      | 0: Read/Writ                           |         |

|                                       |      | 1: Read Only                           |         |

|                                       | 1    | Access ROM/RAM at C0000H-CFFFFH        | 0       |

|                                       |      | 0: Accessed on-board ROM, ie AT bus    |         |

|                                       |      | cycle                                  |         |

|                                       |      | 1: Access Shaow RAM                    |         |

|                                       |      | C0000H-CFFFFH enabled                  |         |

|                                       | 2    | RAM AT D0000H-DFFFFH                   | 0       |

|                                       |      | 0: Read/Writ                           |         |

|                                       |      | 1: Read Only                           |         |

|                                       | 3    | Access ROM/RAM at D0000H-DFFFFH        | 0       |

|                                       |      | 0: Accessed on-board ROM, ie AT bus    |         |

|                                       |      | cycle                                  |         |

|                                       |      | 1: Access Shaow RAM                    |         |

|                                       |      | D0000H-DFFFFH enabled                  |         |

|                                       | 4    | RAM AT E0000H-EFFFFH                   | 0       |

|                                       |      | 0: Read/Writ                           |         |

|                                       |      | 1: Read Only                           |         |

| · · · · · · · · · · · · · · · · · · · | 5    | Access ROM/RAM at E0000H-EFFFFH        | 0       |

|                                       |      | 0: Accessed on-board ROM, ie AT bus    |         |

|                                       |      | cycle                                  |         |

|                                       |      | 1: Access Shaow RAM                    |         |

|                                       |      | E0000H-EFFFFH enabled                  |         |

|                                       | 6    | Access ROM/RAM at F0000H-FFFFFH        | 0       |

|                                       |      | (System BIOS ROM)                      |         |

|                                       |      | 0: Read from ROM, Write to RAM         |         |

|                                       |      | 1: Read from Shadow RAM, Write will    |         |

|                                       |      | be protected (will not be written into |         |

|                                       |      | RAM)                                   |         |

|                                       | 7    | Shadow RAM at C0000H-FFFFFH            | 0       |

|                                       |      | 0: Non Cacheable                       |         |

|                                       |      | 1: Cacheable and Cache write protected |         |

### **ET6000 Pin Description**

| Pin           | Pin       |          |                                           |

|---------------|-----------|----------|-------------------------------------------|

| No.           | Туре      | Symbol   | Description                               |

| Clocks        |           |          |                                           |

| 41            | Ι         | CLKIN    | Oscillator input. The frequency           |

|               |           |          | should be the same as the CPU's           |

|               |           |          | clock.                                    |

| 42            | I         | EXACLK   | AT BUS CLOCK input from crystal.          |

| 39            | I         | CX1      | 14.318MHz input from crystal.             |

| 40            | 0         | CX2      | 14.318MHz output to crystal.              |

| 37            | 0         | OSC119   | 14.318MHz divided by 12 clock output      |

| 13            | 0         | BUSCLK   | 8MHz AT BUS CLOCK.                        |

|               |           | <u> </u> |                                           |

| Reset Co<br>9 | ntri<br>I | PWRGD    | Power On Reset.                           |

| 156           | 0         | RESET3   | CPU Reset. Asserted by either power       |

| 150           | 0         | NL0L15   | on initializing the CPU or bringing       |

|               |           |          | the CPU back to real mode from the        |

|               |           |          | protected mode.                           |

| 43 O          |           | RESET4   | System Reset. Assereted during Power      |

|               | 0         | NLOL 14  | On to reset the whole system.             |

|               |           |          |                                           |

| CPU Cor       | ntrol     |          |                                           |

| 141           | Ι         | ADS-     | An input from the CPU indicates address   |

|               |           |          | and cycle definitions are valid. It is an |

|               |           |          | active low.                               |

| 154           | I         | MIO-     | CPU Status. A high means this is a        |

|               |           |          | memory cycle and low indicates an IO      |

|               |           |          | cycle.                                    |

| 148           | Ι         | WR-      | CPU Status. A high means this is a write  |

|               |           |          | cycle and a low indicates a read cycle.   |

| 155           | Ι         | DC-      | CPU status. A HIGH means it is a data     |

|               |           |          | access cycle, and a Low indicates code    |

|               |           |          | access.                                   |

| 45            | I/O       | RDYN-    | This pin generates the CPU READY          |

|               |           |          | signal to alert the CPU that the cycle    |

|               |           |          | has finished with the exception of the    |

|               |           |          | coprocessor cycle. The MATH co-           |

|               |           |          | processor will generate its own CPU       |

|               |           |          | ready, thus, READY- acts as an            |

|               |           |          | input in this case.                       |

|               |           |          | mput in uns case.                         |

Rev 0.1 April 1992 Cheetah-486

Confidential

| Pin<br>No.       | Pin<br>Type     | Symbol    | Description                            |

|------------------|-----------------|-----------|----------------------------------------|

|                  | JF*             |           |                                        |

| <b>CPU</b> Contr | col (Continued) |           |                                        |

| 153, 152         | I/O             | BE<3:0>-  | INPUT BYTE ENABLE signals from         |

| 151, 149         |                 |           | the CPU. They become output signals    |

|                  |                 |           | at the DMA cycles to reflect XA0,      |

|                  |                 |           | SBHE                                   |

| 147              | Ι               | PHLDA     | When active, it indicates the          |

|                  |                 |           | processor has released the bus in      |

|                  |                 |           | response to HOLD request. This         |

|                  |                 |           | signal is connected to the processor   |

|                  |                 |           | HLDA signal.                           |

| 81               | 0               | NMI       | Non-Maskable Interrupt to the CPU.     |

| 158              | 0               | HOLD      | An active HIGH used to request the     |

|                  |                 |           | CPU to relinquish the bus to DMA,      |

|                  |                 |           | Master or Refresh cycle.               |

| 116-121,         | Ι               | A<7:2>    | CPU Address.                           |

| 103-105,         | I               | A<19:17>  |                                        |

| 18               |                 | CAS3-/A25 |                                        |

| 97-99,           | Ι               | A<24:22>  |                                        |

| 101              | I               | A21       |                                        |

| 96               | I               | A31       |                                        |

| 106-112,         | I/O             | A<16:10>  | CPU Address. Output signals during     |

| 114-115          | I/O             | A<9:8>    | DMA and MASTER MODE.                   |

| 102              | I/O             | A20       |                                        |

| Cache Cont       | rol             |           |                                        |

| 157              | 0               | KEN-      | Active low signal to indicate that the |

|                  | ·····           |           | current cycle is cacheable.            |

| 122              | 0               | BRDY-     | Active low signal. Burst Ready to 486  |

| 142              | I               | BLAST-    | BLAST- input from 486. Indicates       |

|                  |                 |           | that the burst cycle is complete after |

|                  |                 |           | the next BRDY- is returned. Active     |

|                  |                 |           | low.                                   |

| Pin                                 | Pin   |                                               |                                                                                                                                                     |

|-------------------------------------|-------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| No.                                 | Туре  | Symbol                                        | Description                                                                                                                                         |

| DRAM Co                             | ntrol |                                               |                                                                                                                                                     |

| 160                                 | 0     | DWROMCS-                                      | Dual functional pin. It is data write<br>enable for DRAM write cycle and<br>ROM chip select for ROM cycle.                                          |

| 22                                  | 0     | CAS0-                                         | Column Address Strobe for DRAM<br>bank 0.                                                                                                           |

| 21                                  | 0     | CAS1-                                         | Column Address Strobe for DRAM bank 1.                                                                                                              |

| 19                                  | 0     | CAS2-                                         | Column Address Strobe for DRAM<br>bank 2. By combining with BE<3:0><br>each byte can be controlled individually                                     |

| 18                                  | 0     | CAS3-                                         | Column Address Strobe for DRAM<br>bank 3. By combining with BE<3:0><br>each byte can be controlled individually                                     |

| 23-24,<br>21<br>22                  | 0     | RAS<1:0>-<br>CAS1-/RAS3-<br>CAS0-/RAS2-       | Row Address Strobe 0 to 3 correspo-<br>nding to bank 0 to 3. It should be bu-<br>ffered before tying to the DRAMs.<br>These are active low signals. |

| 138-140,<br>124-129,<br>131-132     | I/O   | MAXD<10:8><br>MAXD<7:2><br>MAXD<1:0>          | DRAM Memory Address. They<br>should be buffered before tying to the<br>DRAMs and also used as refresh<br>address output during REF cycle.           |

| Data Bus                            |       |                                               |                                                                                                                                                     |

| 61-69,<br>71-80,<br>82-25,<br>87-95 | I/O   | CD<31:23><br>CD<22:13><br>CD<12:9><br>CD<8:0> | Regular Mode: Connect to the CPU<br>Data Bus. CD<15:0> would be<br>driven during CPU read and DMA<br>write memory cycle                             |

|                                     |       |                                               | Bypass Mode: Connect to CPU Data<br>and DRAM Data Bus. CD<15:0> will<br>pass through transparent latch to<br>parity generation and checking logic.  |

| Pin<br>No. | Pin<br>Type | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data Bus ( | Continued)  |            |                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 5-2        | I/O         | MP<3:0>    | Memory Parity Bit 0 to 3. Output for<br>CPU or DMA write to memory, and input<br>for CPU or DMA read from memory.<br>EVEN parity bit is generated on all write<br>data cycles. This information must be<br>driven back into MP<3:0> with the<br>same timing as read data to insure the<br>correct parity check. MP3 refers to Byte3<br>PARITY, MP2 refers to Byte2 Parity<br>ans so on. |  |

| 133-140,   | I/O         | MAXD<15:8> | ISA Data Bus Bits <15:0>                                                                                                                                                                                                                                                                                                                                                                |  |

| 124-129,   | I/O         | MAXD<7:2>  | and memory address bus                                                                                                                                                                                                                                                                                                                                                                  |  |

| 131-132    | I/O         | MAXD<1:0>  |                                                                                                                                                                                                                                                                                                                                                                                         |  |

| AT Contro  | 1           |            |                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 35         | 0           | L1MCS-     | Low 1 Meg Chip Select to generate<br>SMEMR- and SMEMW- for the AT<br>Bus command which is an indication<br>that it is within the first 1 Meg add-<br>ress range. It is an active low signal.                                                                                                                                                                                            |  |

| 29         | I/O         | XBHE-      | Peripheral Byte High Enable. An act-<br>ive LOW signal which indicates that<br>the data is on the upper byte. It is an<br>output during the CPU and DMA<br>cycle and an input during the<br>master CYCLE.                                                                                                                                                                               |  |

| 59-58,     | I/O         | XA<1:0>    | These signals are latched at address                                                                                                                                                                                                                                                                                                                                                    |  |

| 26         |             | A20M       | outputs during CPU cycles and inputs during DMA or Master cycles.                                                                                                                                                                                                                                                                                                                       |  |

| 8          | 0           | BALE       | Bus Address Latch Enable. The trail-<br>ing edge latches the valid address for<br>the AT Slot.                                                                                                                                                                                                                                                                                          |  |

| 55         | I/O         | MEMR-      | AT Bus Memory Read. It is an output<br>if the CPU is controlling the bus and<br>an input if the DMA is in control. An<br>active LOW signal.                                                                                                                                                                                                                                             |  |

Rev 0.1 April 1992 Cheetah-486

Confidential

| Pin<br>No. | Pin<br>Type      | Symbol  | Description                                                                                                                                |  |

|------------|------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| AT Conf    | trol (Continued) |         |                                                                                                                                            |  |

| 54         | I/O              | MEMW-   | AT Bus Memory Write. An output if<br>the CPU is controlling the bus and an<br>input if the DMA is in control. An ac-<br>tive LOW signal.   |  |

| 56         | I/O              | IOR-    | AT Bus IO Read. It is an output if the<br>CPU is controlling the bus and an in-<br>put if the DMA is in control. An<br>active LOW signal.  |  |

| 57         | I/O              | IOW-    | AT Bus IO Write. It is an output if the<br>CPU is controlling the bus and an<br>input if the DMA is in control. An act-<br>ive LOW signal. |  |

| 14         | Ι                | 0WS-    | Zero Wait State. When LOW, the AT<br>Bus will terminate its current cycle<br>without additional wait state.                                |  |

| 11         | I/O              | CHRDY   | IO Channel Ready. When LOW, the<br>AT Bus will insert wait states until<br>this signal returns to HIGH.                                    |  |

| 30         | Ι                | MCS16-  | 16 Bit Memory Chip Select. When<br>LOW, it is a 16 bit memory transfer<br>from the AT Slot. When HIGH, an 8<br>bit memory transfer         |  |

| 31         | Ι                | IOCS16- | 16 Bit IO Chip Select. When LOW, it<br>is a 16 bit IO transfer. When HIGH,<br>an 8 bit memory transfer.                                    |  |

| 10         | Ι                | IOCHCK- | An AT Bus error condition will cause<br>an NMI to be generated.                                                                            |  |

| 15         | 0                | SDEN-   | Slot Data Enable. Enables the buffer<br>that drives the data bus onto the slot<br>an back.                                                 |  |

| 32         | 0                | ACK-    | An active LOW, tied to the C206<br>ACK - pin.                                                                                              |  |

### ET6000 Pin Description (Continued)

| Pin<br>No. | Pin<br>Type     | Symbol | Description                                                                                                                                                                                         |

|------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT Cont    | rol (Continued) |        |                                                                                                                                                                                                     |

| 27         | Ι               | MISC   | An active LOW signal indicating a local BUS cycle, not an AT cycle.                                                                                                                                 |

| 45         | 0               | INTA-  | Interrupt Acknowledge. Asserted for<br>CPU to read the interrupt vector from<br>the XD Bus.                                                                                                         |

| 28         | 0               | SDIR0- | System Data Bus Direction for the<br>low byte. The data is moved from<br>SD Bus to MD Bus when SDIR0- is<br>LOW. The data is moved from MD<br>Bus to SD Bus when SDIR0- is HIGH                     |

| 34         | 0               | SDIR1- | System Data Bus Direction for the<br>high byte. The data is moved from<br>SD Bus to MD Bus when SDIR1- is<br>LOW. The data is moved from MD<br>Bus to SD Bus when SDIR1- is HIGH                    |

| 144        | 0               | BS16-  | A bus size of 16 caused the CPU to<br>run multiple bus cycles to complete a<br>request from devices that cannot<br>provide or accept 32 bits of data in a<br>singale cycle. BS16- is an active LOW. |

| 6          | 0               | SAON-  | An active LOW signal indicating a LA<br>BUS cycle.                                                                                                                                                  |

| Pin<br>No | Pin<br>Type | Symbol   | Description                                                                                                                                                                                         |  |

|-----------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Refresh   |             |          |                                                                                                                                                                                                     |  |

| 12        | I/O         | REF-     | An output to indicate a refresh cycle.<br>For Master Mode, it is an input from<br>the Master Device to indicate a<br>refresh cycle.                                                                 |  |

| DMA Co    | ntrol       |          |                                                                                                                                                                                                     |  |

| 48        | Ι           | DMAHRQ   | HOLD REQUEST from DMA or other Bus Master for bus control.                                                                                                                                          |  |

| 53        | I           | AEN8-    | Address Enable for 8 bit DMA transf-<br>er. An active LOW signal.                                                                                                                                   |  |

| 52        | Ι           | AEN16-   | Address Enable for 16 bit DMA trans-<br>fer. An active LOW signal.                                                                                                                                  |  |

| 46        | 0           | HLDAOUT- | Indicates that the CPU has relinquish-<br>ed the bus to other masters or DMA.                                                                                                                       |  |

| 33        | I           | MASTER-  | When LOW, it indicates that a bus<br>master other than the CPU or DMA is<br>owning the bus.                                                                                                         |  |

| 49        | I           | ADSTB8   | Address Strobe for 8 bit DMA transfer.                                                                                                                                                              |  |

| 51        | Ι           | ADSTB16  | Address Strobe for 16 bit DMA transfer.                                                                                                                                                             |  |

| 7         | 0           | AEN      | Address enable signal, drive AT Bus AEN directly.                                                                                                                                                   |  |

| 144       | 0           | BS16-    | A bus size of 16 caused the CPU to<br>run multiple bus cycles to complete a<br>request from devices that cannot<br>provide or accept 32 bits of data in a<br>singale cycle. BS16- is an active LOW. |  |

| Decodes   |             |          |                                                                                                                                                                                                     |  |

| 16        | 0           | 8042CS-  | 8742 Keyboard Controller Chip Select. An active LOW signal.                                                                                                                                         |  |

| 47        | 0           | RTCAS-   | Real Time Clock Address Strobe.<br>It should tie to the 82C206. The<br>trailing edge latches the address onto<br>the CA Bus.                                                                        |  |

| Pin<br>No. | Pin<br>Type     | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floating   | Point Interface |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 146        | Ι               | FERR-  | Tied to the 486 FERR- pin.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 159        | 0               | IGNNE- | Connected to the 486 IGNNE- pin.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 145        | Ι               | RDYIN- | This pin generates the NPU READY signal to alert the NPU that the cycle has finished.                                                                                                                                                                                                                                                                                                                                                                         |

| Miscella   | neous           |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 44         | Ι               | TMOUT2 | Output from the 8254 timer located inside the 82C206.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 38         | 0               | TMGATE | TIMER GATE 2 enables the counter<br>two of the 8254. Used for tone<br>generation for the speaker.                                                                                                                                                                                                                                                                                                                                                             |

| 36         | 0               | SPKOUT | Speaker data used to drive the speaker. Buffer required.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27         | I               | MISC   | This pin will connect to a hardwired<br>clock switching control signal, if it<br>exists. If bit 2 of register 10 is<br>programmed to 0 then a high on this<br>signal will keep the system in high<br>speed mode. Otherwise, the system<br>will enter low speed mode if this pin<br>is low. The system will stay in high<br>speed mode and does not count on<br>this signal at all if bit 2 of register 10<br>is programmed to 1. Tied to high if<br>not used. |

| Pin      | Pin  |        |              |  |

|----------|------|--------|--------------|--|

| No.      | Туре | Symbol | Description  |  |

| Power    |      |        |              |  |

| 20,60    | Ι    | VDD    | Power Supply |  |

| 100, 143 |      |        |              |  |

| Ground   |      |        |              |  |

| 1, 17    | Ι    | VSS    | Ground       |  |

| 25, 50   |      |        |              |  |

| 70, 86   |      |        |              |  |

| 113, 130 |      |        |              |  |

| 150      |      |        |              |  |

### 4.0 ET6000 Pin Driving Definition

| Pin Number | Pin Name | I/О Туре | Driving |

|------------|----------|----------|---------|

| 1          | VSS      | I        |         |

| 2          | MP0      | I/O      | 6 ma    |

| 3          | MP1      | I/O      | 6 ma    |

| 4          | MP2      | I/O      | 6 ma    |

| 5          | MP3      | I/O      | 6 ma    |

| 6          | SAON-    | 0        | 4 ma    |

| 7          | AEN      | 0        | 12 ma   |

| 8          | BALE     | 0        | 4 ma    |

| 9          | PWRGD    | Ι        |         |

| 10         | IOCHCK-  | Ι        |         |

| 11         | CHRDY    | I/O      | 6 ma    |

| 12         | REF-     | I/O      | 4 ma    |

| 13         | BUSCLK   | 0        | 6 ma    |

| 14         | 0WS-     | I        |         |

| 15         | SDEN-    | 0        | 4 ma    |

| 16         | 8042CS-  | 0        | 4 ma    |

| 17         | VSS      | Ι        |         |

| 18         | CAS3-    | I/O      | 12 ma   |

| 19         | CAS2-    | 0        | 12 ma   |

| 20         | VDD      | Ι        |         |

| 21         | CAS1-    | 0        | 12 ma   |

| 22         | CAS0-    | 0        | 12 ma   |

| 23         | RAS1-    | 0        | 12 ma   |

| 24         | RAS0-    | 0        | 12 ma   |

| 25         | VSS      | Ι        |         |

| 26         | A20M     | I/O      | 4 ma    |

| 27         | MISC     | I        |         |

| 28         | SDIR0-   | 0        | 4 ma    |

Rev 0.1 April 1992 Cheetah-486

Confidential

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer

## 4.0 ET6000 Pin Driving Definition (Continued)

| Pin Number | Pin Name | I/O Type | Driving |

|------------|----------|----------|---------|

| 29         | XBHE-    | I/O      | 4 ma    |

| 30         | MCS16-   | Ι        |         |

| 31         | IOCS16-  | Ι        |         |

| 32         | ACK-     | 0        | 4 ma    |

| 33         | MASTER-  | Ι        |         |

| 34         | SDIR1-   | 0        | 4 ma    |

| 35         | L1MCS-   | 0        | 4 ma    |

| 36         | SPKOUT   | 0        | 4 ma    |

| 37         | OSC119   | 0        | 6 ma    |

| 38         | TMGATE   | 0        | 4 ma    |

| 39         | CX1      | Ι        |         |

| 40         | CX2      | Ι        |         |

| 41         | CLKIN    | I        |         |

| 42         | EXACLK   | I        |         |

| 43         | RESET4   | 0        | 4 ma    |

| 44         | TMOUT2   | I        |         |

| 45         | INTA-    | 0        | 4 ma    |

| 46         | HLDAOUT  | 0        | 4 ma    |

| 47         | RTCAS    | 0        | 4 ma    |

| 48         | DMAHRQ   | Ι        |         |

| 49         | ADSTB8   | I        |         |

| 50         | VSS      | I        |         |

| 51         | ADSTB16  | I        |         |

| 52         | AEN16-   | Ι        |         |

| 53         | AEN8-    | Ι        |         |

| 54         | MEMW-    | I/O      | 4 ma    |

| 55         | MEMR-    | I/O      | 4 ma    |

| 56         | IOR-     | I/O      | 4 ma    |

## 4.0 ET6000 Pin Driving Definition (Continued)

| Pin Number | Pin Name | I/О Туре | Driving |

|------------|----------|----------|---------|

| 57         | IOW-     | I/O      | 4 ma    |

| 58         | XA0      | I/O      | 4 ma    |

| 59         | XA1      | I/O      | 4 ma    |

| 60         | VDD      | I        |         |

| 61         | CD31     | I/O      | 4 ma    |

| 62         | CD30     | I/O      | 4 ma    |

| 63         | CD29     | I/O      | 4 ma    |

| 64         | CD28     | I/O      | 4 ma    |

| 65         | CD27     | I/O      | 4 ma    |

| 66         | CD26     | I/O      | 4 ma    |

| 67         | CD25     | I/O      | 4 ma    |

| 68         | CD24     | I/O      | 4 ma    |

| 69         | CD23     | I/O      | 4 ma    |

| 70         | VSS      | Ι        |         |

| 71         | CD22     | I/O      | 4 ma    |

| 72         | CD21     | I/O      | 4 ma    |

| 73         | CD20     | I/O      | 4 ma    |

| 74         | CD19     | I/O      | 4 ma    |

| 75         | CD18     | I/O      | 4 ma    |

| 76         | CD17     | I/O      | 4 ma    |

| 77         | CD16     | I/O      | 4 ma    |

| 78         | CD15     | I/O      | 4 ma    |

| 79         | CD14     | I/O      | 4 ma    |

| 80         | CD13     | I/O      | 4 ma    |

| 81         | NMI      | 0        | 4 ma    |

| 82         | CD12     | I/O      | 4 ma    |

| 83         | CD11     | I/O      | 4 ma    |

| 84         | CD10     | I/O      | 4 ma    |

## ETEQ Micro

### 4.0 ET6000 Pin Driving Definition (Continued)

| Pin Number | Pin Name | I/О Туре | Driving |

|------------|----------|----------|---------|

| 85         | CD9      | I/O      | 4 ma    |

| 86         | VSS      | Ι        |         |

| 87         | CD8      | I/O      | 4 ma    |

| 88         | CD7      | I/O      | 4 ma    |

| 89         | CD6      | I/O      | 4 ma    |

| 90         | CD5      | I/O      | 4 ma    |

| 91         | CD4      | I/O      | 4 ma    |

| 92         | CD3      | I/O      | 4 ma    |

| 93         | CD2      | I/O      | 4 ma    |

| 94         | CD1      | I/O      | 4 ma    |

| 95         | CD0      | I/O      | 4 ma    |

| 96         | A31      | Ι        |         |

| 97         | A24      | I/O      | 4 ma    |

| 98         | A23      | Ι        |         |

| 99         | A22      | I        |         |

| 100        | VDD      | I        |         |

| 101        | A21      | I        |         |

| 102        | A20      | Ι        |         |

| 103        | A19      | Ι        |         |

| 104        | A18      | Ι        |         |

| 105        | A17      | I        |         |

| 106        | A16      | I/O      | 4 ma    |

| 107        | A15      | I/O      | 4 ma    |

| 108        | A14      | I/O      | 4 ma    |

| 109        | A13      | I/O      | 4 ma    |

| 110        | A12      | I/O      | 4 ma    |

| 111        | A11      | I/O      | 4 ma    |

| 112        | A10      | I/O      | 4 ma    |

Rev 0.1 April 1992 Cheetah-486

Confidential

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer

## ETEQ Micro

## 4.0 ET6000 Pin Driving Definition (Continued)

| Pin Number | Pin Name | <b>І/О Туре</b> | Driving |

|------------|----------|-----------------|---------|

| 113        | VSS      | I               |         |

| 114        | A9       | I/O             | 4 ma    |

| 115        | A8       | I/O             | 4 ma    |

| 116        | A7       | I               |         |

| 117        | A6       | Ι               |         |

| 118        | A5       | Ι               |         |

| 119        | A4       | Ι               |         |

| 120        | A3       | Ι               |         |

| 121        | A2       | Ι               |         |

| 122        | BRDY-    | 0               | 12 ma   |

| 123        | RDY-     | 0               | 12 ma   |

| 124        | MAXD7    | I/O             | 6 ma    |

| 125        | MAXD6    | I/O             | 6 ma    |

| 126        | MAXD5    | I/O             | 6 ma    |

| 127        | MAXD4    | I/O             | 6 ma    |

| 128        | MAXD3    | I/O             | 6 ma    |

| 129        | MAXD2    | I/O             | 6 ma    |

| 130        | VSS      | Ι               |         |

| 131        | MAXD1    | I/O             | 6 ma    |

| 132        | MAXD0    | I/O             | 6 ma    |

| 133        | MAXD15   | I/O             | 6 ma    |

| 134        | MAXD14   | I/O             | 6 ma    |

| 135        | MAXD13   | I/O             | 6 ma    |

| 136        | MAXD12   | I/O             | 6 ma    |

| 137        | MAXD11   | I/O             | 6 ma    |

| 138        | MAXD10   | I/O             | 6 ma    |

| 139        | MAXD9    | I/O             | 6 ma    |

| 140        | MAXD8    | I/O             | 6 ma    |

### 4.0 ET6000 Pin Driving Definition (Continued)

| Pin Number | Pin Name | I/О Туре | Driving |

|------------|----------|----------|---------|

| 141        | ADS-     | 0        | 4 ma    |

| 142        | BLAST-   | I        |         |

| 143        | VDD      | I        |         |

| 144        | BS16-    | 0        | 4 ma    |

| 145        | RDYIN-   | Ι        |         |

| 146        | FERR-    | 0        |         |

| 147        | PHLDA    | 0        |         |

| 148        | WR-      | 0        | 4 ma    |

| 149        | BE0-     | 0        | 4 ma    |

| 150        | VSS      | I        |         |

| 151        | BE1-     | 0        | 4 ma    |

| 152        | BE2-     | 0        | 4 ma    |

| 153        | BE3-     | 0        | 4 ma    |

| 154        | MIO-     | 0        | 4 ma    |

| 155        | DC-      | 0        | 4 ma    |

| 156        | RESET3   | 0        | 12 ma   |

| 157        | KEN-     | 0        | 12 ma   |

| 158        | HOLD     | 0        | 4 ma    |

| 159        | IGNNE-   | 0        | 4 ma    |

| 160        | DWROMS-  | 0        | 6 ma    |

.

### 4.1 ET6000 Absolute Maximum Ragings

|                       | Symbol | Min  | Max | Units |

|-----------------------|--------|------|-----|-------|

| Supply Voltage        | VDD    |      | 7.0 | v     |

| Input Voltage         | VIN    | -0.5 | 5.5 | V     |

| Output Voltage        | VOUT   | -0.5 | 5.5 | v     |

| Operating Temperature | Тор    | -2.5 | 50  | C     |

| Storage Temperature   | Tstg   | -40  | 125 | C     |

## 4.2 82C490SX Operating Condition

|                     | Symbol | Min  | Max  | Units |

|---------------------|--------|------|------|-------|

| Supply Voltage      | VDD    | 4.75 | 5.25 | v     |

| Ambient Temperature | TA     | 0    | 50   | C     |

-

### 4.3 ET6000 DC Characteristics

|                                          | Symbol | Min | Max  | Units |

|------------------------------------------|--------|-----|------|-------|

| Input Low Voltage                        | VIL    |     |      |       |

| TTL Level (All pins except PWRGD)        |        |     | 0.8  | v     |

| SHMT Level (PWRGD pin)                   |        |     | 1.0  | v     |

| Input High Voltage                       | VIH    |     |      |       |

| TTL Level (All pins except PWRGD, TURBO- |        | 2.0 |      | v     |

| and CLK2IN)                              |        |     | ĺ    |       |

| CLK2IN Level                             |        | 3.7 |      | v     |

| SHMT Level (PWRGD and TURBO- pins)       |        | 4.0 |      | v     |

| Output Low Voltage                       | VOL    |     | 0.45 | v     |

| Output High Voltage                      | VOH    | 2.4 |      | V     |

| Input Low Current AT VIN=VSS             | IIL    | -10 | 10   | uA    |

| Input High Current AT VIN=VDD            | IIH    | -10 | 10   | uA    |

| Tri-State Output OFF Current LOW         | IOZL   |     | -10  | uA    |

| Tri-State Output OFF Current HIGH        | IOZH   |     | 10   | uA    |

| Output Leakage Current                   | IOH    |     | TBD  |       |

| Output Short Circuit Current             | IOS    |     | TBD  |       |

| Power Supply Current                     | EDD    |     |      |       |

| @20MHz                                   |        |     | 150  | mA    |

| @25MHz                                   |        |     | 200  | mA    |

| @33MHz                                   |        |     | 230  | mA    |

| Input Capacitance                        | CIN    |     | 7    | pF    |

| Output or I/O Capacitance                | COUT   |     | 10   | pF    |

### 4.3 ET6000 AC Characteristics

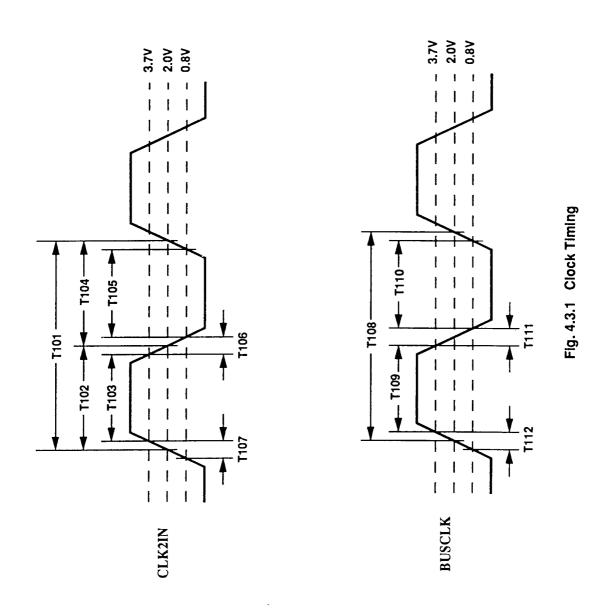

$(TA = 0 C \text{ to } 70 C, VDD = 5V \pm 5\%)$

| 4.3.1 Clock Timing              |      | 251 | <u>25MHz</u> |     | MHz | 50  | MHz |       |

|---------------------------------|------|-----|--------------|-----|-----|-----|-----|-------|

|                                 |      | Min | Мах          | Min | Max | Min | Мах | Units |

| CLK Period                      | T101 | 40  |              | 30  |     | 20  |     | ns    |

| CLK high time at 2.0v           | T102 | 14  |              | 12  |     | 8   |     | ns    |

| CLK high time at 3.7v           | T103 | 10  |              | 8   |     | 5   |     | ns    |

| CLK low time at 2.0v            | T104 | 14  |              | 12  |     | 8   |     | ns    |

| CLK low time at 0.8v            | T105 | 10  |              | 8   |     | 5   |     | ns    |

| CLK fall time (3.7v to 0.8v)    | T106 |     | 5            |     | 4   |     | 2   | ns    |

| CLK rise time (0.8v to 3.7v)    | T107 |     | 5            |     | 4   |     | 2   | ns    |

| BUSCLK Period                   | T108 | 80  | 240          | 61  | 182 | 40  | 120 | ns    |

| BUSCLK high time at 3.7v        | T109 | 47  |              | 15  |     | 12  |     | ns    |

| BUSCLK low time at 0.8v         | T110 | 47  |              | 15  |     | 12  |     | ns    |

| BUSCLK fall time (3.7v to 0.8v) | T111 |     | 8            |     | 6   |     | 5   | ns    |

| BUSCLK rise time (0.8v to 3.7v) | T112 |     | 8            |     | 6   |     | 5   | ns    |

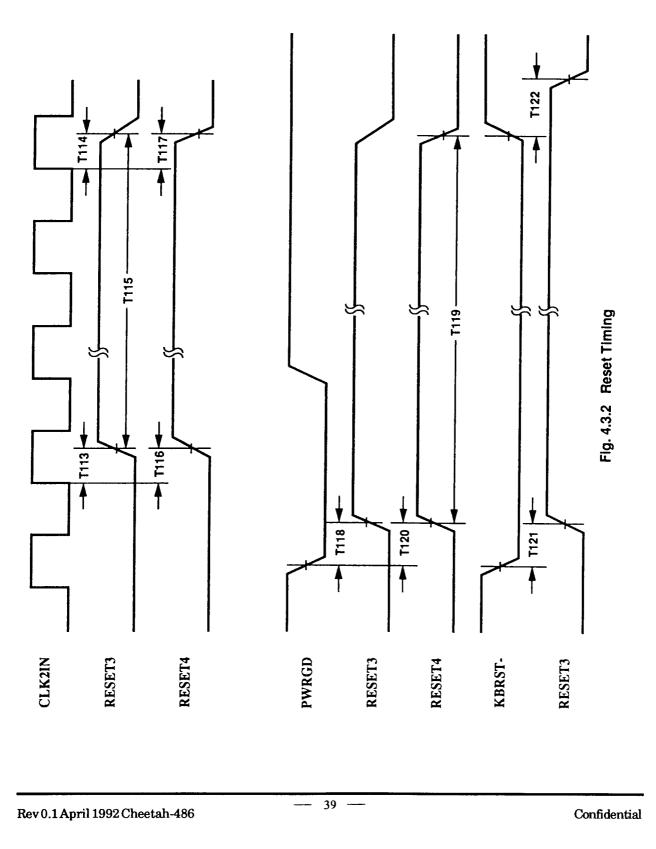

| 4.3.2 Reset Timing                  |          | 251 | <u>25MHz</u> |     | <u>33MHz</u> |     | ИНz |       |

|-------------------------------------|----------|-----|--------------|-----|--------------|-----|-----|-------|

|                                     | <u> </u> | Min | Мах          | Min | Мах          | Min | Мах | Units |

| RESET3 active delay from CLK high   | T113     |     | 13           |     | 10           |     | 7   | ns    |

| RESET3 inactive delay from CLK high | T114     | 3   | 13           |     | 10           |     | 7   | ns    |

| RESET3 Pulse Width                  | T115     | 40  |              | _40 |              | 40  |     | CLK   |

| RESET4 active delay from CLK high   | T116     |     | 30           |     | 24           |     | 15  | ns    |

Notes:

All AC timing parameters are specified under capacitive load of <u>85pF</u>, unless stated otherwise.

Rev 0.1 April 1992 Cheetah-486

| 4.3.2 Reset Timing (Continued)          | <u> </u> | <u>25MHz</u> |     | <u>33MHz</u> |     | <u>50MHz</u> |     |       |

|-----------------------------------------|----------|--------------|-----|--------------|-----|--------------|-----|-------|

|                                         |          | Min          | Max | Min          | Max | Min          | Мах | Units |

| RESET4 inactive delay from CLK high     | T117     |              | 30  |              | 24  |              | 15  | ns    |

| RESET3 active delay from PWRGD active   | T118     | 3            |     | 3            |     | 3            |     | CLK   |

| RESET4 Pulse Width                      | T119     | 40           |     | 40           |     | 40           |     | CLK   |

| RESET4 active delay drom PWRGD inactive | T120     | 2            |     | 2            |     | 2            |     | CLK   |

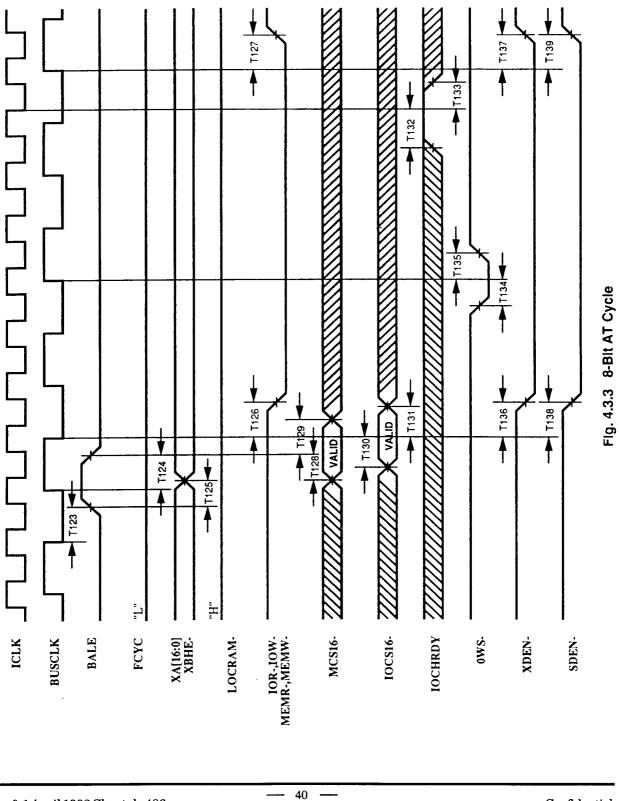

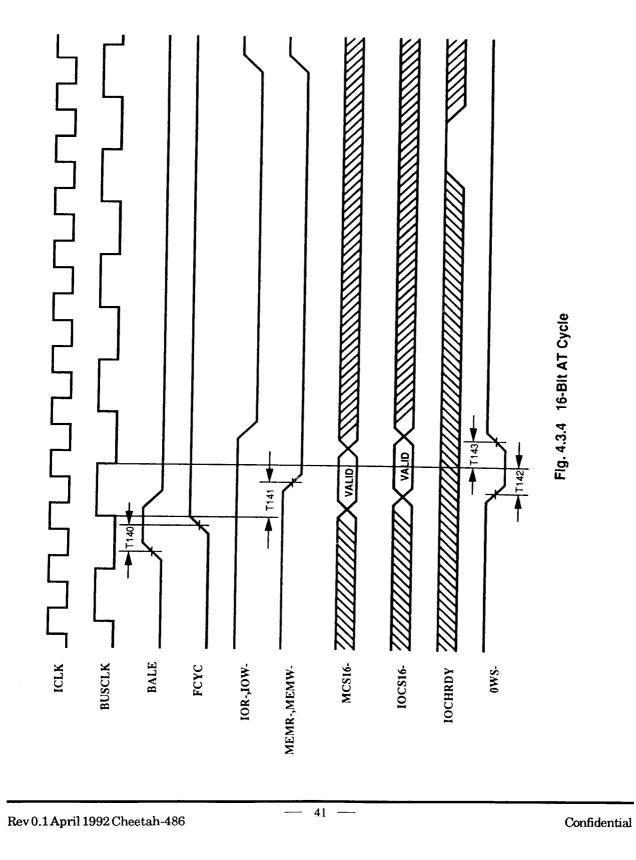

| 4.3.3 AT Cycle Timing                      |      | 251 | <u>25 MHz</u> |     | <u>33MHz</u> |     | <u>/Hz</u> |       |

|--------------------------------------------|------|-----|---------------|-----|--------------|-----|------------|-------|

|                                            |      | Min | Мах           | Min | Max          | Min | Max        | Units |

| BALE active from BUSCLK low                | T123 | 11  |               | 9   |              | 8   |            | ns    |

| BALE inactive from BUSCLK low              | T124 | 11  |               | 9   |              | 8   |            | ns    |

| XA[1:0],A[16:0],XBHE- valid from BALE high | T125 |     | 7             |     | 5            |     | 4          | ns    |

| Command active from BUSCLK low             | T126 |     | 8             |     | 6            |     | 5          | ns    |

| Command inactive from BUSCLK high          | T127 | 3   | 8             | 2   | 6            | 2   | 5          | ns    |

| MCS16- setup to BALE low                   | T128 | 20  |               | 15  |              | 13  |            | ns    |