### VL82C386SX SYSTEM CACHE CONTROLLER

#### **FEATURES**

- Optimized for TOPCAT 386SX and SCAMP-LT Chip Sets

- Improved i386SX<sup>TM</sup> and AM386SX<sup>TM</sup> system performance

- Fast look-aside architecture

- Zero wait state read hit access

- Reduces average processor wait states to near zero

- Multiple cache organizations

- Two-way set associative: 16KB

- Two-way set associative: 32KB

- Memory update strategy

- Write-thru

- Least recently used (LRU) replacement algorithm

- Integrates complete cache directory on-chip

- Supports memory configurations to 16 MB

- · Programmable cache architecture

- Block size: 8 or 16 bytes

- Line size: 2 bytes

- Update strategies: Single cycle (one line)

- · Write-protect region support

- Write-protect regions (#): 256

- Write-protect region size:

2KB between 512K and 1M

- Non-cacheable region support

- Non-cache regions (#): 504

- Non-cacheable region size:

64KB below 512K

2KB between 512K and 1M

64KB above 1M

- · 20 and 25 MHz operation

- Optimized for one or two dual 4K x 8 cache data RAMs

- Operates both in pipelined and in non-pipelined modes

- Built-in self-test and cache data RAM testability features

- · Auto-flush on EMS-update events

- 100-lead plastic quad flat pack (PQFP)

#### **OVERVIEW**

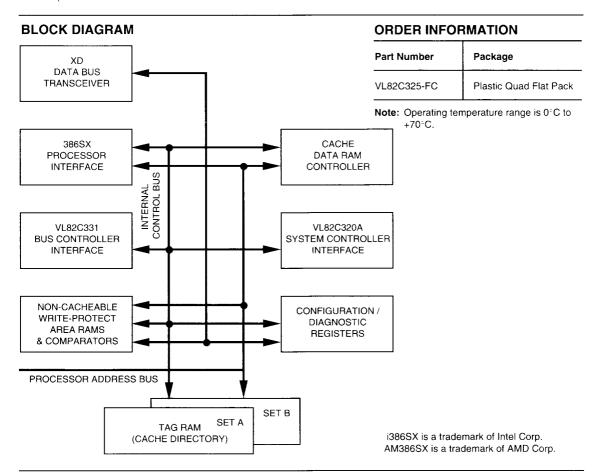

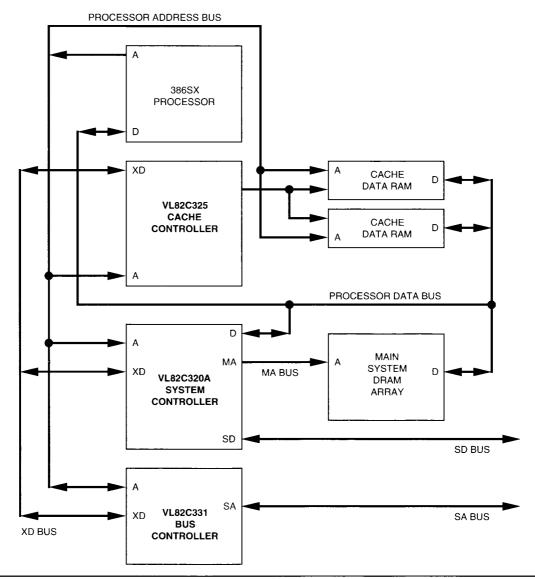

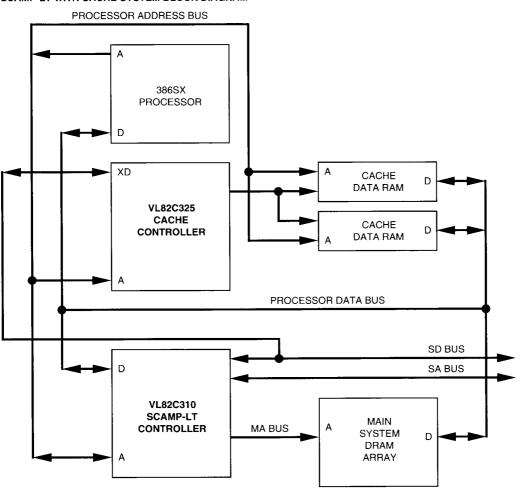

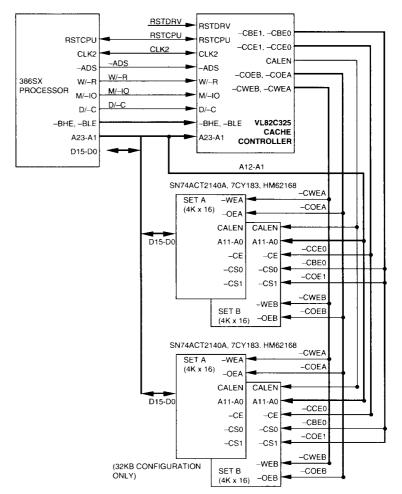

The VL82C325 Memory Cache Controller is a high performance, highly integrated Cache Controller for systems based on the VLSI Technology, Inc.'s TOPCAT 386SX or SCAMP-LT chip sets. To implement a 32KB two-way set associative cache subsystem, all that is required is the VL82C325 and two 8K x 16 cache data RAMs. The

VL82C325 has been designed to be an integral part of the TOPCAT386SX chip set. This feature improves the overall system performance by reducing the number of wait states during non-cache cycles when compared to Cache Controllers which must pipeline all cycles which can not be serviced by reading from the cache data RAM. The

VL82C320A TOPCAT System Controller or VL82C310 SCAMP System Controller, and the VL82C325 operate in parallel to decode 386SX requests. The System Controller starts decoding the 386SX cycle simultaneously with the VL82C325 and is therefore able to actually start a memory cycle before a miss indication is generated by the VL82C325.

#### TOPCAT WITH CACHE SYSTEM BLOCK DIAGRAM

The VL82C325 is a read allocate, writethru cache. It maintains cache coherency during non 386SX cycles by monitoring the VL82C320A/VL82C331 interface or VL82C310 SCAMP-LT interface and the system address bus. Any HLDA cycle which writes to a memory location which is also cached will invalidate the line. HLDA read cycles which result in a hit within the cache data have no effect. Read data for these cycles is not supplied by the cache data RAM.

The VL82C325 supports 16KB or 32KB two-way set associative caches. Onchip high speed SRAM is used for the cache directory which is organized as

two 1024 entry directories. The line size is two bytes. Each cache directory entry defines the storage allocation for a block which is set to be four lines for 16KB cache configurations or eight lines for 32KB caches. Each line or sub-block has its own valid bit within the cache directory entry.

System memory can be declared as cacheable or non-cacheable by setting or clearing entries in the Non-Cache Table (NCT). The NCT has 504 entries which cover all of system memory (memory controlled by the System Controller). In the area 512KB to 1MB. system memory is divided into 2KB regions. Each individual region can be

declared cacheable or non-cacheable. In the remaining areas of system memory, each 64KB region of memory can be individually selected as cacheable or non-cacheable.

System memory can be declared as write-protected (e.g., ROM space) by setting entries in the Write-Protect Table (WPT). The WPT has 256 entries which cover the area of system memory from 512KB to 1MB. Each individual 2KB region in this area can be declared write-protected. Writes to a write-protected region which result in a cache-hit will not update the contents of cache data RAM.

#### SCAMP-LT WITH CACHE SYSTEM BLOCK DIAGRAM

-CWEA

**VSSR**

-CBE0

-CBE1

NC

NC

HRQ

57

56

55

54

53

52

24

25

26

27

28

29

30 5 8 8

35 36 37 38 39 40 4 42 43 44 45 46 47 48 49 20 51

VDDR

M/-10 |

HH-

34

W/-B

HLDA

9

АЗ

Α2

Α1

**VSSR**

-BHE

-BLE

-FLUSH

#### **PIN DIAGRAM** VL82C325 -HIDRIVE -BUSBE1 VDDR CLK2 ΩQΛ VSSI XD5 XD7 XD6 8 66 86 97 96 95 8 88 88 98 85 84 83 82 81 94 93 92 91 87 NC 80 -MASTER 2 A22 **VSSR** 79 **VDDR** 3 78 XD4 4 A21 XD3 77 A20 5 **VDDR** 76 TOP A19 6 75 XD2 VIEW 7 A18 XD1 74 8 A17 73 VSSR 9 A16 XD0 72 10 A15 -RDYOUT 71 VSS 11 NC 70 12 A14 -MISS 69 13 A13 68 VSSR A12 14 -EALE 67 15 A11 -CCE1 66 16 A10 VSSI 65 17 Α9 -CCE0 64 18 **VDDI** 63 CALEN Α8 19 **VSSR** 62 20 Α7 61 -COEB 21 --COEA Α6 60 22 Α5 **VDDR** 59 23 Α4 58 -CWEB

#### SIGNAL DESCRIPTIONS

| Signal<br>Name | Pin<br>Number                      | Signal<br>Type | Signal<br>Description                                                                                                                                                                                                                                                                                                                                                    |

|----------------|------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU AND TIM    | ING INTREFACE                      | PINS           |                                                                                                                                                                                                                                                                                                                                                                          |

| A23-A1         | 2, 4-9,<br>10, 12-17<br>19-26, 100 | I-TTL          | Address bus bits 23 through 1 - These signals are tied to the processor's Address bus bits 23-1.                                                                                                                                                                                                                                                                         |

| –ВНЕ           | 28                                 | IO-TTL<br>8 mA | Byte High Enable - This signal is tied to the processor's Byte High Enable output. It is used to select the upper byte of a 16-bit wide memory or I/O location.                                                                                                                                                                                                          |

| -BLE           | 29                                 | IO-TTL<br>8 mA | Byte Low Enable - This signal is tied to the processor's Byte Low Enable output. It is used to select the lower byte of a 16-bit wide memory or I/O location.                                                                                                                                                                                                            |

| -ADS           | 37                                 | I-TTL          | Address Status - This signal is tied to the processor's -ADS output.                                                                                                                                                                                                                                                                                                     |

| W/-R           | 33                                 | i-TTL          | Write and Not Read - This signal is tied to the processor's W/-R output.                                                                                                                                                                                                                                                                                                 |

| M/-IO          | 36                                 | I-TTL          | Memory and Not I/O Cycle - This signal is tied to the processor's M/–IO output.                                                                                                                                                                                                                                                                                          |

| D/-C           | 34                                 | I-TTL          | Data and Not Code - This signal is tied to the processor's D/–C output.                                                                                                                                                                                                                                                                                                  |

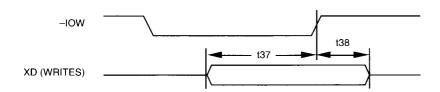

| HLDA           | 32                                 | I-TTL          | Hold Acknowledge - This input is generated by the 386SX CPU, and indicates that the current hold acknowledge cycle is for the DMA Controller or other Bus Master. When active, the VL82C325 ignores the CPU's status signals and monitors –MEMW to determine if the cycle will invalidate any cached item.                                                               |

| -BLKA20        | 42                                 | I-TTL          | Address Bit 20 Enable - This active low input is tied to the —BLKA20 output of the VL82C320A System Controller and is used to deactivate A20. It is a decode of the A20GATE signal from the Keyboard Controller and Port A bit 1. Port A bit 1 may be written directly or set by a dummy read of I/O port EE hex. Refer to the VL82C320A specification for more details. |

| -NCCYC         | 46                                 | I-TPU          | Non-Cache Cycle - This active low input may be driven by external circuitry during access to regions of memory which should not be cached. It is ignored during memory write, I/O, and halt/shutdown cycles.                                                                                                                                                             |

| -WPCYC         | 47                                 | I-TPU          | Write-Protect Cycle - This active low input may be driven by external circuitry during access to regions of memory for which cache data RAM should be write-protected. It is ignored during memory read, I/O, and halt/shutdown cycles.                                                                                                                                  |

| -RDYOUT        | 71                                 | IO-TL<br>8 mA  | VL82C325 Ready - This output is driven active for all cache read hits and diagnostic operations. It is an input in the In-Circuit Test (ICT) mode.                                                                                                                                                                                                                       |

| -RDYIN         | 45                                 | I-TTL          | Processor's Ready - This input is tied directly to the processor's READY input pin.                                                                                                                                                                                                                                                                                      |

| -FLUSH         | 30                                 | I-TPU          | Flush - This input is used to generate hardware-flush requests. When this input is driven active while the VL82C325 is enabled, the cache directory is flushed.                                                                                                                                                                                                          |

| HRQ            | 51                                 | I-TTL          | Hold Request - This input is tied to the processors HOLD input.                                                                                                                                                                                                                                                                                                          |

| CACHE DATA     | A RAM INTERFAC                     | CE PINS        |                                                                                                                                                                                                                                                                                                                                                                          |

| -CWEA          | 57                                 | IO-TL<br>8 mA  | Cache RAM Write Enable A - This output is active low and is tied to the write enable(s) of the first set (A) of cache data RAMs. It is an input in the In-Circuit Test (ICT) mode.                                                                                                                                                                                       |

| -CWEB          | 58                                 | IO-TL<br>8 mA  | Cache RAM Write Enable B - This output is active low and is tied to the write enable(s) of the second set (B) of cache data RAMs. It is an input in the In-Circuit Test (ICT) mode.                                                                                                                                                                                      |

### **SIGNAL DESCRIPTIONS (Cont.)**

| Signal<br>Name | Pin<br>Number                   | Signal<br>Type     | Signal<br>Description                                                                                                                                                                                                                                                                                                   |  |

|----------------|---------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -COEA          | 60                              | IO-TL<br>8 mA      | Cache RAM Output Enable A - An active low signal which is tied to the output enable(s) of the first set (A) of cache data RAMs. It is an input in the In-Circuit Test (ICT) mode.                                                                                                                                       |  |

| -COEB          | 61                              | IO-TL<br>8 mA      | Cache RAM Output Enable B - This active low signal which is tied to the output enable(s) of the second set (B) of cache data RAMs. It is an input in the In-Circuit Test (ICT) mode.                                                                                                                                    |  |

| CALEN          | 63                              | IO-TL<br>8 mA      | Cache RAM Address Latch Enable - An active high signal which opens the input address latches on all of the cache data RAMs. It is an input in the In-Circuit Test (ICT) mode.                                                                                                                                           |  |

| -CCE0          | 64                              | O<br>8 mA          | Cache RAM Chip Enable 0 - An active low signal which is tied to the chip enable(s) of the least significant 16KB of cache data memory.                                                                                                                                                                                  |  |

| -CCE1          | 66                              | O<br>8 mA          | Cache RAM Chip Enable 1 - An active low signal which is tied to the chip enable(s) of the most significant 16KB of cache memory. This pin is not connected in the 16KB configuration.                                                                                                                                   |  |

| -CBE0          | 55                              | O<br>8 mA          | Cache RAM Byte Enable 0 - An active low signal which is tied to the chip select(s) of the cache data RAMs corresponding to data bits 0-8.                                                                                                                                                                               |  |

| -CBE1          | 54                              | O<br>8 mA          | Cache RAM Byte Enable 1 - An active low signal which is tied to the chip select(s) of the cache data RAMs corresponding to data bits 8-15.                                                                                                                                                                              |  |

| SYSTEM ANI     | BUS CONTROL                     | LER INTERFACE      | PINS                                                                                                                                                                                                                                                                                                                    |  |

| XD7- XD0       | 72, 74,<br>75, 77,<br>78, 82-84 | IO-TTL<br>12/24 mA | X Data Bus - These signals are tied to the XD bus in TOPCAT systems and the SD bus in SCAMP systems. This bus is used to read and write the VL82C325's internal configuration registers.                                                                                                                                |  |

| -MISS          | 69                              | IO-TL<br>8 mA      | Miss - This active low output indicates that the current memory cycle request can not be serviced by the VL82C325. It is an input in the In-Circuit-Test (ICT) mode.                                                                                                                                                    |  |

| -EALE          | 67                              | O<br>8 mA          | Bus ALE - This output is tied to the –EALE input of the VL82C331 Bus Controller. It is used to strobe the byte enables into the Bus Controller.                                                                                                                                                                         |  |

| RSTDRV         | 40                              | I-TTL              | Power-on Reset Input - This active high input is driven by the VL82C331 Bus Controller's RSTDRV output. It indicates that a hardware reset signal has been activated. This is the same signal which is output to the ISA bus. This signal is used as the power-on reset source and is used to reset all internal logic. |  |

| RESCPU         | 41                              | I-TTL              | Reset CPU - This input signal is tied directly to the processor's RESET input. It is used by the VL82C325 to synchronize its internal clock to the processor's clock. The internal configuration registers are not initialized from RESCPU.                                                                             |  |

| CLK2           | 86                              | I-CMOS             | Clock - This signal is tied to the processor's clock input.                                                                                                                                                                                                                                                             |  |

| –TRI           | 38                              | I-TPU              | Three-state - This input is used to put all of the VL82C325's outputs and bidirectional pins into the three-state mode for testing.                                                                                                                                                                                     |  |

| -MEMW          | 44                              | I-TTL              | Memory Write - This input is driven by the –MEMW signal from the VL82C331 Bus Controller. When it is active during hold acknowledge, it indicates that a write operation is taking place to system memory during DMA or Bus Master operations.                                                                          |  |

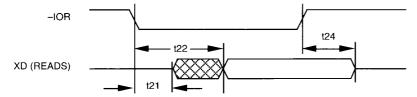

| -IOR           | 49                              | I-TTL              | I/O Read - This input is driven by the –IOR signal from the Bus Control It indicates that an I/O read operation is taking place. The VL82C325 internal configuration registers are accessed via I/O reads and writes.                                                                                                   |  |

### ADVANCE INFORMATION

### VL82C325

### SIGNAL DESCRIPTIONS (Cont.)

| Signal<br>Name | Pin<br>Number                                      | Signal<br>Type | Signal<br>Description                                                                                                                                                                                                                                                              |

|----------------|----------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| –IOW           | 50                                                 | I-TTL          | I/O Write - This input is driven by the –IOW signal from the Bus Controller. It indicates that an I/O write operation is taking place. The VL82C325's internal configuration registers are accessed via I/O reads and writes.                                                      |

| -HIDRIVE       | 81                                                 | I-TPU          | High Drive - This input is a wire-strap option. When low, the XD7-XD0 outputs will sink the full 24 mA. When high, they sink 12 mA. Note that all AC specifications are specified at 24 mA drive. —HIDRIVE has an internal pull-up and can be left open if 12 mA drive is desired. |

| -BUSBE0        | 88                                                 | IO-TTL<br>8 mA | Bus Byte Enable 0 - An active low output which drives the –BE0/A0 input of the VL82C331 Bus Controller. It indicates that the low byte of the processor's data bus (D7-D0) is to be used in this cycle.                                                                            |

| -BUSBE1        | 89                                                 | IO-TTL<br>8 mA | Bus Byte Enable 1 - An active low output which drives the –BE1/–BHE input of the VL82C331 Bus Controller. It indicates that the high byte of the processor's data bus (D15-D8) is to be used in this cycle.                                                                        |

| -MASTER        | 80                                                 | I-TPU          | Master - This input is tied to the Bus Controller's –MASTER input. It permits Master mode DMA access to the VL82C325's internal configuration registers. If Master mode access is not desired, then this pin can be left unconnected or pulled up.                                 |

| POWER SUP      | PLIES AND "NO                                      | CONNECT" PINS  |                                                                                                                                                                                                                                                                                    |

| VDDR           | 3, 35, 59,<br>76, 87                               | PWR            | I/O Ring Power Supply inputs, nominally +5 V.                                                                                                                                                                                                                                      |

| VSSR           | 27, 48, 56,<br>62, 68, 73,<br>79, 85               | GND            | I/O Ring Ground returns, nominally 0 V.                                                                                                                                                                                                                                            |

| VDDI           | 18, 43, 95                                         | PWR            | Internal Power Supply inputs, nominally +5 V.                                                                                                                                                                                                                                      |

| VSSI           | 1, 11, 39<br>65, 92                                | GND            | Internal Ground returns, nominally 0 V.                                                                                                                                                                                                                                            |

| NC             | 31, 52, 53,<br>70, 90, 91,<br>93, 94, 96<br>97, 99 |                | No Connects - All "no connects" must be left unconnected. Never connect these pins to signal nets or to power nets.                                                                                                                                                                |

### ADVANCE INFORMATION

VL82C325

#### SIGNAL LEGEND

| Signal<br>Type | Description                                         | Signal<br>Type | Description                          |

|----------------|-----------------------------------------------------|----------------|--------------------------------------|

| I-TTL          | TTL level input                                     | O-OD           | Open drain                           |

| I-TPD          | Input with 30k ohm pull-down resistor               | 0              | CMOS and TTL level compatible output |

| I-TPU          | Input with 30k ohm pull-up resistor                 | O-TTL          | TTL level output                     |

| I-TSPU         | Schmitt-trigger input with 30k ohm pull-up resistor | O-TS           | Three-state level output             |

| I-CMOS         | CMOS level input                                    | 11             | Input used for testing               |

| IO-TL          | TTL level input/output                              | GND            | Ground                               |

| IT-OD          | TTL level input/open drain output                   | PWR            | Power                                |

| IO-OD          | Input/open drain, slow turn-on                      |                |                                      |

#### **DEFINITION OF TERMS**

For the sake of consistency, a set of definitions is included here. These terms are organized in a top-down manner as they are typically used to describe the hierarchy of the VL82C325's internal tag storage.

Associativity The number of entries in a

cache to which one address could possibly be mapped, e.g., in a oneway controller each address maps to one location only, while in a twoway controller, each address could be in one of two locations.

Block

Set The set of tags is the

highest level of the cache memory organization hierarchy. There is one set for each degree of associativity, so a two-way set associative cache has two sets of tags which are all accessed in parallel in the Controller. Each set is made of a number of

This is the second level of hierarchy, it consists of a number of items (sub-

blocks and sub-blocks.

blocks or lines) which all

Line

Sub-block

Write-thru

share the same values in the upper bit of their addresses. Typically there is one tag RAM entry for each block, and there are multiple sub-blocks/block.

This is the third level (lowest) of the hierarchy. It is the smallest amount of memory which is updated at once. In singlechip cache controllers this is the same as a line. since there can be fewer bits of total tag storage required with this third level of hierarchy.

Same as sub-block for integrated caches (three levels of hierarchy), for direct mapped caches with external tag storage (two levels), it is the same as a block. A line may be longer than the data bus width of the processor.

This policy forces a write cycle to external memory (DRAM) for each write performed by the processor. The cache data RAM (SRAM) might or might

not be updated with the contents of the write.

Read-An update policy which allocate allows cache blocks to be

> allocated only on readmiss cycles. Write-miss cycles do not allocate space in the cache

directory.

Look-aside This policy enables a cycle to be started in the System Controller, in

parallel with the VL82C325, even before cache hit-miss has been determined. This can reduce average cache-

miss cycle times.

LRU

Leat Recently Used refers to the algorithm which is used to replace items in the cache. In a two-way set associative cache there are two candidates for replacement (one in

> each set). That candidate which least recently generated a cache hit (read or write) will be chosen for replacement.

#### **FUNCTIONAL DESCRIPTION**

#### RESPONSE TO CYCLE TYPES

The VL82C325 will cache only the memory which exists in the main memory controlled by the VL82C320A System Controller. This includes all memory segments which have been shadowed as well as memory (ROM or RAM) which exists on the ISA Bus.

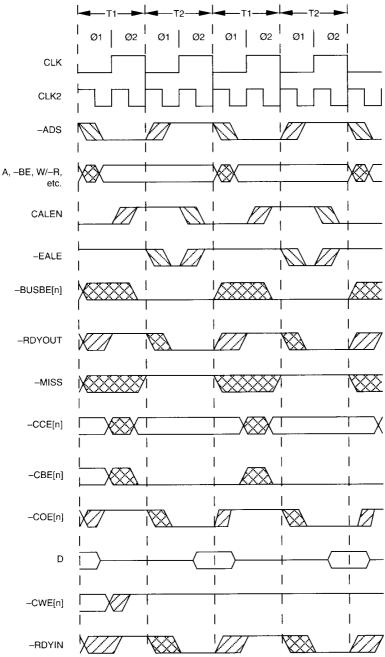

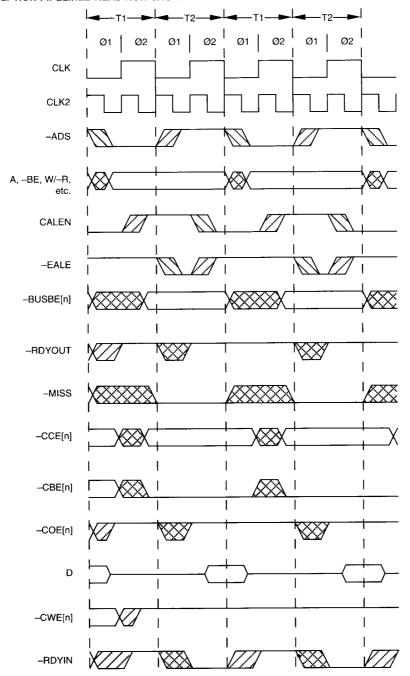

The VL82C325 is a look-aside Cache Controller. It operates in conjunction with the System Controller. The System Controller is able to begin a cycle in main memory while the VL82C325 simultaneously determines whether the cycle hit or missed in the cache data memory.

If a cache miss occurs and the cycle is cacheable, then the VL82C325 disables the cache data RAMs outputs, and allows the System Controller to complete the cycle. This is accomplished by asserting the –MISS signal to the System Controller. The System Controller is responsible for terminating miss cycles with READY.

If the cycle was a read, then the VL82C325 allocates a block for the new data in the cache directory. At the end of the cycle, the VL82C325 writes the new data into the cache data RAMs.

If the cycle was a write, then the VL82C325 does nothing, because directory space is only allocated on read-miss cycles (read-allocate).

If a cache hit occurs, then the VL82C325 must complete the cycle in the cache data RAMs, i.e., it reads from or writes to cache data memory.

If the cycle was a read, then the cycle in the System Controller must be aborted. This is accomplished by negating the —MISS signal to the System Controller (indicating a hit). In this case, the VL82C325 must terminate the cycle with READY because the aborted cycle in the System Controller will not provide a READY.

If the cycle was a write, then the cycle in the System Controller is allowed to complete as normal (write-thru), and the

data is simultaneously written into the cache data RAMs. This maintains coherency between main memory and cache data memory. In this case, the state of the –MISS signal is ignored by the System Controller. The System Controller provides the READY.

The VL82C325 will assert –MISS during non-cacheable read cycles. All such cycles must complete in the System Controller. Data is not read from cache data RAMs, and the cache directory is unaltered. Write cycles are always considered to be cacheable.

The VL82C325 never allocates cache space for HLDA cycles. However, if a HLDA write hits in the cache, then some action must be taken to prevent the cache data memory from becoming stale. Therefore, the cache directory valid bit for that line is invalidated. The remaining valid bits for the other lines in the same block are unaltered.

Tables 1 and 2 summarize the VL82C325's and System Controller's responses to all cycle types.

### **TABLE 1. RESPONSE TO CPU CYCLES**

|       |      | Bus Cyc | le Type              |                                         |             | Cache        | Response      | )            |                                                                          |

|-------|------|---------|----------------------|-----------------------------------------|-------------|--------------|---------------|--------------|--------------------------------------------------------------------------|

| M/–IO | D/-C | W/–R    | 386 Cycle            | Conditions                              | -MISS       | Cnfig<br>Reg | Data<br>RAM   | Direc<br>RAM | VL82C320A Response                                                       |

| 0     | 0    | 0       | INTA                 |                                         | 0           |              |               |              | INTA to '331                                                             |

| 0     | 0    | 1       | Undefined            |                                         | 0           |              |               |              | Halt/shutdown                                                            |

| 0     | 1    | 0       | I/O read             | '325 Reg<br>Other                       | 0           | Read         |               |              | I/O read to '331                                                         |

| 0     | 1    | 1       | I/O write            | '325 Reg<br>Other                       | 0           | Write        |               |              | I/O write to '331                                                        |

| 1     | 0    | 0       | Memory<br>code read  | Hit<br>Miss<br>Non-cache                | 1<br>0<br>0 |              | Read<br>Write | Update       | Aborted memory read<br>Memory read (16, 2x8)                             |

| 1     | 0    | 1       | Halt/shutdown        |                                         | 0           |              |               |              | Halt/shutdown                                                            |

| 1     | 1    | 0       | Memory<br>data read  | Hit<br>Miss<br>Non-cache                | 1<br>0<br>0 |              | Read<br>Write | Update       | Aborted memory read<br>Memory read (16, 2x8)<br>Memory read (8, 16, 2x8) |

| 1     | 1    | 1       | Memory<br>data write | Hit/writeable<br>Hit/write-prot<br>Miss | 0<br>0<br>0 |              | Write         |              | Memory Write (8, 16, 2x8)                                                |

#### **TABLE 2. RESPONSE TO HLDA CYCLES**

| Bus Cycle Type | Cache Response |       |              |             |              |

|----------------|----------------|-------|--------------|-------------|--------------|

| 386 Cycle      | Conditions     | -MISS | Cnfig<br>Reg | Data<br>RAM | Direc<br>RAM |

| Memory read    |                | 0     |              |             |              |

| Memory Wite    | Hit<br>Miss    | 0 0   |              |             | Invalidate   |

| I/O read       |                | 0     |              |             |              |

| I/O write      |                | 0     |              |             |              |

### ADVANCE INFORMATION

VL82C325

#### **CACHE ORGANIZATION**

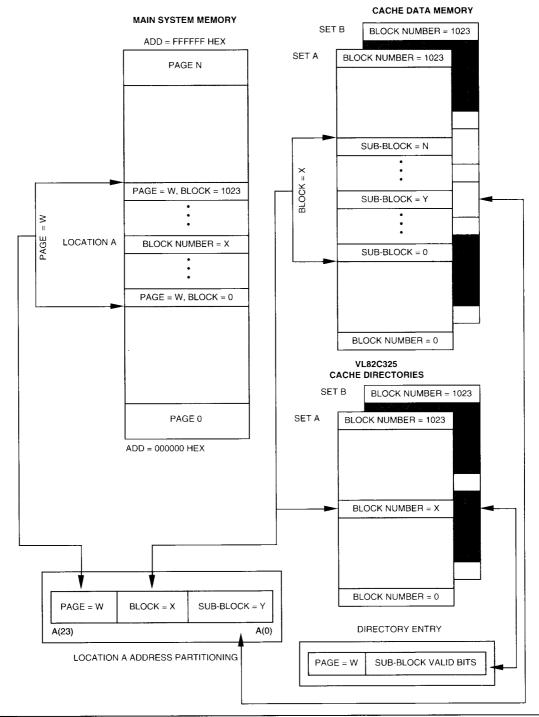

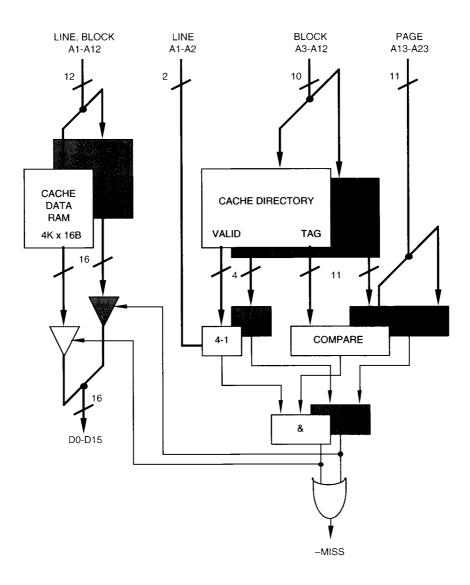

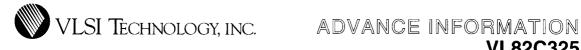

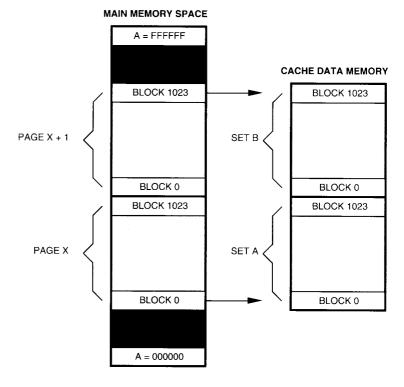

The VL82C325 is a two-way set associative Cache Controller. It supports cache sizes of either 16KB or 32KB, arranged as 2 x 4K x 16-bit or 4 x 4K x 16-bit respectively (refer to Figure 4). Table 3 gives a summary of the cache directory structure in each mode.

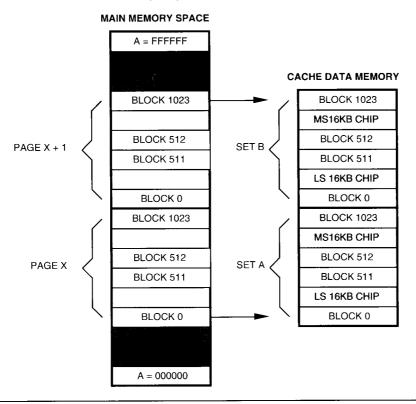

Figure 1 depicts the manner in which main memory maps to the cache data memory. Main memory is divided into pages, each page being the size of one set of cache data memory. Pages are further divided into 1024 blocks each. A block of main memory at offset X in page W always maps to a block at offset X in either of set A or set B of

cache data memory. Because there are two sets, two such block Xs (each from a different page) may reside in cache data memory simultaneously. However, if a third access is made to yet another block having offset X in a third and different page, then one of the original blocks is discarded to make space for the new one. A least recently used (LRU) algorithm is used to determine whether it will map to set A or to set B.

The page number associated with each cached block is retained in the cache directory. The directory contains one entry per block. Thus, there are two directories (one for each set) each containing 1024 entries.

Blocks are further divided into subblocks or lines. Each directory entry also contains a valid bit per sub-block. The sub-block valid bits reduce the number of accesses to main store by allowing the VL82C325 to fetch only those lines which have been requested by the processor.

Hit/miss is determined as follows:

The block number of the memory address is used to extract an entry from each of the set directories. The memory address is then compared to each entry in parallel. If either entry compares true, then a hit has occurred. It is not possible for both entries to compare true. The look-up function is depicted in Figures 2 and 3.

#### TABLE 3. CACHE DIRECTORY CONFIGURATIONS

| Cache<br>Size<br>(KB) | # of<br>Sets | Block<br>Size<br>(B) | Sub-Block<br>Size<br>(Line) (B) | Page<br>Size<br>(KB) | # of<br>Pages | # of<br>Directory<br>Entries per Set |

|-----------------------|--------------|----------------------|---------------------------------|----------------------|---------------|--------------------------------------|

| 16                    | 2            | 8                    | 2                               | 8                    | 2048          | 1024                                 |

| 32                    | 2            | 16                   | 2                               | 16                   | 1024          | 1024                                 |

FIGURE 1. TWO-WAY SET ASSOCIATIVE CACHE ORGANIZATION

#### FIGURE 2. 16KB CACHE LOOK-UP

#### FIGURE 3. 32KB CACHE LOOK-UP

#### NON-CACHEABLE & WRITE-PROTECT REGIONS

Sometimes it is undesirable to cache certain areas of memory, e.g., areas who's contents may change invisibly to the processors local bus. Examples are I/O controllers or dual ported memories in multi-processor systems. Two mechanisms are provided for the definition of non-cacheable regions:

The first is a dedicated input signal to the Controller. The user may decode non-cacheable addresses outside the Controller, and provided that the –NCCYC signal is asserted with the correct timing, then the cycle will be treated as non-cacheable.

In addition, non-cacheable regions can be user-defined in a look-up table within the VL82C325. Non-cacheable regions can be established in 2KB increments in area A (between 512KB and 1MB), and in 64KB increments in area B (below 512KB or above 1MB). Immediately following power-on reset, all of memory is configured to be cacheable.

It may also be necessary to declare certain areas of memory write-protected. For example, when caching ROM. Two mechanisms are provided for the definition of write-protected regions:

The first is a dedicated input signal to the Controller. The user may decode write-protected addresses outside the Controller, and provided that the —WPCYC signal is asserted with the correct timing, then the cycle will be treated as write-protected.

In addition, write-protected regions can be user-defined in a look-up table within the Cache Controller. Write-protect regions can be established in 2KB increments in area A (between 512KB and 1MB). Write-protect regions cannot be established in area B of system memory. Immediately following poweron reset, all of memory is configured to be non-write-protected.

Prior to enabling the VL82C325 by setting the CENA bit, in the Cache Configuration Register the bits corresponding to the non-cacheable regions and to write-protect regions should be set, as desired, in the Non-Cache Table (NCT) and in the Write-Protect Table (WPT) respectively.

Prior to setting up the NCT/WPT, the NCTPGM bit in the Cache Control Register (CCTRL) must be set to a 1 to enable programming of the tables. After all non-cache areas and write-protect areas are defined, NCTPGM should be cleared and the NCTENA, bit

of the CCTRL, should be set to enable the NCT/WPT comparators. Table 4 shows how the NCT/WPT tables interact with the W/-R, -NCCYC, and -WPCYC pins and with the NCTENA bit in the CCTRL register.

#### TABLE 4. NCT/WPT INTERACTION WITH OTHER SIGNALS

| W/–R |   | -NCT<br>ENA | NCT | Cacheable (?) | -WP<br>CYC | NCT<br>ENA | WPT | Writeable<br>(?) |

|------|---|-------------|-----|---------------|------------|------------|-----|------------------|

| 1    | × | x           | х   | Y             | 0          | х          | Х   | N                |

| 0    | 0 | ×           | Х   | Ν             | 1          | 0          | Х   | Υ                |

| 0    | 1 | 0           | Х   | Y             | 1          | 1          | 0   | Y                |

| 0    | 1 | 1           | 0   | Y             | 1          | 1          | 1   | N                |

| 0    | 1 | 1           | 1   | N             |            |            |     |                  |

#### TABLE 5. NCT/WPT (AREA A) DEFINITION

512KB ≤ MAIN MEMORY ADDRESS < 1M

| Offset<br>(Hex) | NON-CACHE<br>D7 D6 | REGION START<br>D5 D4 | ING ADDRESS IN<br>D3 D2 | HEX, A | 23-A0<br>D0 |

|-----------------|--------------------|-----------------------|-------------------------|--------|-------------|

| 00              | 081800             | 081000                | 080800                  | 080    | 000         |

| 01              | 083800             | 083000                | 082800                  | 082000 |             |

| •               | •                  | •                     | •                       |        | •           |

| •               | •                  | •                     | •                       |        | •           |

| •               | •                  | •                     | •                       | ,      | •           |

| 3E              | 0FD800             | 0FD000                | 0FC800                  | 0FC    | 000         |

| 3F              | 0FF800             | 0FF000                | 0FE800                  | 0FE    | 000         |

|                 |                    |                       | -                       | WPT    | NCT         |

### **TABLE 6. NCT (AREA B) DEFINITION**

MAIN MEMORY ADDRESS < 512KB or  $\geq 1M$

| Offset<br>(Hex) | NON- | CACHE I               | REGION D5 | STARTIN<br>D4 | IG ADDR | ESS IN I | HEX, A-2<br>D1 | 3-A16<br>D0 |  |  |  |

|-----------------|------|-----------------------|-----------|---------------|---------|----------|----------------|-------------|--|--|--|

| 00              | 07   | 06                    | 05        | 04            | 03      | 02       | 01             | 00          |  |  |  |

| 01              |      | Not used (see Area A) |           |               |         |          |                |             |  |  |  |

| 02              | 17   | 16                    | 15        | 14            | 13      | 12       | 11             | 10          |  |  |  |

| 03              | 1F   | 1E                    | 1D        | 1C            | 1B      | 1A       | 19             | 18          |  |  |  |

| •               | •    | •                     | •         | •             | •       | •        | ٠              | •           |  |  |  |

| •               | •    | •                     |           | •             | •       | •        | •              | •           |  |  |  |

| •               | •    | •                     | •         | •             | •       | •        | •              | •           |  |  |  |

| 1E              | F7   | F6                    | F5        | F4            | F3      | F2       | F1             | F0          |  |  |  |

| 1F              | FF   | FE                    | FD        | FC            | FB      | FA       | F9             | F8          |  |  |  |

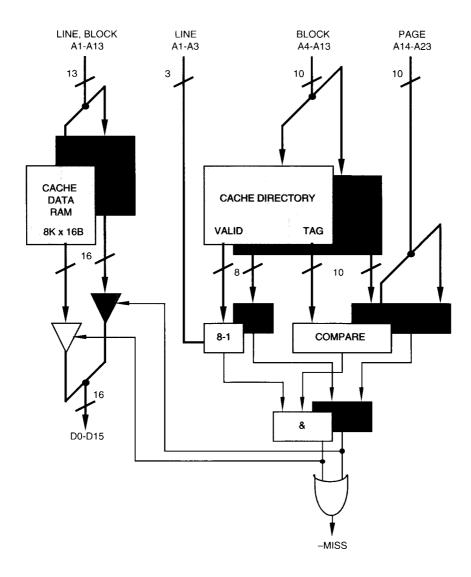

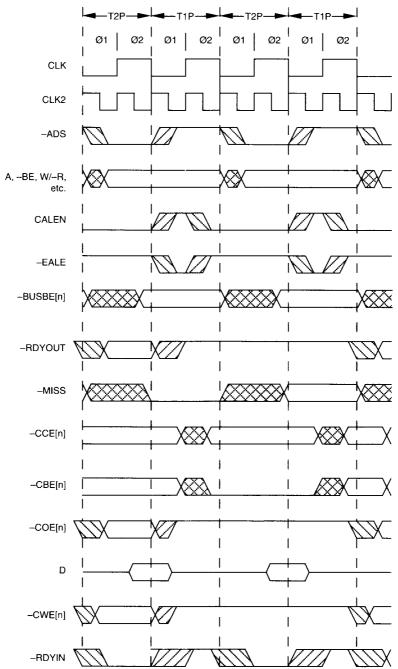

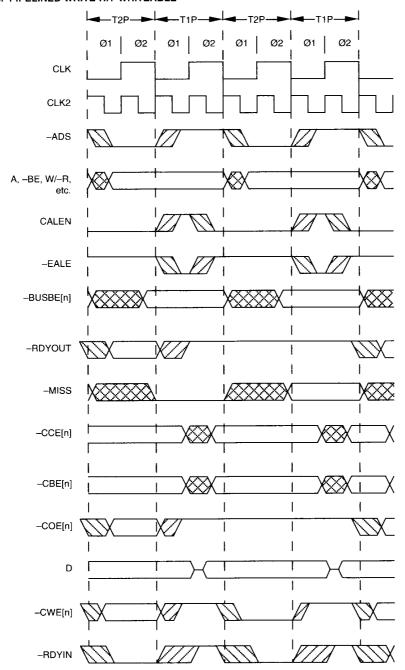

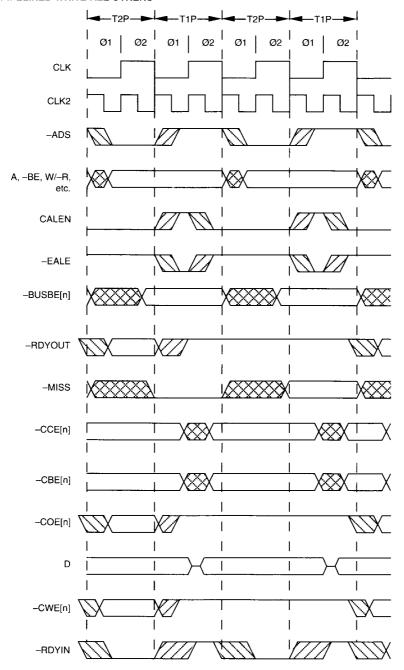

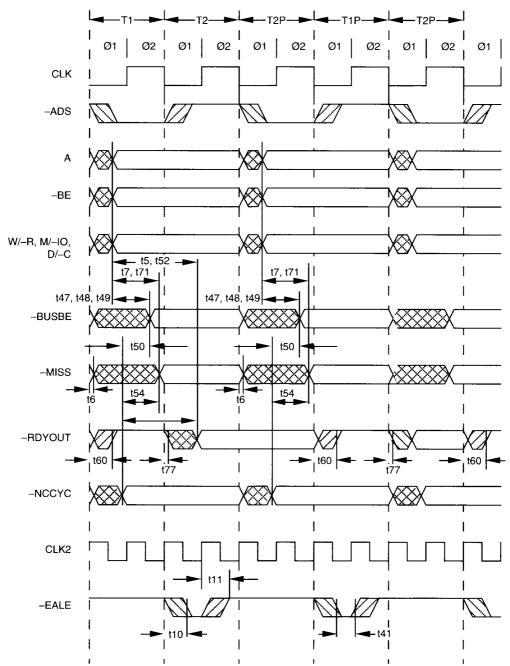

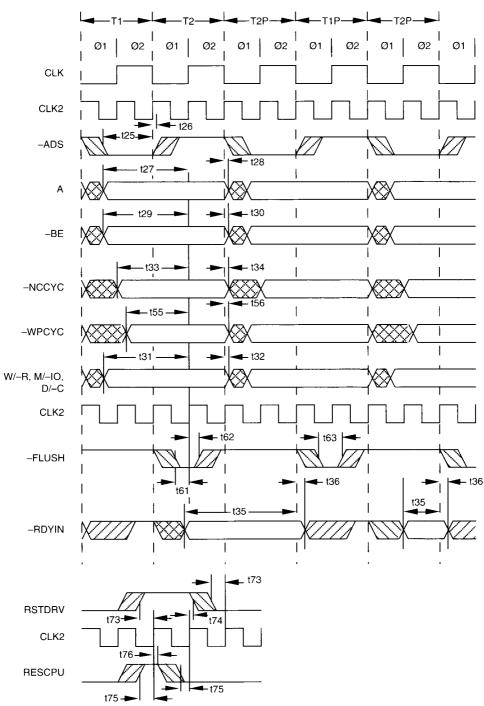

#### **CPU AND TOPCAT INTERFACES**

#### 386SX PROCESSOR INTERFACE

The VL82C325 monitors the 386SX bus cycle definition signals to determine which cycles it can service totally (memory reads from Cache Data RAM) or must participate in (cache miss etc.). Figure 4 illustrates the interconnect between the processor and the VL82C325. The processor and the VL82C325 share the same CLK2 signal.

The VL82C325 has two reset input signals. RSTDRV is used as the global power-on reset signal within the VL82C325 and when it is asserted, it causes all the internal registers and state machines to assume their initialization state. Any data stored in an internal register, directory, or NCT will be lost and must be restored after RSTDRV has been negated. RSTCPU is used to synchronize the VL82C325's internal processor state machines to CLK2 and the 386SX processor. Asserting RSTCPU with RSTDRV not asserted does not initialize the VL82C325's Configuration/Control Registers, directory or NCT.

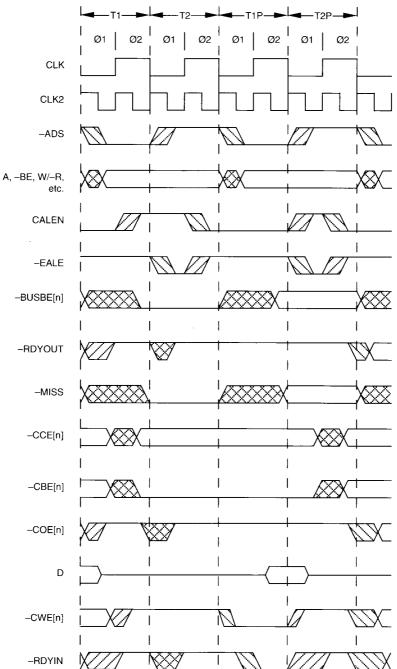

The 386SX processor's Next Address Request (–NA) input may be driven according to the rules of the 386SX CPU. The VL82C325 does not control –NA, but it will operate both in pipelined and in non-pipelined modes.

When one of the VL82C325's internal registers is referenced by the 386SX, the peripheral data bus is used for the data transfer (XD bus). I/O read and write cycles are used for these transfers; all of which execute with slot bus type cycle timing.

# VL82C320A SYSTEM CONTROLLER INTERFACE

The System Controller is responsible for executing all on-board cycles (DRAM). When a cycle misses in the cache, the System Contoller may have to complete the cycle. In order to minimize the average wait states of miss cycles, the VL82C320A System Controller starts to decode the cycle even before the VL82C325 indicates a miss. The VL82C325 issues the –MISS signal to the System Controller which then aborts the cycle on a cache hit or allows the System Controller to continue on miss and write cycles.

During a read-hit, the VL82C325 will provide the READY to terminate the cycle. However, for cycles which complete in the System Controller, the System Controller must terminate the cycle. The CPU's READY input signal indicates to the VL82C325 that the cycle is complete and that the data is available on the data bus (read cycles). The VL82C325 can then negate the write strobe to the cache data memories to update the cache during cacheable read-misses.

The VL82C325's internal configuration registers are accessed via I/O reads and writes. During these cycles, the data is transferred to/from the CPU by means of the peripheral data bus (XD7-XD0 bus). The VL82C325's Configuration Registers are not accessible during DMA cycles, but may be made accessable in Master mode DMA cycles by connecting the –MASTER input signal.

## VL82C331 BUS CONTROLLER INTERFACE

The Bus Controller is responsible for executing all off-board cycles (includes ROM and I/O cycles which are considered off-board). When a cycle misses in the cache, the Bus Controller may have to complete the cycle. The Bus Controller is not connected to the VL82C325's –MISS signal, so it can not tell whether the cycle was a hit or a miss. However, it is "slaved" to the System Controller, and so the System Controller will not command the Bus Controller on cache hit cycles.

During read-miss cycles the VL82C325 requires that a full 16-bit line be fetched, even if the CPU asked only for a single byte. The Bus Controller's byte enable inputs are generated by the VL82C325 (–BUSBE1, –BUSBE0). The VL82C325 converts 8-bit readmisses to 16-bit reads by manipulating the Bus Controller's byte enables. The cycle is converted to 16-bit only if the address of the cycle is determined to be in a cacheable region. Tables 7 and 8 summarizes the conversions for various cycle types.

The VL82C325 also supplies the –EALE signal to the Bus Controller. This ensures that the Bus Controller samples the VL82C325 generated byte enables with the correct timing.

During HLDA cycles, the Bus Controller must control the CPU's byte enables. Therefore, the VL82C325 reverses the direction on its –BHE, –BLE, and –BUSBE1, –BUSBE0 pins; allowing the Bus Controller to drive the byte enables through the VL82C325.

HLDA writes which hit into the cache invalidate the cached line. The VL82C325 uses the –MEMW signal from the Bus Controller to detect these cycles. On the rising edge of –MEMW (when HLDA true), if the memory address hits in the cache, the cached line is invalidated.

#### FIGURE 4. CPU AND TOPCAT INTERFACES

### TABLE 7. 8- TO 16-BIT CONVERSION - CPU CYCLES

| M/-IO | D/-C | W/-R | 386 Cycle            | Conditions                  | Size              |

|-------|------|------|----------------------|-----------------------------|-------------------|

| 0     | 0    | 0    | INTA                 |                             |                   |

| 0     | 0    | 1    | Undefined            |                             |                   |

| 0     | 1    | 0    | I/O read             |                             |                   |

| 0     | 1    | 1    | I/O write            |                             |                   |

| 1     | 0    | 0    | Memory<br>code read  | Code fetch is always 16-bit | 16                |

| 1     | 0    | 1    | Halt/shutdown        |                             |                   |

| 1     | 1    | 0    | Memory<br>data read  | Non-cache                   |                   |

|       |      |      | uala reau            | Cache                       | Convert to 16-bit |

| 1     | 1    | 1    | Memory<br>data write |                             |                   |

#### TABLE 8. 8- TO 16-BIT CONVERSION - HLDA CYCLES

| Bus Cycle Type |            |      |

|----------------|------------|------|

| 386 Cycle      | Conditions | Size |

| Memory read    |            |      |

| Memory write   |            |      |

| I/O read       |            |      |

| I/O write      |            |      |

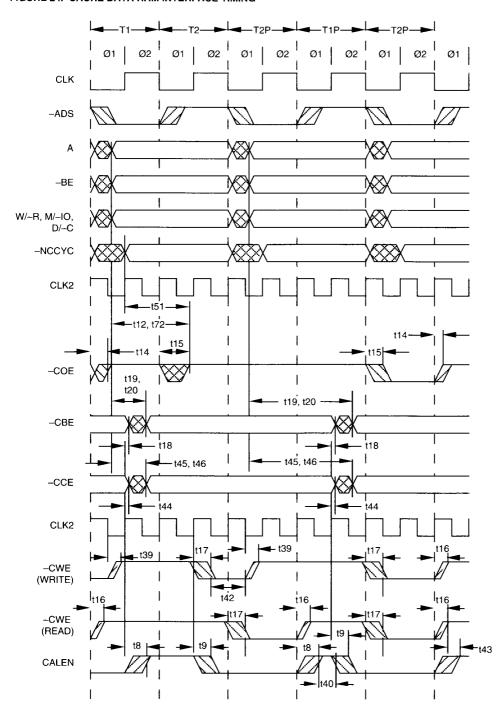

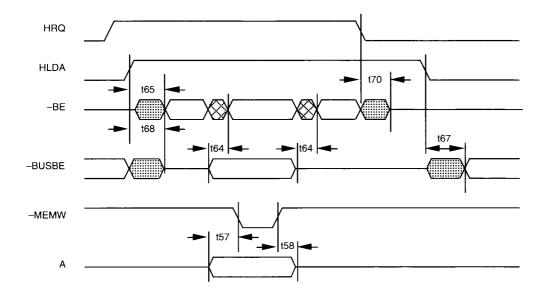

#### **CACHE DATA RAM INTERFACE**

The VL82C325 directly controls the cache data RAMs with no external logic required. The interface is optimized for use with dual 4K x 16 cache data RAMs. Each RAM is capable of operating in a two-way set associative mode, with each set being 4K x 16-bit. Therefore, a 16KB cache can be implemented using only one RAM chip, or two chips for a 32KB cache.

The VL82C325 produces two chip enable signals, -CCE1 - -CCE0, one each for the least significant and most significant 16KB of RAM. -CCE1 is not used in the 16KB configuration.

Two byte enables –CBE1, –CBE0 allow the cache data RAMs to perform byte write operations. –CBE0 is connected to the chip select inputs corresponding to the least significant byte of each cache data RAM (bits 0-7). –CBE1 enables the most significant byte (bits 8-15).

A read- or write-hit into set A causes set A to be read or written with –COEA or –CWEA respectively. Similarly for set B using –COEB or –CWEB.

The cache data RAMs have on-chip address latches which must be strobed. The processor's –ADS signal is unsuitable for this due to the pipelined mode of the 386SX. The VL82C325 produces the signal CALEN which is used to latch the cache data RAM addresses.

The data input/outputs of the RAMs are tied directly to the processor's data bus. This provides for the fastest possible access time to the data RAMs. Only during a read-hit are the data outputs enabled. The remainder of the time they are disabled, thus allowing normal operation of the processor data bus.

FIGURE 5. CACHE DATA RAM INTERFACE 16KB/32KB TWO-WAY SET ASSOCIATIVE

## EMS/MEMORY MANAGEMENT WITH CACHE

Hardware EMS or other memory management schemes are commonly used to extend the physical memory capacity of computing systems. The VL82C320A System Controller includes such an EMS capability. It is important to note the impact of hardware EMS upon a cached system.

EMS hardware resides between the CPU's address bus and that of physical memory. It translates the CPU's address before applying it to the physical memory. The CPU's address bus is often referred to as the physical address bus (particularly in CPU's such as the 386SX which have on-chip memory management). However, when hardware EMS is employed, the CPU's address bus is actually a virtual address bus.

The VL82C325 caches physical data, while the cache directory contains CPU addresses (virtual addresses if EMS employed). This is not a problem until, or unless, the virtual to physical translation algorithm is altered (reprogramming EMS registers). This can cause the data in the cache data RAMs to become stale. It is therefore advised that either of the following strategies be used when hardware EMS is employed:

- Ensure that the cache is flushed each time that memory is reconfigured. Note that to avoid spurious effects, it may be necessary to first disable the cache, then reconfigure memory, flush the cache, and then re-enable the cache.

- Define EMS-controlled virtual memory regions to be noncacheable (using NCT or the –NCCYC pin).

- Enable the Auto-EMS Flush feature by setting the A\_EMS bit in the Cache Configuration Register (CCR). This feature will cause the cache directory to automatically flush any time that a change to EMS registers occurs (see the section titled "Flushing").

If two or more EMS pages map to the same physical memory page, then the cache data may become stale because the VL82C325 will not recognize that the addresses are equivalent. Data

which is cached at one address may be written to at another address and the cached data will not be updated. Avoid multiple mapped pages, or define such pages as non-cacheable.

If memory is managed using only the 386SX's on-chip memory management schemes, then the CPU's address is truly a physical bus and the above precautions are unnecessary.

Other less obvious factors can also disturb the cache. For example, changing the DRAM configuration registers RAMMAP and RAMMOV (in the System Controller) will invalidate cache contents. In general, never reconfigure memory without considering cache. If in doubt, follow procedure #1 outlined above.

#### **FLUSHING**

A cache flush empties the cache. The next memory access is therefore guaranteed to miss. A flush does not alter the contents of cache data RAM, but simply invalidates all of cache data by clearing all of the VALID-bits in the tag RAMs. A flush can be caused in any of the following three ways.

- 1) The –FLUSH input signal is driven low while the cache is enabled.

- The software flush bit (FLUSH) in the Cache Control Register (CCR) is set to 1.

- An EMS-update event occurs while the Auto-EMS-Flush enable bit (A EMS) in the CCR is set to 1.

Flushing requires approximately 12 CLK2 cycles to complete. While the cache is flushing, it is automatically disabled and will issue a miss for any cycle which executes during the flush. If the cache was previously enabled, then it will automatically re-enable when the flush is completed.

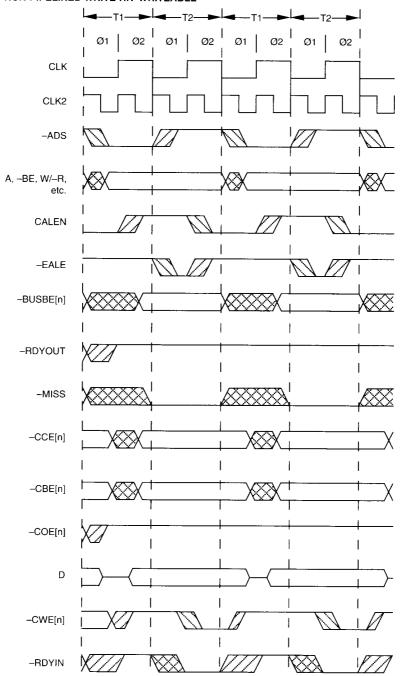

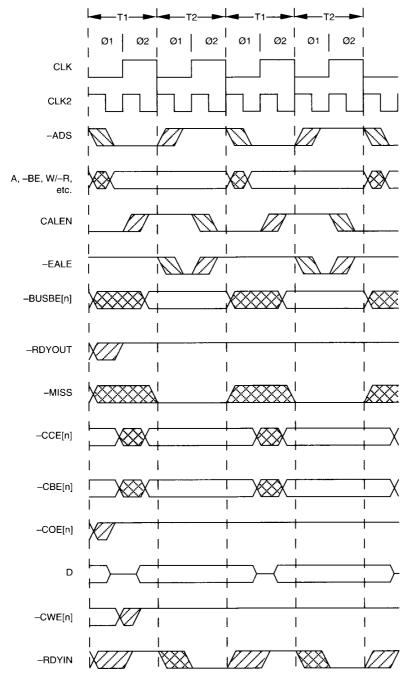

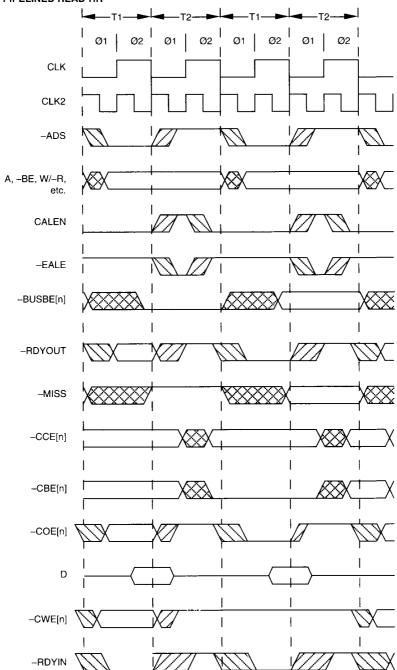

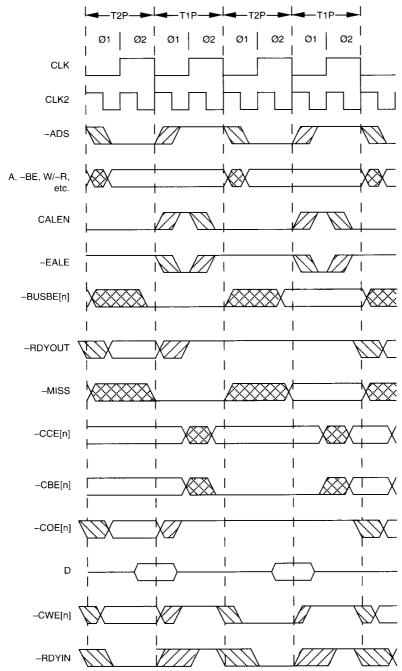

If the cache is disabled at the time when the flush request occurs, then the flush will commence immediately. If, however, the cache is enabled, then the request pends until the next end of a T2 state (non-pipelined), the next end of a T1 state (non-pipelined) or the next end of a T1P state (pipelined). This ensures that the cache look-up for the cycle in progress is not interrupted. An interruption in the look-up could cause a false result.

#### -FLUSH: Hardware Flush Signal

The –FLUSH pin operates only when the cache is enabled. When the cache is disabled, the tag RAMs are available for the various tag RAM diagnostics operations (see the section titled "Testing"). This ensures that the –FLUSH pin will not interfere with testing.

The –FLUSH pin may be asserted synchronously or asynchronously. If asserted synchronously, it must meet the setup and hold requirements which are defined in the section titled "AC Characteristics". If asserted asynchronously, then it must meet the minimum pulse width requirement which is defined in the same section.

If –FLUSH is sampled low by the rising edge of CLK2 on or before the middle of state T2, then the flush will commence at the end of that T2 state.

Otherwise, it will pend until the end of the next T2, T1, or T1P. Similarly for pipelined cycles, –FLUSH must be sampled low on or before the middle of T1P.

#### Software-Flush

A software flush is initiated by setting the FLUSH bit in the CCR to a 1. Software flushes can be issued regardless of whether the cache is enabled or disabled. However, FLUSH will be ignored if the tag RAM is busy executing a diagnostic test. Issuing software flushes while running diagnostics is not recommended. First wait for the diagnostics test to complete.

FLUSH is a return-to-zero bit, i.e. when the flush operation is complete FLUSH will automatically return to 0.

#### **Auto-EMS Flush**

An Auto-EMS Flush will occur if an EMS-update event occurs while the Auto-EMS Flush enable bit (A\_EMS) in the CCR is set to 1. This feature can be disabled by setting A\_EMS to 0.

Updates to EMS registers can require that the cache be flushed (see the section titled "EMS / Memory Management with Cache"). Hardware accomplishes an Auto-EMS Flush by automatically forcing the software FLUSH bit in CCR to a 1. Therefore, the discussion on software flush given above applies here also. The following is a list of the EMS-update events which can cause an Auto-EMS Flush to occur.

- An I/O read of E9 Hex (EMS Active Set) register. This operation selects the standard EMS register set.

- An I/O write to E9 Hex (EMS Active Set) register. This operation selects the alternate EMS register set.

- An I/O write to any of the following registers with configuration registers write-enabled.

- 3.1) EMSEN1, EMS Enable 1 (ED Hex with configuration index of 0B Hex).

- 3.2) EMSEN2, EMS Enable 2 (ED Hex with configuration index of OC Hex).

- EA Hex (EMS data port low byte).

- 3.4) EB Hex (EMS Data port high byte).

#### TESTING

#### **IN-CIRCUIT TESTING**

The –TRI input pin is provided to aid in the in-circuit testing of board-level designs. This is an active low input, which when true, causes all of the VL82C325's outputs to become three-stated. The in-circuit tester can then drive the VL82C325's pins to test other devices on the board.

In addition, the VL82C325 can be placed in a special In-Circuit Test (ICT) mode. In this mode, input pins are mapped directly to output pins. This provides a relatively simple means of determining whether all pins have been correctly soldered and whether the component orientation is correct. There are many more inputs than outputs, so three maps (A,B,C) are required to cover all inputs. The three inputs -NCCYC, -WPCYC, and -FLUSH select the map. Table 9. defines the map selection and the mapping of input pins to output pins in each map. All ICT input to ICT output paths invert so, e.g., in map A, XD0 gets the inverse of A16. Also RESCPU is ORed with -MASTER in map A, and HLDA is ANDed with HRQ in map C.

#### **TABLE 9. ICT PIN MAP**

| Мар А | Мар В | Map C | ICT Inputs |

|-------|-------|-------|------------|

| 1     | 0     | 0     | -NCCYC     |

| 0     | 1     | 0     | -WPCYC     |

| 0     | 0     | 1     | -FLUSH     |

| ICT Inputs        | ICT Inputs | ICT Inputs   | ICT Outputs |

|-------------------|------------|--------------|-------------|

| -IOW              | -M/IO      | -CWEA        | -CBE1       |

| -IOR              | -ADS       | -CWEB        | -CBE0       |

| -BUSBE1           | -HIDRIVE   | -COEA        | -вне        |

| -BUSBE0           | -CLK2      | -COEB        | -BLE        |

| RESCPU or -MASTER | -BLKA20    | CALEN        | -CCE0       |

| W/-R              | -MEMW      | -MISS        | -CCE1       |

| D/-C              | -RDYIN     | -RDYOUT      | -EALE       |

| A23               | A15        | A7           | XD7         |

| A22               | A14        | A6           | XD6         |

| A21               | A13        | A5           | XD5         |

| A20               | A12        | A4           | XD4         |

| A19               | A11        | А3           | XD3         |

| A18               | A10        | A2           | XD2         |

| A17               | А9         | A1           | XD1         |

| A16               | A8         | HLDA and HRQ | XD0         |

The following sequence is used to set or clear the ICT mode.

- 1) Set the -TRI pin low.

- Set XD0 high to set ICT mode or set XD0 low to clear ICT mode.

- 3) Simultaneously pulse –IOR and –IOW low for a minimum of 100 ns.

A hardware reset (RSTDRV) will also clear the ICT mode.

#### **TESTING MAIN MEMORY**

Main memory can be tested with the VL82C325 installed. Simply disable the VL82C325 with the CENA bit in the Cache Configuration Register (CCR) (see the section titled "Summary of Programming Model" for more information). With the VL82C325 disabled, all accesses go directly to main memory.

#### **TESTING NCT/WPT RAMS**

The non-cacheable region table and write-protect region table are accessable through the VL82C325's programming registers NCT\_INDX and NCT/WPT. These are read/write registers, so the tables may be tested through these ports. See the section titled "Summary of Programming Model" for more details.

#### **TESTING CACHE DIRECTORY RAMS**

The VL82C325 provides hardware to assist in the in-system testing of the onchip cache directory RAMs. Built-in test logic automatically cycles through the tag RAMs performing data writes and read verify operations. The VL82C325 must be disabled (by clearing the CENA bit in the CCR register) before attempting to run any of the tag RAM diagnostics tests. Six tests are available, of which four run in the background, i.e., once initiated they require no further user action to complete. Foreground tests require user action to complete (user must read RAMDATA). To run one of the tests, use the following procedure:

- Disable the cache by clearing the CENA bit in CCR.

- Select from the six tests by programming the TR\_OPCODE field in TSR.

- If required, write 20-bit data pattern to RAMDATA.

- 4) Start the test by setting the TRDIAG bit in CCTRL.

- 5) For background tests: Poll the

TRDIAG bit in CCR. When it returns to 0, the test is complete.

For foreground tests: Read 20-bit data pattern from RAMDATA, and repeat until TRDIAG returns to 0.

6) If required, read the test-passed bits TPA and TPB in CCTRL. A 1 in TPA indicates that directory A passed the test; similarly a 1 in TPB indicates that directory B passed.

Background tests can be left running while the system is performing other tasks such as testing main system memory. Table 10 summarizes the six available tests, and gives approximate execution times for background tests.

#### Write

Writes RAMDATA to every location of each directory. This test in conjunction with the following (read-verify) is used to test the cache flush mechanism. "Write" is used to preload the directory RAMs with RAMDATA, then a software flush should be executed by setting the FLUSH bit in CCR.

A flush invalidates every line in the cache by clearing all of the VALID bits

#### **TABLE 10. CACHE DIRECTORY TESTS**

|                    |                                                                                                                   | Time      | (μ <b>s</b> ) |

|--------------------|-------------------------------------------------------------------------------------------------------------------|-----------|---------------|

| TR_OPCODE<br>(Bin) | Description                                                                                                       | 20<br>MHz | 25<br>MHz     |

| 00100              | Write: Writes RAMDATA to every location.                                                                          | 77        | 62            |

| 00010              | Read-verify: Read every location and verify that the contents are equal to RAMDATA with the MS 10 bits "flushed". | 77        | 62            |

| 00110              | Writes and Read-verify: Writes and verifies RAMDATA and the inverse of RAMDATA to every location.                 | 410       | 330           |

| 00111              | Write Checkerboard and Read-verify: Similar to previous test but alternates the pattern at adjacent addresses.    | 410       | 330           |

| 01000              | Dump Tag Directory A: A diagnostic dump of the contents of Tag Directory RAM A.                                   |           |               |

| 01000              | Dump Tag Directory B: A diagnostic dump of the contents of Tag Directory RAM B.                                   |           |               |

(four or eight depending on the mode). The VALIDs are active low so they are flushed to high. In fact, the most significant (MS) 10 bits of each location in each directory are flushed.

Then a "read-verify" test should be executed. That test will read every location of each directory and verify that the MS 10 bits were flushed and that the LS (least significant) 10 bits are still equal to the LS 10 bits of RAMDATA.

#### Read-Verify

This test will read every location of each directory and verify that the MS 10 bits were flushed and that the LS 10 bits are equal to the LS 10 bits of RAMDATA. This test, in conjunction with the previous, (write) is used to test the cache flush mechanism.

#### Write and Read-Verify

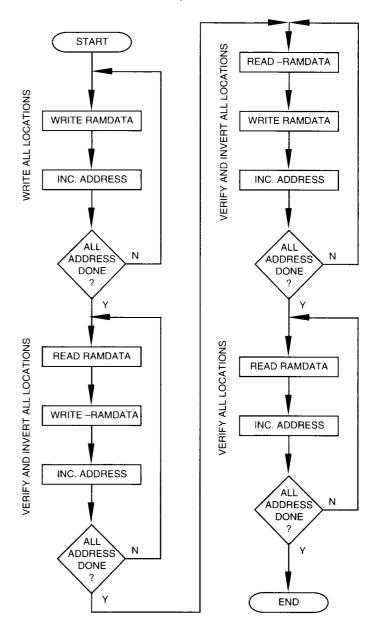

Writes and verifies RAMDATA and the inverse of RAMDATA to every location of each directory according to the flow diagram in Figure 6.

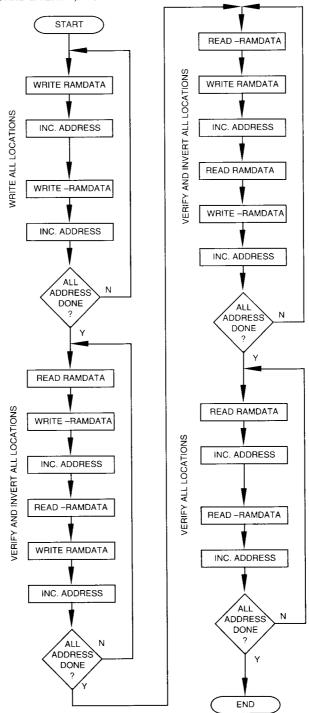

Write Checkerboard and Read-Verify Writes and verifies RAMDATA and the inverse of RAMDATA to every location of each directory according to the flow diagram in Figure 7.

#### Directory Dump (A or B)

Dumps the contents of one directory RAM. This is a foreground test, i.e., it does not operate totally automatically like the background tests do. The user is required to read the directory data from the RAMDATA register. Three reads are required to obtain all 20 bits of a single RAM location (see the section titled "Summary of Programming Model"). 1024 locations must be dumped (3072 reads). ALL 3072 reads must be performed or the test will not complete.

#### FIGURE 6. WRITE & READ-VERIFY, FLOW DIAGRAM

FIGURE 7. WRITE CHECKERBOARD & VERIFY, FLOW DIAGRAM

### FIGURE 8. TESTING CACHE DATA RAMS (16KB)

#### TESTING CACHE DATA RAMS

Before testing the cache data RAMs, first flush the cache with the FLUSH bit in the CCR. This ensures that all of the valid bits are cleared and that the LRU table is cleared. This enables the test to determine whether the failure occurred in set A or in set B. Blocks will first be allocated to set A, and then to set B, and then to the least recently used. Diagnosing to set A or B, is of course, only necessary if the cache data memory was created using different physical RAMs for each set.

It is important that the code which is executing the test of the cache data RAMs not interfere with the allocation of space in the RAMs. This code should therefore be located in a non-cacheable region. Similarly, any stack or variable space should be noncacheable. A contiguous region of system memory space equal to or greater than the total cache data size should be set aside for the testing of the cache data RAMs. This region should be defined as cacheable.

Having flushed the cache, if the test routine then sequentially reads every location in the cacheable region, starting at offset 0 and ending at offset CacheDataSize-1, then an image of the cacheable region will be copied directly into the cache. If the test now makes no further references to cacheable memory outside this region, then the VL82C325 will not re-allocate any of the cache data RAM space (because space can be allocated only on read-misses to cacheable regions). If this rule is obeyed, then the cache data RAM can be tested just like any normal static RAM. Figure 8 depicts the mapping of main memory to cache data RAM (for 16KB configuration) when the above rules are followed. Figure 9 depicts the mapping for the 32KB configuration.

#### FIGURE 9. TESTING CACHE DATA RAMS (32KB)

#### **DUMPING CACHE DATA RAMS**

The current contents of the cache data RAMs can be dumped for diagnostic purposes. First, disable the cache by clearing the CENA bit in the CCR register. No further allocation of cache can occur, so the cache data memory is now "frozen". Then set the

BLOCK\_CWE bit in the TSR register. This blocks the cache write-enable outputs, preventing further writes to cache data RAM. Next re-enable the cache, then beginning with a cache flush, follow the directions in the section titled "Testing Cache Data RAMs" to re-allocate the cache direc-

tory map. The cache data RAMs can now be read using one of the memory maps depicted in Figures 8 and 9. A cache data RAM dump is most useful when preceded by a cache directory RAM dump. See the section titled "Testing Cache Directory RAMs".

### ADVANCE INFORMATION

VL82C325

#### SUMMARY OF PROGRAMMING MODEL

The VL82C325 is configured via ten 8-bit I/O registers. Four other 8-bit I/O ports (Access Control Registers) are required to control the access to the Configuration Registers. Finally, three other TOPCAT registers are monitored for the Auto-EMS Flush feature, but no data is retained in the VL82C325 for these registers.

Except where otherwise noted, all accesses to these registers must be 8-bit accesses. Cycles complete with slot bus timing. A register indexing scheme allows many configuration registers to occupy only a very small region of I/O space. It is the same mechanism which is employed in the VL82C320A/ VL82C310 System Controllers and VL82C331 Bus Controller and is an extension of their register spaces.

Table 11 is a summary of the Access Control Registers. Eight Configuration registers are mapped to the TOPCAT Indexed Configuration Register Table and two (NCT\_INDX, NCT/WPT) are mapped to the TOPCAT Indexed EMS Register Table. The Access Control Registers allow the user to select the appropriate indices into these two register tables. They also permit the write-protection of the VL82C325's Configuration Registers. They are all write-only registers.

Note that before accessing any VL82C325 register in indexed EMS space, the correct index value (24 Hex) must be written into EMS\_INDX. Similarly, before accessing any VL82C325 register in indexed configuration space, the correct index value

(06, 14, 28-2F Hex) must be written into CFG INDX.

When configuration is complete, it is recommended that the registers be write-protected by writing to CFG\_DIS. This helps to prevent inadvertent changes to the VL82C325's setup parameters. Write-protection can be removed by writing to CFG\_EN.

Table 12 lists those VL82C325 registers which reside in indexed EMS space, and Table 13 lists those which reside in indexed configuration space. Table 14 lists the additional Auto-EMS Flush registers (no data is retained in these registers; see the section titled ("Auto-EMS Flush").

#### TABLE 11. ACCESS CONTROL REGISTER MAP

| I/O Addr<br>(Hex) | R/W        | Name     | Description                                                                                                                                                                |

|-------------------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E8*               | W EMS_INDX |          | EMS Index Register - 24 (Hex) to access register's NCT_INDX and NCT/WPT. Other values access other TOPCAT EMS registers.                                                   |

| EC*               | W          | CFG_INDX | Configuration Index Register - 06, 14, 28-2F (Hex) to access VL82C325 registers. Other values access other TOPCAT configuration registers.                                 |

| F9*               | W          | CFG_DIS  | Configuration Disable - If special features are enabled, then any write will write-protect the registesters in indexed configuration space and those in indexed EMS space. |

| FB*               | W          | CFG_EN   | Configuration Enable - If special features are enabled, then any write will write-enable the registesters in indexed configuration space and those in indexed EMS space    |

<sup>\*</sup>Shadow (local copy) of identical register in System Controller.

#### **TABLE 12. INDEXED EMS REGISTER MAP**

| EMS_INDX<br>(Hex) | R/W | Name     | I/O Addr<br>(Hex) | Description                        |

|-------------------|-----|----------|-------------------|------------------------------------|

| 24                | R/W | NCT_INDX | EA                | NCT Index Register                 |

|                   | R/W | NCT/WPT  | EB                | Non-cache and write-protect tables |

#### **TABLE 13. INDEXED CONFIGURATION REGISTER MAP**

| EMS_INDX<br>(Hex) | R/W | Name    | I/O Addr<br>(Hex) | Description                  |

|-------------------|-----|---------|-------------------|------------------------------|

| 06*               | w   | REFCTL  | ED                | Refresh Control Register     |

| 14*               | w   | MISCSET |                   | Miscellaneous Set Register   |

| 28                | R/W | CCR     |                   | Cache Configuration Register |

| 29                | R/W | CCTRL   |                   | Cache Control Register       |

| 2A                | R/W | TSR     |                   | Test Status Register         |

| 2B                | R/W | RAMDATA |                   | Tag RAM Data Register        |

| 2C                | R   | EMS_IMG |                   | EMS_INDX Image Register      |

| 2F                | R   | VER     |                   | Version Register             |

<sup>\*</sup>Shadow (local copy) of identical register in System Controller.

#### **TABLE 14. MONITORED AUTO-EMS REGISTERS**

| EMS_INDX<br>(Hex) | R/W | Name    | I/O Addr<br>(Hex) | Description             |

|-------------------|-----|---------|-------------------|-------------------------|

|                   |     | EMS_SET | E9 **             | EMS Active Set Register |

| 0B **             |     | EMSEN1  | ED                | EMS Enable1 Register    |

| 0C **             |     | EMSEN2  |                   | EMS Enable2 Register    |

<sup>\*</sup>System Controller registers (see the section titled "Auto-EMS Flush).

### ADVANCE INFORMATION

VL82C325

The following sections describe the individual registers and bit functions. In the tables, the "RSTDRV/INTRST" column indicates how that bit or field is

affected by the hardware reset (RST-DRV pin) and the software reset (INTRST bit in the CCTRL register) operations. That is, 0/0 indicates that

the bit is set to 0 by either operation, while 1/- indicates that the bit is set to 1 by hardware resets but is unaffected by software resets.

#### TABLE 15. EMS INDEX REGISTER (EMS\_INDX) (I/O Address E8 (Hex))

| Bit | R/W | RSTDRV/<br>INTRST | Name               | Description                                                                                                                                                                                                                                                                                                            |

|-----|-----|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-0 | w   | 0/-               | INDEX-EMS<br>(5-0) | Index into Indexed-EMS Register table. Must be 24 (Hex) to access the VL82C325's registers NCT_INDX or NCT/WPT.                                                                                                                                                                                                        |