# **SiS900**

# Fast Ethernet PCI Bus 10/100 Mbps LAN Single Chip with OnNow Support

Preliminary

Revision 1.0 November 10, 1998

Silicon Integrated System Corp.

This specification is subject to change without notice. Silicon Integrated System Corporation assumes no responsibility for any errors contained herein.

Copyright by Silicon Integrated System Corp., All Right Reserved.

Preliminary Rev. 1.0, Nov 10, 1998

Silicon Integrated System Corporation

# **Table of Contents**

| 1. | INTRO | ODUCTI  | ON          |                                       | 1    |

|----|-------|---------|-------------|---------------------------------------|------|

|    | 1.1   | SiS900  | Overview    |                                       | 1    |

|    |       | 1.1.1   |             | Organization                          |      |

|    |       |         |             |                                       |      |

| 2. | PIN A | SSIGNM  | IENT        |                                       | 3    |

|    | 2.1   |         |             | tion                                  |      |

|    | 2.2   |         |             |                                       |      |

|    | 2.3   |         |             | EEPROM Interface                      |      |

|    | 2.4   |         |             | Signals                               |      |

|    | 2.5   |         |             | t Signals                             |      |

|    | 2.6   | Power a | ind Ground  | Pins                                  | 9    |

| 3. | FUNC  | TIONAL  | DESCRIP     | TION                                  | . 10 |

|    | 3.1   | Media A | Access cont | roller                                | . 10 |

|    |       | 3.1.1   | PCI Bus In  | nterface                              | . 11 |

|    |       |         | 3.1.1.1     | Byte Ordering                         | . 11 |

|    |       |         | 3.1.1.2     | Interrupt Control                     | . 11 |

|    |       |         | 3.1.1.3     | Latency Timer                         |      |

|    |       | 3.1.2   | Bus Opera   | ution                                 |      |

|    |       |         | 3.1.2.1     | Target Read                           |      |

|    |       |         | 3.1.2.2     | Target Write                          |      |

|    |       |         | 3.1.2.3     | Master Read                           |      |

|    |       |         | 3.1.2.4     | Master Write                          |      |

|    |       |         | 3.1.2.5     | Configuration Access                  |      |

|    |       | 3.1.3   |             | nagement                              |      |

|    |       |         | 3.1.3.1     | Overview                              |      |

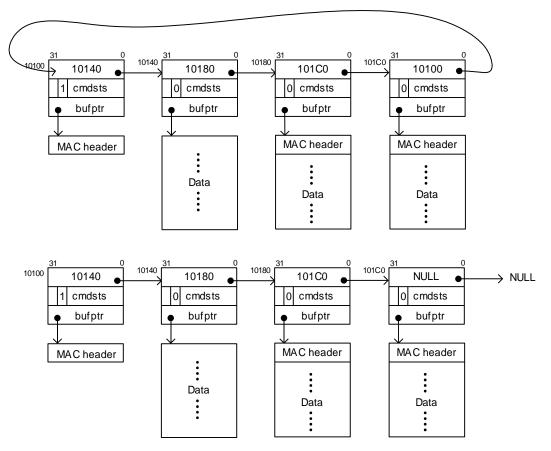

|    |       |         |             | 3.1.3.1.1 Descriptor Format           | . 16 |

|    |       |         |             | 3.1.3.1.2 Single Descriptor Packets   |      |

|    |       |         |             | 3.1.3.1.3 Multiple Descriptor Packets |      |

|    |       |         |             | 3.1.3.1.4 Descriptor Lists            |      |

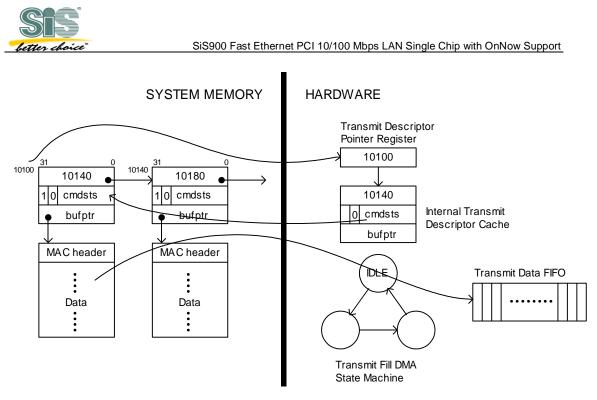

|    |       |         | 3.1.3.2     | Transmit Architecture                 |      |

|    |       |         | 0100        | 3.1.3.2.1 Transmit Data Flow          |      |

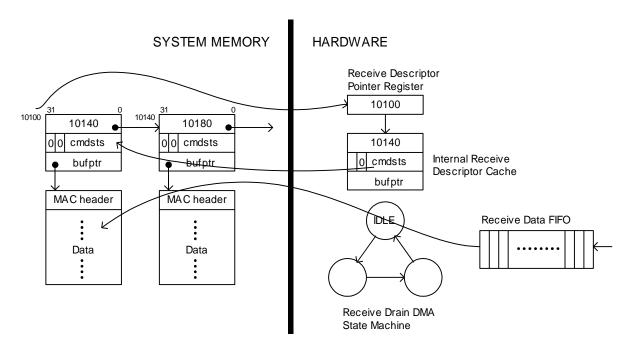

|    |       |         | 3.1.3.3     | Receive Architecture                  |      |

|    |       | 214     | D           | 3.1.3.3.1 Receive Data Flow           |      |

|    |       | 3.1.4   |             | nd Transmit FIFOs                     |      |

|    |       |         | 3.1.4.1     | Receive FIFO                          |      |

|    |       | 3.1.5   | 3.1.4.2     | Transmit FIFO                         |      |

|    |       | 0.1.6   |             | Iedia Access Controller (MAC)         |      |

|    |       | 3.1.6   | 3.1.6.1     | Receive State Machine (RSM)           |      |

|    |       |         | 3.1.6.2     | Receive Logic                         |      |

|    |       |         | 3.1.6.3     | De-nibblizer                          |      |

|    |       |         | 3.1.6.4     | CRC Checker                           |      |

|    |       |         | 3.1.6.5     | Receive Filter                        |      |

|    |       | 3.1.7   |             | MAC                                   |      |

|    |       | 5.1.7   | 3.1.7.1     | Transmit State Machine (TSM)          |      |

|    |       |         | 3.1.7.2     | Protocol State Machine                |      |

|    |       |         | 3.1.7.3     | Preamble Generator                    |      |

|    |       |         | 3.1.7.4     | CRC Generator                         |      |

|    |       |         | 3.1.7.5     | Jam Generator                         |      |

|    |       |         |             |                                       | -    |

| 5 | SiS900 Fast Ethernet PCI | 10/100 Mbps | LAN Single Chi | p with OnNow Support |

|---|--------------------------|-------------|----------------|----------------------|

|   |                          |             |                |                      |

|     | 3.1.8  |                  | rol                                |     |  |  |  |

|-----|--------|------------------|------------------------------------|-----|--|--|--|

|     | 3.1.9  | -                | x Operation                        |     |  |  |  |

|     |        | -                | ers Access                         |     |  |  |  |

|     | 3.1.11 |                  | Operation                          |     |  |  |  |

|     | 3.1.12 |                  | ration                             |     |  |  |  |

|     | 3.1.13 | Power Management |                                    |     |  |  |  |

|     |        | 3.1.13.1         | SiS900 Device Power States         |     |  |  |  |

|     |        | 3.1.13.2         | SiS900 Wake-up Events              |     |  |  |  |

|     |        |                  | Link State Change Detected Event   |     |  |  |  |

|     |        | 3.1.13.4         | Wake-up Frame Received Event       |     |  |  |  |

|     |        | 3.1.13.5         | Magic Packet Received Event        |     |  |  |  |

| 3.2 |        |                  | ty                                 |     |  |  |  |

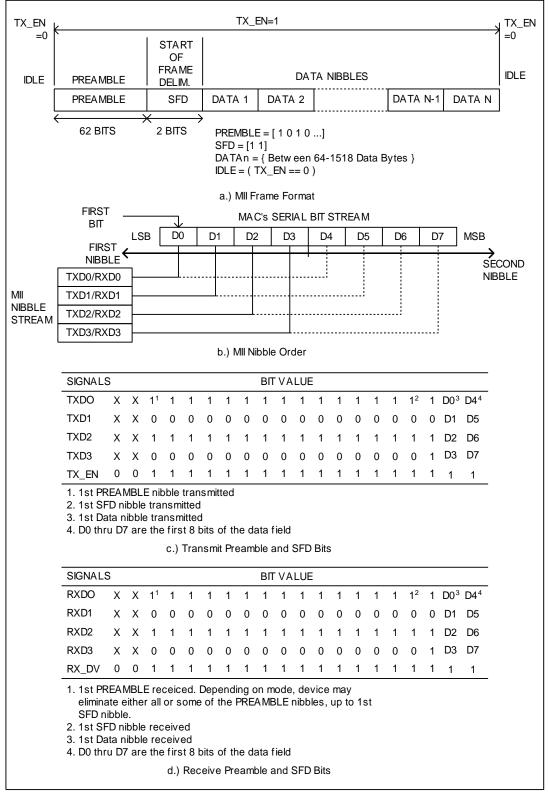

|     | 3.2.1  | Media Inde       | ependent Interface                 |     |  |  |  |

|     |        | 3.2.1.1          | MII - 100 Mbps                     |     |  |  |  |

|     |        | 3.2.1.2          | MII - 10 Mbps                      | 31  |  |  |  |

|     | 3.2.2  | Encoder          |                                    | 32  |  |  |  |

|     |        | 3.2.2.1          | 4B5B Encoder - 100 Mbps            | 32  |  |  |  |

|     |        | 3.2.2.2          | Manchester Encoder - 10 Mbps       | 32  |  |  |  |

|     | 3.2.3  | Decoder          |                                    | 33  |  |  |  |

|     |        | 3.2.3.1          | 4B5B Decoder - 100 Mbps            | 33  |  |  |  |

|     |        | 3.2.3.2          | Manchester Decoder - 10 Mbps       | 34  |  |  |  |

|     | 3.2.4  | Clock and        | Data Recovery                      | 34  |  |  |  |

|     |        | 3.2.4.1          | Clock Recovery - 100 Mbps          | 34  |  |  |  |

|     |        | 3.2.4.2          | Data Recovery - 100 Mbps           |     |  |  |  |

|     |        | 3.2.4.3          | Clock Recovery - 10 Mbps           |     |  |  |  |

|     |        | 3.2.4.4          | Data Recovery - 10 Mbps            |     |  |  |  |

|     | 3.2.5  | Scrambler        | • •                                |     |  |  |  |

|     |        | 3.2.5.1          | 100 Mbps                           |     |  |  |  |

|     |        | 3.2.5.2          | 10 Mbps                            |     |  |  |  |

|     | 3.2.6  | Descrambl        | er                                 |     |  |  |  |

|     |        | 3.2.6.1          | 100 Mbps                           |     |  |  |  |

|     |        | 3.2.6.2          | 10 Mbps                            |     |  |  |  |

|     | 3.2.7  | Twister Pa       | ir Transmitter                     |     |  |  |  |

|     |        | 3.2.7.1          | Transmitter - 100 Mbps             |     |  |  |  |

|     |        | 3.2.7.2          | Transmitter - 10 Mbps              |     |  |  |  |

|     |        | 3.2.7.3          | Transmit Level Adjust              |     |  |  |  |

|     |        | 3.2.7.4          | Transmit Rise And Fall Time Adjust | 38  |  |  |  |

|     |        | 3.2.7.5          | STP (150 Ohm) Cable Mode           |     |  |  |  |

|     |        | 3.2.7.6          | Transmit Activity Indication       |     |  |  |  |

|     |        | 3.2.7.7          | Transmit Disable                   |     |  |  |  |

|     |        | 3.2.7.8          | Transmit Power Down                | 38  |  |  |  |

|     | 3.2.8  |                  | air Receiver                       |     |  |  |  |

|     | 0.2.0  | 3.2.8.1          | Receiver - 100 Mbps                |     |  |  |  |

|     |        | 3.2.8.2          | Receiver - 10 Mbps                 |     |  |  |  |

|     |        | 3.2.8.3          | TP Squelch - 100 Mbps              |     |  |  |  |

|     |        | 3.2.8.4          | TP Squelch - 10 Mbps               |     |  |  |  |

|     |        | 3.2.8.5          | Equalizer Disable                  |     |  |  |  |

|     |        | 3.2.8.6          | Receive Level Adjust               |     |  |  |  |

|     |        | 3.2.8.7          | Receive Activity Indication        |     |  |  |  |

|     | 3.2.9  |                  |                                    |     |  |  |  |

|     | 5.2.7  | 3.2.9.1          | 100 Mbps                           |     |  |  |  |

|     |        | 3.2.9.1          | 10 Mbps                            |     |  |  |  |

|     |        | 3.2.9.2          | Collision Test                     |     |  |  |  |

|     |        |                  |                                    | • • |  |  |  |

| ter choi | ice"     | SiS900 Fast Ethernet PCI 10/100 Mbps LAN Single Chip with OnNow Supp | oort |

|----------|----------|----------------------------------------------------------------------|------|

|          |          | 3.2.9.4 Collision Indication                                         | 41   |

|          | 3.2.10   | Start Of Packet                                                      | 41   |

|          |          | 3.2.10.1 100 Mbps                                                    | 41   |

|          |          | 3.2.10.2 10 Mbps                                                     | 41   |

|          | 3.2.11   | End Of Packet                                                        | 42   |

|          |          | 3.2.11.1 100 Mbps                                                    | 42   |

|          |          | 3.2.11.2 10 Mbps                                                     | 43   |

|          | 3.2.12   | Link Integrity & Auto-Negotiation                                    | 43   |

|          |          | 3.2.12.1 General                                                     | 43   |

|          |          | 3.2.12.2 Transmit NLP                                                | 45   |

|          |          | 3.2.12.3 Transmit FLP                                                | 45   |

|          |          | 3.2.12.4 Transmit TXLINK                                             | 45   |

|          |          | 3.2.12.5 Receive 10Base-T Link Integrity Algorithm                   | 45   |

|          |          | 3.2.12.6 Receive NLP Link Integrity Algorithm                        | 45   |

|          |          | 3.2.12.7 Receive 100Base-TX Link integrity Algorithm                 | 46   |

|          |          | 3.2.12.8 Auto-Negotiation Data Field                                 | 46   |

|          |          | 3.2.12.9 Receive Auto-Negotiation Algorithm                          | .47  |

|          |          | 3.2.12.10 Auto-Negotiation Outcome Indication                        | .49  |

|          |          | 3.2.12.11 Auto-Negotiation Status                                    | .49  |

|          |          | 3.2.12.12 Auto-Negotiation Enable                                    | 50   |

|          |          | 3.2.12.13 Auto-Negotiation Reset                                     |      |

|          |          | 3.2.12.14 Link Indication                                            | 50   |

|          |          | 3.2.12.15 Link Disable                                               | 51   |

|          | 3.2.13   | Jabber                                                               | 51   |

|          |          | 3.2.13.1 100 Mbps                                                    | 51   |

|          |          | 3.2.13.2 10 Mbps                                                     |      |

|          |          | 3.2.13.3 Jabber Disable                                              |      |

|          | 3.2.14   | Receive Polarity Correction                                          |      |

|          |          | 3.2.14.1 100 Mbps                                                    |      |

|          |          | 3.2.14.2 10 Mbps                                                     |      |

|          |          | 3.2.14.3 Auto-polarity Disable                                       |      |

|          | 3.2.15   | Full Duplex Mode                                                     |      |

|          |          | 3.2.15.1 100Mbps                                                     |      |

|          |          | 3.2.15.2 10Mbps                                                      |      |

|          | 0.0.1.6  | 3.2.15.3 Full Duplex Indication                                      |      |

|          | 3.2.16   | 100/10 Mbps Selection                                                |      |

|          |          | 3.2.16.1 General                                                     |      |

|          | 0.0.17   | 3.2.16.2 10/100 Mbps Indication                                      |      |

|          | 3.2.17   | PHY Loopback                                                         |      |

|          |          | 3.2.17.1 Internal CRS Loopback                                       |      |

|          | 2 2 1 0  | 3.2.17.2 Diagnostic Loopback                                         |      |

|          | 3.2.18   | PHY Reset                                                            |      |

|          | 3.2.19   | Power Down<br>Oscillator                                             |      |

|          | 3.2.20   |                                                                      |      |

|          | 3.2.21   | LED Drivers                                                          | . 55 |

| REG      | ISTERS   | DESCRIPTION                                                          | 55   |

| 4.1      | Register | r Overview                                                           | 55   |

| 4.2      | PCI Coi  | nfiguration Registers                                                | 56   |

|          | 4.2.1    | Configuration Identification Register                                |      |

|          | 4.2.2    | Configuration Command and Status Register                            |      |

|          | 4.2.3    | Configuration Revision ID Register                                   | 58   |

|          | 4.2.4    | Configuration Latency Timer Register                                 | .59  |

4.

| etter choice" |                    | SiS900 Fast Ethernet PCI 10/100 Mbps LAN Single Chip with OnNow Sup | port |

|---------------|--------------------|---------------------------------------------------------------------|------|

|               | 4.2.5              | Configuration IO Base Address Register                              | 59   |

|               | 4.2.6              | Configuration Memory Address Register                               |      |

|               | 4.2.7              | Configuration Subsystem Identification Register                     |      |

|               | 4.2.8              | Configuration Expansion ROM Base Address Register                   |      |

|               | 4.2.9              | Configuration Capabilities Pointer Register                         |      |

|               | 4.2.10             | Configuration Interrupt Select Register                             |      |

|               | 4.2.11             | Configuration Power Management Capabilities Register                |      |

|               | 4.2.12             | Configuration Power Management Control/Status Register              | 62   |

| 4.3           |                    | perational Registers.                                               |      |

| 1.5           | 4.3.1              | Command Register                                                    |      |

|               | 4.3.2              | Configuration Register                                              |      |

|               | 4.3.3              | Serial EEPROM Access Register                                       |      |

|               | 4.3.4              | PCI Test Control Register                                           |      |

|               | 4.3.5              | Interrupt Status Register                                           |      |

|               | 4.3.6              | Interrupt Mask Register                                             |      |

|               | 4.3.7              | Interrupt Enable Register                                           |      |

|               | 4.3.8              | Enhanced PHY Access Register                                        |      |

|               | 4.3.9              | Transmit Descriptor Pointer Register                                |      |

|               | 4.3.10             | Transmit Configuration Register                                     |      |

|               | 4.3.11             | Receive Descriptor Pointer Register                                 |      |

|               | 4.3.12             | Receive Configuration Register                                      |      |

|               | 4.3.13             | Flow Control Register.                                              |      |

|               | 4.3.14             | Receive Filter Control Register                                     |      |

|               | 4.3.15             | Receive Filter Data Register                                        |      |

|               | 4.3.16             | Power Management Control Register                                   |      |

|               | 4.3.17             | Power Management Wake-up Event Register                             |      |

|               | 4.3.18             | Wake-up Sample Frame CRC Register                                   |      |

|               | 4.3.19             | Wake-up Sample Frame Byte Mask Register                             |      |

| 4.4           |                    | HY Registers                                                        |      |

|               | 4.4.1              | Control Register                                                    |      |

|               | 4.4.2              | Status Register                                                     |      |

|               | 4.4.3              | PHY ID #1 Register                                                  |      |

|               | 4.4.4              | PHY ID #2 Register                                                  |      |

|               | 4.4.5              | Auto-Negotiation Advertisement Register                             | 87   |

|               | 4.4.6              | Auto-Negotiation Remote End Capability Register                     | 87   |

|               | 4.4.7              | Configuration 1 Register                                            |      |

|               | 4.4.8              | Configuration 2 Register                                            |      |

|               | 4.4.9              | Status Output Register                                              |      |

|               | 4.4.10             | Mask Register                                                       |      |

|               | 4.4.11             | Reservered Register                                                 |      |

| ELEC          | TRICAL             | CHARACTERISTICS                                                     |      |

|               |                    |                                                                     |      |

| 5.1           |                    | e Maximum Ratings                                                   |      |

| 5.2           |                    | nended Operating Conditions                                         |      |

|               | 5.3.1              | PCI Interface DC Specification                                      |      |

|               | 5.3.2              | Boot ROM/EEPROM Interface DC Specification                          |      |

| E 1           | 5.3.3<br>Traviet D | Analog Signals DC Specification                                     |      |

| 5.4           |                    | air Characteristics, Transmit                                       |      |

| 5.5           |                    | air Characteristics, Receive                                        |      |

| 5.6           |                    | cifications                                                         |      |

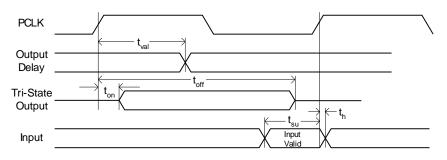

| 57            | 5.6.1<br>Timin a   | PCI Interface AC Specification                                      |      |

| 5.7           | -                  | Specification                                                       |      |

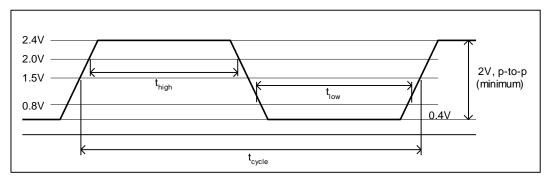

|               | 5.7.1              | Clock Specifications                                                | 97   |

|               |                    |                                                                     |      |

5

| bett | er chai                                                                             | ce"                                                                                                              |                                                                                                                                                            | SiS900 Fast Ethernet PCI 10/100 Mbps LAN Single Chip with OnNow Support                                                                  |

|------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

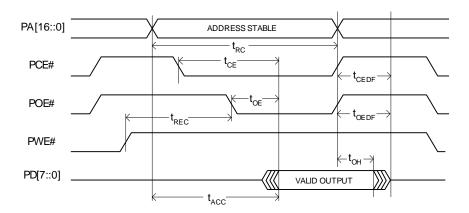

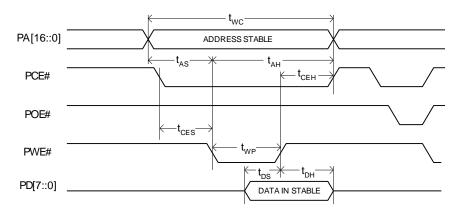

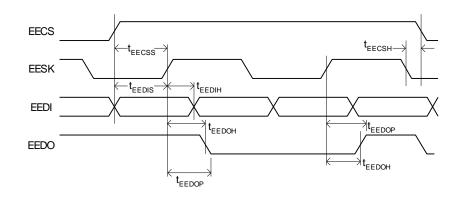

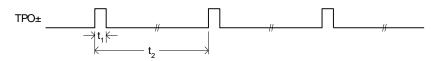

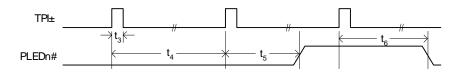

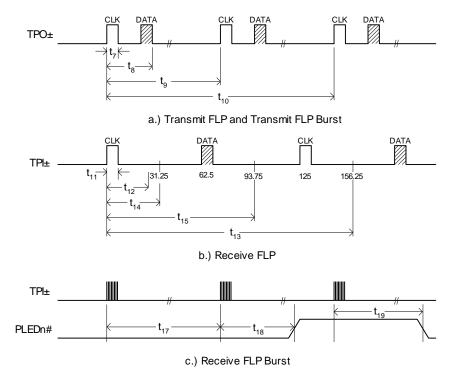

|      |                                                                                     | 5.7.2<br>5.7.3<br>5.7.4<br>5.7.5<br>5.7.6                                                                        | Boot ROM<br>EEPROM<br>Link Puls                                                                                                                            | PCI Clock9725 Mhz Clock Timing Characteristics99ngs.100M Timings.101(Timings.103e Timing Characteristic104ver Timing Characteristics.107 |

| 6.   | APPL                                                                                | ICATIO                                                                                                           |                                                                                                                                                            | IATION                                                                                                                                   |

|      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>PHYS | Twist P<br>Twist P<br>Cable S<br>Transm<br>Return<br>Long C<br>Oscillat<br>Power S<br>PCB La<br>6.11.1<br>6.11.2 | air Transm<br>air Receive<br>air Transm<br>election<br>itter Droop<br>Loss<br>able<br>or<br>Supply Dec<br>yout Guide<br>Placemen<br>Trace Rou<br>Power and | tics                                                                                                                                     |

| APPE | NDIX                                                                                | A - EEP                                                                                                          | ROM MAI                                                                                                                                                    | P                                                                                                                                        |

# Features

- Integrated Fast Ethernet controller and 10/100 megabit per second (Mbps) Physical Layer Transceivers for the PCI local bus

- PCI specification revision 2.1 compliant

- 32-bit glueless PCI host interface

- Plug and Play compatible

- Supports PCI clock frequency from DC to 33 MHz independent of network clock

- Supports network operation with PCI clock from 25Mhz to 33Mhz

- Supports both +3.3v and +5v PCI signaling

- High-performance 32-bit PCI bus master architecture with integrated Direct Memory Access (DMA ) Controller for low CPU and bus utilization

- Supports an unlimited PCI burst length

- Supports big endian and little endian byte alignments

- Supports PCI Device ID, Vendor ID/Subsystem ID, Subsystem Vendor ID programming through the EEPROM interface

- Implements optional PCI 3.3v auxiliary power source 3.3Vaux pin and optional PCI power management event (PME#) pin

- IEEE 802.3 and 802.3u standard compatible

- IEEE 802.3u Auto Negotiation and Parallel detection for automatic speed selection

- Full duplex and half duplex mode for both 10 and 100 Mbps.

- Fully compliant ANSI X3.263 TP-PMD physical sub-layer which includes adaptive equalization and Baseline Wander compensation.

- Automatic Jam and IEEE 802.3x Auto-Negotiation for flow control

- Single access to complete PHY register set

- Built-in waveform shaping requires no external filters

- Single 25Mhz clock for 10 and 100 Mbps operation.

- Power down of 10Base-T/100Base-TX sections when not in use

- Jabber control and auto-polarity correction for 10Base-T.

- User programmable LED function mapping

- Supports software, enhanced software, and automatic polling schemes to internal PHY status monitor and interrupt

- Supports 10BASE-T, 100BASE-TX, and any future

- Supports PC97, PC98, and Net PC requirements Green PC compatible

- Supports Advanced Configuration and Power Interface Specification (ACPI) Revision 1.0

- Supports PCI Bus Power Management Interface Specification Version 1.0a

- Supports Network Device Class Power Management Specification Version 1.0a

- Supports PCI Hot-Plug Specification Revision 1.0

- Implements full OnNow features including pattern matching and link status wake-up with automatic internal PHY status polling

- Implements optional Magic Packet<sup>TM</sup> remote wake-up scheme

- Implements IEEE 802.3x compliant Flow Control

Preliminary Rev. 1.0, Nov 10, 1998

vi

- Additional features

- Internal 128-bit Multicast Hash Table address filter

- Serial EEPROM support

- Boot ROM supports up to 128 Kbytes

- Extensive programmable internal/external loopback capabilities

- +3.3V power supply with +5V tolerant I/Os

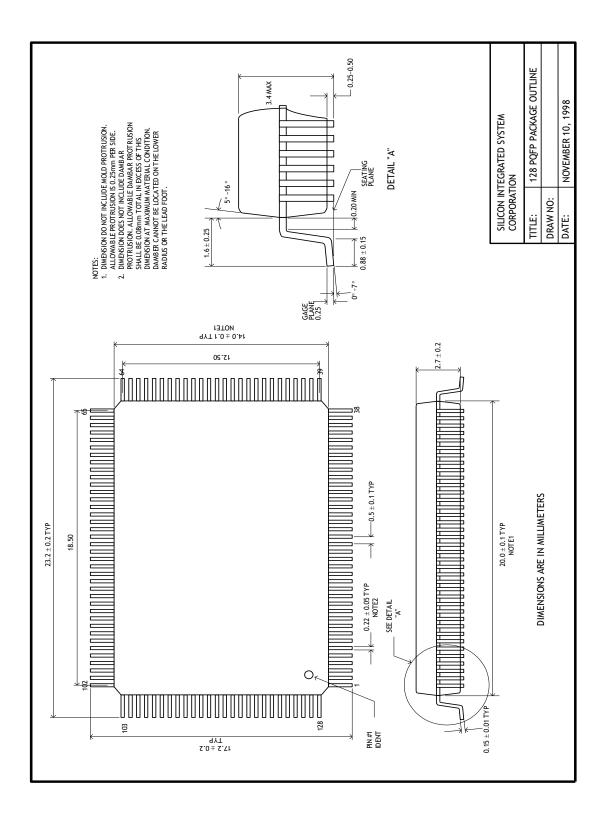

- 128pin PQFP package. Low-Power CMOS 0.35um Technology

# 1. INTRODUCTION

#### 1.1 SiS900 Overview

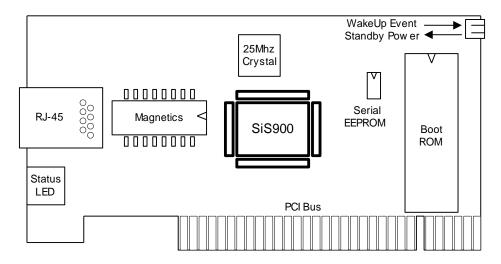

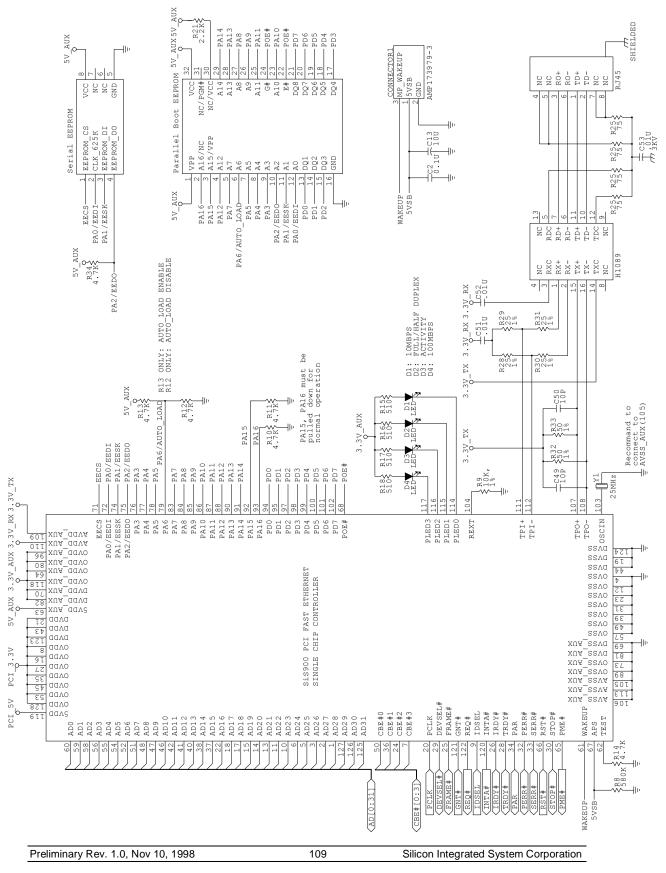

SiS900 is a single chip 10/100Mbps Fast Ethernet LAN solution, which fully integrates both the Media Access Controller (MAC) with PCI bus master interface and 802.3u compliant 10/100Mbps physical layer interface into a 128 pins PQFP, 0.35um process chip. It is targeted at low-cost, low-power, high volume desktop PC motherboards, mobile PC module, adapter cards, and embedded systems.

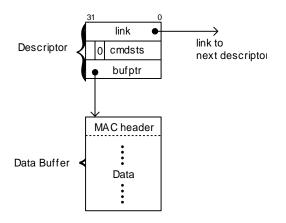

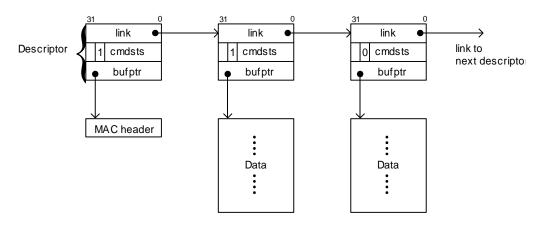

SiS900 fully implements the PCI bus version 2.1 interface for host communications. Packet descriptors and data are transferred via bus-mastering DMA channels, reducing the burden on the host CPU. The buffer management scheme utilized by SiS900 optimizes the use of memory space and the system bus. Descriptor information, describing the buffer space in which packet information is held, is symmetrical between transmit and receive operations. SiS900 supports both half-duplex and full-duplex operations with minimum inter frame gap and IEEE802.3x full-duplex flow control. In order to meet the PC 98 and the Green PC power saving requirements, SiS900 supports ACPI and Network Device Class Power Management specification. All the device states of D0, D1, D2, D3hot, and D3cold are implemented. SiS900 also supports Remote Wake On LAN and OnNow for the Desktop PC management. Additional features include a serial EEPROM interface for device information access and a Boot ROM interface up to 128K bytes for remote boot functions support.

SiS900 also integrates analog interface for twisted pair Fast Ethernet applications. SiS900 can be configured for either 100 Mbps (100Base-TX) or 10 Mbps (10Base-T) Ethernet operation. SiS900 consists of 4B5B/Manchester encoder/decoder, scrambler/descrambler, 100Base-TX/10Base-T twisted pair transmitter with wave shaping and output driver, 100Base-TX/10Base-T twisted pair receiver with on chip equalizer and baseline wander correction, clock and data recovery, and Auto Negotiation capability. The addition of internal output wave shaping circuitry and on-chip filters eliminates the need for external filters normally required in 100Base-TX and 10Base-T applications. SiS900 can automatically configure itself for 100 or 10 Mbps and Full or Half Duplex operation with the on-chip Auto Negotiation algorithm. SiS900 PHY can access eleven 16-bit registers through the internal Management Interface (MI) serial port. These registers contain configuration inputs, status outputs, and device capabilities.

#### **1.1.1 Document Organization**

The document is organized in the following sections:

- Chapter 1 Introduction, provides a general description of SiS900 with system diagrams.

- Chapter 2 Pin Description, describes SiS900 package, pin out and each of SiS900 pins.

- Chapter 3 Functional Description, describes the operation of SiS900 in detail.

- Chapter 4 Registers Description, specifies the register sets and register bit definitions.

- Chapter 5 DC and AC Specifications, specifies timing parameters for SiS900.

- Chapter 6 Application Circuit Information, specifies the guideline for application circuit layout.

- Chapter 7 Physical Dimensions, specifies the SiS900 package outline and dimensions

Figure 1-1 SiS900 System Diagram

# 2. PIN ASSIGNMENT

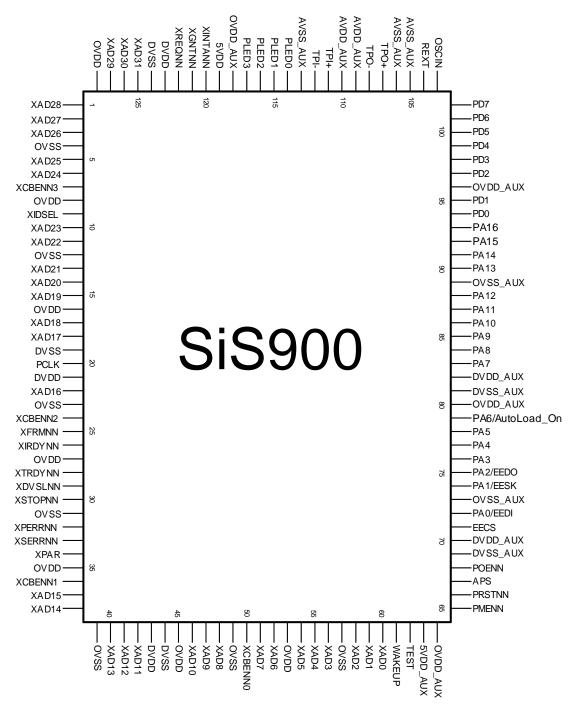

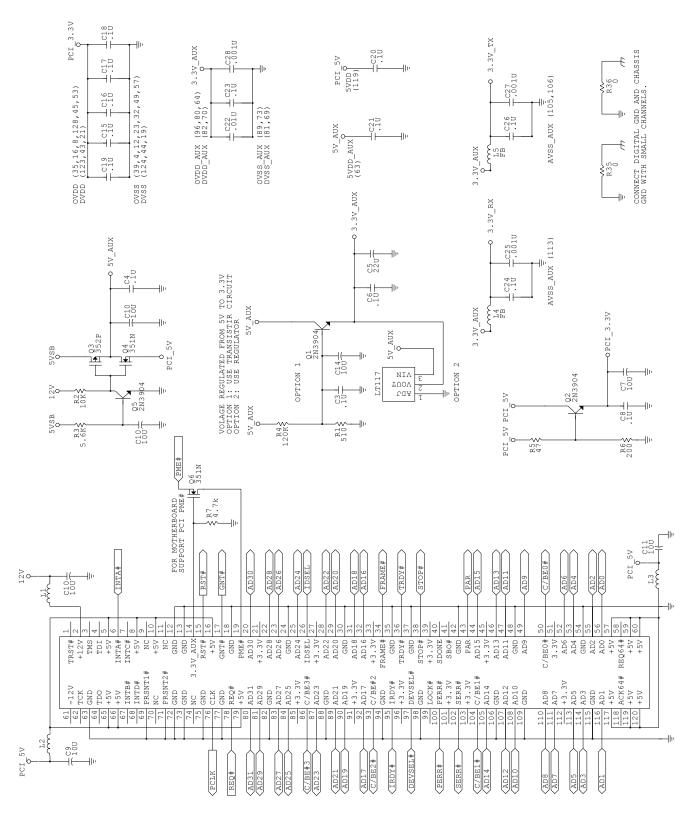

Figure 2-1 Pin Assignment

3

# 2.1 Signal Type Definition

| Ir    |                                                                                                                                                                                                                                                                                                                           |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι     | Input is a standard input only signal.                                                                                                                                                                                                                                                                                    |

| 0     | Totem Pole Output is a standard active driver.                                                                                                                                                                                                                                                                            |

| I/O   | Input/Output signal.                                                                                                                                                                                                                                                                                                      |

| T/S   | Tri-State is a bi-directional, tri-state input/output pin.                                                                                                                                                                                                                                                                |

| S/T/S | Sustained Tri-State is an active low tri-state signal owned and driven by one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent can't start driving a s/t/s signal any sooner than one clock after the previous owner tri-states it. |

| O/D   | Open Drain allows multiple devices to share as a wired OR.                                                                                                                                                                                                                                                                |

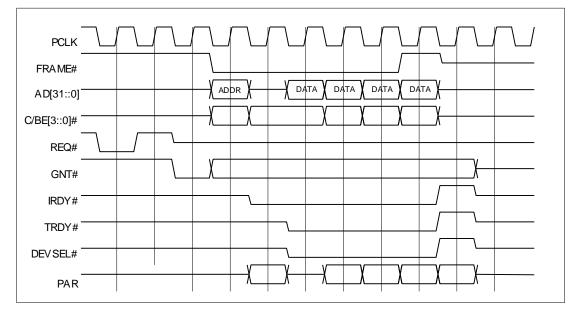

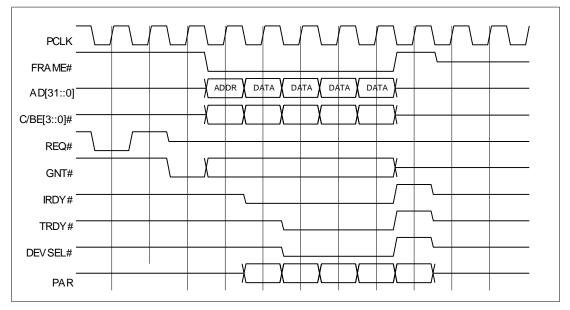

#### 2.2 PCI Bus Interface

| PIN NAME   | PIN NUMBER                                                                                       | ТҮРЕ  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|--------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31::0]  | 125-127, 1-3, 5-6,<br>10-11, 13-15, 17-18,<br>22, 37-38, 40-42,<br>46-48, 51-52, 54-56,<br>58-60 | T/S   | Address and Data<br>Multiplexed address and data bus. As a bus master, the<br>SiS900 will drive address during the first bus phase.<br>During subsequent phase, the SiS900 will either read or<br>write data expecting the target to increment its address<br>pointer. As a bus target, the SiS900 will decode each<br>address on the bus and respond if it is the target being<br>addressed.                                                                           |

| CBE[3::0]# | 7, 24, 36, 50                                                                                    | T/S   | <b>Bus Command/Byte Enable</b><br>During the address phase these signals define the "bus<br>command" or the type of bus transaction that will take<br>place. During the data phase these pins indicate which<br>byte lanes contain valid data. CBE[0]# applies to byte 0<br>(bits7-0) and CBE[3]# applies to byte 3 (bits31-24) in the<br>Little Endian Mode. In Big Endian Mode, CBE[0]#<br>applies to byte 0 (bits31-24) and CBE[3]# applies to<br>bytes 3 (bits7-0). |

| DEVSEL#    | 29                                                                                               | S/T/S | <b>Device Select</b><br>As a target, the SiS900 asserts this signal low when it<br>recognizes its address after FRAME# is asserted. As a<br>bus master, the SiS900 samples this signal to insure that a<br>PCI target recognizes destination address for the data<br>transfer.                                                                                                                                                                                          |

| FRAME#     | 25                                                                                               | S/T/S | <b>Frame</b><br>As a bus master, this signal is asserted low to indicate the beginning and duration of a bus transaction. Data transfer takes place when this signal is asserted. It is de-asserted before the transaction is in its final phase. As a target, the device monitors this signal before decoding the address to check if the current transaction is addressed to it.                                                                                      |

| GNT#       | 121                                                                                              | T/S   | <b>Grant</b><br>This signal is asserted low to indicate to the SiS900 that<br>it has been granted ownership of the bus by the central<br>arbiter. This input is used when the SiS900 is acting as a                                                                                                                                                                                                                                                                     |

|       |     |       | bus master.                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDSEL | 9   | Ι     | Initialization Device Select                                                                                                                                                                                                                                                                                                                                                               |

|       |     |       | This pin is sampled by the SiS900 to identify when configuration read and write accessed are intended for it.                                                                                                                                                                                                                                                                              |

| INTA# | 120 | O/D   | Interrupt A                                                                                                                                                                                                                                                                                                                                                                                |

|       |     |       | This signal is asserted low when an interrupt condition as<br>defined in the Interrupt Status Register, Interrupt Mask,<br>and Interrupt Enable registers occurs.                                                                                                                                                                                                                          |

| IRDY# | 26  | S/T/S | Initiator Ready                                                                                                                                                                                                                                                                                                                                                                            |

|       |     |       | As a bus master, this signal will be asserted low when the<br>SiS900 is ready to complete the current data phase<br>transaction. This signal is used in conjunction with the<br>TRDY# signal. Data transaction takes place at the rising<br>edge of PCLK when both IRDY# and TRDY# are<br>asserted low. As a target, this signal indicates that the<br>master has put the data on the bus. |

| PAR   | 34  | T/S   | Parity                                                                                                                                                                                                                                                                                                                                                                                     |

|       |     |       | This signal indicates even parity across AD[31-0] and C/BE[3-0]# including the PAR pin. As a master, PAR is asserted during address and write data phases. As a target, PAR is asserted during read data phases.                                                                                                                                                                           |

| PCLK  | 20  | Ι     | PCI Bus Clock                                                                                                                                                                                                                                                                                                                                                                              |

|       |     |       | This PCI bus clock provides timing for all bus phases.<br>The rising edge defines the start of each phase. The clock<br>frequency ranges from 0 to 33MHz.                                                                                                                                                                                                                                  |

| PERR# | 32  | S/T/S | Parity Error                                                                                                                                                                                                                                                                                                                                                                               |

|       |     |       | The SiS900 as a master or target will assert this signal<br>low to indicated a parity error on any incoming data<br>(except for special cycles). As a bus master, it will<br>monitor this signal on all write operations (except for<br>special cycles).                                                                                                                                   |

| PME#  | 65  | O/D   | Power Management Event                                                                                                                                                                                                                                                                                                                                                                     |

|       |     |       | The SiS900 may asserts PME# only when both PME_En<br>and PME_Status in PMCSR are set. It is de-asserted<br>when PME_En or PME_Status is cleared by software.<br>The SiS900 will assert PME# when it generates or<br>detects an event that requires the system to change its<br>power state. If auxiliary power source exists, PME# can<br>be asserted even when main power is off.         |

| REQ#  | 122 | T/S   | Request                                                                                                                                                                                                                                                                                                                                                                                    |

|       |     |       | The SiS900 will assert this signal low to request the ownership of the PCI bus to the central arbiter.                                                                                                                                                                                                                                                                                     |

| RST#  | 66  | Ι     | <b>Reset</b><br>When this signal is asserted all outputs of SiS900 will be<br>tri-stated and the device will be put into a known state.                                                                                                                                                                                                                                                    |

| SERR# | 33  | O/D   | System Error                                                                                                                                                                                                                                                                                                                                                                               |

|       |     |       | This signal is asserted low by SiS900 during address parity errors and system errors if enabled.                                                                                                                                                                                                                                                                                           |

| STOP# | 30  | S/T/S | Stop                                                                                                                                                                                                                                                                                                                                                                                       |

|       |     |       | This signal is asserted low by the target device to request                                                                                                                                                                                                                                                                                                                                |

|       |    |       | the master device to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRDY# | 28 | S/T/S | Target Ready                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |    |       | As a target, this signal will be asserted low when the (slave) device is ready to complete the current data phase transaction. This signal is used in conjunction with the IRDY# signal. Data transaction takes place at the rising edge of PCLK when both IRDY# and TRDY# are asserted low. As a master, this signal indicates that the target is ready for the data during write operation and with the data during read operation. |

#### 2.3 Boot ROM/Serial EEPROM Interface

| PIN NAME          | PIN NUMBER | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|-------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA16              | 93         | I/O  | Boot ROM Address 16                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | As an output, this pin is for Boot ROM Address 16.<br>PA16-PA0 provides access up to 128K bytes Boot ROM.<br>This pin also acts as hardware trap to enable MAC test<br>mode during power-up stage if pull-up resistor is used in<br>this pin. MAC test mode is for engineering testing only.<br>For normal operation, this pin shall be pulled-down. |

| PA15              | 92         | I/O  | Boot ROM Address 15                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | As an output, this pin is for Boot ROM Address 15. At<br>power-up stage, if pull-up resistor is used in this pin,<br>PHY test mode is enabled. PHY test mode is for<br>engineering testing only. For normal operation, this pin<br>shall be pulled-down.                                                                                             |

| PA14              | 91         | 0    | Boot ROM Address 14                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 14.                                                                                                                                                                                                                                                                                                 |

| PA13              | 90         | 0    | Boot ROM Address 13                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 13.                                                                                                                                                                                                                                                                                                 |

| PA12              | 88         | 0    | Boot ROM Address 12                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 12.                                                                                                                                                                                                                                                                                                 |

| PA11              | 87         | 0    | Boot ROM Address 11                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 11.                                                                                                                                                                                                                                                                                                 |

| PA10              | 86         | 0    | Boot ROM Address 10                                                                                                                                                                                                                                                                                                                                  |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 10.                                                                                                                                                                                                                                                                                                 |

| PA9               | 85         | 0    | Boot ROM Address 9                                                                                                                                                                                                                                                                                                                                   |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 9.                                                                                                                                                                                                                                                                                                  |

| PA8               | 84         | 0    | Boot ROM Address 8                                                                                                                                                                                                                                                                                                                                   |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 8.                                                                                                                                                                                                                                                                                                  |

| PA7               | 83         | 0    | Boot ROM Address 7                                                                                                                                                                                                                                                                                                                                   |

|                   |            |      | In normal mode, this pin is for Boot ROM Address 7.                                                                                                                                                                                                                                                                                                  |

| PA6<br>/Auto Load | 79         | I/O  | Boot ROM Address 6/Hardware Trap for Enable<br>EEPROM Auto Load Function                                                                                                                                                                                                                                                                             |

|                   |            |      | As an output, this pin is for Boot ROM Address 6. At<br>power-up stage, if pull-up resistor is used in this pin, auto<br>load EEPROM function is enabled. If pull-down resistor                                                                                                                                                                      |

|          |                |     | is used in this pin, auto load EEPROM function is<br>disabled. For normal operation, this pin shall be<br>pulled-up or pulled-down depend on the need of auto<br>loading EEPROM.                                                                |

|----------|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA5      | 78             | 0   | Boot ROM Address 5                                                                                                                                                                                                                              |

|          |                |     | In normal mode, this pin is for Boot ROM Address 5.                                                                                                                                                                                             |

| PA4      | 77             | 0   | Boot ROM Address 4                                                                                                                                                                                                                              |

|          |                |     | In normal mode, this pin is for Boot ROM Address 4.                                                                                                                                                                                             |

| PA3      | 76             | 0   | Boot ROM Address 3                                                                                                                                                                                                                              |

|          |                |     | In normal mode, this pin is for Boot ROM Address 3.                                                                                                                                                                                             |

| PA2/EEDO | 75             | 0   | Boot ROM Address 2/Serial EEPROM Data Output                                                                                                                                                                                                    |

|          |                |     | This is a multiplexed pin. During Serial EEPROM<br>access, the SiS900 will read the contents of the EEPROM<br>serially through this pin. Require external pull-up<br>resister. During Boot ROM access, it acts as Boot ROM<br>Address 2 output. |

| PA1/EESK | 74             | 0   | Boot ROM Address 1/Serial EEPROM Clock                                                                                                                                                                                                          |

|          |                |     | This is a multiplexed pin. During Serial EEPROM<br>access, this pin provides the clock for the Serial<br>EEPROM. During Boot ROM access, it acts as Boot<br>ROM Address 1 output.                                                               |

| PA0/EEDI | 72             | I/O | Boot ROM Address 0/Serial ROM Data In                                                                                                                                                                                                           |

|          |                |     | This is a multiplexed pin. During Serial EEPROM<br>access, the SiS900 will use this pin to serially write op<br>codes, addresses and data into the serial EEPROM.<br>During Boot ROM access, it acts as Boot ROM Address<br>0 output.           |

| EECS     | 71             | 0   | Serial EEPROM Chip Select                                                                                                                                                                                                                       |

|          |                |     | This enables the EEPROM during loading of the Ethernet configuration data.                                                                                                                                                                      |

| PD[7::0] | 102-97, 95, 94 | I/O | Boot ROM Data [7::0]                                                                                                                                                                                                                            |

|          |                |     | In normal mode, this group of 4 signals is for Boot ROM Data 7-0.                                                                                                                                                                               |

| POE#     | 68             | 0   | Boot ROM Output Enable                                                                                                                                                                                                                          |

|          |                |     | It is asserted low during read operation of boot device.                                                                                                                                                                                        |

# 2.4 Transmit/Receive Signals

| PIN NAME | PINNUMBER | ТҮРЕ | DESCRIPTION                                                                                                                   |

|----------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------|

| TPO+     | 107       | 0    | Twisted Pair Transmit Output, Positive.                                                                                       |

| TPO-     | 108       | 0    | Twisted Pair Transmit Output, Negative.                                                                                       |

| TPI+     | 111       | Ι    | Twisted Pair Receive Input, Positive.                                                                                         |

| TPI-     | 112       | Ι    | Twisted Pair Receive Input, Negative.                                                                                         |

| REXT     | 104       | Ι    | Transmit Current Set                                                                                                          |

|          |           |      | An external resistor connected between this pin and GND<br>will set the output current level for the twisted pair<br>outputs. |

| OSCIN  | 103 | Ι              | Clock Oscillator Input                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |     |                | There must be either 25 Mhz crystal between this pin and GND or a 25 Mhz clock applied to this pin. TX_CLK is generated from this input.                                                                                                                                                                                                                                          |

| PLED3# | 117 | I/O            | Programmable LED Output                                                                                                                                                                                                                                                                                                                                                           |

|        |     | O.D.<br>Pullup | The default function of this pin is to be a 100 Mbps Link<br>Detect output. This pin can also be programmed through<br>the MI serial port to indicate other events or by user<br>controlled. This pin can drive an LED from VCC.<br>When programmed as 100 Mbps Link Detect Output<br>(default):<br>1 = No Detect<br>0 = 100 Mbps Link Detected                                   |

| PLED2# | 116 | I/O            | Programmable LED Output                                                                                                                                                                                                                                                                                                                                                           |

|        |     | O.D.<br>Pullup | The default function of this pin is to be an Activity<br>Detect output. This pin can also be programmed through<br>the MI serial part to indicate other events or by user<br>controlled. This pin can drive an LED from VCC.<br>When programmed as an Activity Detect Output<br>(default):<br>1 = No Activity<br>0 = Transmit or Receive packet Occurred, Hold Low for<br>100 ms. |

| PLED1# | 115 | I/O            | Programmable LED Output                                                                                                                                                                                                                                                                                                                                                           |

|        |     | O.D.<br>Pullup | The default function of this pin is to be a Full Duplex<br>Detect output. This pin can also be programmed through<br>the MI serial part to indicate other events or by user<br>controlled. This pin can drive an LED from both VCC<br>and GND.<br>When programmed as Full Duplex Detect Output<br>(default).<br>1 = Half Duplex<br>0 = Full Duplex                                |

| PLED0# | 114 | I/O            | Programmable LED Output                                                                                                                                                                                                                                                                                                                                                           |

|        |     | O.D.<br>Pullup | The default function of this pin is to be a 10 Mbps Link<br>Detect output. This pin can also be programmed through<br>the MI serial port to indicate other events or by user<br>controlled. This pin can drive an LED from both VCC<br>and GND.<br>When programmed as 10 Mbps Link Detect Output<br>(default):<br>1 = No Detect<br>0 = 10 Mbps Link Detected                      |

# 2.5 Power Management Signals

| PIN NAME | PINNUMBER | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                       |

|----------|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APS      | 67        | Ι    | Auxiliary Power Source                                                                                                                                                                                                            |

|          |           |      | This pin indicates the presence of auxiliary power source.<br>When "1" it indicates the presence of auxiliary power<br>source, SiS900 is capable of asserting PME# from<br>D3cold. When "0" it indicates the absence of auxiliary |

8

|        |    |   | power source, SiS900 can't assert PME# from D3cold.                                                                                                                                                                                                |

|--------|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST   | 62 | Ι | Internal Testing Pin                                                                                                                                                                                                                               |

|        |    |   | THIS PIN WILL RESERVE FOR FUTURE TESTING<br>USE. USER CAN TIE THIS PIN LOW TO PREVENT<br>FROM FLOATING.                                                                                                                                            |

| WAKEUP | 61 | 0 | Wake Up                                                                                                                                                                                                                                            |

|        |    |   | This pin is a high active power management event<br>indication. The SiS900 will assert WAKEUP when it<br>generates or detects an event, which requires the system<br>to change its power state. It is de-asserted when main<br>power is turned on. |

#### 2.6 Power and Ground Pins

| PIN NAME  | PIN NUMBER         | ТҮРЕ                                                                                                                                                                         | DESCRIPTION                                                                                                                                                                     |  |

|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DVDD      | 21, 43, 123        |                                                                                                                                                                              | Digital supply: +3.3Vdc is required. This power is used<br>for internal logic except sleepless logic and may be from<br>PCI connector pins or 3.3V regulator output from +5Vdc. |  |

| DVSS      | 19, 44, 124        |                                                                                                                                                                              | Digital ground.                                                                                                                                                                 |  |

| DVDD_AUX  | 70, 82             | Digital supply: +3.3Vdual is required. This power is used<br>for internal sleepless logic and may be from PCI<br>connector pin A14 or 3.3V regulator output from<br>+5Vdual. |                                                                                                                                                                                 |  |

| DVSS_AUX  | 69, 81             |                                                                                                                                                                              | Digital ground for internal sleepless logic.                                                                                                                                    |  |

| OVDD      | 8, 16, 27, 35, 45, |                                                                                                                                                                              | Digital supply: +3.3Vdc is required.                                                                                                                                            |  |

|           | 53, 128            |                                                                                                                                                                              |                                                                                                                                                                                 |  |

| OVSS      | 4, 12, 23, 31, 39, |                                                                                                                                                                              | Digital ground.                                                                                                                                                                 |  |

|           | 49, 57             |                                                                                                                                                                              |                                                                                                                                                                                 |  |

| OVDD_AUX  | 64, 80, 96, 118    |                                                                                                                                                                              | Digital supply (sleepless): +3.3Vdual is required.                                                                                                                              |  |

| OVSS_AUX  | 73, 89             |                                                                                                                                                                              | Digital ground (sleepless).                                                                                                                                                     |  |

| 5VDD*     | 119                |                                                                                                                                                                              | Digital supply: +5Vdc is required. This power is from PCI connector pins.                                                                                                       |  |

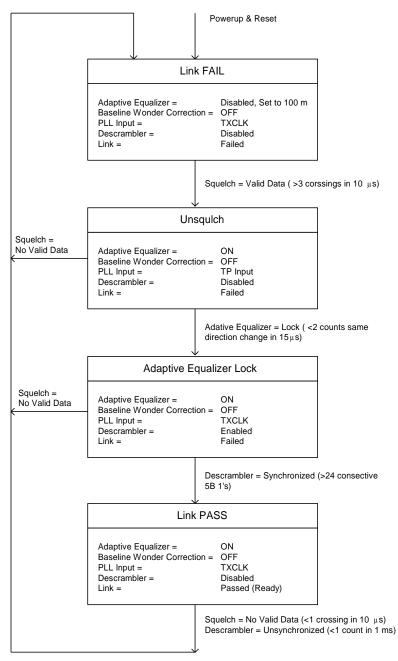

| 5VDD_AUX* | 63                 |                                                                                                                                                                              | Digital supply: +5Vdual is required. This power is from LAN WAKE-UP header.                                                                                                     |  |