# Content

| 1. |                                                                                     | SiS530/ SiS5595 OVERVIEW                                                                                                                                                                                                                        | 3                                                        |

|----|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2. |                                                                                     | FEATURES                                                                                                                                                                                                                                        | 2                                                        |

|    | 2.1.                                                                                | SiS530 HOST, PCI, 3D A.G.P. VIDEO/GRAPHICS & MEMORY CONTROLLER                                                                                                                                                                                  | 3                                                        |

|    | 2.2.                                                                                | FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                        | 10                                                       |

| 3. | •                                                                                   | PIN ASSIGNMENT                                                                                                                                                                                                                                  | 12                                                       |

|    | 3.1.<br>3.2.<br>3.3.<br>3.4.                                                        | SiS530 PIN ASSIGNMENT (TOP VIEW-LEFT SIDE)                                                                                                                                                                                                      | 13<br>14                                                 |

| 4. | •                                                                                   | SIGNAL DESCRIPTION                                                                                                                                                                                                                              | 22                                                       |

|    | 4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.<br>4.7.<br>4.8.                        | HOST INTERFACE SIGNALS L2 CACHE INTERFACE SIGNALS DRAM INTERFACE SIGNALS PCI INTERFACE SIGNALS IDE INTERFACE SIGNALS VGA INTERFACE SIGNALS POWER SIGNALS MISC. SIGNALS                                                                          | 23<br>24<br>25<br>28<br>28<br>30                         |

| 5. | •                                                                                   | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                          | 31                                                       |

|    | 5.1.<br>5.1.1<br>5.2.<br>5.3.<br>5.3.1                                              | CACHE CONTROLLERDRAM CONTROLLERDRAM CONFIGURATION                                                                                                                                                                                               | 31<br>34<br>35                                           |

| С  |                                                                                     | SDRAINI<br>JRATION35<br>B. DRAM SCRAMBLE TABLE                                                                                                                                                                                                  |                                                          |

|    | 5.3.4<br>5.3.6<br>5.4.<br>5.4.2<br>5.4.3<br>5.5.<br>5.6.<br>5.7.1<br>5.7.2<br>5.8.8 | ARBITER REFRESH CYCLE PCI BRIDGE PCI ARBITER PCI MASTER BRIDGE PCI TARGET BRIDGE POWER MANAGEMENT SUPPORT IDE CONTROLLER INTEGRATED HIGH PERFORMANCE 3D VGA CONTROLLER HIGHLIGHT FUNCTION BLOCK TECHNICAL DESCRIPTION BALL CONNECTIVITY TESTING | 39<br>39<br>39<br>42<br>44<br>46<br>52<br>52<br>53<br>65 |

|    | 5.8.1<br>5.8.2                                                                      |                                                                                                                                                                                                                                                 |                                                          |

|    |                                                                                     |                                                                                                                                                                                                                                                 |                                                          |

| 6.         | HARDWARE TRAPPING DESCRIPTION                     | 70  |

|------------|---------------------------------------------------|-----|

| 7.         | CORE LOGIC CONFIGURATION REGISTER                 | 73  |

| 7.1.       | HOST-TO-PCI BRIDGE CONFIGURATION SPACE            | 73  |

| 7.1        |                                                   | 73  |

| 7.1        |                                                   | 73  |

| 7.1        |                                                   |     |

| 7.1        |                                                   |     |

| 7.1        |                                                   | 74  |

| 7.1        |                                                   |     |

| 7.1        |                                                   |     |

| 7.1        | .8. DISPLAY STATUS                                | 75  |

| 7.1        | 9. GART AND PAGE TABLE CACHE                      | 75  |

| 7.1        | .10. DRAM PRIORITY TIMER                          |     |

| 7.1        | .11. A.G.P. AND HOST BRIDGE                       |     |

| 7.2.       | DEVICE 2 (VIRTUAL PCI-TO-PCI BRIDGE)              | 75  |

| 7.3.       | PCI IDE DEVICE                                    | 76  |

| 7.4.       | REGISTER DESCRIPTIONS                             |     |

| 7.4        |                                                   |     |

|            | 2. VIRTUAL PCI-TO-PCI BRIDGE REGISTERS (DEVICE 2) |     |

| 7.4        |                                                   | 112 |

| _          |                                                   |     |

| 8.         | INTEGRATED 3D VGA CONTROLLER REGISTERS            |     |

| 8.1.       | GENERAL REGISTERS                                 | 127 |

| 8.2.       | CRT CONTROLLER REGISTERS                          | 129 |

| 8.3.       | SEQUENCER REGISTERS                               | 136 |

| 8.3        | .1. SEQUENCER INDEX REGISTER                      | 136 |

| 8.4.       | GRAPHICS CONTROLLER REGISTER                      |     |

| 8.5.       | ATTRIBUTE CONTROLLER AND VIDEO DAC REGISTERS      |     |

| 8.6        | COLOR REGISTERS                                   |     |

| 8.6        |                                                   |     |

| 8.7.       | EXTENDED REGISTERS                                |     |

| 8.7        |                                                   |     |

|            | 2D GRAPHICS ENGINE REGISTER                       |     |

| 8.8.       |                                                   |     |

| 8.8        |                                                   |     |

| 8.8<br>8.8 |                                                   |     |

| 8.8        |                                                   |     |

| 8.8        |                                                   |     |

| 8.9.       | VIDEO ACCELERATOR REGISTERS                       |     |

|            |                                                   |     |

| 8.10.      |                                                   |     |

| 8.11.      | AGP CONFIGURATION REGISTERS                       |     |

| 8.12.      |                                                   |     |

| 8.13.      | LEGEND OF 3D REGISTERS                            |     |

|            | 3.1. LEGEND OF 3D REGISTERS                       |     |

|            | 3.2. 3D REGISTERS SUMMARY                         |     |

|            | 3.3. VERTEX PARAMETER REGISTERS                   |     |

|            | 3.4. PRIMITIVE SETTING REGISTERS                  |     |

|            | 3.5. ENGINE FIRE & STATUS REGISTER                |     |

|            | 3.6. ENABLE SETTING REGISTER                      |     |

| _          | 3.7. Z SETTING REGISTERS                          |     |

| _          | 3.8. ALPHA SETTING REGISTERS                      |     |

|            | 3.9. DESTINATION SETTING REGISTERS                |     |

| 8.1        | 3.10. MISCELLANEOUS SETTING REGISTERS             | 224 |

| SiS530 Host, | PCI, 3D | <b>Graphics</b> | & Memory | y Controllei |

|--------------|---------|-----------------|----------|--------------|

|              |         |                 |          |              |

|      |                                           | ,   |

|------|-------------------------------------------|-----|

|      | 3.11. TEXTURE SETTING REGISTERS           |     |

|      | 3.13. STIPPLE PATTERN REGISTERS           | 239 |

| 9.   | ELECTRICAL CHARACTERISTICS                | 245 |

| 9.1. | ABSOLUTE MAXIMUM RATINGS                  | 245 |

| 9.2. | DC CHARACTERISTICS                        | 245 |

| 9.3. | DC CHARACTERISTICS FOR DAC (ANALOG OUTPUT |     |

|      | CHARACTERISTICS)                          | 245 |

| 9.4. | AC CHARACTERISTICS FOR DAC (ANALOG OUTPUT |     |

|      | CHARACTERISTICS)                          | 246 |

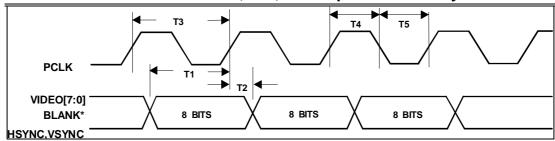

| 9.5. | AC CHARACTERISTICS FOR FOR INTEGRATED 3D  |     |

|      | VGA CONTROLLER                            | 246 |

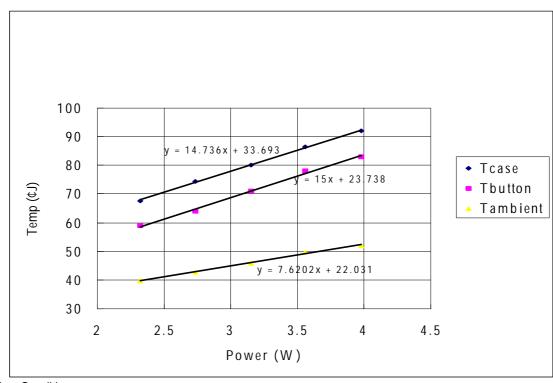

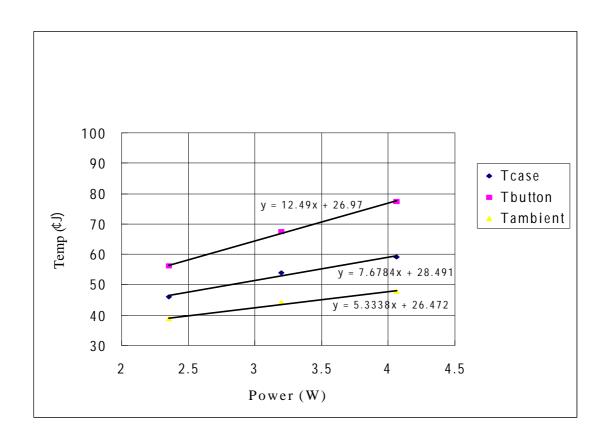

| 10.  | THERMAL ANALYSIS                          | 249 |

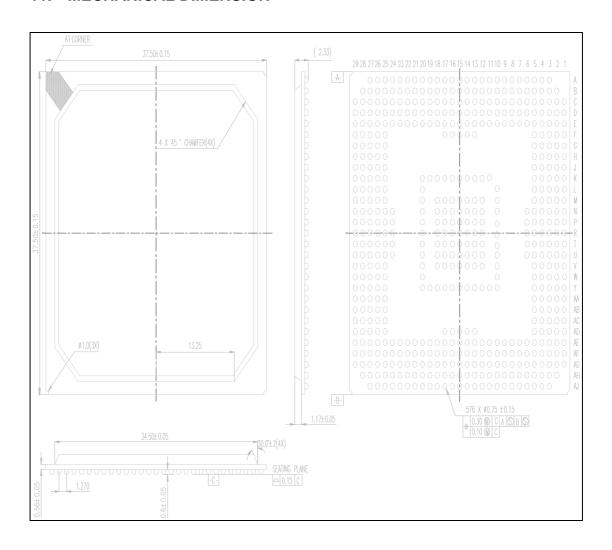

| 11.  | MECHANICAL DIMENSION                      | 251 |

| 12.  | TOPSIDE MARK IDENTIFICATION               | 252 |

| 13.  | COPYRIGHT NOTICE                          | 253 |

|      |                                           |     |

## 1 SiS530/SiS5595 OVERVIEW

SiS530 Host, PCI, 3D A.G.P. Video/Graphics & Memory Controller SiS5595 PCI SYSTEM I/O

The P5 A.G.P./VGA chipset, SiS530/5595, provides a high performance/cost index Desktop/Mobile solution for the Intel Pentium P54C/P55C, AMD K5/K6/K6-II, Cyrix M1/M2 and other compatible Pentium CPU with 3D A.G.P. VGA system.

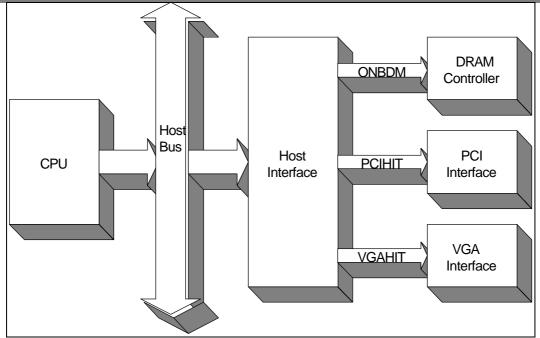

The Host, PCI, 3D A.G.P. Video/Graphics & Memory Controller, SiS530 integrates the Host-to-PCI bridge, the PCI interface, the L2 cache controller, the DRAM controller, the high performance hardware 2D/3D VGA controller, and the PCI IDE controller.

The Host interface supports Synchronous/Asynchronous Host/DRAM clocking configuration to eminently improve the system performance and DRAM compatibility issues.

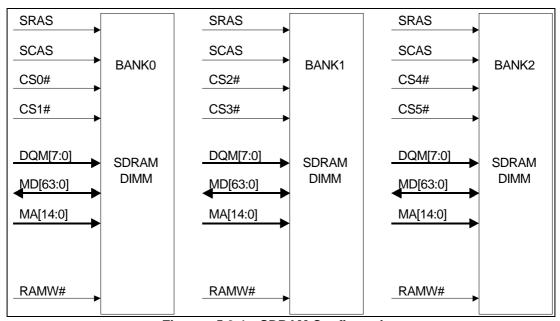

The L2 cache controller can support up to 2 MB P.B. SRAM, and the DRAM controller can support SDRAM memory up to 1.5 GBytes with three double-sided SDRAM DIMMs configuration. The cacheable DRAM sizes support up to 256 MBytes.

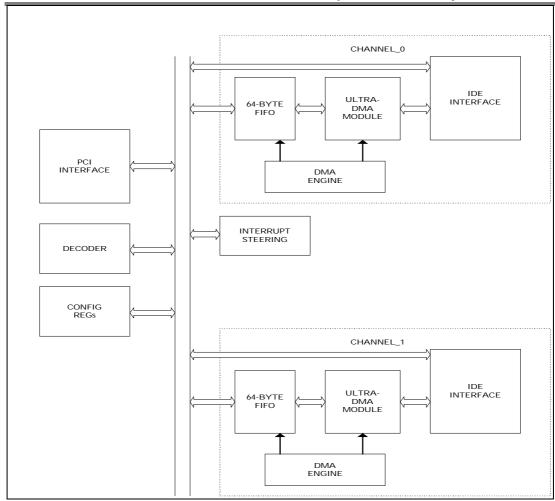

The built-in fast PCI IDE controller supports the ATA PIO/DMA, and the Ultra DMA33/66 function that support the data transfer rate up to 66 MB/s. It provides the separate data path for two IDE channels that can eminently improve the performance under the multi-tasking environment.

The A.G.P. internal interface is supported for integrated H/W 3D VGA controller. The integrated VGA controller is a high performance and targeted at 3D graphics application. In addition, the integrated 3D Video/Graphics controller adopts the 64bits 100MHz host bus interface high technology to improve the performance eminently. To cost-effective the PC system, the share system memory architecture will be adopted and it can flexibly using the 2MB, 4MB and 8MB frame buffer size from programming the system BIOS. To enhance the system performance, SiS530 also supports the local frame buffer solution and memory sizes can support up to 8MB with SDRAM and SGRAM.

In addition to provide the standard interface for CRT monitors, it also provides the Digital Flat Panel Port (DFP) for a standard interface between a personal computer and a digital flat panel monitor. This port allows a host computer to connect directly to an external flat panel monitor without the need for analog-to-digital conversion found in most flat panel monitors today. As for DVD solution, the integrated 3D VGA controller also support DVD H/W accelerator to improve the DVD playback performance.

The SiS5595 PCI system I/O integrates the PCI-to-ISA bridge with the DDMA, PC/PCI DMA and Serial IRQ capability, the ACPI/Legacy PMU, the Data Acquisition Interface, the Universal Serial Bus host/hub interface, and the ISA bus interface which contains the ISA bus controller, the DMA controllers, the interrupt controllers, the Timers and the Real Time Clock (RTC). It also integrates the Keyboard Controller and PS/2 mouse interface that can support keyboard power on function for users to power on system by entering the hot key or password from keyboard. The built-in USB controller, which is fully compliant to OHCI (Open Host Controller Interface), provides two USB ports capable of running full/low speed USB devices. The Data Acquisition Interface offers the ability of monitoring and reporting the environmental condition of the PC. It could monitor 5 positive analog voltage inputs, 2 Fan speed inputs, and one temperature input.

In addition, SiS5595 also supports ACPI function to meet *Advanced Configuration and Power Interface* (ACPI) 1.0 specification for Windows 98 environment, it can support power-management timer, Power button, Real-time clock alarm wake up, more sleeping state, ACPI LED for sleeping and working state, LAN wake up, Modem Ring In wake up, and OnNow initiative function.

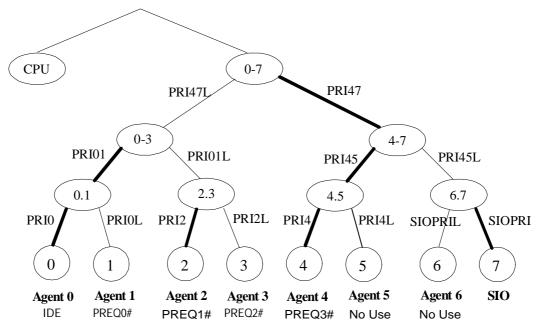

The following will show the system block diagram. **PBSRAM CPU** Host Address Bus Host Data Bus CRT Monite TAG RAM MA Rus DRAM Digital Monit (LCD Panel) IDE **SiS530** Bus IDE DEVICE Transceiver PCI Bus PCI Device H/W USB SiS5595 Monitor GPIOs Sensors Keyboard BIOS ISA Bus

Figure 1.1-1 SiS530/SiS5595 System Block Diagram

2

#### 2 FEATURES

# 2.1 SiS530 HOST, PCI, 3D A.G.P. VIDEO/GRAPHICS & MEMORY CONTROLLER

# ■ Supports Intel/AMD/Cyrix/IDT Pentium CPU Host Bus at 66/75/83/95/100 MHz and 2.5/3.3V Bus Interface

- Supports the Pipelined Address of Pentium compatible CPU

- Supports the Linear Address Mode of Cyrix CPU

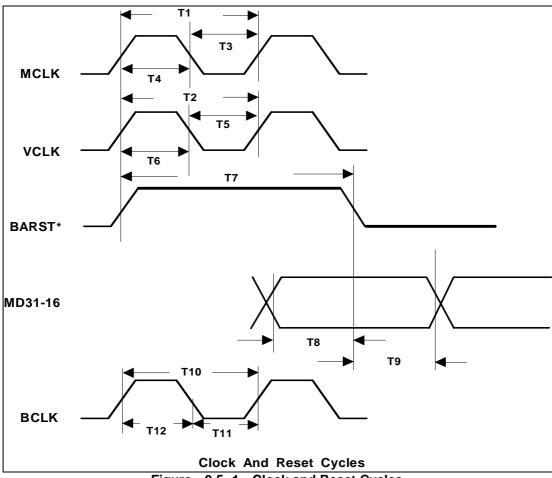

- 100/100, 95/95, 83/83, 75/75 and 66/66 MHz Synchronous Host/DRAM clocking configuration

- 100/75, 95/75, 83/66, 66/100 and 66/83 MHz Asynchronous Host/DRAM clocking configuration

- Supports Host Bus operation for integrated 3D VGA Controller

### ■ Meets PC99 Requirements

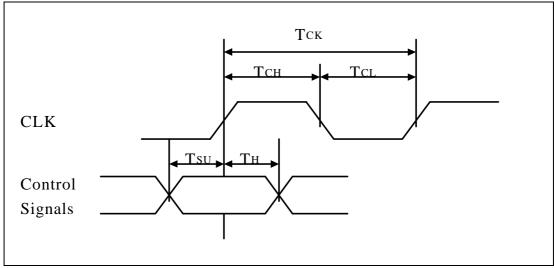

#### ■ Supports PCI Revision 2.2 Specification

### ■ Integrated Super AGP VGA for Hardware 2D/3D Video/Graphics Accelerators

- Supports tightly coupled 64 bits 100MHz host interface to VGA to speed up GUI performance and the video playback frame rate

- Built-in programmable 24-bit true-color RAMDAC up to 230 MHz pixel clock

- Built-in reference voltage generator and monitor sense circuit

- Supports loadable RAMDAC for gamma correction in high color and true color modes

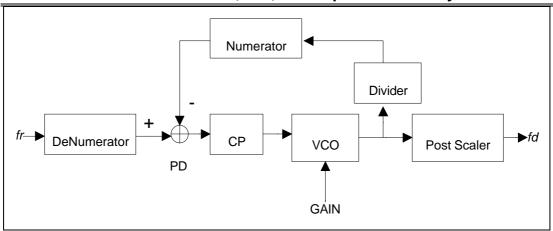

- Built-in dual-clock generator

- Supports Multiple Adapters and Multiple Monitors

- Built-in PCI multimedia interface

- Flexible design for shared frame buffer or local frame buffer architecture

- Shared System Memory Area 2MB, 4MB and 8MB

- Supports SDRAM and SGRAM local frame buffer and memory size up to 8 MB

- Supports Digital Flat Panel Port for Digital Monitor (LCD Panel)

- Supports DVD H/W Accelerator

#### ■ Integrated Second Level (L2) Cache Controller

- Write Back Cache Mode

- Direct Mapped Cache Organization

- Supports Pipelined Burst SRAM

- Supports 256K/512K/1M/2M Bytes Cache Sizes

- Cache Hit Read/Write Cycle of 3-1-1-1

- Cache Back-to-Back Read Cycle of 3-1-1-1-1-1-1

- Supports Single Read Allocation for L2 Cache

- Supports Concurrency of CPU to L2 cache and Integrated A.G.P. VGA master to DRAM accesses

#### ■ Integrated DRAM Controller

- Supports up to 3 double sided DIMMs (6 rows memory)

- Supports 8Mbytes to 1.5 GBytes of main memory

- Supports Cacheable DRAM Sizes up to 256 MBytes

- Supports 1M/2M/4M/8M/16M/32M x N for 2-bank or 4-bank SDRAM

- Supports 3.3V DRAM

- Supports Concurrent Write Back

- Supports CAS before RAS Refresh, Self Refresh

- Supports Relocation of System Management Memory

- Programmable CS#, DQM#, SRAS#, SCAS#, RAMWE# and MA Driving Current

- Option to Disable Local Memory in Non-cacheable Regions

- Entries GART cache to Minimize the Number of Memory Bus Cycles Required for Accessing Graphical Texture Memory

- Programmable Counters to Ensure Guaranteed Minimum Access Time for Integrated A.G.P. VGA, CPU, and PCI accesses

- Two Programmable Non-cacheable Regions

- Supports X-1-1-1/X-2-2-2 Burst Write Cycles

- Fully Configurable for the Characteristic of Shadow RAM (640 KBytes to 1 MBytes)

- Shadow RAM in Increments of 16 KBytes Built-in 8 Way Associative/16

- Supports SDRAM 7/8-1-1-1 Burst Read Cycles

#### ■ Provides High Performance PCI Arbiter

- Supports up to 4 PCI Masters

- Supports Rotating Priority Mechanism

- Hidden Arbitration Scheme Minimizes Arbitration Overhead

- Supports Concurrency between CPU to Memory and PCI to PCI

- Supports Concurrency between CPU to 33Mhz PCI Access and 33Mhz PCI to integrated A.G.P. VGA Access

- Programmable Timers Ensure Guaranteed Minimum Access Time for PCI Bus Masters, and CPU

#### ■ PCI Bus Interface

- Supports 32-bit PCI local bus standard Revision 2.2 compliant

- Integrated write-once subsystem vendor ID configuration register

- Supports zero wait-state memory mapped I/O burst write

- Integrated 2 stages PCI post-write buffer to enhance frame buffer write performance

- Integrated 256 bits read cache to enhance frame buffer read performance

- Supports full 16-bit re-locatable VGA I/O address decoding

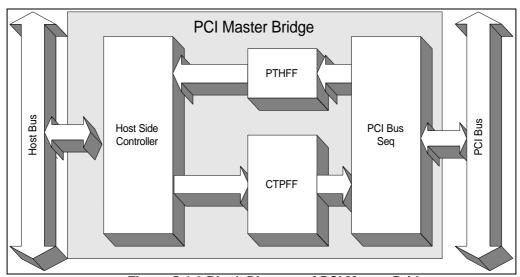

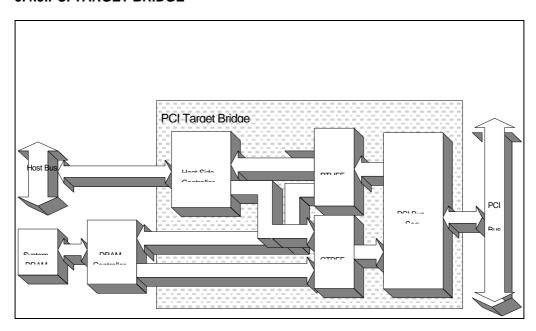

#### ■ Integrated Host-to-PCI Bridge

- Supports Asynchronous PCI Clock

- Translates the CPU Cycles into the PCI Bus Cycles

- Zero Wait State Burst Cycles

- Supports Pipelined Process in CPU-to-PCI Access

- Maximum PCI Burst Transfer from 256 Bytes to 4 Kbytes

- Supports Memory Remapping Function for PCI master accessing Graphical Window

#### ■ Integrated A.G.P. Compliant Target/66Mhz Host-to-PCI Bridge

- Supports Graphic Window Size from 4MBytes to 256MBytes

- Supports Pipelined Process in CPU-to-Integrated 3D A.G.P. VGA Access

- Supports 8 Way, 16 Entries Page Table Cache for GART to enhance Integrated A.G.P. VGA Controller Read/Write Performance

- Supports PCI-to-PCI bridge function for memory write from 33Mhz PCI bus to Integrated A.G.P. VGA

- Integrated Posted Write Buffers and Read Prefetch Buffers to Increase System Performance

- CPU-to-Memory Posted Write Buffer (CTMFF) with 12QW Deep, Always Sustains 0

Wait Performance on CPU-to-Memory

- CPU-to-Memory Read Buffer with 4 QW Deep

- CPU-to-PCI Posted Write Buffer with 2 QW Deep

- PCI-to-Memory Posted Write Buffer with 8 QW Deep, Always Streams 0 Wait Performance on PCI-to/from-Memory Access

- PCI-to-Memory Read Prefetch Buffer with 8 QW Deep

- CPU-to-VGA Posted Write Buffer with 4 QW Deep

#### ■ Fast PCI IDE Master/Slave Controller

- Bus Master Programming Interface for Windows 98 Compliant Controller

- Plug and Play Compatible

- Supports Scatter and Gather

- Supports Dual Mode Operation Native Mode and Compatibility Mode

- Supports IDE PIO Timing Mode 0, 1, 2, 3 and 4

- Supports Multiword DMA Mode 0, 1, 2

- Supports Ultra DMA 33/66

- Two Separate IDE Bus

- Two 16 DW FIFO for PCI Burst Transfers.

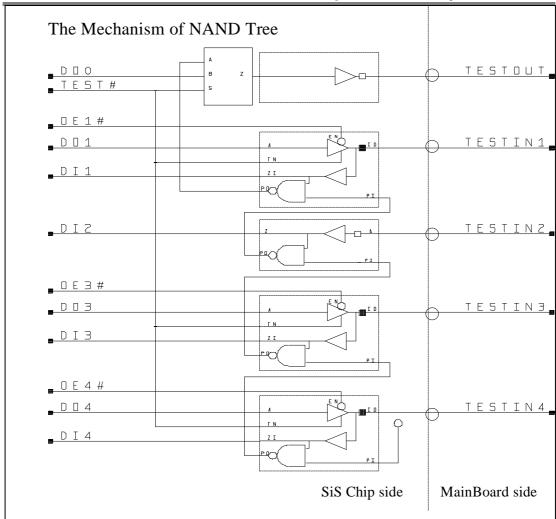

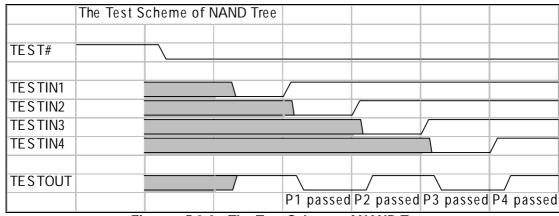

- Supports NAND Tree for Ball Connectivity Testing

- 576-Balls BGA Package

- 3.3V Core with mixed 2.5V, 3.3V and 5V I/O CMOS Technology

# 2.1.1. INTEGRATED HIGH PERFORMANCE & HIGH QUALITY 3D GRAPHICS/VIDEO ACCELERATORS

### High Performance & High Quality 3D Accelerator

- Integrated a high performance 3D engine

- Integrated 32-bit floating point format VLIW triangle setup engine

- Integrated 16kbit texture cache

- Supports Super-AGP for texture fetch

- Peak polygon rate: 800K polygon/sec @ 50 pixel/polygon with Gouraud shaded, point-sampled, linear and bilinear texture mapping

- Peak fill rate: 40M pixel/sec

- Integrated a high quality 3D engine

- Supports solid, flat, and Gouraud shading

- Supports high quality dithering

- Supports Z-test, Alpha-test, and scissors clipping test

- Supports line pattern, and ROP

- Supports Z-buffer and Alpha buffer

- Supports per-pixel texture perspective correction

- Supports point-sampled, linear, bi-linear, and tri-linear texture filtering

- Supports MIP structure texture

- Supports rectangle structure texture

- Supports 1/2/4 BPP palletize texture

- Supports 1/2/4/8 BPP luminance texture

- Supports 4/8 BPP mix mode texture format

- Supports 8/16/24/32 BPP RGB/ARGB texture format

- Supports video texture in all supported texture formats

- The supported video formats are RGB555, RGB565, and YUV422 formats

- Supports texture transparency, blending, wrapping, mirror, and clamping

- Supports fogging, Alpha blending, and primitive transparency

#### High Performance 2D Accelerator

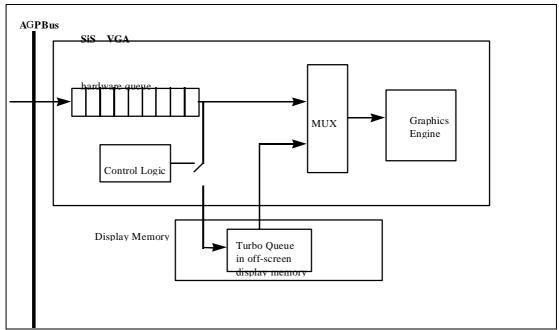

- Integrated 42 double-words hardware command queue

- Supports Turbo Queue (Software Command Queue in off-screen memory) architecture to achieve extra-high performance

- Integrated Direct Draw Accelerator

- Integrated 1T 64-bit BITBLT graphics engine with the following functions:

- 256 raster operations

- Rectangle fill

- Color expansion

- Enhanced Color expansion

- Multiple Scan-line

- Poly-Line-drawing with styled pattern

- Integrated 8x8 pattern registers

- Integrated 8x8 mask registers

- Rectangle Clipping

- Transparent BitBlt

- Trapezoid Fill

- Supports memory-mapped, zero wait-state, burst engine write

- Supports burst frame buffer read/write for SDRAM

- Integrated 64x64x2 bit-mapped hardware cursor

- Maximum 8M Bytes frame buffer with linear addressing

- Integrated 4 stages engine write-buffer and 9x64 bits read-buffer to minimize engine wait-state

- Integrated 64x32 CRT FIFOs to support super high resolution graphics modes and reduce CPU wait-state

#### Video Accelerator

- Supports single frame buffer architecture

- Supports YUV-to-RGB color space conversion

- Supports bi-linear video interpolation with integer increments of 1/64

- Supports graphics and video overlay function

- Independent graphics and video formats

- 16 color-key and/or chroma-key operation

- 3-bit graphics and video blending

- Supports current scan line of refresh read-back

- Supports tearing free double buffer swapping

- Supports RGB555, RGB565, YUV422, and YUV420 video format

- Integrated two 96x64 video playback line buffers

- Supports DCI Drivers

- Supports Direct Draw Drivers

#### **DVD H/W Accelerator**

- Supports Color Space Conversion

- Supports Video Scaling

- Supports YUV12 Format

### Display Memory Interface

#### Supports Local Frame Buffer:

- Supports SDRAM and SGRAM timing

- Supports 32/64 bits LVTTL memory data bus interface

- Supports Block-Write function for SGRAM

- Supports 2MB, 4MB, and 8MB memory configuration

- Supports 1Mx16, 1Mx32, 256Kx32, 512Kx32 SDRAM/SGRAM types up to 100 MHz

#### Supports Shared Frame Buffer:

- Supports SDRAM timing

- Supports 64 bits memory data bus interface

- Supports programmable 2MB, 4MB, and 8MB memory configuration

#### High Integration

- Integrated programmable 24-bit true-color RAMDAC up to 230 MHz pixel clock

- Integrated reference voltage generator and monitor sense circuit

- Supports loadable RAMDAC for gamma correction in high color and true color modes

- Integrated dual-clock generator

- Integrated PLL loop filter

- Integrated two 96x64 video line buffers for MPEG video playback

- Integrated PCI multimedia interface

#### Resolution, Color & Frame Rate

- Supports 230 MHz pixel clock

- Supports super high resolution graphics modes

- 640x480 4/8/16/32 bpp @85Hz NI

- 800x600 8/16/32 bpp @ 85Hz NI

- 1024x768 8/16/32 bpp @ 85Hz NI

- 1280x1024 8/16/32 bpp @ 85 Hz NI (32-bpp mode for local frame buffer only)

- 1600x1200 8/16 bpp @256 colors 85Hz NI (16-bpp mode for local frame buffer only)

- Supports virtual screen up to 2048x2048

- Supports 80/132 columns text modes

#### Digital Flat Panel Port

- Supports low-cost TMDS and LVDS interface

- Supports TFT-24bit, TFT-18bit, TFT-12bit LCD Monitor

- Supports DDC2B (VESA DDC 3.0) for display configuration and detection

- VESA DPMS support for display power management

- Compliant with VESA EDID 2.0 Standard

- Supports Hot Plugging function defined by VESA Plug and Display (P&D) 1.0 Standard

- Supports up to 1024x768@75Hz (VESA standard CRT timings)

- Supports 85MHz pixel clock for 1280x1024 flat panel display by using the reduced refresh rate timing

### **Power Management**

- Supports VESA Display Power Management Signaling (DPMS) compliant VGA monitor for power management

- Supports direct I/O command to force graphics controller into standby/suspend/off state

9

■ Power down internal SRAM in direct color mode

#### Multimedia Application

- Supports DDC1 and DDC2B specifications

- Supports RAMDAC snoop for multimedia applications

#### Miscellaneous

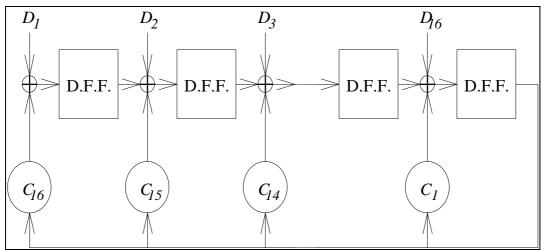

Supports Signature Analysis for automatic test

#### 2.2. FUNCTIONAL BLOCK DIAGRAM

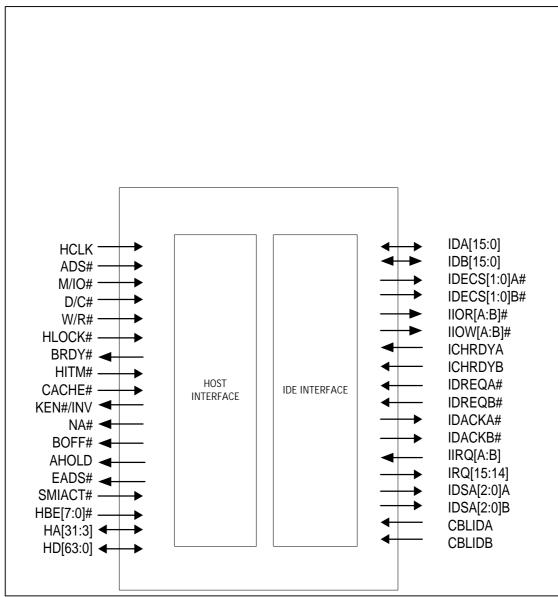

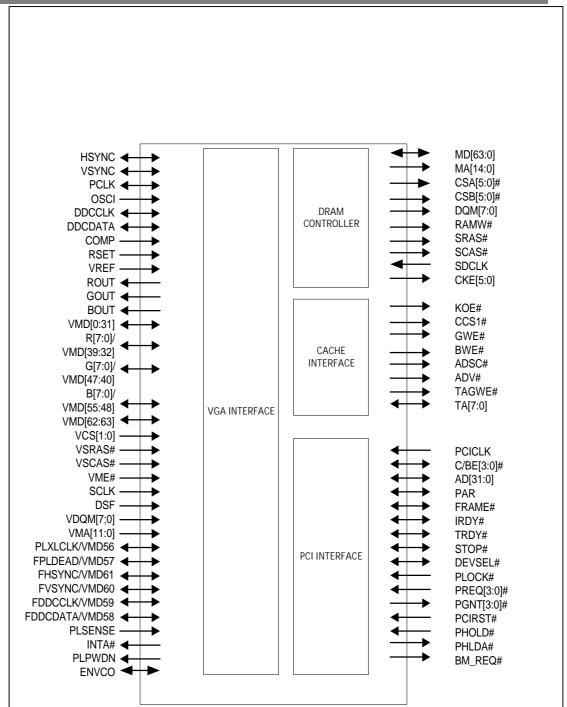

Figure 2.2-1 Functional Block Diagram (1)

~To be continued

Figure 2.2-2 Functional Block Diagram (2)

## 3 PIN ASSIGNMENT

## 3.1. SiS530 PIN ASSIGNMENT (TOP VIEW-LEFT SIDE)

|    | 1       | 2          | 3       | 4           | 5           | 6           | 7     | 8      | 9    | 10        | 11        | 12    | 13        | 14         | 15          |    |

|----|---------|------------|---------|-------------|-------------|-------------|-------|--------|------|-----------|-----------|-------|-----------|------------|-------------|----|

| A  |         |            | AVDD1   | AVDD<br>2/3 | BOUT        | ROUT        | AVSS4 | MD29   | MD59 | MD24      | MD22      | MD19  | MD49      | CKE2       | CKE4        | A  |

| В  |         | ENVCO      | DDCCLK  | AVSS<br>2/3 | AVDD4       | GOUT        | RSET  | MD62   | MD27 | MD57      | MD55      | MD52  | MD17      | CKE1       | DQM3        | В  |

| С  | VMD63   | PLPWD<br>N | DDCDATA | VSYNC       | NC          | NC          | VREF  | MD30   | MD28 | MD25      | MD23      | MD20  | MD18      | CKE0       | DQM7        | С  |

| D  | PL-DCLK | VMD60      | VMD62   | HSYNC       | NC          | NC          | NC    | MD31   | MD60 | MD26      | MD54      | MD21  | MD51      | MD16       | DQM2        | D  |

| E  | VCS1#   | VMD56      | VMD57   | VMD59       | OSCI        | AVSS1       | COMP  | MD63   | MD61 | MD58      | MD56      | MD53  | MD48      | CKE5       | NC          | E  |

| F  | VMD55   | VDQM4      | VDQM6   | VDQM7       | PLSENS<br>E |             |       |        |      |           |           |       | MD50      | CKE3       | NC          | F  |

| G  | VMD50   | VMD51      | VMD52   | VMD54       | VMD61       |             |       |        |      |           |           |       |           |            |             | G  |

| н  | VMD44   | VMD46      | VMD47   | VMD48       | VMD58       |             |       |        |      |           |           |       |           |            |             | Н  |

| J  | VMD40   | VMD42      | VMD43   | VMD53       | VDQM5       |             |       |        |      |           |           |       |           |            |             | J  |

| κ  | VMD35   | VMD36      | VMD38   | VMD39       | VMD49       |             |       |        |      |           | OVDD<br>3 | DVDD  | OVDD<br>3 | DVDD       | OVDD3       | κ  |

| L  | SCLK    | VMD32      | VMD34   | VMD41       | VMD45       |             |       |        |      | OVDD<br>3 |           |       |           |            |             | L  |

| М  | VMA8    | VMA9       | VMA10   | DSF         | VMD37       |             |       |        |      | DVDD      |           | VSS   | VSS       | VSS        | VSS         | М  |

| N  | VMA3    | VMA4       | VMA6    | VMA7        | VMA11       | VMD33       |       |        |      | OVDD<br>3 |           | VSS   | VSS       | vss        | VSS         | N  |

| P  | VSRAS#  | VCS0#      | VMA0    | VMA2        | VMA1        | VMA5        |       |        |      | DVDD      |           | VSS   | VSS       | VSS        | VSS         | P  |

| R  | VMD29   | VMD30      | VWE#    | VSCAS#      | NC          | NC          |       |        |      | OVDD<br>3 |           | vss   | VSS       | vss        | VSS         | R  |

| Τ  | VMD28   | VMD27      | VMD26   | VMD25       | VMD31       | VDQM3       |       |        |      | DVDD      |           | VSS   | VSS       | VSS        | VSS         | T  |

| U  | VMD24   | VDQM2      | VDQM0   | VMD23       | VDQM1       | VMD21       |       |        |      | OVDD<br>3 |           | VSS   | VSS       | VSS        | VSS         | U  |

| V  | VMD22   | VMD20      | VMD19   | VMD18       | VMD17       |             |       |        |      | DVDD      |           | VSS   | VSS       | VSS        | VSS         | V  |

| W  | VMD16   | VMD15      | VMD14   | VMD13       | VMD9        |             |       |        |      | OVDD<br>3 |           |       |           |            |             | W  |

| Y  | VMD12   | VMD11      | VMD10   | VMD8        | VMD5        |             |       |        |      | OVDD<br>3 | OVDD<br>3 | DVDD  | OVDD<br>3 | DVDD       | OVDD3       | Υ  |

| AA | VMD7    | VMD6       | VMD4    | VMD1        | PHOLD#      |             |       |        |      |           |           |       |           |            |             | AA |

| AB | VMD3    | VMD2       | VMD0    | INTA#       | PREQ2#      |             |       |        |      |           |           |       |           |            |             | AB |

| AC | PHLDA#  | BMREQ#     | PCIRST# | PREQ3#      | PGNT3#      |             |       |        |      |           |           |       |           |            |             | AC |

| AD | PREQ0#  | PREQ1#     | PGNT0#  | PGNT1#      | AD28        |             |       |        |      |           |           |       | IDA12     | IIOWA      | NC          | AD |

| ΑE | PGNT2#  | AD31       | AD30    | AD29        | 5VDD        | AD20        | AD16  | TRDY#  | PAR  | AD4       | AD0       | IDA10 | IDA14     | IIRQA      | NC          | AE |

| AF | AD27    | AD26       | AD25    | AD24        | AD17        | DEVSEL<br># | AD15  | AD11   | AD9  | AD3       | IDA8      | IDA9  | IDA3      | IDA0       | ICHRDY<br>A | AF |

| AG | AVDD    | PCICLK     | AVSS    | AD21        | C/BE2#      | PLOCK#      | AD14  | AD10   | AD7  | AD2       | IRQ15     | IDA5  | IDA2      | IDA15      | IDACKA<br># | AG |

| АН |         | C/BE3#     | AD23    | AD19        | FRAME#      | STOP#       | AD13  | AD8    | AD6  | AD1       | IDA7      | IDA4  | IDA13     | IDRE<br>QA | IDSAA1      | AH |

| AJ |         |            | AD22    | AD18        | IRDY#       | C/BE1#      | AD12  | C/BE0# | AD5  | IRQ14     | IDA6      | IDA11 | IDA1      | IIORA      | IDSAA0      | AJ |

|    | 1       | 2          | 3       | 4           | 5           | 6           | 7     | 8      | 9    | 10        | 11        | 12    | 13        | 14         | 15          |    |

## 3.2. SiS530 PIN ASSIGNMENT (TOP VIEW-RIGHT SIDE)

|          | 16           | 17    | 18    | 19      | 20      | 21     | 22           | 23   | 24    | 25    | 26      | 27         | 28           | 29         |    |

|----------|--------------|-------|-------|---------|---------|--------|--------------|------|-------|-------|---------|------------|--------------|------------|----|

| Α        | AVDD         | SDCLK | MA14  | MA8     | MA4     | CSA0#  | CSA4#        | DQM0 | MD14  | MD12  | MD9     | MD40       |              |            | Α  |

| В        | CSB0#        | CSB4# | MA12  | MA7     | MA3     | CSA1#  | CSA5#        | DQM4 | MD46  | MD11  | MD41    | MD39       | MD6          |            | В  |

| С        | CSB1#        | CSB5# | MA11  | MA6     | MA2     | CSA3#  | SRAS#        | WE#  | MD13  | MD43  | MD8     | MD38       | MD5          | MD37       | С  |

| D        | CSB2#        | TEST# | MA10  | MA5     | MA0     | DQM5   | DQM1         | MD15 | MD45  | MD10  | MD36    | MD3        | MD35         | MD34       | D  |

| E        | DQM6         | AVSS  | MA9   | MA1     | CSA2#   | SCAS#  | MD47         | MD44 | MD42  | MD7   | MD1     | MD33       | MD32         | TAGW<br>E# | E  |

| F        | CSB3#        | MA13  |       |         |         |        |              |      |       | MD4   | TA7     | TA6        | TA5          | TA3        | F  |

| G        |              |       |       |         |         |        |              |      |       | MD2   | TA2     | TA1        | CCS1#        | GWE#       | G  |

| н        |              |       |       |         |         |        |              |      |       | MD0   | BWE#    | ADSC#      | KOE#         | HA30       | н  |

| J        |              |       |       |         |         |        |              |      |       | TA4   | TA0     | HA4        | HA29         | НАЗ        | J  |

| κ        | DVDD         | OVDD3 | DVDD  | OVDD3   | OVDD3   |        |              |      |       | ADV#  | HA28    | HA22       | HA26         | HA21       | K  |

| L        |              |       |       |         | OVDD3   |        |              |      |       | HA6   | HA24    | HA27       | HA25         | HA7        | L  |

| М        | VSS          | VSS   | VSS   |         | DVDD    |        |              |      |       | HA23  | HA8     | HA5        | HA11         | HA9        | М  |

| N        | VSS          | VSS   | VSS   |         | OVDD2   |        |              |      | HA31  | HA10  | HA12    | HA15       | HA14         | HA16       | N  |

| P        | VSS          | VSS   | VSS   |         | DVDD    |        |              |      | HA13  | HA17  | HA18    | HA19       | HA20         | HBE7#      | P  |

| R        | VSS          | VSS   | VSS   |         | OVDD2   |        |              |      | NC    | NC    | HBE2#   | HBE4#      | HBE5#        | HBE6#      | R  |

| <b>T</b> | VSS          | VSS   | VSS   |         | DVDD    |        |              |      | HBE1# | HBE3# | ADS#    | EADS#      | W/R#         | HBE0#      | T  |

| U        | VSS          | VSS   | VSS   |         | OVDD2   |        |              |      | NA#   | HITM# | AHOLD   | BRDY#      | BOFF#        | HLOC<br>K# | U  |

| v        | VSS          | VSS   | VSS   |         | DVDD    |        |              |      |       | M/IO# | SMIACT# | CACHE<br># | KEN#/IN<br>V | D/C#       | V  |

| W        |              |       |       |         | OVDD2   |        |              |      |       | HD6   | HD1     | HD3        | HD2          | HD0        | W  |

| Y        | DVDD         | OVDD2 | DVDD  | OVDD2   | OVDD2   |        |              |      |       | HD10  | HD8     | HD7        | HD5          | HD4        | Υ  |

| AA       |              |       |       |         |         |        |              |      |       | HD17  | HD13    | HD12       | HD11         | HD9        | AA |

| AB       |              |       |       |         |         |        |              |      |       | HD23  | HD16    | HD18       | HD15         | HD14       | AB |

| AC       |              |       |       |         |         |        |              |      |       | HD29  | HD19    | HD21       | HD20         | HD22       | AC |

| AD       | IDB8         | IDB13 |       |         |         |        |              |      |       | HD35  | HD28    | HD25       | HD26         | HD24       | AD |

| ΑE       | CBLIDA       | IDB10 | IDB15 | CBLIDB  | HD62    | HD51   | HD43         | HD45 | HD42  | AVSS  | HD33    | HD31       | HD30         | HD27       | AE |

| AF       | IDB7         | IDB4  | IDB2  | ICHRDYB | IDACKB# | HD58   | HD63         | HD57 | HD53  | HD48  | HD44    | HD37       | HD34         | HD32       | AF |

| AG       | IDECSA1<br># | IDB5  | IDB12 | IDB0    | IIORB   | IDSAB0 | IDECSB<br>1# | HD59 | HD54  | HD49  | HD41    | HD40       | HD39         | HD36       | AG |

| AH       | IDECSA0<br># | IDB9  | IDB3  | IDB14   | IIOWB   | IDSAB1 | IDECSB<br>0# | HD60 | HD55  | HD50  | HD47    | HD46       | HD38         |            | AH |

| AJ       | IDSAA2       | IDB6  | IDB11 | IDB1    | IDREQB  | IIRQB  | IDSAB2       | HD61 | HD56  | HD52  | HCLK    | AVDD       |              |            | AJ |

|          | 16           | 17    | 18    | 19      | 20      | 21     | 22           | 23   | 24    | 25    | 26      | 27         | 28           | 29         |    |

## 3.3. SiS530 ALPHABETICAL PIN LIST

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| 5VDD           | AE5               |

| AD0            | AE11              |

| AD1            | AH10              |

| AD2            | AG10              |

| AD3            | AF10              |

| AD4            | AE10              |

| AD5            | AJ9               |

| AD6            | AH9               |

| AD7            | AG9               |

| AD8            | AH8               |

| AD9            | AF9               |

| AD10           | AG8               |

| AD11           | AF8               |

| AD12           | AJ7               |

| AD13           | AH7               |

| AD14           | AG7               |

| AD15           | AF7               |

| AD16           | AE7               |

| AD17           | AF5               |

| AD18           | AJ4               |

| AD19           | AH4               |

| AD20           | AE6               |

| AD21           | AG4               |

| AD22           | AJ3               |

| AD23           | АН3               |

| AD24           | AF4               |

| AD25           | AF3               |

| AD26           | AF2               |

| AD27           | AF1               |

| AD28           | AD5               |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| AD29           | AE4               |

| AD30           | AE3               |

| AD31           | AE2               |

| ADS#           | T26               |

| ADSC#          | H27               |

| ADV#           | K25               |

| AHOLD          | U26               |

| AVDD           | AG1               |

| AVDD           | A16               |

| AVDD           | AJ27              |

| AVDD1          | А3                |

| AVDD2/3        | A4                |

| AVDD4          | B5                |

| AVSS           | AG3               |

| AVSS           | E16               |

| AVSS           | E17               |

| AVSS           | AE25              |

| AVSS1          | E6                |

| AVSS2/3        | B4                |

| AVSS4          | A7                |

| BMREQ#         | AC2               |

| BOFF#          | U28               |

| BOUT           | A5                |

| BRDY#          | U27               |

| BWE#           | H26               |

| C/BE0#         | AJ8               |

| C/BE1#         | AJ6               |

| C/BE2#         | AG5               |

| C/BE3#         | AH2               |

| CACHE#         | V27               |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| CBLIDA         | AE16              |

| CBLIDB         | AE19              |

| CCS1#          | G28               |

| CKE0           | C14               |

| CKE1           | B14               |

| CKE2           | A14               |

| CKE3           | F14               |

| CKE4           | A15               |

| CKE5           | E14               |

| COMP           | E7                |

| CSA0#          | A21               |

| CSA1#          | B21               |

| CSA2#          | E20               |

| CSA3#          | C21               |

| CSA4#          | A22               |

| CSA5#          | B22               |

| CSB0#          | B16               |

| CSB1#          | C16               |

| CSB2#          | D16               |

| CSB3#          | F16               |

| CSB4#          | B17               |

| CSB5#          | C17               |

| D/C#           | V29               |

| DDCCLK         | В3                |

| DDCDATA        | C3                |

| DEVSEL#        | AF6               |

| DQM0           | A23               |

| DQM1           | D22               |

| DQM2           | D15               |

| DQM3           | B15               |

| SIGNAL<br>NAME | SiS530<br>BALL NO | SIGNAL<br>NAME | SiS530<br>BALL NO | SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|----------------|-------------------|----------------|-------------------|

| DQM4           | B23               | HA9            | M29               | HCLK           | AJ26              |

| DQM5           | D21               | HA10           | N25               | HD0            | W29               |

| DQM6           | E16               | HA11           | M28               | HD1            | W26               |

| DQM7           | C15               | HA12           | N26               | HD2            | W28               |

| DSF            | M4                | HA13           | P24               | HD3            | W27               |

| DVDD           | M10               | HA14           | N28               | HD4            | Y29               |

| DVDD           | P10               | HA15           | N27               | HD5            | Y28               |

| DVDD           | T10               | HA16           | N29               | HD6            | W25               |

| DVDD           | V10               | HA17           | P25               | HD7            | Y27               |

| DVDD           | K12               | HA18           | P26               | HD8            | Y26               |

| DVDD           | Y12               | HA19           | P27               | HD9            | AA29              |

| DVDD           | Y13               | HA20           | P28               | HD10           | Y25               |

| DVDD           | K14               | HA21           | K29               | HD11           | AA28              |

| DVDD           | Y14               | HA22           | K27               | HD12           | AA27              |

| DVDD           | K18               | HA23           | M25               | HD13           | AA26              |

| DVDD           | Y18               | HA24           | L26               | HD14           | AB29              |

| DVDD           | M20               | HA25           | L28               | HD15           | AB28              |

| DVDD           | P20               | HA26           | K28               | HD16           | AB26              |

| DVDD           | T20               | HA27           | L27               | HD17           | AA25              |

| DVDD           | V20               | HA28           | K26               | HD18           | AB27              |

| EADS#          | T27               | HA29           | J28               | HD19           | AC26              |

| ENVCO          | B2                | HA30           | H29               | HD20           | AC28              |

| FRAME#         | AH5               | HA31           | N24               | HD21           | AC27              |

| GOUT           | B6                | HBE0#          | T29               | HD22           | AC29              |

| GWE#           | G29               | HBE1#          | T24               | HD23           | AB25              |

| HA3            | J29               | HBE2#          | R26               | HD24           | AD29              |

| HA4            | J27               | HBE3#          | T25               | HD25           | AD27              |

| HA5            | M27               | HBE4#          | R27               | HD26           | AD28              |

| HA6            | L25               | HBE5#          | R28               | HD27           | AE29              |

| HA7            | L29               | HBE6#          | R29               | HD28           | AD26              |

| HA8            | M26               | HBE7#          | P29               | HD29           | AC25              |

| SIGNAL | SiS530  | SI  | GNAL  | SiS530  | SIGNAL   | SiS530  |

|--------|---------|-----|-------|---------|----------|---------|

| NAME   | BALL NO |     | AME   | BALL NO | NAME     | BALL NO |

| HD30   | AE28    | Н   | ID61  | AJ23    | IDB5     | AG17    |

| HD31   | AE27    | Н   | D62   | AE20    | IDB6     | AJ17    |

| HD32   | AF29    | Н   | ID63  | AF22    | IDB7     | AF16    |

| HD33   | AE26    | Н   | ITM#  | U25     | IDB8     | AD16    |

| HD34   | AF28    | HL  | OCK#  | U29     | IDB9     | AH17    |

| HD35   | AD25    | HS  | SYNC  | D4      | IDB10    | AE17    |

| HD36   | AG29    | ICH | IRDYA | AF15    | IDB11    | AJ18    |

| HD37   | AF27    | ICH | IRDYB | AF19    | IDB12    | AG18    |

| HD38   | AH28    |     | DA0   | AF14    | IDB13    | AD17    |

| HD39   | AG28    |     | DA1   | AJ13    | IDB14    | AH19    |

| HD40   | AG27    |     | DA2   | AG13    | IDB15    | AE18    |

| HD41   | AG26    |     | DA3   | AF13    | IDECSA0# | AH16    |

| HD42   | AE24    |     | DA4   | AH12    | IDECSA1# | AG16    |

| HD43   | AE22    |     | DA5   | AG12    | IDECSB0# | AH22    |

| HD44   | AF26    |     | DA6   | AJ11    | IDECSB1# | AG22    |

| HD45   | AE23    |     | DA7   | AH11    | IDSAA0   | AJ15    |

| HD46   | AH27    |     | DA8   | AF11    | IDSAA1   | AH15    |

| HD47   | AH26    |     | DA9   | AF12    | IDSAA2   | AJ16    |

| HD48   | AF25    | ID  | DA10  | AE12    | IDSAB0   | AG21    |

| HD49   | AG25    | IE  | DA11  | AJ12    | IDSAB1   | AH21    |

| HD50   | AH25    | ID  | )A12  | AD13    | IDSAB2   | AJ22    |

| HD51   | AE21    | ID  | DA13  | AH13    | IIORA    | AJ14    |

| HD52   | AJ25    | ID  | DA14  | AE13    | IIORB    | AG20    |

| HD53   | AF24    | ID  | DA15  | AG14    | IIOWA    | AD14    |

| HD54   | AG24    | IDA | CKA#  | AG15    | IIOWB    | AH20    |

| HD55   | AH24    | IDA | CKB#  | AF20    | IIRQA    | AE14    |

| HD56   | AJ24    |     | DB0   | AG19    | IIRQB    | AJ21    |

| HD57   | AF23    |     | DB1   | AJ19    | INTA#    | AB4     |

| HD58   | AF21    | II  | DB2   | AF18    | IRDY#    | AJ5     |

| HD59   | AG23    |     | DB3   | AH18    | IREQA    | AH14    |

| HD60   | AH23    | [[  | DB4   | AF17    | IREQB    | AJ20    |

| 010            | 0:0500            | 010111         | 0:050            | 818            | 0:0500            |

|----------------|-------------------|----------------|------------------|----------------|-------------------|

| SIGNAL<br>NAME | SiS530<br>BALL NO | SIGNAL<br>NAME | SiS53<br>BALL NO | SIGNAL<br>NAME | SiS530<br>BALL NO |

| IRQ14          | AJ10              | MD11           | B25              | MD42           | E24               |

| IRQ15          | AG11              | MD12           | A25              | MD43           | C25               |

| KEN#/INV       | V28               | MD13           | C24              | MD44           | E23               |

| KOE#           | H28               | MD14           | A24              | MD45           | D24               |

| M/IO#          | V25               | MD15           | D23              | MD46           | B24               |

| MA0            | D20               | MD16           | D14              | MD47           | E22               |

| MA1            | E19               | MD17           | B13              | MD48           | E13               |

| MA2            | C20               | MD18           | C13              | MD49           | A13               |

| MA3            | B20               | MD19           | A12              | MD50           | F13               |

| MA4            | A20               | MD20           | C12              | MD51           | D13               |

| MA5            | D19               | MD21           | D12              | MD52           | B12               |

| MA6            | C19               | MD22           | A11              | MD53           | E12               |

| MA7            | B19               | MD23           | C11              | MD54           | D11               |

| MA8            | A19               | MD24           | A10              | MD55           | B11               |

| MA9            | E18               | MD25           | C10              | MD56           | E11               |

| MA10           | D18               | MD26           | D10              | MD57           | B10               |

| MA11           | C18               | MD27           | B9               | MD58           | E10               |

| MA12           | B18               | MD28           | C9               | MD59           | A9                |

| MA13           | F17               | MD29           | A8               | MD60           | D9                |

| MA14           | A18               | MD30           | C8               | MD61           | E9                |

| MD0            | H25               | MD31           | D8               | MD62           | B8                |

| MD1            | E26               | MD32           | E28              | MD63           | E8                |

| MD2            | G25               | MD33           | E27              | NA#            | U24               |

| MD3            | D27               | MD34           | D29              | NC             | C5                |

| MD4            | F25               | MD35           | D28              | NC             | D5                |

| MD5            | C28               | MD36           | D26              | NC             | R5                |

| MD6            | B28               | MD37           | C29              | NC             | C6                |

| MD7            | E25               | MD38           | C27              | NC             | D6                |

| MD8            | C26               | MD39           | B27              | NC             | R6                |

| MD9            | A26               | MD40           | A27              | NC             | D7                |

| MD10           | D25               | MD41           | B26              | NC             | E15               |

|                |                   |                | 1                 |                | 1                 |

|----------------|-------------------|----------------|-------------------|----------------|-------------------|

| SIGNAL<br>NAME | SIS530<br>BALL NO | SIGNAL<br>NAME | SIS530<br>BALL NO | SIGNAL<br>NAME | SIS530<br>BALL NO |

| NC             | F15               | PCICLK         | AG2               | TA7            | F26               |

| NC             | AD15              | PCIRST#        | AC3               | TAGWE#         | E29               |

| NC             | AE15              | PGNT0#         | AD3               | TEST#          | D17               |

| NC             | R24               | PGNT1#         | AD4               | TRDY#          | AE8               |

| NC             | R25               | PGNT2#         | AE1               | VCS0#          | P2                |

| OSCI           | E5                | PGNT3#         | AC5               | VCS1#          | E1                |

| OVDD2          | Y16               | PHLDA#         | AC1               | VDQM0          | U3                |

| OVDD2          | Y17               | PHOLD#         | AA5               | VDQM1          | U5                |

| OVDD2          | Y19               | PL-DCLK        | D1                | VDQM2          | U2                |

| OVDD2          | N20               | PLOCK          | AG6               | VDQM3          | T6                |

| OVDD2          | R20               | PLPWDN         | C2                | VDQM4          | F2                |

| OVDD2          | U20               | PLSENSE        | F5                | VDQM5          | J5                |

| OVDD2          | W20               | PREQ0#         | AD1               | VDQM6          | F3                |

| OVDD2          | Y20               | PREQ1#         | AD2               | VDQM7          | F4                |

| OVDD3          | L10               | PREQ2#         | AB5               | VMA0           | P3                |

| OVDD3          | N10               | PREQ3#         | AC4               | VMA1           | P5                |

| OVDD3          | R10               | ROUT           | A6                | VMA2           | P4                |

| OVDD3          | U10               | RSET           | В7                | VMA3           | N1                |

| OVDD3          | W10               | SCAS#          | E21               | VMA4           | N2                |

| OVDD3          | Y10               | SCLK           | L1                | VMA5           | P6                |

| OVDD3          | K11               | SDCLK          | A17               | VMA6           | N3                |

| OVDD3          | Y11               | SMIACT#        | V26               | VMA7           | N4                |

| OVDD3          | K13               | SRAS#          | C22               | VMA8           | M1                |

| OVDD3          | K15               | STOP#          | AH6               | VMA9           | M2                |

| OVDD3          | Y15               | TA0            | J26               | VMA10          | М3                |

| OVDD3          | K16               | TA1            | G27               | VMA11          | N5                |

| OVDD3          | K17               | TA2            | G26               | VMD0           | AB3               |

| OVDD3          | K19               | TA3            | F29               | VMD1           | AA4               |

| OVDD3          | K20               | TA4            | J25               | VMD2           | AB2               |

| OVDD3          | L20               | TA5            | F28               | VMD3           | AB1               |

| PAR            | AE9               | TA6            | F27               | VMD4           | AA3               |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| VMD5           | Y5                |

| VMD6           | AA2               |

| VMD7           | AA1               |

| VMD8           | Y4                |

| VMD9           | W5                |

| VMD10          | Y3                |

| VMD11          | Y2                |

| VMD12          | Y1                |

| VMD13          | W4                |

| VMD14          | W3                |

| VMD15          | W2                |

| VMD16          | W1                |

| VMD17          | V5                |

| VMD18          | V4                |

| VMD19          | V3                |

| VMD20          | V2                |

| VMD21          | U6                |

| VMD22          | V1                |

| VMD23          | U4                |

| VMD24          | U1                |

| VMD25          | T4                |

| VMD26          | T3                |

| VMD27          | T2                |

| VMD28          | T1                |

| VMD29          | R1                |

| VMD30          | R2                |

| VMD31          | T5                |

| VMD32          | L2                |

| VMD33          | N6                |

| VMD34          | L3                |

| VMD35          | K1                |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| VMD36          | K2                |

| VMD37          | M5                |

| VMD38          | K3                |

| VMD39          | K4                |

| VMD40          | J1                |

| VMD41          | L4                |

| VMD42          | J2                |

| VMD43          | J3                |

| VMD44          | H1                |

| VMD45          | L5                |

| VMD46          | H2                |

| VMD47          | НЗ                |

| VMD48          | H4                |

| VMD49          | K5                |

| VMD50          | G1                |

| VMD51          | G2                |

| VMD52          | G3                |

| VMD53          | J4                |

| VMD54          | G4                |

| VMD55          | F1                |

| VMD56          | E2                |

| VMD57          | E3                |

| VMD58          | H5                |

| VMD59          | E4                |

| VMD60          | D2                |

| VMD61          | G5                |

| VMD62          | D3                |

| VMD63          | C1                |

| VREF           | C7                |

| VSCAS#         | R4                |

| VSRAS#         | P1                |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| VSS            | M12               |

| VSS            | N12               |

| VSS            | P12               |

| VSS            | R12               |

| VSS            | T12               |

| VSS            | U12               |

| VSS            | V12               |

| VSS            | M13               |

| VSS            | N13               |

| VSS            | P13               |

| VSS            | R13               |

| VSS            | T13               |

| VSS            | U13               |

| VSS            | V13               |

| VSS            | M14               |

| VSS            | N14               |

| VSS            | P14               |

| VSS            | R14               |

| VSS            | T14               |

| VSS            | U14               |

| VSS            | V14               |

| VSS            | M15               |

| VSS            | N15               |

| VSS            | P15               |

| VSS            | R15               |

| VSS            | T15               |

| VSS            | U15               |

| VSS            | V15               |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| VSS            | M16               |

| VSS            | N16               |

| VSS            | P16               |

| VSS            | R16               |

| VSS            | T16               |

| VSS            | U16               |

| VSS            | V16               |

| VSS            | M17               |

| VSS            | N17               |

| VSS            | P17               |

| VSS            | R17               |

| VSS            | T17               |

| VSS            | U17               |

| SIGNAL<br>NAME | SiS530<br>BALL NO |

|----------------|-------------------|

| VSS            | V17               |

| VSS            | M18               |

| VSS            | N18               |

| VSS            | P18               |

| VSS            | R18               |

| VSS            | T18               |

| VSS            | U18               |

| VSS            | V18               |

| VSYNC          | C4                |

| VWE#           | R3                |

| W/R#           | T28               |

| WE#            | C23               |

#### SiS530 MULTIPLEX PIN LIST 3.4.

| J.4. J            | 13330 MOLTI    | FLEX FIN LIS   |

|-------------------|----------------|----------------|

| SiS530<br>BALL NO | SIGNAL<br>NAME | SIGNAL<br>NAME |

| L2                | VMD32          | R0             |

| N6                | VMD33          | R1             |

| L3                | VMD34          | R2             |

| K1                | VMD35          | R3             |

| K2                | VMD36          | R4             |

| M5                | VMD37          | R5             |

| K3                | VMD38          | R6             |

| K4                | VMD39          | R7             |

| J1                | VMD40          | G0             |

| L4                | VMD41          | G1             |

| J2                | VMD42          | G2             |

| J3                | VMD43          | G3             |

| H1                | VMD44          | G4             |

| L5                | VMD45          | G5             |

| H2                | VMD46          | G6             |

| SiS530<br>BALL NO | SIGNAL<br>NAME | SIGNAL<br>NAME |

|-------------------|----------------|----------------|

| НЗ                | VMD47          | G7             |

| H4                | VMD48          | В0             |

| K5                | VMD49          | B1             |

| G1                | VMD50          | B2             |

| G2                | VMD51          | В3             |

| G3                | VMD52          | B4             |

| J4                | VMD53          | B5             |

| G4                | VMD54          | В6             |

| F1                | VMD55          | В7             |

| E2                | VMD56          | PLXLCLK        |

| E3                | VMD57          | FPLDEDA        |

| H5                | VMD58          | FDDCDAT        |

| E4                | VMD59          | FDDCCLK        |

| D2                | VMD60          | PLVSYNC        |

| G5                | VMD61          | PLHSYNC        |

## 4 SIGNAL DESCRIPTION

## 4.1. HOST INTERFACE SIGNALS

| NAME   | TYPE<br>ATTR | DESCRIPTION                                                                                                                                                                                                                                                                                                                 |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK   | I            | Host Clock:                                                                                                                                                                                                                                                                                                                 |

|        |              | Primary clock input to drive the part.                                                                                                                                                                                                                                                                                      |

| ADS#   | I            | Address Status :                                                                                                                                                                                                                                                                                                            |

|        |              | Address Status is driven by the CPU to indicate the start of a CPU bus                                                                                                                                                                                                                                                      |

|        |              | cycle.                                                                                                                                                                                                                                                                                                                      |

| M/IO#  | I            | Memory I/O Command Indicator :                                                                                                                                                                                                                                                                                              |

|        |              | Memory I/O definition is an input to indicate an I/O cycle when low, or a memory cycle when high.                                                                                                                                                                                                                           |

| D/C#   | I            | Data/Code Command Indicator :                                                                                                                                                                                                                                                                                               |

|        |              | Data/Code is used to indicate whether the current cycle is a data or code access.                                                                                                                                                                                                                                           |

| W/R#   | I            | Write/Read Command Indicator :                                                                                                                                                                                                                                                                                              |

|        |              | Write/Read from the CPU indicates whether the current cycle is a write or read access.                                                                                                                                                                                                                                      |

| BRDY#  | 0            | Burst Ready :                                                                                                                                                                                                                                                                                                               |

|        |              | Burst Ready indicates that data presented is valid during a burst cycle.                                                                                                                                                                                                                                                    |

| CACHE# | I            | Cacheable Indicator :                                                                                                                                                                                                                                                                                                       |

|        |              | The Cache pin indicates an L1 internally cacheable read cycle or a burst write-back cycle. If this pin is driven inactive during a read cycle, the CPU will not cache the returned data, regardless of the state of the KEN# pin.                                                                                           |

| KEN#/  | 0            | Cache Enable/Invalidate :                                                                                                                                                                                                                                                                                                   |

| INV    |              | This function as both the KEN# signal during CPU read cycles, and the INV signal during L1 snoop cycles. During CPU cycles, KEN#/INV is normally low. KEN#/INV will be driven high during the 1st BRDY# or NA# assertion of a non-L1-cacheable CPU read.  KEN#/INV is driven high (low) during the EADS# assertion of a PCI |

|        |              | master DRAM write (read) snoop cycle.                                                                                                                                                                                                                                                                                       |

| NA#    | 0            | Next Address: The SiS Chip always asserts NA# no matter the burst, or pipelined burst SRAMs are used. This signal is connected to CPU and indicates to CPU                                                                                                                                                                  |

|        |              | that it is ready to process a second cycle.                                                                                                                                                                                                                                                                                 |

| BOFF#  | 0            | Back Off:                                                                                                                                                                                                                                                                                                                   |

|        | -            | The SiS Chip asserts BOFF# to stop the current CPU cycle.                                                                                                                                                                                                                                                                   |

| AHOLD  | 0            | Address Hold :                                                                                                                                                                                                                                                                                                              |

|        |              | The SiS Chip asserts AHOLD when a PCI master is performing a cycle to DRAM. AHOLD is held for the duration of PCI burst transfer. The SiS Chip negates AHOLD when the completion of PCI to DRAM read or write cycles complete and during PCI peer transfers.                                                                |

| _         |     |                                                                                                                                                                                                                                                                                                           |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HLOCK#    | I   | Host Lock :                                                                                                                                                                                                                                                                                               |

|           |     | When CPU asserts HLOCK# to indicate the current bus cycle is locked.                                                                                                                                                                                                                                      |

| EADS#     | 0   | External Address Strobe :                                                                                                                                                                                                                                                                                 |

|           |     | The EADS# is driven to indicate that a valid external address has been driven to the CPU address pins to be used for an inquire cycle.                                                                                                                                                                    |

| HITM#     | I   | Hit Modified :                                                                                                                                                                                                                                                                                            |

|           |     | Hit Modified indicates the snoop cycle hits a modified line in the L1 cache of the CPU.                                                                                                                                                                                                                   |

| SMIACT#   | I   | System Management Interrupt Active :                                                                                                                                                                                                                                                                      |

|           |     | The SMIACT# pin is used as the SMI acknowledgement input from the CPU to indicate that the SMI# is being acknowledged and the processor is operating in System Management Mode (SMM).                                                                                                                     |

| HBE[7:0]# | I   | Host Byte Enables :                                                                                                                                                                                                                                                                                       |

|           |     | CPU Byte Enables indicate which byte lanes on the CPU data bus carry valid data during the current bus cycle. HBE7# indicates that the most significant byte of the data bus is valid while HBE0# indicates that the least significant byte of the data bus is valid.                                     |

| HA[31:3]  | I/O | Host Address Bus :                                                                                                                                                                                                                                                                                        |