# 1. Introduction

The SiS5120 is a highly integrated single chip solution for Pentium PCI/ISA system. It consists of Host-to-PCI bridge function, PCI to ISA bridge function, PCI IDE function, Universal Serial Bus host/hub function.

SiS 5120 supports Enhanced Power Management, including legacy Power Management Unit and Advanced Configuration and Power Interface (ACPI). It also supports ATA Synchronous DMA transfer protocol to improve the IDE performance and Common Architecture for moving ISA function to PCI to improve system performance.

# 2. Features

- Support Intel Pentium CPU and other compatible CPU host bus at 50/55/60/66/75 MHz

- Support the Pipelined Address Mode of Pentium CPU

- Support the Full 64-bit Pentium Processor data Bus

- Meet PC97 Requirements

- Integrated Second Level (L2) Cache Controller

- Write Back/Write Through Cache Modes

- 8 bits or 7 bits Tag with Direct Mapped Cache Organization

- Integrated 16K bits Dirty RAM

- Support Pipelined Burst SRAM

- Support 256 KBytes and 512 KBytes Cache Sizes

- Cache Hit Read/Write Cycle of 3-1-1-1

- Cache Back-to-Back Read/Write Cycle of 3-1-1-1-1-1-1

# • Integrated DRAM Controller

- Support 6/3 Banks (Single/Double sided) of FPM/EDO/SDRAM DIMMs/SIMMs

- Support 2Mbytes to 384Mbytes of main memory

- Support Cacheable DRAM Sizes up to 128 MBytes.

- Support 256K/512K/1M/2M/4M/8M/16M/32M x N FPM/EDO/SDRAM DRAM

- Support 64 Mb DRAM Technology

- Support 3.3V or 5V DRAM.

- Supports Symmetrical and Asymmetrical DRAM.

- Support 32 bits/64 bits mixed mode configuration

- Support Concurrent Write Back

- Support CAS before RAS Refresh

- Support Relocation of System Management Memory

- Programmable CAS#, RAS# and MA Driving Current, No Glue TTL need in 2 banks (up to 64MB) configuration.

- Fully Configurable for the Characteristic of Shadow RAM ( 640 KBytes to 1 MBytes)

- Support FPM DRAM 5-3-3-3(-3-3-3) Burst Read Cycles

- Support EDO DRAM 5-2-2-2(-2-2-2) Burst Read Cycles

- Support SDRAM 6-1-1-1(-2-1-1-1) Burst Read Cycles

- Support X-1-1-1/X-2-2-2/X-3-3-3 Burst Write Cycles

- Support 8 Qword Deep Buffer for Read/Write Reordering, Dword Merging and 3/2-1-1-1 Post write Cycles

- Two Programmable Non-Cacheable Regions

- Option to Disable Local Memory in Non-Cacheable Regions

- Shadow RAM in Increments of 16 KBytes

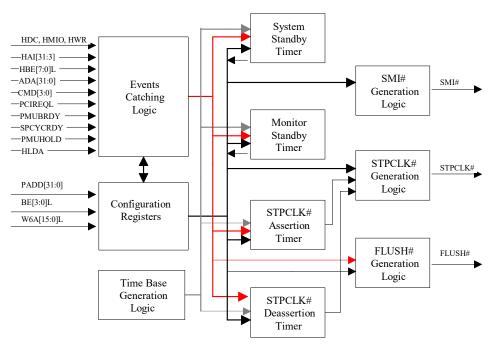

## • Integrated PMU Controller

- Meet ACPI Requirements

- Support Both ACPI and Legacy PMU

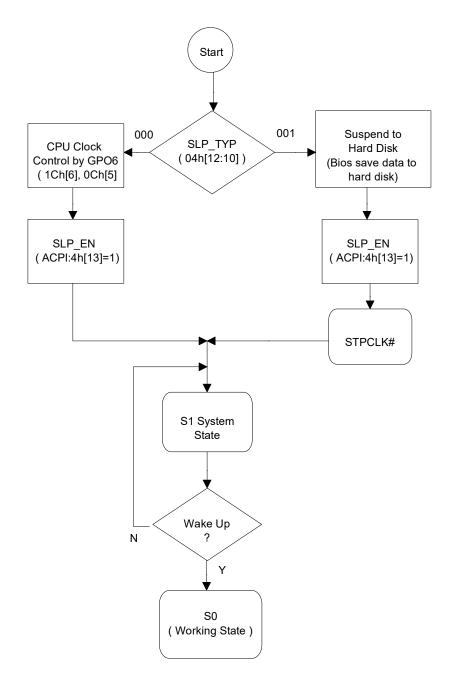

- Support Suspend to Disk

- Support SMM Mode of CPU

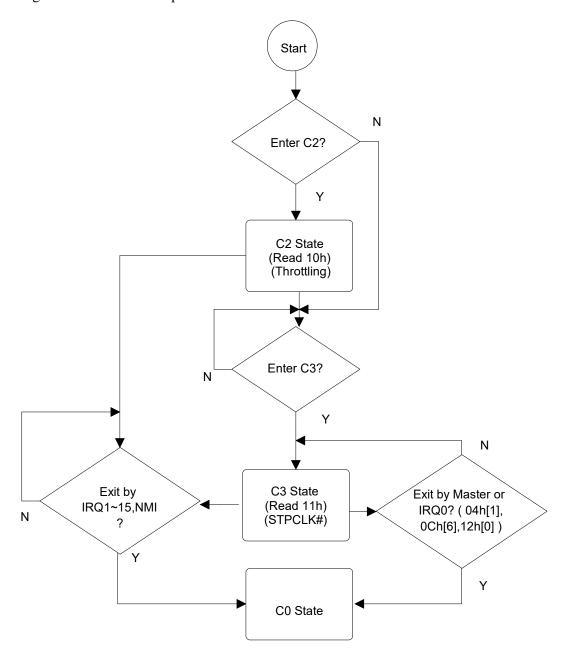

- Support CPU Stop Clock

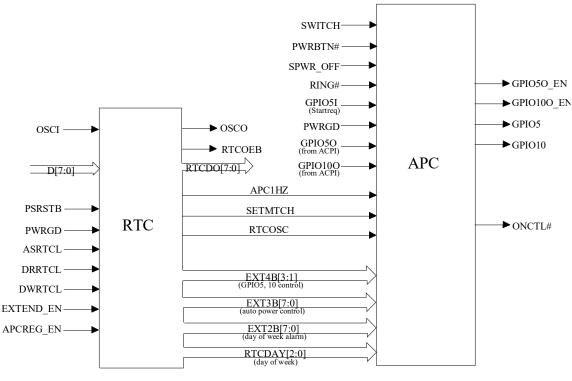

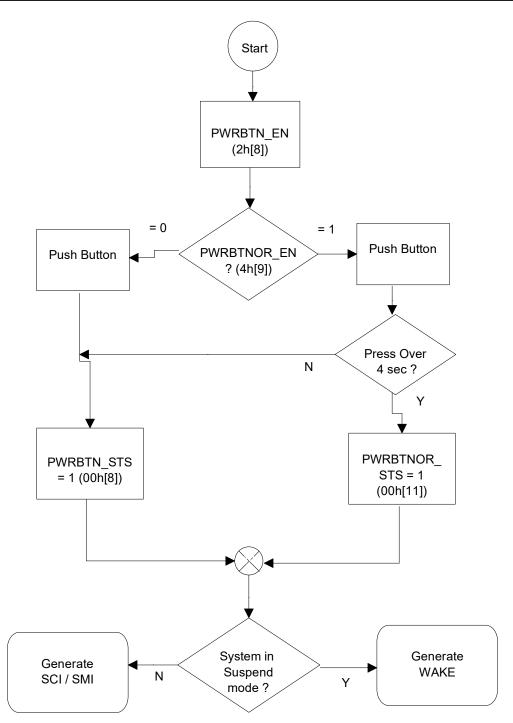

- Support Power Button

- Support Automatic Power Control

- Support Battery Management AC Indicator and LB,LLB

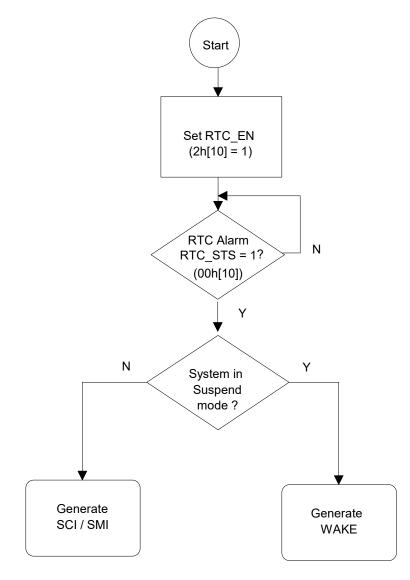

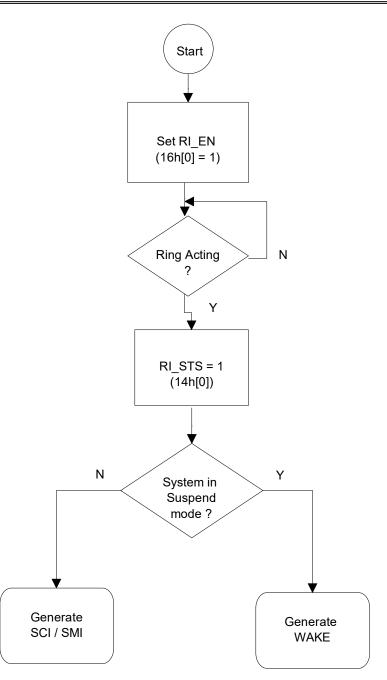

- Support Modem Ring-in, RTC Alarm Wake up

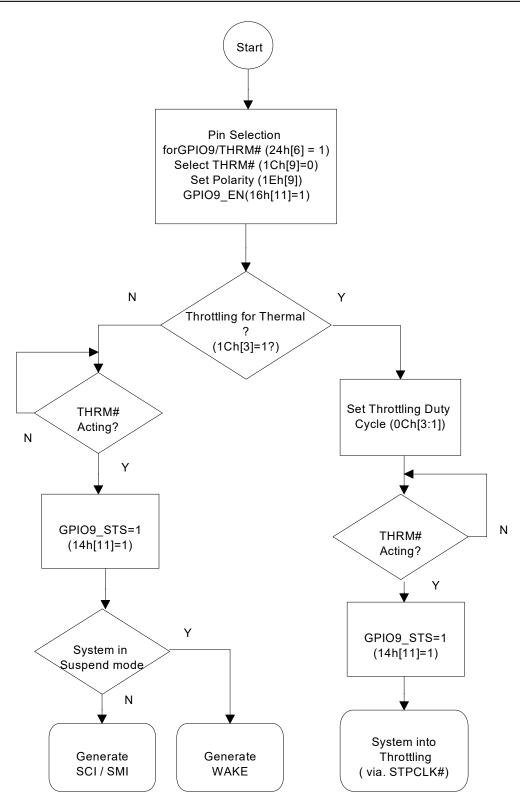

- Support Thermal Detection

- Support GPIOs, and GPOs for External Devices Control

- Support Two Programmable Chip Select

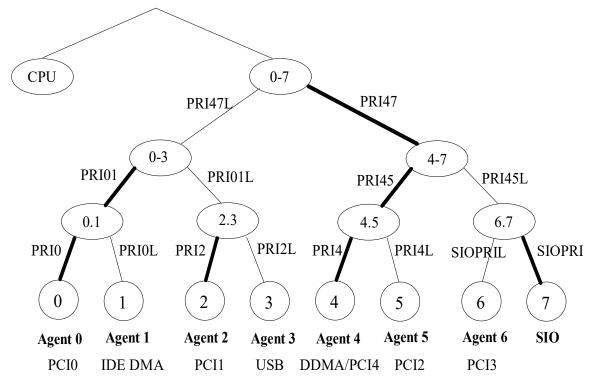

## • Provides High Performance PCI Arbiter.

- Support up to 5 PCI Masters

- Support Rotating Priority Mechanism

- Hidden Arbitration Scheme Minimizes Arbitration Overhead.

- Support Concurrency between CPU to Memory and PCI to PCI.

- Support Concurrency between CPU to L2 Cache and PCI/ISA to DRAM.

## • Integrated Host-to-PCI Bridge

- Support Asynchronous and Synchronous PCI Clock

- Translates the CPU Cycles into the PCI Bus Cycles

- Provides CPU-to-PCI Read Assembly and Write Disassembly Mechanism

- Translates Sequential CPU-to-PCI Memory Write Cycles into PCI Burst Cycles

- Zero Wait State Burst Cycles

- Support IDE Posted Write

- Support Pipelined Process in CPU-to-PCI Access

- Support Advance Snooping for PCI Master Bursting

- Maximum PCI Burst Transfer from 256 Bytes to 4 KBytes

- Integrated Posted Write Buffers and Read Prefetch Buffers to Increase System Performance

- CPU-to-Memory Posted Write Buffer (CTMFF) with 8 QW Deep, Always Sustains 0 Wait Performance on CPU-to-Memory.

- CPU-to-Memory Read Buffer with 4 QW Deep

- CPU-to-PCI Posted Write Buffer(CTPFF) with 8 DW Deep

- PCI-to-Memory Posted Write Buffer(PTHFF) with 8 QW Deep, Always Streams 0 Wait Performance on PCI-to/from-Memory Access

- PCI-to-Memory Read Prefetch Buffer(CTPFF) with 8 QW Deep

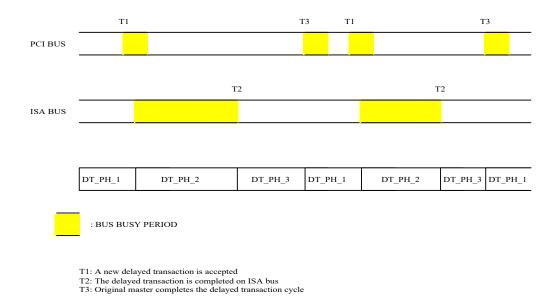

## • Integrated PCI-to-ISA Bridge

- Translates PCI Bus Cycles into ISA Bus Cycles

- Translates ISA Master or DMA Cycles into PCI Bus Cycles

- Provides a Dword Post Buffer for PCI to ISA Memory cycles

- Two 32 bit Prefetch/Post Buffers Enhance the DMA and ISA Master Performance

- Fully Compliant to PCI 2.1

## • Enhanced DMA Functions

- 8-, 16- bit DMA Data Transfer

- ISA compatible, and Fast Type F DMA Cycles

- Two 8237A Compatible DMA Controllers with Seven Independent Programmable Channels

- Provides the Readability of the two 8237 Associated Registers

- Support Distributed DMA

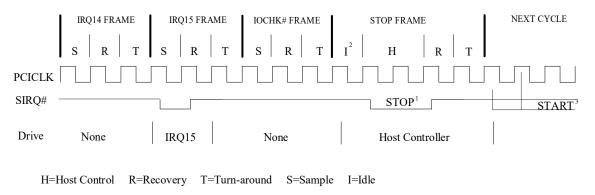

## • Built-in Two 8259A Interrupt Controllers

- 14 Independently Programmable Channels for Level- or Edge-triggered Interrupts

- Provides the Readability of the two 8259A Associated Registers

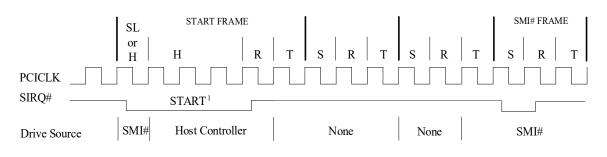

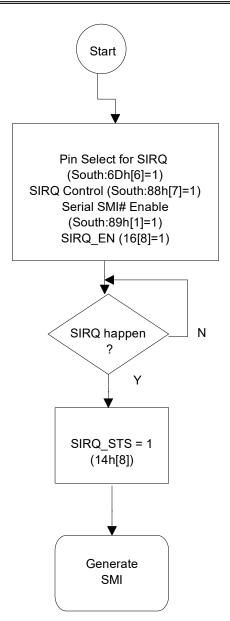

- Support Serial IRQ

## • Three Programmable 16-bit Counters compatible with 8254

- System Timer Interrupt

- Generates Refresh Request

- Speaker Tone Output

- Provides the Readability of the 8254 Associated Registers

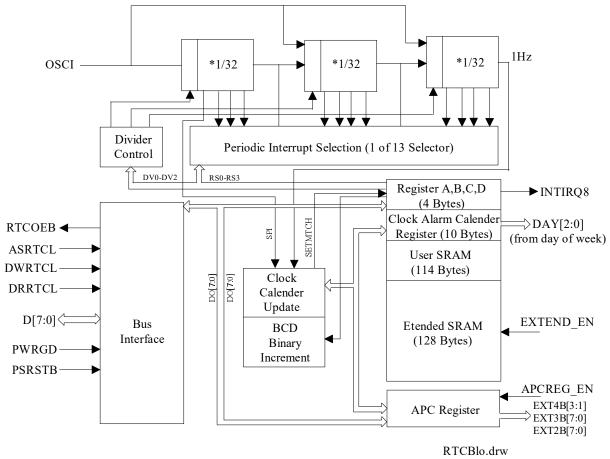

- Built-in Real Time Clock(RTC) with 256B CMOS SRAM

- Built-in up to one Month Alarm for ACPI

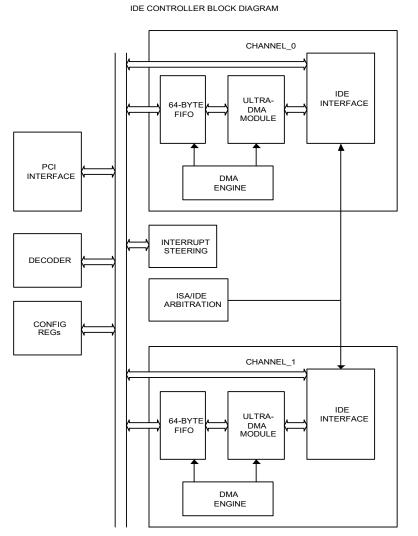

- Fast PCI IDE Master/Slave Controller

- Bus Master Programming Interface for ATA Windows 95 Compliant Controller

- Support PCI Bus Mastering

- Plug and Play Compatible

- Support Scatter and Gather

- Support Dual Mode Operation Native Mode and Compatibility Mode

- Support IDE PIO Timing Mode 0, 1, 2, 3 and 4

- Support Multiword DMA Mode 0, 1, 2

- Support Ultra DMA/33

- Two Separate IDE Bus

- Two 16 Dword FIFO for PCI Burst Transfers.

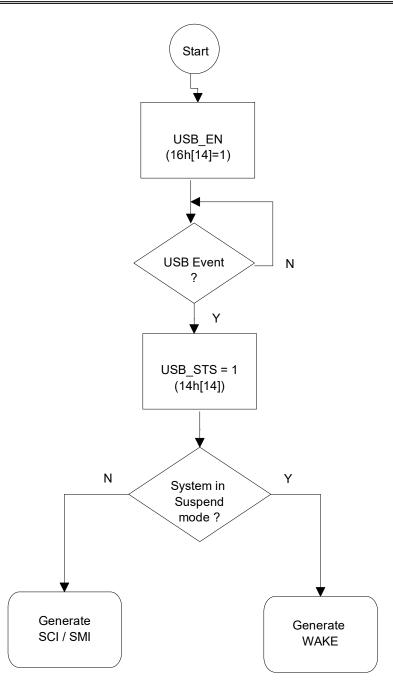

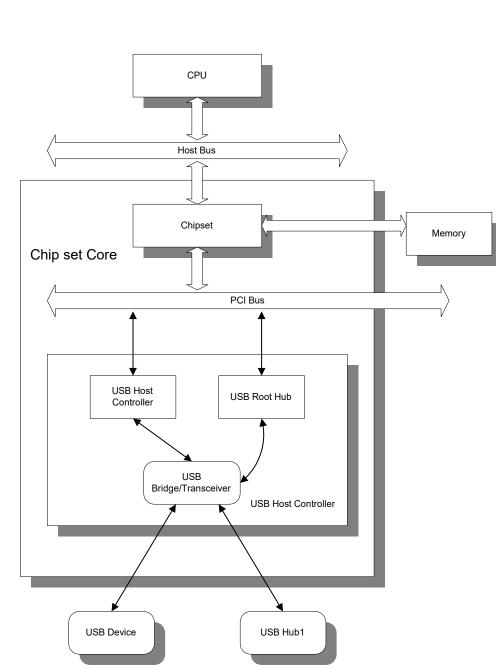

## Universal Serial Bus Host Controller

- OpenHCI Host Controller with Root Hub

- Two USB ports

- Support Legacy Devices

- Support Over Current Detection

- Support I<sup>2</sup>C Serial Bus

- Support the Reroutibility of the four PCI Interrupts

- Support 2MB Flash ROM Interface

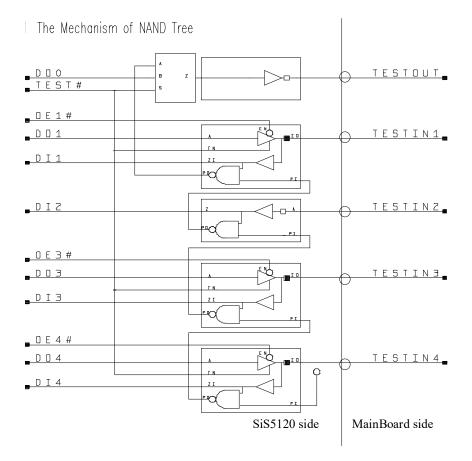

- Support NAND Tree for ball connectivity testing

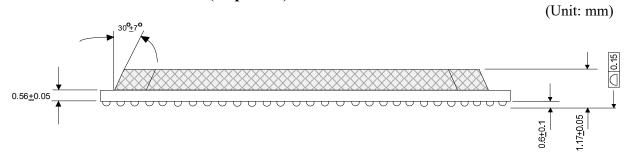

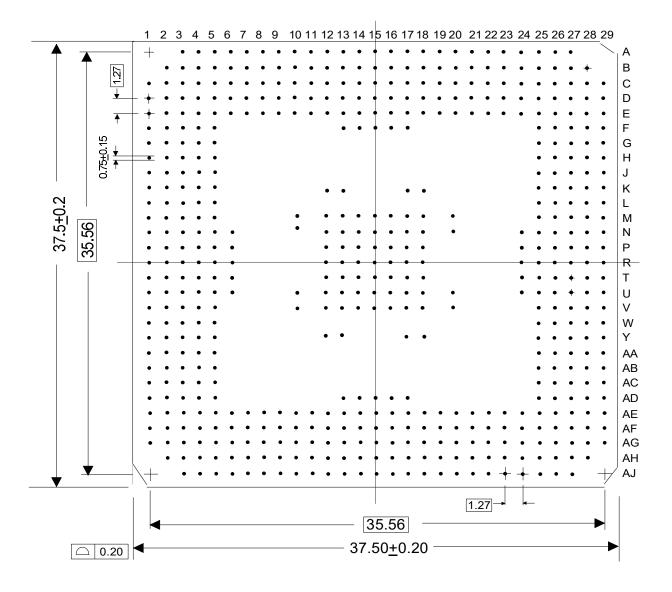

- 480-Balls BGA Package

- 0.35µm 3.3V Technology

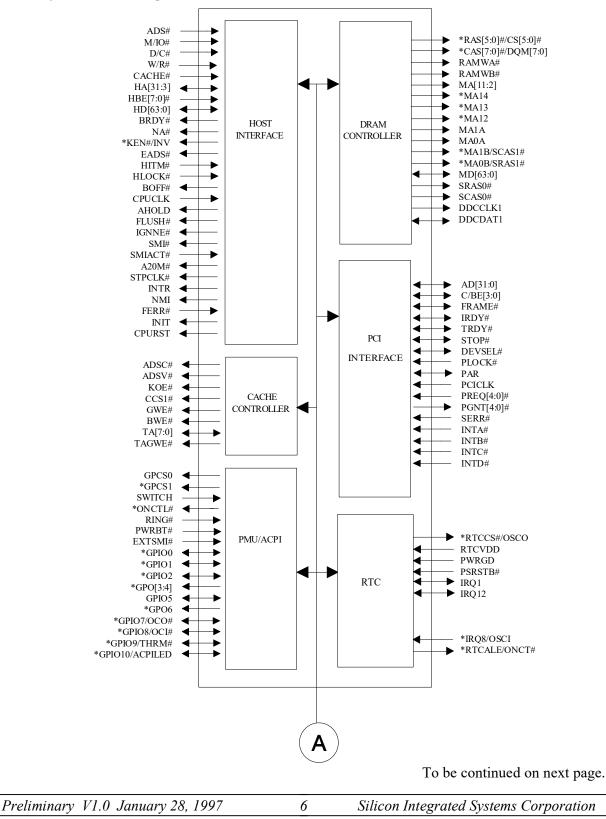

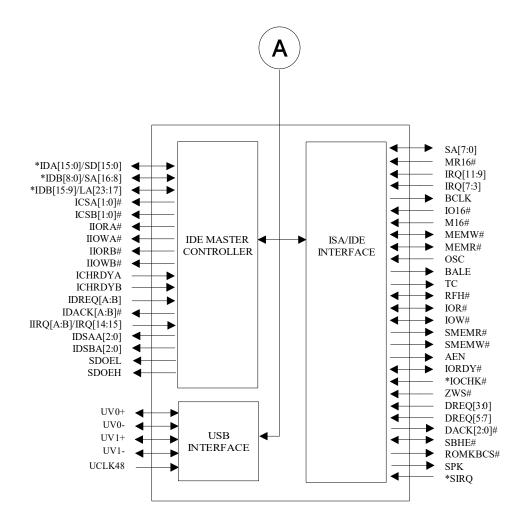

# 2.1 Functional Block Diagram

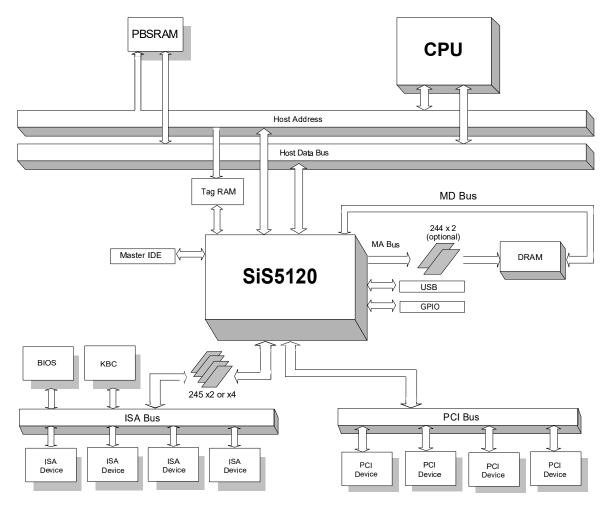

#### 2.1.1 System Block Diagram

Figure 2-1

## \*Multi-function pins

KEN#/INV OSCI/IRQ8 GPIO7/OCO# RAS[5:0]#/CS[5:0]# OSCO/RTCCS# GPIO8/OCI# CAS[7:0]#/DQM[7:0] ONCTL#/RTCALE GPIO9/THRM#/IOCHK# MA12/GPO3 LLB/GPIO1 **GPIO10/ACPILED** MA13/GPO4 GPCS1/SIRQ LB/GPIO2 IDA[15:0]/SD[15:0] MA14/GPO6 AC/GPIO0 MA1B/SCAS1# IIRQ[A:B]/IRQ[14:15] IDB[8:0]/SA[16:8] MA0B/SRAS1# IDB[15:9]/LA[23:17]

# 3. Functional Description

## 3.1 Host Interface

The SiS Chip is designed to support Pentium CPU host interface at 75/66.667/60/55/50MHz. The host data bus and the DRAM bus are 64-bit wide.

The SiS Chip supports the pipelined addressing mode of the Pentium CPU by issuing the next address signal, NA#. NA# signal is asserted except single read DRAM cycle.

The SiS Chip supports the CPU L1 write back (WB) or write through (WT) cache policies and the SiS Chip L2 WB or WT cache policies. The L1 cache is snooped by the assertion of EADS# when the CPU is put in the HOLD state.

The SiS Chip issues AHOLD to the Pentium CPU in response to the assertion of PCI master requests. Once the AHOLD is asserted, SiS Chip does not immediately assert PGNT[4:0]# until both the CPU to PCI posted write buffer and the memory write buffer are empty. During inquire cycles, the AHOLD may be negated temporarily to allow the CPU to write back the inquired hit modified line to L2 or DRAM.

# **3.2 Cache Controller**

The built-in L2 Cache Controller uses a direct-mapped scheme, which can be configured as either in the write through or write back mode. Pipelined burst SRAMs are supported.

SiS Chip supports SRAM types auto-detection and auto-sizing. Table 3-1 shows the cache sizes that are supported by the SiS Chip when using synchronous SRAM, with the corresponding TAG RAM sizes, data RAM sizes, and cacheable memory sizes.

| Cache Size | Data RAM | Tag RAM | Cacheable Size |

|------------|----------|---------|----------------|

| 256K       | 32Kx32x2 | 8Kx8    | 64M            |

| 512K       | 32Kx32x4 | 16Kx8   | 128M           |

Table 3-1 Cache Size with 8-bit tag

The SiS Chip also provides an alternative to save the dirty SRAM chip. This is accomplished by integrated 16Kb Dirty RAM.

# 3.3 DRAM Controller

## 3.3.1 DRAM Type

The SiS Chip can support up to 384MBytes of DRAMs size and each bank could be single or double sided 64 bits FPM (Fast Page mode) DRAM, EDO (Extended Data Output) DRAM, and SDRAM (Synchronous DRAM) DRAM. Half populated bank(32-bit) is also supported. The installed EDO/FPM DRAM type can be 256K, 512k, 1M, 2M, 4M, 8M or 16M bit deep by n bit wide DRAMs, and both symmetrical and asymmetrical type DRAM are supported. It also supports SDRAM 1M, 2M, 4M, 8M, 16M or 32M bit deep by n bit wide DRAMs, and both single and double sided. It is also permissible to mix the DRAMs (FPM/EDO/SDRAM) bank by bank and the corresponding DRAM timing will be switched automatically according to register settings.

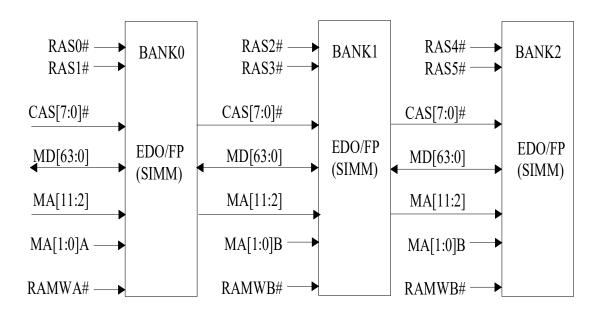

## 3.3.2 DRAM Configuration

SiS Chip supports six rows of DRAMs each 64 bits wide. The six rows of DRAMs may be implemented in six banks of single-sided SIMMs for FPM/EDO DRAM, three banks of double-sided SIMMs, three banks of SDRAM or any other combinations as required. Access to the rows are not interleaved and need not to be populated starting from row 0 or in consecutive sequence.

The SiS Chip can support EDO, FPM and SDRAM. SDRAM, EDO and FPM DRAM's can be mixed for each bank, it must contain only one type of DRAM in each bank. The basic configurations are shown as the following sections:

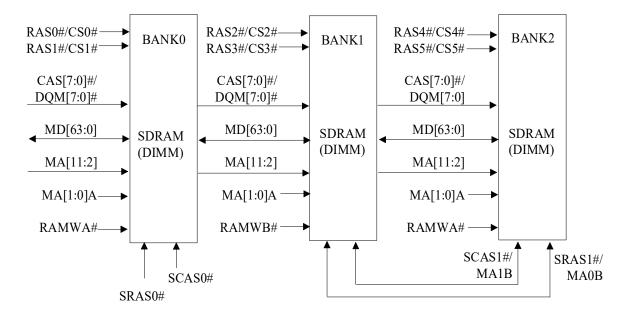

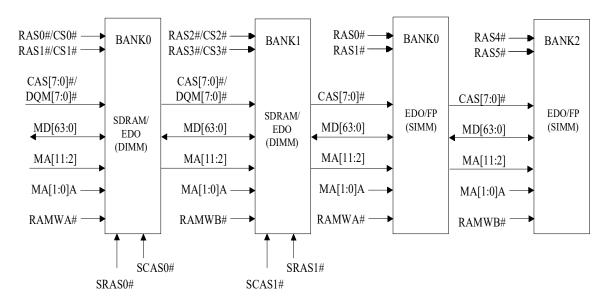

## EDO/FPM DRAM Configuration (4 SIMM/6 SIMM):

#### SDRAM Configuration (2 DIMM/3 DIMM):

DRAM Type Mixed Configuration: EDO/FPM + SDRAM (4 SIMM + 2 DIMM)

Note: 1. SiS Chip only support six rows (3 banks) DRAMs.

- 2. It is recommended that board designer must follow DC characteristics of each type DRAM (SDRAM, EDO, FPM) to design the portion of DRAM in DRAM mode mixed configuration.

- 3. Please refer to "Multiplexed pins" section to define the pin for each function.

#### **3.3.3 DRAM Scramble Table**

Preliminary V1.0 January 28, 1997 10 Silicon Integrated Systems Corporation

The DRAM scramble table contains information for memory address mapping. These tables provide the translation between CPU host address and memory Row and Column address. There are several memory address mapping: 64-bit mapping and 32-bit mapping for FPM/EDO DRAM, 2Banks and 4Banks mapping for SDRAM that SiS Chip supports:

## 64-bit mapping table for FPM/EDO DRAM

#### a. Symmetric:

| Туре    | 256K | (9x9)  | 1M (10x10) |        | 4M (1 | 1x11)  | 16M ( | 12x12) |

|---------|------|--------|------------|--------|-------|--------|-------|--------|

| Address | Row  | Column | Row        | Column | Row   | Column | Row   | Column |

| MA0     | 15   | 3      | 15         | 3      | 15    | 3      | 15    | 3      |

| MA1     | 16   | 4      | 16         | 4      | 16    | 4      | 16    | 4      |

| MA2     | 17   | 5      | 17         | 5      | 17    | 5      | 17    | 5      |

| MA3     | 18   | 6      | 18         | 6      | 18    | 6      | 18    | 6      |

| MA4     | 19   | 7      | 19         | 7      | 19    | 7      | 19    | 7      |

| MA5     | 20   | 8      | 20         | 8      | 20    | 8      | 20    | 8      |

| MA6     | 12   | 9      | 21         | 9      | 21    | 9      | 21    | 9      |

| MA7     | 13   | 10     | 22         | 10     | 22    | 10     | 22    | 10     |

| MA8     | 14   | 11     | 14         | 11     | 23    | 11     | 23    | 11     |

| MA9     | NA   | NA     | 13         | 12     | 24    | 12     | 24    | 12     |

| MA10    | NA   | NA     | NA         | NA     | 14    | 13     | 25    | 13     |

| MA11    | NA   | NA     | NA         | NA     | NA    | NA     | 26    | 14     |

11

#### **b.** Asymmetric:

| Туре    | 512K | (10x9) | 1M ( | 11x9)  | 2M (1 | 1x10)  |

|---------|------|--------|------|--------|-------|--------|

| Address | Row  | Column | Row  | Column | Row   | Column |

| MA0     | 15   | 3      | 15   | 3      | 15    | 3      |

| MA1     | 16   | 4      | 16   | 4      | 16    | 4      |

| MA2     | 17   | 5      | 17   | 5      | 17    | 5      |

| MA3     | 18   | 6      | 18   | 6      | 18    | 6      |

| MA4     | 19   | 7      | 19   | 7      | 19    | 7      |

| MA5     | 20   | 8      | 20   | 8      | 20    | 8      |

| MA6     | 21   | 9      | 21   | 9      | 21    | 9      |

| MA7     | 13   | 10     | 22   | 10     | 22    | 10     |

| MA8     | 14   | 11     | 14   | 11     | 23    | 11     |

| MA9     | 12   | NA     | 12   | NA     | 13    | 12     |

| MA10    | NA   | NA     | 13   | NA     | 14    | NA     |

| MA11    | NA   | NA     | NA   | NA     | NA    | NA     |

| Туре    | 1M ( | 12x8)  | 2M ( | 12x9)  | 4M (1 | 2x10)  | 8M (1 | 2x11)  |

|---------|------|--------|------|--------|-------|--------|-------|--------|

| Address | Row  | Column | Row  | Column | Row   | Column | Row   | Column |

| MA0     | 15   | 3      | 15   | 3      | 15    | 3      | 15    | 3      |

| MA1     | 16   | 4      | 16   | 4      | 16    | 4      | 16    | 4      |

| MA2     | 17   | 5      | 17   | 5      | 17    | 5      | 17    | 5      |

| MA3     | 18   | 6      | 18   | 6      | 18    | 6      | 18    | 6      |

| MA4     | 19   | 7      | 19   | 7      | 19    | 7      | 19    | 7      |

| MA5     | 20   | 8      | 20   | 8      | 20    | 8      | 20    | 8      |

| MA6     | 21   | 9      | 21   | 9      | 21    | 9      | 21    | 9      |

| MA7     | 22   | 10     | 22   | 10     | 22    | 10     | 22    | 10     |

| MA8     | 11   | NA     | 23   | 11     | 23    | 11     | 23    | 11     |

| MA9     | 12   | NA     | 12   | NA     | 24    | 12     | 24    | 12     |

| MA10    | 13   | NA     | 13   | NA     | 13    | NA     | 25    | 13     |

| MA11    | 14   | NA     | 14   | NA     | 14    | NA     | 14    | NA     |

## 32-bit mapping table for FPM/EDO DRAM

# a. Symmetric:

| Туре    | 256K | (9x9)  | 1M (10x10) |        | 4M (1 | 1x11)  | 16M ( | 12x12) |

|---------|------|--------|------------|--------|-------|--------|-------|--------|

| Address | Row  | Column | Row        | Column | Row   | Column | Row   | Column |

| MA0     | 15   | 3      | 15         | 3      | 15    | 3      | 15    | 3      |

| MA1     | 16   | 4      | 16         | 4      | 16    | 4      | 16    | 4      |

| MA2     | 17   | 5      | 17         | 5      | 17    | 5      | 17    | 5      |

| MA3     | 18   | 6      | 18         | 6      | 18    | 6      | 18    | 6      |

| MA4     | 19   | 7      | 19         | 7      | 19    | 7      | 19    | 7      |

| MA5     | 11   | 8      | 20         | 8      | 20    | 8      | 20    | 8      |

| MA6     | 12   | 9      | 21         | 9      | 21    | 9      | 21    | 9      |

| MA7     | 13   | 2      | 13         | 2      | 22    | 2      | 22    | 2      |

| MA8     | 14   | 10     | 14         | 10     | 23    | 10     | 23    | 10     |

| MA9     | NA   | NA     | 12         | 11     | 13    | 11     | 24    | 11     |

| MA10    | NA   | NA     | NA         | NA     | 14    | 12     | 25    | 12     |

| MA11    | NA   | NA     | NA         | NA     | NA    | NA     | 14    | 13     |

## b. Asymmetric:

| Туре                                       | 512K                                                                                                                     | (10x9)                                                                                                              | 1M (                                                                                                                     | 11x9)                                                                                                     | 2M (1                                                                                                                    | 1x10)                                                                                                               |                                                                                                                          |                                                                                                           |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Address                                    | Row                                                                                                                      | Column                                                                                                              | Row                                                                                                                      | Column                                                                                                    | Row                                                                                                                      | Column                                                                                                              |                                                                                                                          |                                                                                                           |

| MA0                                        | 15                                                                                                                       | 3                                                                                                                   | 15                                                                                                                       | 3                                                                                                         | 15                                                                                                                       | 3                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA1                                        | 16                                                                                                                       | 4                                                                                                                   | 16                                                                                                                       | 4                                                                                                         | 16                                                                                                                       | 4                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA2                                        | 17                                                                                                                       | 5                                                                                                                   | 17                                                                                                                       | 5                                                                                                         | 17                                                                                                                       | 5                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA3                                        | 18                                                                                                                       | 6                                                                                                                   | 18                                                                                                                       | 6                                                                                                         | 18                                                                                                                       | 6                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA4                                        | 19                                                                                                                       | 7                                                                                                                   | 19                                                                                                                       | 7                                                                                                         | 19                                                                                                                       | 7                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA5                                        | 20                                                                                                                       | 8                                                                                                                   | 20                                                                                                                       | 8                                                                                                         | 20                                                                                                                       | 8                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA6                                        | 14                                                                                                                       | 9                                                                                                                   | 21                                                                                                                       | 9                                                                                                         | 21                                                                                                                       | 9                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA7                                        | 13                                                                                                                       | 2                                                                                                                   | 13                                                                                                                       | 2                                                                                                         | 22                                                                                                                       | 2                                                                                                                   |                                                                                                                          |                                                                                                           |

| MA8                                        | 11                                                                                                                       | 10                                                                                                                  | 11                                                                                                                       | 10                                                                                                        | 14                                                                                                                       | 10                                                                                                                  |                                                                                                                          |                                                                                                           |

| MA9                                        | 12                                                                                                                       | NA                                                                                                                  | 12                                                                                                                       | NA                                                                                                        | 12                                                                                                                       | 11                                                                                                                  |                                                                                                                          |                                                                                                           |

| MA10                                       | NA                                                                                                                       | NA                                                                                                                  | 14                                                                                                                       | NA                                                                                                        | 13                                                                                                                       | NA                                                                                                                  |                                                                                                                          |                                                                                                           |

| MA11                                       | NA                                                                                                                       | NA                                                                                                                  | NA                                                                                                                       | NA                                                                                                        | NA                                                                                                                       | NA                                                                                                                  |                                                                                                                          |                                                                                                           |

|                                            |                                                                                                                          |                                                                                                                     |                                                                                                                          |                                                                                                           |                                                                                                                          |                                                                                                                     |                                                                                                                          |                                                                                                           |

|                                            |                                                                                                                          |                                                                                                                     | 2M (12x9)                                                                                                                |                                                                                                           |                                                                                                                          |                                                                                                                     | (j                                                                                                                       |                                                                                                           |

| Туре                                       | 1M (                                                                                                                     | 12x8)                                                                                                               | 2M (                                                                                                                     | 12x9)                                                                                                     | 4M (1                                                                                                                    | 2x10)                                                                                                               | 8M (1                                                                                                                    | 2x11)                                                                                                     |

| Type<br>Address                            | 1M (<br>Row                                                                                                              | 12x8)<br>Column                                                                                                     | 2M (<br>Row                                                                                                              | 12x9)<br>Column                                                                                           | 4M (1<br>Row                                                                                                             | 2x10)<br>Column                                                                                                     | 8M (1<br>Row                                                                                                             | 2x11)<br>Column                                                                                           |

|                                            | `                                                                                                                        | ·                                                                                                                   | `                                                                                                                        | 1 <u> </u>                                                                                                |                                                                                                                          | <u> </u>                                                                                                            |                                                                                                                          |                                                                                                           |

| Address                                    | Row                                                                                                                      | Column<br>3<br>4                                                                                                    | Row                                                                                                                      | Column<br>3<br>4                                                                                          | Row                                                                                                                      | Column<br>3<br>4                                                                                                    | Row                                                                                                                      | Column<br>3<br>4                                                                                          |

| Address<br>MA0                             | Row 15                                                                                                                   | Column<br>3                                                                                                         | Row 15                                                                                                                   | Column<br>3                                                                                               | Row 15                                                                                                                   | Column<br>3                                                                                                         | Row 15                                                                                                                   | Column<br>3                                                                                               |

| Address<br>MA0<br>MA1                      | Row<br>15<br>16                                                                                                          | Column<br>3<br>4                                                                                                    | Row<br>15<br>16                                                                                                          | Column           3           4           5           6                                                    | Row<br>15<br>16                                                                                                          | Column<br>3<br>4                                                                                                    | Row<br>15<br>16                                                                                                          | Column<br>3<br>4                                                                                          |

| Address<br>MA0<br>MA1<br>MA2               | Row<br>15<br>16<br>17                                                                                                    | Column<br>3<br>4<br>5                                                                                               | Row           15           16           17                                                                               | Column<br>3<br>4<br>5                                                                                     | Row           15           16           17                                                                               | Column<br>3<br>4<br>5                                                                                               | Row           15           16           17                                                                               | Column<br>3<br>4<br>5                                                                                     |

| Address<br>MA0<br>MA1<br>MA2<br>MA3        | Row           15           16           17           18                                                                  | Column           3           4           5           6                                                              | Row           15           16           17           18                                                                  | Column           3           4           5           6                                                    | Row           15           16           17           18                                                                  | Column           3           4           5           6                                                              | Row           15           16           17           18                                                                  | Column           3           4           5           6                                                    |

| Address<br>MA0<br>MA1<br>MA2<br>MA3<br>MA4 | Row           15           16           17           18           19                                                     | Column           3           4           5           6           7                                                  | Row           15           16           17           18           19                                                     | Column           3           4           5           6           7                                        | Row           15           16           17           18           19                                                     | Column           3           4           5           6           7                                                  | Row           15           16           17           18           19                                                     | Column           3           4           5           6           7                                        |

| AddressMA0MA1MA2MA3MA4MA5                  | Row           15           16           17           18           19           20                                        | Column           3           4           5           6           7           8                                      | Row           15           16           17           18           19           20                                        | Column 3 4 5 6 7 8                                                                                        | Row           15           16           17           18           19           20                                        | Column           3           4           5           6           7           8                                      | Row           15           16           17           18           19           20                                        | Column           3           4           5           6           7           8                            |

| AddressMA0MA1MA2MA3MA4MA5MA6               | Row           15           16           17           18           19           20           21                           | Column           3           4           5           6           7           8           9                          | Row           15           16           17           18           19           20           21                           | Column           3           4           5           6           7           8           9                | Row           15           16           17           18           19           20           21                           | Column           3           4           5           6           7           8           9                          | Row           15           16           17           18           19           20           21                           | Column           3           4           5           6           7           8           9                |

| AddressMA0MA1MA2MA3MA4MA5MA6MA7            | Row           15           16           17           18           19           20           21           10              | Column           3           4           5           6           7           8           9           2              | Row           15           16           17           18           19           20           21           22              | Column 3 4 5 6 7 8 9 2                                                                                    | Row           15           16           17           18           19           20           21           22              | Column           3           4           5           6           7           8           9           2              | Row           15           16           17           18           19           20           21           22              | Column         3           4         5           6         7           8         9           2         2  |

| AddressMA0MA1MA2MA3MA4MA5MA6MA7MA8         | Row           15           16           17           18           19           20           21           10           11 | Column           3           4           5           6           7           8           9           2           NA | Row           15           16           17           18           19           20           21           22           11 | Column         3           4         5           6         7           8         9           2         10 | Row           15           16           17           18           19           20           21           22           23 | Column           3           4           5           6           7           8           9           2           10 | Row           15           16           17           18           19           20           21           22           23 | Column         3           4         5           6         7           8         9           2         10 |

## **MA Mapping table for SDRAM**

# a. 2Banks Device SDRAM Type:

| Туре    | 1M (12 | x11x8) | 2M (1: | x11x9) | 4M (1x | 11x10) |

|---------|--------|--------|--------|--------|--------|--------|

| Address | Row    | Column | Row    | Column | Row    | Column |

| MA0     | 15     | 3      | 15     | 3      | 15     | 3      |

| MA1     | 16     | 4      | 16     | 4      | 16     | 4      |

| MA2     | 17     | 5      | 17     | 5      | 17     | 5      |

| MA3     | 18     | 6      | 18     | 6      | 18     | 6      |

| MA4     | 19     | 7      | 19     | 7      | 19     | 7      |

| MA5     | 20     | 8      | 20     | 8      | 20     | 8      |

| MA6     | 21     | 9      | 21     | 9      | 21     | 9      |

| MA7     | 22     | 10     | 22     | 10     | 22     | 10     |

| MA8     | 12     | NA     | 23     | 11     | 23     | 11     |

| MA9     | 13     | NA     | 13     | NA     | 24     | 12     |

| MA10    | 14     | NA     | 14     | NA     | 14     | NA     |

| MA11    | 11     | 11     | 12     | 12     | 13     | 13     |

| MA12    | NA     | NA     | NA     | NA     | NA     | NA     |

| MA13    | NA     | NA     | NA     | NA     | NA     | NA     |

| MA14    | NA     | NA     | NA     | NA     | NA     | NA     |

| Туре    | 4M (1: | x13x8)     | 8M (1: | x13x9) | 16M (12 | x13x10) |  |

|---------|--------|------------|--------|--------|---------|---------|--|

| Address | Row    | Row Column |        | Column | Row     | Column  |  |

| MA0     | 15     | 3          | 15     | 3      | 15      | 3       |  |

| MA1     | 16     | 4          | 16     | 4      | 16      | 4       |  |

| MA2     | 17     | 5          | 17     | 5      | 17      | 5       |  |

| MA3     | 18     | 6          | 18     | 6      | 18      | 6       |  |

| MA4     | 19     | 7          | 19     | 7      | 19      | 7       |  |

| MA5     | 20     | 8          | 20     | 8      | 20      | 8       |  |

| MA6     | 21     | 9          | 21     | 9      | 21      | 9       |  |

| MA7     | 22     | 10         | 22     | 10     | 22      | 10      |  |

| MA8     | 12     | NA         | 23     | 11     | 23      | 11      |  |

| MA9     | 13     | NA         | 13     | NA     | 24      | 12      |  |

| MA10    | 14     | NA         | 14     | NA     | 14      | NA      |  |

| MA11    | 11     | 11         | 12     | 12     | 13      | 13      |  |

| MA12    | NA     | NA         | NA     | NA     | NA      | NA      |  |

| MA13    | 23     | NA         | 24     | NA     | 25      | NA      |  |

| MA14    | 24     | NA         | 25     | NA     | 26      | NA      |  |

## b. 4banks Device SDRAM Type:

| Туре                                                                                                                  | 2M (2x                                                                                                | (11x8))                                                  | 4M (2)                                                                                                                      | x12x8)                                                   | 8M (2)                                                                                                                               | x12x9)                                                   | 16M (2x12x10) |        |  |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------|--------|--|

| Address                                                                                                               | Row                                                                                                   | Column                                                   | Row                                                                                                                         | Column                                                   | Row                                                                                                                                  | Column                                                   | Row           | Column |  |

| MA0                                                                                                                   | 15                                                                                                    | 3                                                        | 15                                                                                                                          | 3                                                        | 15                                                                                                                                   | 3                                                        | 15            | 3      |  |

| MA1                                                                                                                   | 16                                                                                                    | 4                                                        | 16                                                                                                                          | 4                                                        | 16                                                                                                                                   | 4                                                        | 16            | 4      |  |

| MA2                                                                                                                   | 17                                                                                                    | 5                                                        | 17                                                                                                                          | 5                                                        | 17                                                                                                                                   | 5                                                        | 17            | 5      |  |

| MA3                                                                                                                   | 18                                                                                                    | 6                                                        | 18                                                                                                                          | 6                                                        | 18                                                                                                                                   | 6                                                        | 18            | 6      |  |

| MA4                                                                                                                   | 19                                                                                                    | 7                                                        | 19                                                                                                                          | 7                                                        | 19                                                                                                                                   | 7                                                        | 19            | 7      |  |

| MA5                                                                                                                   | 20                                                                                                    | 8                                                        | 20                                                                                                                          | 8                                                        | 20                                                                                                                                   | 8                                                        | 20            | 8      |  |

| MA6                                                                                                                   | 21                                                                                                    | 9                                                        | 21                                                                                                                          | 9                                                        | 21                                                                                                                                   | 9                                                        | 21            | 9      |  |

| MA7                                                                                                                   | 22                                                                                                    | 10                                                       | 22                                                                                                                          | 10                                                       | 22                                                                                                                                   | 10                                                       | 22            | 10     |  |

| MA8                                                                                                                   | 23                                                                                                    | NA                                                       | 23                                                                                                                          | NA                                                       | 23                                                                                                                                   | 11                                                       | 23            | 11     |  |

| MA9                                                                                                                   | 13                                                                                                    | NA                                                       | 13                                                                                                                          | NA                                                       | 24                                                                                                                                   | NA                                                       | 24            | 12     |  |

| MA10                                                                                                                  | 14                                                                                                    | NA                                                       | 14                                                                                                                          | NA                                                       | 14                                                                                                                                   | NA                                                       | 25            | NA     |  |

| MA11                                                                                                                  | 11                                                                                                    | 11                                                       | 11                                                                                                                          | 11                                                       | 12                                                                                                                                   | 12                                                       | 13            | 13     |  |

| MA12                                                                                                                  | 12                                                                                                    | 12                                                       | 12                                                                                                                          | 12                                                       | 13                                                                                                                                   | 13                                                       | 14            | 14     |  |

| MA13                                                                                                                  | NA                                                                                                    | NA                                                       | 24                                                                                                                          | NA                                                       | 25                                                                                                                                   | NA                                                       | 26            | NA     |  |

| MA14                                                                                                                  | NA                                                                                                    | NA                                                       | NA                                                                                                                          | NA                                                       | NA                                                                                                                                   | NA                                                       | NA            | NA     |  |

| ( <del></del>                                                                                                         |                                                                                                       |                                                          |                                                                                                                             |                                                          |                                                                                                                                      |                                                          | 1             |        |  |

| Туре                                                                                                                  | 8M (2                                                                                                 | x13x8)                                                   | 16M (2                                                                                                                      | x13x9)                                                   | 32M (2x13x10)                                                                                                                        |                                                          |               |        |  |

| Address                                                                                                               | Row                                                                                                   | Column                                                   | Row                                                                                                                         | Column                                                   | Row                                                                                                                                  | Column                                                   |               |        |  |

| MA0                                                                                                                   | 15                                                                                                    | 2                                                        | 1 -                                                                                                                         |                                                          |                                                                                                                                      |                                                          |               |        |  |

| MA1                                                                                                                   |                                                                                                       | 3                                                        | 15                                                                                                                          | 3                                                        | 15                                                                                                                                   | 3                                                        |               |        |  |

| ri                                                                                                                    | 16                                                                                                    | 4                                                        | 16                                                                                                                          | 4                                                        | 16                                                                                                                                   | 4                                                        |               |        |  |

| MA2                                                                                                                   | 16<br>17                                                                                              | 4<br>5                                                   | 16<br>17                                                                                                                    | 4<br>5                                                   |                                                                                                                                      | 4<br>5                                                   |               |        |  |

| MA2<br>MA3                                                                                                            |                                                                                                       | 4<br>5<br>6                                              | 16                                                                                                                          | 4<br>5<br>6                                              | 16                                                                                                                                   | 4                                                        |               |        |  |

| MA3<br>MA4                                                                                                            | 17<br>18<br>19                                                                                        | 4<br>5<br>6<br>7                                         | 16<br>17<br>18<br>19                                                                                                        | 4<br>5<br>6<br>7                                         | 16<br>17<br>18<br>19                                                                                                                 | 4<br>5<br>6<br>7                                         |               |        |  |

| MA3                                                                                                                   | 17<br>18                                                                                              | 4<br>5<br>6<br>7<br>8                                    | 16<br>17<br>18                                                                                                              | 4<br>5<br>6<br>7<br>8                                    | 16<br>17<br>18                                                                                                                       | 4<br>5<br>6<br>7<br>8                                    |               |        |  |

| MA3<br>MA4                                                                                                            | 17<br>18<br>19                                                                                        | 4<br>5<br>6<br>7                                         | 16<br>17<br>18<br>19                                                                                                        | 4<br>5<br>6<br>7                                         | 16<br>17<br>18<br>19                                                                                                                 | 4<br>5<br>6<br>7                                         |               |        |  |

| MA3<br>MA4<br>MA5                                                                                                     | 17<br>18<br>19<br>20                                                                                  | 4<br>5<br>6<br>7<br>8                                    | 16<br>17<br>18<br>19<br>20                                                                                                  | 4<br>5<br>6<br>7<br>8                                    | 16<br>17<br>18<br>19<br>20                                                                                                           | 4<br>5<br>6<br>7<br>8                                    |               |        |  |

| MA3<br>MA4<br>MA5<br>MA6<br>MA7<br>MA8                                                                                | 17<br>18<br>19<br>20<br>21                                                                            | 4<br>5<br>6<br>7<br>8<br>9                               | 16         17         18         19         20         21         22         23                                             | 4<br>5<br>6<br>7<br>8<br>9                               | 16<br>17<br>18<br>19<br>20<br>21                                                                                                     | 4<br>5<br>6<br>7<br>8<br>9                               |               |        |  |

| MA3<br>MA4<br>MA5<br>MA6<br>MA7                                                                                       | 17<br>18<br>19<br>20<br>21<br>22                                                                      | 4<br>5<br>6<br>7<br>8<br>9<br>10                         | 16           17           18           19           20           21           22                                            | 4<br>5<br>6<br>7<br>8<br>9<br>10                         | 16           17           18           19           20           21           22                                                     | 4<br>5<br>6<br>7<br>8<br>9<br>10                         |               |        |  |

| MA3<br>MA4<br>MA5<br>MA6<br>MA7<br>MA8                                                                                | 17<br>18<br>19<br>20<br>21<br>22<br>23                                                                | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>NA                   | 16         17         18         19         20         21         22         23                                             | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                   | 16           17           18           19           20           21           22           23                                        | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11                   |               |        |  |

| MA3           MA4           MA5           MA6           MA7           MA8           MA9                               | 17         18         19         20         21         22         23         13                       | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>NA<br>NA             | 16         17         18         19         20         21         22         23         24                                  | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>NA             | 16         17         18         19         20         21         22         23         24                                           | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12             |               |        |  |

| MA3           MA4           MA5           MA6           MA7           MA8           MA9           MA10                | 17         18         19         20         21         22         23         13         14            | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>NA<br>NA<br>NA       | 16         17         18         19         20         21         22         23         24         14         12         13 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>NA<br>NA<br>NA | 16         17         18         19         20         21         22         23         24         25                                | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>NA       |               |        |  |

| MA3           MA4           MA5           MA6           MA7           MA8           MA9           MA10           MA11 | 17         18         19         20         21         22         23         13         14         11 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>NA<br>NA<br>NA<br>11 | 16         17         18         19         20         21         22         23         24         14         12            | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>NA<br>NA<br>12 | 16           17           18           19           20           21           22           23           24           25           13 | 4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>NA<br>13 |               |        |  |

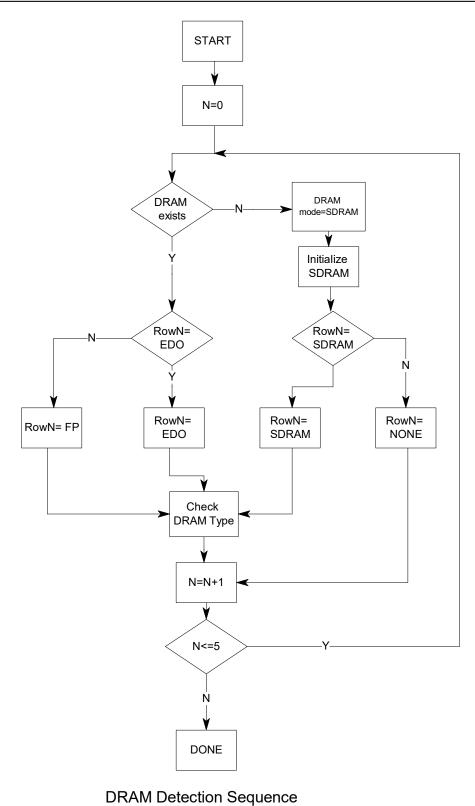

#### 3.3.4 DRAM Detection Sequence

SiS Chip supports six rows (three banks) DRAMs for DRAM's SIMMs/DIMMs from row0 to row5. The DRAMs detection sequence is a row-based detection sequence, it is performed by the BIOS row by row and fulfill the DRAM configuration information into the corresponding DRAM configuration registers. The following steps will be described the DRAM detection sequence.

- Step 1. To detect if there is any DRAM populated in rowN, SiS Chip set this row with maximum DRAM size, then write/read the same address with test pattern by the normal DRAM read/write timing and compare the data. If the read data is the same as the write pattern, then there exists DRAM in the rowN; otherwise, proceed the SDRAM detection from step 3.

- Step 2. If the DRAM is detected in the rowN by step 1, SiS Chip treat it as EDO or FPM DRAM. SiS Chip first write test pattern into DRAM, then set register 55h bit 6 (EDO test bit) to be "1" in PCI/memory bridge configuration register, and do the read, compare test pattern from the same DRAM location. The EDO test bit will delay the data forward to CPU after 4096 CPU clock. If the CPU still get the right data, then EDO mode DRAM is set to this row; otherwise, the FP mode DRAM is set. Go to step 8.

- Step 3. If the DRAM is detected not populated in rowN by normal write/read procedure, SiS Chip check if there is SDRAM exist in this row or not. SiS Chip first assume the DRAM mode is SDRAM (set bits [7:6] of register 60h/61h/62h to be "11" in Host to PCI bridge configuration register, it depends on which bank is under detection), and then do the SDRAM initialization procedure from step 4 to step 7.

- Step 4. Set register 56h bit 3 to "1" to enable SDRAM sizing, then set register 57h bit 7 to be "1", register 57 bit 7 will drive a precharge command to SDRAM, then disable this bit (set to be "0").

- Step 5. Set register 57h bit 6 to be "1", this bit will drive a "mode register set" (MRS) command to SDRAM. When SDRAM receive MRS command, it will load the needed information (Toggle/Linear mode, CAS Latency) into SDRAM. After doing MRS, disable this bit ( set to be "0").

- Step 6. Set register 57h bit 5 to be "1" at least two times, then SDRAM will perform refresh cycle at least two times before the normal operation. Disable this bit ( set to be "0").

- Step 7. Write/Read the test pattern into SDRAM, then compare the data. If the data is correct, SDRAM is detected, and set rowN as SDRAM; otherwise, rowN is no DRAM populated. Set Register 56h bit 3 to "0".

- Step 8. After DRAM mode is set, SiS Chip do DRAM sizing by write/read test pattern based on the MA mapping table.

- Step 9. Repeat from step 1 to step 8 to detect the other rows.

Note : The value of N is from 0 to 5.

DRAM Detection Sequence flow charts are shown below:

## **3.3.5 DRAM Performance**

All the DRAM cycles are synchronous with the CPU clock. The following table shows the different possible speed settings that depend on different DRAM type, RAS# setting, CAS# setting, and so forth.

| setting, and so forth. |                     |               |               | 1        |

|------------------------|---------------------|---------------|---------------|----------|

| Cycle Type             | DRAM type           | 75Mhz         | 66/60/50 Mhz  | Note     |

| Read Page Hit          | EDO                 | 5-2-2-2       | 5-2-2-2       | ¥ 1      |

|                        | FPM                 | 5-3-3-3       | 5-3-3-3       | *1       |

|                        | SDRAM               | 6-1-1-1       | 6-1-1-1       | CL=2     |

|                        |                     | 7-1-1-1       | 7-1-1-1       | CL=3     |

| Read Row Start         | EDO                 | 9-2-2-2       | 8-2-2-2       | *2       |

|                        | FPM                 | 9-3-3-3       | 8-3-3-3       | *1       |

|                        | SDRAM               | 10-1-1-1      | 9-1-1-1       | CL=2     |

|                        |                     | 11-1-1-1      | 10-1-1-1      | CL=3     |

| Read Page Miss         | EDO                 | 13-2-2-2      | 12-2-2-2      | *3, *4   |

|                        | FPM                 | 13-3-3-3      | 12-3-3-3      | 1        |

|                        |                     |               |               | *3       |

|                        |                     |               |               | *4       |

|                        | SDRAM               | 11-1-1-1      | 10-1-1-1      | CL=2, *4 |

|                        |                     | 12-1-1-1      | 11-1-1-1      | CL=3, *4 |

| Back-to-Back           | EDO                 | 5-2-2-2-2-2-2 | 5-2-2-2-2-2-2 |          |

| Burst Read Page        |                     |               |               |          |

| Hit                    |                     |               |               |          |

|                        | FPM                 | 5-3-3-3-3-3-3 | 5-3-3-3-3-3-3 |          |

|                        | SDRAM               | 6-1-1-2-1-1-1 | 6-1-1-2-1-1-1 | CL=2, *5 |

|                        |                     | 7-1-1-3-1-1-1 | 7-1-1-3-1-1-1 | CL=3, *5 |

| Posted Write           | EDO/FPM/            | 3-1-1-1       | 3-1-1-1       |          |

|                        | SDRAM               |               |               |          |

| Write Retire Rate      | EDO                 | 2-2-2         | 2-2-2         |          |