MAN-000649-000 Revision 1.2 September 12, 2000

# PCI-649

# Bus Master Ultra DMA PCI-IDE/ATA Chip

# **Product Specification**

CMD Technology, Inc. 9501 Jeronimo Road Irvine, CA 92618 (949) 454-0800 www.cmd.com Copyright © 2000, CMD Technology, Inc. All rights reserved. No part of this publication maybe reproduced, transmitted, transcribed, or translated into any language or computer format, in any form or by any means without prior written permission of:

CMD Technology, Inc. 9501 Jeronimo Road Irvine, CA 92618, USA.

CMD Technology, Inc. reserves the right to make changes to the product(s) or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable, but CMD Technology, Inc. shall not be responsible for any errors that may appear in this document. CMD Technology, Inc. makes no commitment to update or keep current the information contained in this document.

However, no responsibility is assumed for its use; nor any infringement of patents or other rights of third parties which may result from its use. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

CMD Technology, Inc. products are not designed or intended for use in Life Support Systems. A Life Support System is a product or system intended to support or sustain life, which if it fails, can be reasonably expected to result in significant personal injury or death. If Buyer or any of its direct or indirect customers applies any product purchased or licensed from CMD Technology, Inc. to any such unauthorized use, Buyer shall indemnify and hold CMD Technology, Inc., its affiliates and their respective suppliers, harmless against all claims, costs, damages and expenses arising directly or indirectly, out of any such unintended or unauthorized use, even if such claims alleges that CMD Technology, Inc. or any other person or entity was negligent in designing or manufacturing the product.

Specifications are subject to change without notice.

# Table of Contents

i

| 1. Overview                                                              | 1-1  |

|--------------------------------------------------------------------------|------|

| Key Benefits                                                             | 1-1  |

| Features                                                                 | 1-1  |

| PCI-649 Technical Description                                            | 1-2  |

| Functional Description                                                   | 1-2  |

| Functional Block Diagram                                                 | 1-3  |

| PCI Interface                                                            | 1-4  |

| PCI Initialization                                                       | 1-4  |

| PCI Bus Operations                                                       | 1-4  |

| PCI Configuration Space                                                  | 1-5  |

| Deviations from the Specification                                        | 1-6  |

| 2. Pin Descriptions                                                      | 2-1  |

| Pin-Out Diagram                                                          | 2-1  |

| Pin Descriptions (in numerical order)                                    | 2-3  |

| Pin Descriptions (by category/alphabetical order)                        | 2-9  |

| IDE/ATA Primary Channel                                                  | 2-9  |

| IDE/ATA Secondary Channel                                                | 2-11 |

| PCI Interface                                                            | 2-14 |

| Miscellaneous I/O                                                        | 2-17 |

| 3. Bootstrap Jumper Settings                                             | 3-1  |

| 4. External EPROM Pin-out Diagram                                        | 4-1  |

| 5. Mechanical Dimensions (TQFP)                                          | 5-1  |

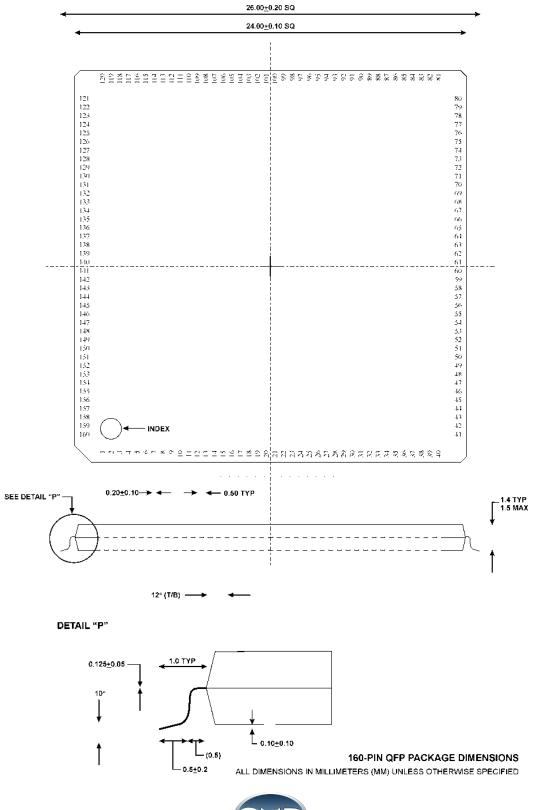

| PCI-649 Dimensions                                                       | 5-1  |

| Physical Part Markings                                                   | 5-2  |

| Part Number to Order                                                     | 5-2  |

| 6. Register Definitions                                                  | 6-1  |

| 6.1 PCI Configuration Space Registers                                    | 6-1  |

| PCI Configuration Registers Map                                          | 6-1  |

| Vendor/Device ID                                                         | 6-2  |

| Command/Status Register                                                  | 6-2  |

| Class/Revision ID Register                                               | 6-4  |

| Programming Interface Byte Register (PROGIF)                             | 6-4  |

| Interrupt Line Register (INTLINE)                                        | 6-5  |

| Subsystem Configuration Register (SUBCONF)                               | 6-6  |

| 6.2 Task File Registers                                                  | 6-6  |

| 6.3 CMD Proprietary IDE/ATA Timing Control Registers for Overall Control | 6-7  |

| Configuration Register (CFR)                                             | 6-7  |

| IDE/ATA 8-bits Task File Timing Control Register (CMDTIM)                | 6-7  |

|                                                                          |      |

| 6.4 CMD Proprietary IDE/ATA Timing Control Register for Primary Channel<br>Control Register for Primary Channel (CNTRL) | 6-8<br>6-8 |

|-------------------------------------------------------------------------------------------------------------------------|------------|

| Status Register for Primary Channel                                                                                     | 6-8        |

| PIO IDE/ATA Address Setup Timing Register for Primary Channel's Master Drive (ARTTIMO)                                  | 6-8        |

| PIO/MDMA IDE/ATA Data DIOR/DIOW or DMACK Timing Register for Primary Channel's Master Drive (DRWTIMO)                   | 6-8        |

| PIO IDE/ATA Address Setup Timing Register for Primary Channel's Slave Drive (ARTTIM1)                                   | 6-9        |

| PIO/MDMA Data DIOR/DIOW or DMACK Timing Register for Primary Channel's Slave Drive (DRWTIM1)                            |            |

| Active Count Conversion Table                                                                                           | 6-9        |

| Recovery Count Conversion Table                                                                                         | 6-9        |

|                                                                                                                         | 6-10       |

| 5                                                                                                                       | 6-10       |

|                                                                                                                         | 6-10       |

|                                                                                                                         | 6-10       |

| <b>0</b> ( )                                                                                                            | 6-10       |

|                                                                                                                         | 6-10       |

|                                                                                                                         | 6-11       |

| ,                                                                                                                       | 6-11       |

|                                                                                                                         | 6-11       |

|                                                                                                                         | 6-11       |

|                                                                                                                         | 6-12       |

| Capability ID (CAP_ID)                                                                                                  | 6-12       |

| Next Item Pointer (N-I_PTR)                                                                                             | 6-12       |

| Power Management Capabilities Register (PMC)                                                                            | 6-12       |

| PCI Functions Power Management State (PMCSP)                                                                            | 6-14       |

| Data Register (DR)                                                                                                      | 6-15       |

| 6.8 Overall PCI Master Control Registers for both channels                                                              | 6-16       |

| Interrupt Enable and Status Register for both channels &                                                                |            |

| Master Read Select Control Register for both channels (MRDMODE)                                                         | 6-16       |

| Bus Master IDE/ATA Control Status Register (BMIDECSR)                                                                   | 6-17       |

|                                                                                                                         | 6-17       |

| <b>o</b> ,                                                                                                              | 6-17       |

|                                                                                                                         | 6-18       |

|                                                                                                                         | 6-19       |

|                                                                                                                         | 6-20       |

|                                                                                                                         | 6-21       |

| 5                                                                                                                       | 6-21       |

|                                                                                                                         | 6-21       |

|                                                                                                                         | 6-22       |

|                                                                                                                         | 6-23       |

| 7. Electrical Specifications                                           | 7-1  |

|------------------------------------------------------------------------|------|

| 7.1 DC Specifications                                                  | 7-1  |

| Maximum Ratings                                                        | 7-1  |

| Operating Conditions (Vss = $0V$ )                                     | 7-1  |

| 7.2 DC Characteristics (For VDD= 3.3V, 0 to 70°C)                      | 7-1  |

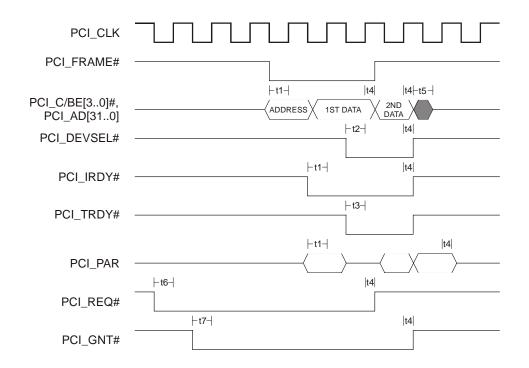

| 8. PCI DMA Master Read Timing (33MHz PCI_CLK)                          | 8-1  |

| DMA Read Signal Diagram                                                | 8-1  |

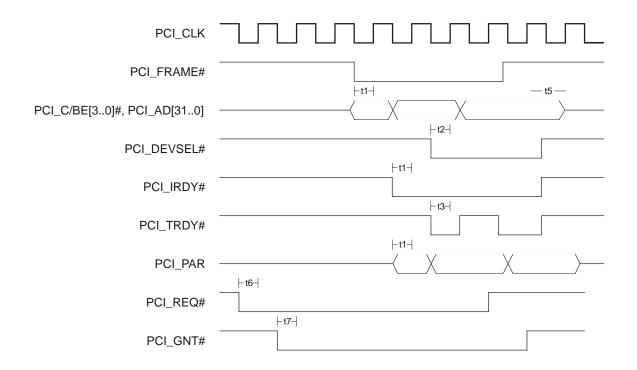

| 9. PCI DMA Master Write Timing (33MHz PCI_CLK)                         | 9-1  |

| DMA Write Signal Diagram                                               | 9-1  |

| 10. Appendix A                                                         | 10-1 |

| 10.1 Timing Settings Guide                                             | 10-1 |

| 10.2 PCI Bus Speed and Clock Cycle                                     | 10-1 |

| 10.3 Setting the Drive Mode                                            | 10-1 |

| 10.4 Register Set-up for PIO/MDMA Timing                               | 10-3 |

| IDE/ATA Task File Timing Control Register (CMDTIM)                     | 10-3 |

| Drive x Address Setup Register (ARTTIMx) for PIO modes                 | 10-3 |

| Drive x DIOR/DIOW or DACK Timing Register (DRWTIMx) for PIO/MDMA Modes | 10-3 |

| Channel x in Ultra DMA IDE/ATA Timing Control Registers (UDIDETCRx)    | 10-4 |

| 10.5 Register Set-Up for UDMA Timing                                   | 10-4 |

| IDE/ATA Task File Timing Control Register (CMDTIM)                     | 10-4 |

| Channel x Ultra DMA IDE/ATA Timing Control Registers (UDIDETCRx)       | 10-4 |

| 11. Appendix B: Miscellaneous Design Notes                             | 11-1 |

| 11.1 Configuration Setup                                               | 11-1 |

| 11.2 Configuration Mechanism #2                                        | 11-1 |

| 11.3 PIO Mode Interrupt Processing                                     | 11-1 |

| 11.4 DMA Programming                                                   | 11-2 |

| 11.5 Read Ahead Operation                                              | 11-2 |

| 11.6 Recommended PIO Mode Register Setting                             |      |

| (ICS-000649-C01 Version Only)                                          | 11-2 |

| 12. Appendix C: Deviations from the Specification                      | 12-1 |

| Deviations from the Specification                                      | 12-1 |

мD

Page intentionally left blank.

# 1. Overview

CMD's PCI-649 is a single chip solution for a PCI to IDE/ATA controller. It accepts host commands through the PCI bus, processes them and transfers data between the host and IDE/ATA devices. It can be used to control two independent IDE/ATA channels: primary and secondary. Each channel has its own IDE/ATA bus and will support up to two ATA/ATAPI devices for a maximum of four devices. The PCI-649 supports up to a 100 MB/sec transfer rate as specified in ATA/ATAPI-5.

This controller provides OEMs with an enabling solution for interfacing to storage media such as hard disk drives. For personal computer manufacturers, using the PCI-649 will differentiate them from the competition by allowing for the addition of more drives and incorporating the newest drive standards, all at a lower cost. For non-personal computer manufacturers, it will allow a cost-effective solution with hard disk drives to be implemented in their system.

### **Key Benefits**

CMD's PCI-649 stand-alone Ultra ATA/100 PCI to IDE/ATA host controller is the perfect single chip solution for designs based on chipsets without an integrated IDE host controller, or designs which need to expand the number of IDE channels to accommodate the growing number of storage peripherals with IDE interface. Any system with a PCI bus interface can simply add the Ultra ATA/100 interface by adding a card with the PCI-649 and loading the driver into the system.

The PCI-649 comes complete with drivers for DOS, Windows 95/98, Windows Millennium, Windows NT 4.0, and Windows 2000. It is also fully operational and compatible with default IDE drivers from Microsoft.

#### Features

- 2 independent IDE/ATA Channels

- Supports up to four IDE/ATA devices

- 128 Bytes buffer

- · Supports ultra and multiword DMA timing modes

- CRC (Cyclical Redundancy Check)

- Built in 80-Pin cable detect circuitry

- Supports External BIOS

- 32-bit 33 MHz PCI Interface

- Supports bus master DMA at 133 MB/sec PCI burst rate

- Supports maximum IDE/ATA data transfer rate of 100 MB/sec

- Compatible with Microsoft IDE/ATA drivers (Windows 95/98, Windows Millennium, WIndows NT 4.0 and Windows 2000)

- 3.3V Operating Voltage with 5V tolerant I/O

- Available in 160-pin TQFP

## **PCI-649 Technical Description**

The PCI-649 is available in a 160-pin TQFP (Thin Quad Flat Package) including more ground pins in order to accommodate the new higher data transfer rate specified in the ATA/ATAPI-5 specification. It is compliant with ATA/ATAPI-5 and will support transfer rates up to the Ultra ATA/100 rate in both channels. Each channel is independent and will support up to two IDE/ATA devices (such as hard disk drives, DVD drives, etc.) for a total of four devices per controller. The selected PCI bus targeted for this device is the 32-bit wide bus at 33MHz. The chip has an internal phase lock loop that will provide the 100MHz internal clock, allowing a data transfer rate of 100MB/sec on IDE/ATA interface. A built-in 80-pin cable detector provides users the ability to determine whether a cable can support the latest Ultra ATA/100 transfer rate. The PCI-649 is capable of supporting Native mode, external BIOS, Legacy mode, Enhanced IDE mode (ultra DMA and multiword DMA mode).

#### References

For more details about the IDE/ATA technology, the reader is referred to the following industry specifications:

- ATA/ATAPI-5 (at time of publication, ATA/ATAPI-5 has not been formally approved)

- PCI Local Bus Specification Revision 2.1

- Advanced Power Management Specification Revision 1.0

- PCI IDE Controller Specification Revision 1.0

- Programming Interface for Bus Master IDE Controller, Revision 1.0

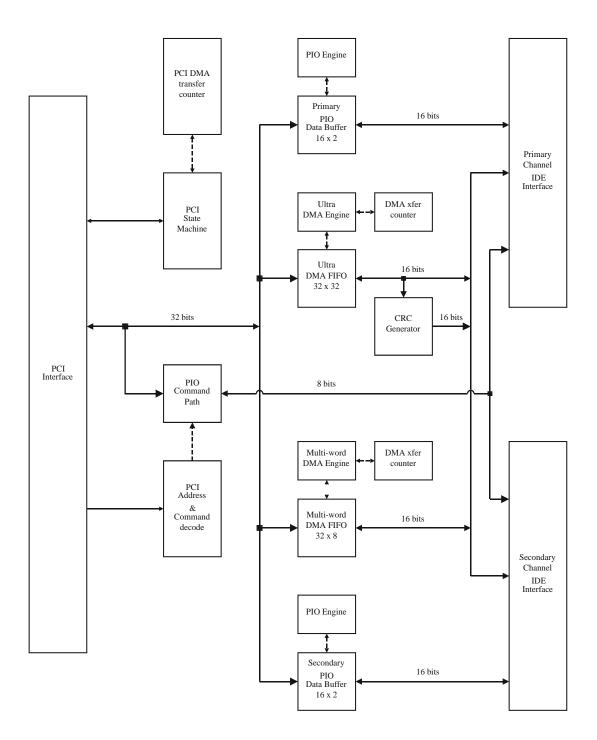

### **Functional Description**

PCI-649 is more than a PCI to IDE/ATA bridge chip that transfers data between the PCI bus and storage media (e.g hard disk drive, etc) over the IDE/ATA bus. As a host controller, it also performs functions associated with the host, such as storing configuration information, and processing data for errors. The PCI-649 can be described in the following functional blocks:

- PCI Interface. Provides the interface to any system that has a PCI bus. Instructions and system clocks are based on this interface.

- IDE/ATA Interface. Two separate channels (Primary and Secondary) to access storage media such as hard disk drive, floppy disk drive, CD-ROM.

- Controller Interface. Additional hardware interface for controlling and configuring the Host Controller.

- Host Function.

# **Functional Block Diagram**

### **PCI Interface**

The PCI-649 PCI interface is compliant with the PCI Local Bus Specification (Revision 2.1, June 1, 1995). PCI stands for Peripheral Component Interconnect, a high-performance and robust interconnect bus that provides a processor-independent data path between the CPU and high-speed peripherals. The standard for PCI is monitored by the PCI Special Interest Group (PCI-SIG). The PCI-SIG is an unincorporated association of members of the microcomputer industry created to monitor and enhance the development of PCI architecture. The PCI-SIG is led by a nine-member steering committee and governed by PCI-SIG bylaws (HTTP://www.pcisig.com/).

The PCI-649 can act as a PCI master and a PCI slave, and contains the PCI-649 PCI configuration space and internal registers. When the PCI-649 needs to access shared memory, it becomes the bus master of the PCI bus and completes the memory cycle without external intervention. In the mode when it acts as a bridge between the PCI bus and the IDE/ATA bus it will behave as a PCI slave.

# **PCI** Initialization

Generally, when a system initializes a module containing a PCI device, the configuration manager reads the configuration space of each PCI device on the PCI bus. Hardware signals select a specific PCI device based on a bus number, a slot number, and a function number. If a device that is addressed (via signal lines) responds to the configuration cycle by claiming the bus, then that function's configuration space is read out from the device during the cycle. Since any PCI device can be a multifunction device, every supported function's configuration space needs to be read from the device. Based on the information read, the configuration manager will assign system resources to each supported function within the device. Sometimes new information needs to be written into the function's configuration space. This is accomplished with a configuration write cycle.

### **PCI Bus Operations**

PCI-649 behaves either as a PCI bus master or a PCI slave device at any time and switches between these modes as required during device operation.

As a PCI slave, the PCI-649 responds to the following PCI bus operations:

- I/O Read

- I/O Write

- Configuration Read

- Configuration Write

- Memory Read

All other PCI cycles are ignored by the PCI-649.

As a PCI bus master, the PCI-649 generates the following PCI bus operations:

- Memory Read Multiple

- Memory Read Line

- Memory Read

- Memory Write

#### **PCI Configuration Space**

This section describes how the PCI-649 implements the required PCI configuration register space. The intent of PCI configuration space definition is to provide an appropriate set of configuration registers which satisfy the needs of current and anticipated system configuration mechanisms, without specifying those mechanisms or otherwise placing constraints on their use. These registers allow for:

- Full device relocation (including interrupt binding)

- Installation, configurations, and booting without user interventions

- System address map construction by device-independent software

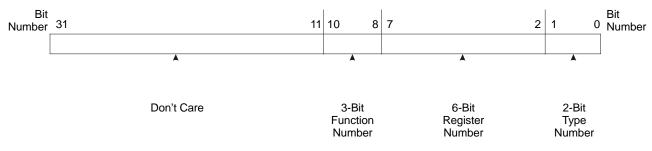

#### Address Lines During Configuration Cycle

PCI-649 only responds to Type 0 configuration cycles. Type 1 cycles, which pass a configuration request on to another PCI bus, are ignored.

The PCI controller in PCI-649 responds to configuration and I/O cycles.

The address phase during a PCI-649 configuration cycle indicates the function number and register number being addressed which can be decoded by observing the status of the address lines AD[31:0].

The value of the signal lines AD[7:2] during the address phase of configuration cycles selects the register of the configuration space to access. Valid values are between 0 and 15, inclusive. Accessing registers outside this range results in an all-0s value being returned on reads, and no action being taken on writes. The Class Code register contains the Class Code, Sub-Class Code, and Register-Level Programming Interface registers.

All writable bits in the configuration space are reset to 0 by the hardware reset, PRST\* asserted. After reset, PCI-649 is disabled and will only respond to PCI configuration write and PCI configuration read cycles. Write cycles to reserved bits and registers will have no effect. Read cycles to reserved bits will always result in 0 being read.

### **Deviations from the Specification**

The PCI-649 product has been developed and tested to the specification listed in this document. As a result of testing and customer feedback, we may become aware of deviations to the specification that could affect the component's operation. To ensure awareness of these deviations by anyone considering the use of the PCI-649, we have included Appendix C, Deviations to the Specification. Please ensure that Appendix C is carefully reviewed. It is also important that you have the most current version of this specification. If there are any questions, please contact CMD Technology, Inc.

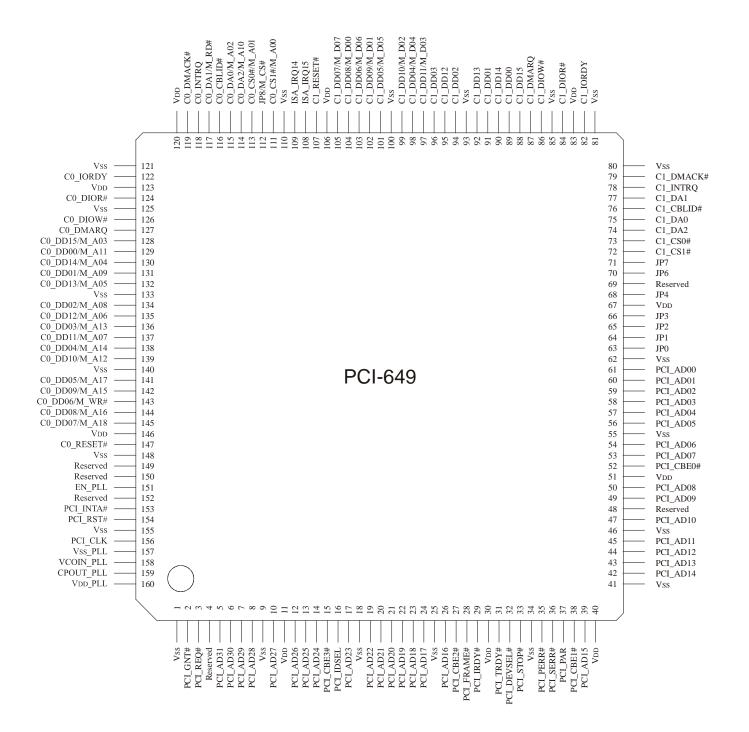

2. Pin Descriptions

#### **Pin-Out Diagram**

| <b>Pin Descriptions</b> | (in numerical order) |

|-------------------------|----------------------|

|-------------------------|----------------------|

| Pin # | Name            | Туре | External<br>Damping<br>Resistor | External<br>Pull Up/<br>Pull Down<br>Resistor | Description                                                                                                                    |

|-------|-----------------|------|---------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                         |

| 2     | PCI_GNT#        | I    | -                               | -                                             | PCI Grant. This signal indicates to the agent that access to the bus has been granted.                                         |

| 3     | PCI_REQ#        | T/O  | -                               | -                                             | PCI Request. This signal indicates to the arbiter that this agent desires use of bus.                                          |

| 4     | Reserved        | -    | -                               | -                                             | Do not connect                                                                                                                 |

| 5     | PCI_AD31        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 6     | PCI_AD30        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 7     | PCI_AD29        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 8     | PCI_AD28        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 9     | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                         |

| 10    | PCI_AD27        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 11    | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                                                                                      |

| 12    | PCI_AD26        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 13    | PCI_AD25        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 14    | PCI_AD24        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 15    | PCI_CBE3#       | В    | -                               | -                                             | Bit 3 of the PCI Bus Command and Byte Enable pins                                                                              |

| 16    | PCI_IDSEL       | I    | -                               | -                                             | PCI ldsel is used as a chip select during configuration read and write transactions.                                           |

| 17    | PCI_AD23        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 18    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                         |

| 19    | PCI_AD22        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 20    | PCI_AD21        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 21    | PCI_AD20        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 22    | PCI_AD19        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 23    | PCI_AD18        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 24    | PCI_AD17        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 25    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                         |

| 26    | PCI_AD16        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                       |

| 27    | PCI_CBE2#       | В    | -                               | -                                             | Bit 2 of the PCI Bus Command and Byte Enable pins                                                                              |

| 28    | PCI_FRAME#      | В    | -                               | -                                             | PCI Frame is a cycle frame driven by the current master to indicate the beginning and duration of an access.                   |

| 29    | PCI_IRDY#       | В    | -                               | -                                             | Initiator Ready indicates the initiating agent's (bus master's) ability to complete the current data phase of the transaction. |

| Pin # | Name            | Туре | External<br>Damping<br>Resistor | External<br>Pull Up/<br>Pull Down<br>Resistor | Description                                                                                                                                                                                                                       |

|-------|-----------------|------|---------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30    | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                                                                                                                                                                                         |

| 31    | PCI_TRDY#       | В    | -                               | -                                             | Target Ready indicates the target agent's (selected device's) ability to complete the current data phase of the transaction.                                                                                                      |

| 32    | PCI_DEVSEL#     | В    | -                               | -                                             | Device select, when actively driven, indicates the driving device has decoded its addresses as target of the current access.                                                                                                      |

| 33    | PCI_STOP#       | В    | -                               | -                                             | Stop indicates that the current target is requesting the master to stop the current transaction.                                                                                                                                  |

| 34    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                                                                                                                            |

| 35    | PCI_PERR#       | В    | -                               | -                                             | Parity Error is used exclusively for the reporting of data parity errors on all PCI transactions except a Special Cycle. The minimum duration of PCI_PERR# is one clock for each data phase that a data parity error is detected. |

| 36    | PCI_SERR#       | O/D  | -                               | -                                             | System Error is used for other error signaling, including address parity and data parity on Special Cycle commands, and may optionally be used on any other non-parity or system errors.                                          |

| 37    | PCI_PAR         | В    | -                               | -                                             | Parity on PCI provides a mechanism to determine transaction by trans-<br>action if the master is successful in addressing the desired target and if<br>data transfers correctly between them.                                     |

| 38    | PCI_CBE1#       | В    | -                               | -                                             | Bit 1 of the PCI Bus Command and Byte Enable pins                                                                                                                                                                                 |

| 39    | PCI_AD15        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 40    | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                                                                                                                                                                                         |

| 41    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                                                                                                                            |

| 42    | PCI_AD14        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 43    | PCI_AD13        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 44    | PCI_AD12        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 45    | PCI_AD11        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 46    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                                                                                                                            |

| 47    | PCI_AD10        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 48    | Reserved        |      | -                               | -                                             | Do not connect                                                                                                                                                                                                                    |

| 49    | PCI_AD09        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 50    | PCI_AD08        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 51    | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                                                                                                                                                                                         |

| 52    | PCI_CBE0#       | В    | -                               | -                                             | Bit 0 of the PCI Bus Command and Byte Enable pins                                                                                                                                                                                 |

| 53    | PCI_AD07        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| 54    | PCI_AD06        | В    | -                               | -                                             | PCI Address and Data Pin                                                                                                                                                                                                          |

| Pin # | Name            | Туре | External<br>Damping<br>Resistor | External<br>Pull Up/<br>Pull Down<br>Resistor | Description                                               |

|-------|-----------------|------|---------------------------------|-----------------------------------------------|-----------------------------------------------------------|

| 55    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                    |

| 56    | PCI_AD05        | В    | -                               | -                                             | PCI Address and Data Pin                                  |

| 57    | PCI_AD04        | В    | -                               | -                                             | PCI Address and Data Pin                                  |

| 58    | PCI_AD03        | В    | -                               | -                                             | PCI Address and Data Pin                                  |

| 59    | PCI_AD02        | В    | -                               | -                                             | PCI Address and Data Pin                                  |

| 60    | PCI_AD01        | В    | -                               | -                                             | PCI Address and Data Pin                                  |

| 61    | PCI_AD00        | В    | -                               | -                                             | PCI Address and Data Pin                                  |

| 62    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                    |

| 63    | JP0             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 64    | JP1             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 65    | JP2             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 66    | JP3             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 67    | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                 |

| 68    | JP4             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 69    | Reserved        | -    | -                               | -                                             | Do not connect                                            |

| 70    | JP6             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 71    | JP7             | Ι    | -                               | -                                             | Configuration Pin. See Chapter 4.                         |

| 72    | C1_CS1#         | 0    | 51 <b>Ω</b>                     | -                                             | Secondary Channel Chip Select for Command Block registers |

| 73    | C1_CS0#         | 0    | 51 <b>Ω</b>                     | -                                             | Secondary Channel Chip Select for Command Block registers |

| 74    | C1_DA2          | 0    | 51 <b>Ω</b>                     | -                                             | Bit 2 of Secondary IDE Channel's Device Address           |

| 75    | C1_DA0          | 0    | 51 <b>Ω</b>                     | -                                             | Bit 0 of Secondary IDE Channel's Device Address           |

| 76    | C1_CBLID#       | Ι    | -                               | -                                             | Secondary IDE Channel's Cable Detect pin                  |

| 77    | C1_DA1          | 0    | 51 <b>Ω</b>                     | -                                             | Bit 1 of Secondary IDE channel's Device Address           |

| 78    | C1_INTRQ        | Ι    | 51 <b>Ω</b>                     | -/10 K $\Omega$                               | Secondary IDE Channel's Interrupt Request                 |

| 79    | C1_DMACK#       | 0    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's DMA Acknowledge pin               |

| 80    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                    |

| 81    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                    |

| 82    | C1_IORDY        | Ι    | 51 $\Omega$                     | 4.7 KΩ/ -                                     | Secondary IDE Channel's I/O Ready pin                     |

| 83    | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                 |

| 84    | C1_DIOR#        | 0    | 51 $\Omega$                     | -                                             | Secondary IDE Channel's Device I/O Read pin               |

| 85    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                    |

| 86    | C1_DIOW#        | 0    | 51 $\Omega$                     | -                                             | Secondary IDE Channel's Disk I/O Write pin                |

ML

| Pin # | Name            | Туре | External<br>Damping<br>Resistor | External<br>Pull Up/<br>Pull Down<br>Resistor | Description                                                                                                                                                                 |

|-------|-----------------|------|---------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 87    | C1_DMARQ        | I    | 51 <b>Ω</b>                     | -/5.6 K $\Omega$                              | Secondary IDE Channel's DMA Request pin                                                                                                                                     |

| 88    | C1_DD15         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 15                                                                                                                                  |

| 89    | C1_DD00         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 0                                                                                                                                   |

| 90    | C1_DD14         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 14                                                                                                                                  |

| 91    | C1_DD01         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 1                                                                                                                                   |

| 92    | C1_DD13         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 13                                                                                                                                  |

| 93    | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                                                                      |

| 94    | C1_DD02         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 2                                                                                                                                   |

| 95    | C1_DD12         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 12                                                                                                                                  |

| 96    | C1_DD03         | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data Bit 3                                                                                                                                   |

| 97    | C1_DD11/M_D03   | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data bit 11 / EPROM Data pin 3                                                                                                               |

| 98    | C1_DD04/M_D04   | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data bit 4 / EPROM Data pin 4                                                                                                                |

| 99    | C1_DD10/M_D02   | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data bit 10 / EPROM Data pin 2                                                                                                               |

| 100   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                                                                      |

| 101   | C1_DD05/M_D05   | В    | 51 $\Omega$                     | -                                             | Secondary IDE Channel's Device Data bit 5 / EPROM Data pin 5                                                                                                                |

| 102   | C1_DD09/M_D01   | В    | 51 $\Omega$                     | -                                             | Secondary IDE Channel's Device Data bit 9 / EPROM Data pin 1                                                                                                                |

| 103   | C1_DD06/M_D06   | В    | 51 $\Omega$                     | -                                             | Secondary IDE Channel's Device Data bit 6 / EPROM Data pin 6                                                                                                                |

| 104   | C1_DD08/M_D00   | В    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Device Data bit 8 / EPROM Data pin 0                                                                                                                |

| 105   | C1_DD07/M_D07   | В    | 51 $\Omega$                     | -/10 K $\Omega$                               | Secondary IDE Channel's Device Data bit 7 / EPROM Data pin 7                                                                                                                |

| 106   | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                                                                                                                                   |

| 107   | C1_RESET#       | 0    | 51 <b>Ω</b>                     | -                                             | Secondary IDE Channel's Disk Reset pin                                                                                                                                      |

| 108   | ISA_IRQ15       | T/O  | -                               |                                               | ISA_IRQ15 is used to request an interrupt for secondary IDE/ATA chan-<br>nel in the PCI IDE/ATA legacy mode It is tri-stated when the IDE/ATA<br>channel is in native mode. |

| 109   | ISA_IRQ14       | T/O  | -                               |                                               | ISA_IRQ14 is used to request an interrupt for primary IDE/ATA channel<br>in the PCI IDE/ATA legacy mode It is tri-stated when the IDE/ATA chan-<br>nel is in native mode.   |

| 110   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                                                                                                      |

| 111   | C0_CS1#/M_A00   | 0    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Chip Select Pin for Command Block registers / EPROM Address pin 0                                                                                     |

| 112   | JP8 / M-CS#     | В    | -                               | -                                             | Configuration Pin/EPROM chip select. Refer to section A-2.                                                                                                                  |

| 113   | C0_CS0#/M_A01   | 0    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Chip Select Pin for Command Block registers / EPROM Address pin 1                                                                                     |

| 114   | C0_DA2/M_A10    | 0    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Address bit 2 / EPROM Address pin 10                                                                                                           |

| 115   | C0_DA0/M_A02    | 0    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Address bit 0 / EPROM Address pin 2                                                                                                            |

ŇD

| Pin # | Name            | Туре | External<br>Damping<br>Resistor | External<br>Pull Up/<br>Pull Down<br>Resistor | Description                                                          |

|-------|-----------------|------|---------------------------------|-----------------------------------------------|----------------------------------------------------------------------|

| 116   | C0_CBLID#       | I    | -                               | -                                             | Primary IDE Channel's Cable Detect Pin                               |

| 117   | C0_DA1 / M_RD#  | 0    | 51Ω                             | -                                             | Primary IDE Channel's Device Address bit 1 / EPROM Read Pin          |

| 118   | C0_INTRQ        | I    | 51Ω                             | -/10 KΩ                                       | Primary IDE Channel's Interrupt Request pin                          |

| 119   | C0_DMACK#       | 0    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's DMA Acknowledge                                |

| 120   | V <sub>DD</sub> | Р    | -                               | -                                             | Power                                                                |

| 121   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                               |

| 122   | C0_IORDY        | I    | 51 <b>Ω</b>                     | 4.7 KΩ/-                                      | Primary IDE Channel's I/O Ready pin                                  |

| 123   | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                            |

| 124   | C0_DIOR#        | 0    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Disk I/O Read pin                              |

| 125   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                               |

| 126   | C0_DIOW#        | 0    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Disk I/O Write pin                             |

| 127   | C0_DMARQ#       | I    | 51 $\Omega$                     | -/5.6 K                                       | Primary IDE Channel's DMA Request pin                                |

| 128   | C0_DD15/M_A03   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 15 / EPROM Address pin 3  |

| 129   | C0_DD00/M_A11   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 0 / EPROM Address pin 11  |

| 130   | C0_DD14/M_A04   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 14 / EPROM Address pin 4  |

| 131   | C0_DD01/M_A09   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 1 / EPROM Address pin 9   |

| 132   | C0_DD13/M_A05   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 13 / EPROM Address pin 5  |

| 133   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                               |

| 134   | C0_DD02/M_A08   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 2 / EPROM Address pin 8   |

| 135   | C0_DD12/M_A06   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 12 / EPROM Address pin 6  |

| 136   | C0_DD03/M_A13   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 3 / EPROM Address pin 13  |

| 137   | C0_DD11/M_A07   | В    | 51 $\Omega$                     | -                                             | Primary IDE Channel's Device Disk Data bit 11 / EPROM Address pin 7  |

| 138   | C0_DD04/M_A14   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 4 / EPROM Address pin 14  |

| 139   | C0_DD10/M_A12   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 10 / EPROM Address pin 12 |

| 140   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                               |

| 141   | C0_DD05/M_A17   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 5 / EPROM Address pin 17  |

| 142   | C0_DD09/M_A15   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 9 / EPROM Address pin 15  |

| 143   | C0_DD06         | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 6                         |

| 144   | C0_DD08/M_A16   | В    | 51 <b>Ω</b>                     | -                                             | Primary IDE Channel's Device Disk Data bit 8 / EPROM Address pin 16  |

| 145   | C0_DD07/M_A18   | В    | 51 $\Omega$                     | -/10 K $\Omega$                               | Primary IDE Channel's Device Disk Data bit 7 / EPROM Address pin 18  |

| 146   | V <sub>DD</sub> | Р    | -                               | -                                             | 3.3 Volts                                                            |

| 147   | C0_RESET#       | 0    | 51 $\Omega$                     | -                                             | Primary IDE Channel Disk Reset                                       |

| Pin # | Name            | Туре | External<br>Damping<br>Resistor | External<br>Pull Up/<br>Pull Down<br>Resistor | Description                                                                                       |

|-------|-----------------|------|---------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|

| 148   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                            |

| 149   | Reserved        | -    | -                               | -                                             | Do not connect                                                                                    |

| 150   | Reserved        | -    | -                               | -                                             | Do not connect                                                                                    |

| 151   | EN_PLL          | I    | -                               | -                                             | Enable PLL Test Pin                                                                               |

| 152   | Reserved        | -    | -                               | -                                             | Do not connect                                                                                    |

| 153   | PCI_INTA#       | O/D  | -                               | -                                             | Interrupt A is used to request an interrupt.                                                      |

| 154   | PCI_RST#        | I    | -                               | -                                             | Reset is used to bring all PCI specific registers, sequencers, and signals to a consistent state. |

| 155   | V <sub>SS</sub> | G    | -                               | -                                             | Ground                                                                                            |

| 156   | PCI_CLK         | I    | -                               | -                                             | Clock provides timing for all transaction on PCI and is an input to every PCI device.             |

| 157   | VSS_PLL         | G    | -                               | -                                             | Phase Locked Loop signal / Ground                                                                 |

| 158   | VCOIN_PLL       |      | -                               | -                                             | Phase Locked Loop signal / RC Circuit required                                                    |

| 159   | CPOUT_PLL       | 0    | -                               | -                                             | Phase Locked Loop signal / RC Circuit required                                                    |

| 160   | VDD_PLL         | Р    | -                               | -                                             | Phase Locked Loop signal / Power                                                                  |

**Notes:** The values for the damping, pull up and pull down resistors are taken from the ATA specification's recommendation. # following a signal name denotes an active low signal.

# **KEY TO PIN TYPE**

Each pin is assigned a type, which identifies the pin category as determined by the PCI specification. The types are as follows:

|   | Туре | Description                           |

|---|------|---------------------------------------|

|   | В    | Bi-directional Tri-state Input/Output |

|   |      | Input                                 |

| ( | 0    | Output                                |

| ( | O/D  | Open Drain                            |

| - | T/O  | Tri-state Output                      |

|   | G    | Ground                                |

|   | Р    | 3.3 Volts                             |

|   |      |                                       |

# Pin Descriptions (by category/alphabetical order)

# IDE/ATA Primary Channel

| Cable Detect  | Pin Names: C0_CBLID#<br>Pin Numbers: 116<br>C0_CBLID# (Cable Detect) determines the type of cable attached to the<br>primary channel. Drives using 80-pin cables will be allowed to transfer<br>data at a rate up to 100MB/sec; otherwise, the maximum data transfer<br>rate is 33 MB/sec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip Select   | Pin Names: C0_CS0#; C0_CS1#<br>Pin Numbers: 113, 111<br>C0_CS0# is the Drive Chip Select for Command Block Register Access<br>to the Primary Channel. C0_CS1# is the Drive Chip Select for Control<br>Block Register access to the Primary Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Disk Address  | Pin Names: C0_DA[20]<br>Pin Numbers: 114, 117, 115<br>Disk Address bits 0 through 2 are normally outputs to the ATA connector<br>selecting the register in the drive's Command Block register.<br>C0_DA[2::0] sends address signals to the primary channel. These<br>address signals are decoded from the AD[2::0] and C/BE[3::0] inputs.<br>All of these pins have internal pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Disk Data Bus | Pin Names: C0_DD[150]<br>Pin Numbers: 128, 130, 132, 135, 137, 139, 142, 144, 145, 143, 141, 138, 136, 134, 131, 129<br>Disk Data bits 0 through 15 are the 16-bit bi-directional data bus which connects to the IDE/ATA drive(s). C0_DD[15::0] are data signals to the primary Channel. C0_DD[7::0] defines the low byte while C0_DD[15::8] defines the high byte of this 16-bit data register. The data bus is normally in a high impedance state and is driven by the PCI-649 during the DIOW# command pulse in either single/multi-word DMA mode, or valid at every edge of C0_DIOR# (HSTROBE) or C0_IORDY (DSTROBE) in Ultra DMA mode. C0_DD07 is a multifunction pin which allows a host to recognize the absence of an ATA/ATAPI device at power-up. A 10K $\Omega$ pull down resistor is recomended to be connected to this pin. Variation in an ATA/ATAPI device may require that the designer change the resistor to 6.8K $\Omega$ on some systems. |

| Disk I/O Read     | Pin Name: C0_DIOR#<br>Pin Number: 124<br>Primary Channel Disk I/O Read is an active low output which enables<br>data to be read from the drive. The duration and repetition rate of<br>C0_DIOR# cycles is determined by PCI-649 programming. C0_DIOR# to<br>the primary channel is driven high when inactive. This signal is defined<br>as HSTROBE in Ultra DMA write mode to write data to the primary chan-<br>nel drive. This signal is also defined as primary channel HDMARDY# in<br>Ultra DMA read mode. |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disk I/O Write    | Pin Name: C0_DIOW#<br>Pin Number: 126<br>Primary Channel Disk I/O Write is an active low output that enables data<br>to be written to the drive. The duration and repetition of C0_DIOW#<br>cycles is determined by PCI-649 Programming. C0_DIOW# to the pri-<br>mary channel is driven high when inactive. This signal is defined as<br>primary channel STOP in ultra DMA mode.                                                                                                                               |

| DMA Acknowledge   | Pin Name: C0_DMACK#<br>Pin Number: 119<br>This signal is normally used by the PCI-649 in response to C0_DMARQ<br>to either acknowledge that the primary channel is ready to accept data,<br>or that data is available. This signal is also used to write CRC code to<br>the primary channel drive at the end of each Ultra DMA burst transfer.                                                                                                                                                                 |

| DMA Request       | Pin Name: C0_DMARQ<br>Pin Number: 127<br>This signal is used in a handshake manner with C0_DMACK#, and shall<br>be asserted high by the currently selected drive attached to the primary<br>IDE/ATA Channel when it is ready to transfer data to or from the host.                                                                                                                                                                                                                                             |

| Interrupt Request | Pin Name: C0_INTRQ<br>Pin Number: 118<br>Primary channel interrupt request is an input signal used to generate the<br>ISA_IRQ14 output when the primary IDE/ATA channel is in legacy mode.<br>When the primary IDE/ATA channel is in native mode, this pin generates<br>the PCI_INTA# Output. This input should have a $1k\Omega$ pull-down resistor<br>connected to it.                                                                                                                                       |

МĎ

| I/O Ready  | Pin Name: C0_IORDY<br>Pin Number:122<br>The Primary channel drive I/O ready is an active high input. It indicates<br>that the IDE/ATA disk drive has completed the current command cycle.<br>A 1k $\Omega$ pull-up resistor is recommended. This signal is defined as<br>DSTROBE in Ultra DMA read mode to read data from the currently<br>selected drive to the primary channel. This signal is also defined as<br>DDMARDY# in Ultra DMA write mode. |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disk Reset | Pin Name: C0_RESET#<br>Pin Number: 147<br>Disk Reset is an active low output which signals the IDE/ATA drive to ini-<br>tialize its control register. C0_RESET# is a buffered version of the<br>PCI_RST# input and can be generated by programming the PCI-649<br>register and connects directly to the ATA connector. C0_RESET#<br>asserts reset to the primary IDE/ATA channel.                                                                     |

| Interrupt  | Pin Name: ISA_IRQ14<br>Pin Number: 109<br>ISA_IRQ14 is used to generate an interrupt for primary IDE/ATA channel<br>in PCI IDE/ATA Legacy Mode (For PC-AT compatibles). ISA_IRQ14 is<br>tri-stated when IDE/ATA port 0 is in Native Mode.                                                                                                                                                                                                             |

# IDE/ATA Secondary Channel

| Cable Detect | Pin Names: C1_CBLID#<br>Pin Number: 76<br>C1_CBLID# (Cable Detect) determines the type of cable attached to the<br>secondary channel. Attached drives using 80-pin cables will be allowed<br>to transfer data at a rate up to 100MB/sec; otherwise, the maximum data<br>transfer rate is 33 MB/sec. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip Select  | Pin Names: C1_CS0#; C1_CS1#<br>Pin Numbers: 73, 72<br>C1_CS0# is the Drive Chip Select for Command Block Register access<br>to the Secondary Channel's master drive. C1_CS1# is the Drive Chip<br>Select for Control Block Register access to the Secondary Channel's<br>slave drive.               |

| Disk Address   | Pin Names: C1_DA[20]<br>Pin Numbers: 74, 77, 75<br>Disk Address bits 0 through 2 are normally outputs to the ATA connector<br>to select the register in the drive's Command Block register. C1_DA<br>[20] sends address signals to the secondary channel. These address<br>signals are decoded from the AD[2::0] and C/BE[3::0] inputs. All of<br>these pins have internal pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |