# National Semiconductor

**Preliminary**

May 2004 Revision 1.1

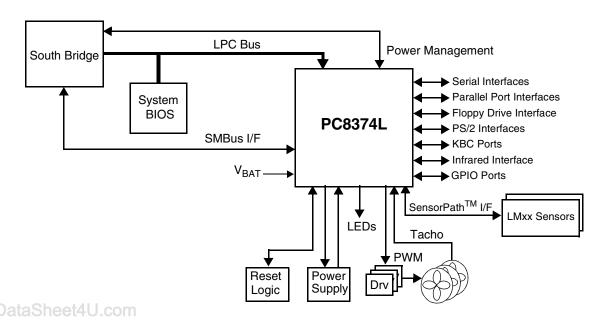

# PC8374L SensorPath™ SuperI/O with Glue Functions

# **General Description**

The National Semiconductor PC8374L Advanced I/O product is a member of the PC837x SuperI/O family. All PC837x devices are highly integrated and are pin and software compatible, thus providing drop-in interchangeability and enabling a variety of assembly options using only a single motherboard and BIOS.

PC8374L integration allows for a smaller system board size and saves on total system cost.

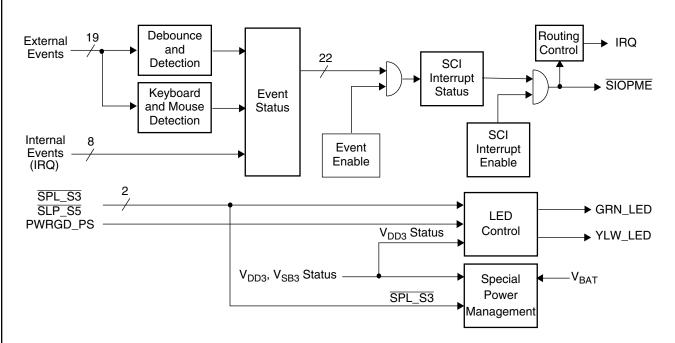

The PC8374L includes legacy Superl/O functions, system glue functions, health monitoring and control, commonly used functions such as GPIO, and ACPI-compliant Power Management support.

The PC8374L integrates miscellaneous analog and digital system glue functions to reduce the number of discrete components required. The host communicates with the functions integrated in the PC8374L device through an LPC Bus Interface.

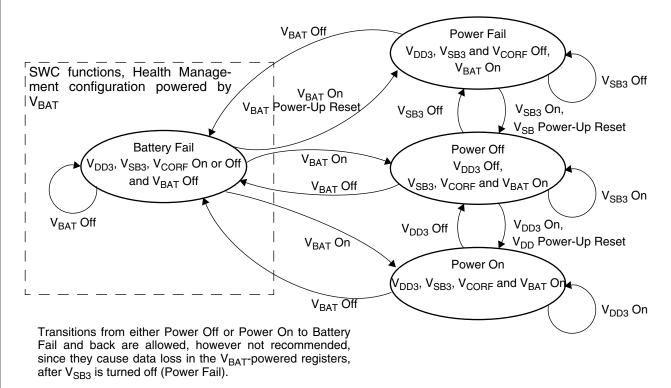

The PC8374L extended wake-up support complements the ACPI controller in the chipset. The System Wake-Up Control (SWC) module, powered by  $V_{SB3}$ , supports a flexible wake-up mechanism.

The PC8374L supports both I/O and memory mapping of module registers and enables building legacy-free systems.

# **Outstanding Features**

- SensorPath<sup>™</sup> interface to LMxx sensor devices for system health support

- Fan monitor and control

- Heceta6-compatible register set, accessible via the LPC interface and SMBus

- Glue functions to complement the South Bridge functionality

- V<sub>SB3</sub>-powered Power Management with 19 wake-up sources

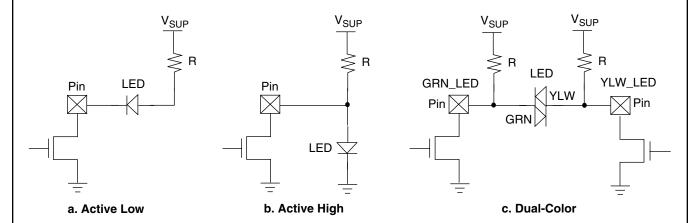

- Controls three LED indicators

- 16 GPIO ports with a variety of wake-up options

- I/O-mapped and memory-mapped registers

- Legacy modules: Parallel Port, Floppy Disk Controller (FDC), two Serial Ports, Slow InfraRed Port and a Keyboard and Mouse Controller (KBC)

- LPC interface, based on Intel's LPC Interface Specification Revision 1.1, August 2002

- PC01 Revision 1.0 and Advanced Configuration and Power Interface (ACPI) Specification Revision 2.0 compliant

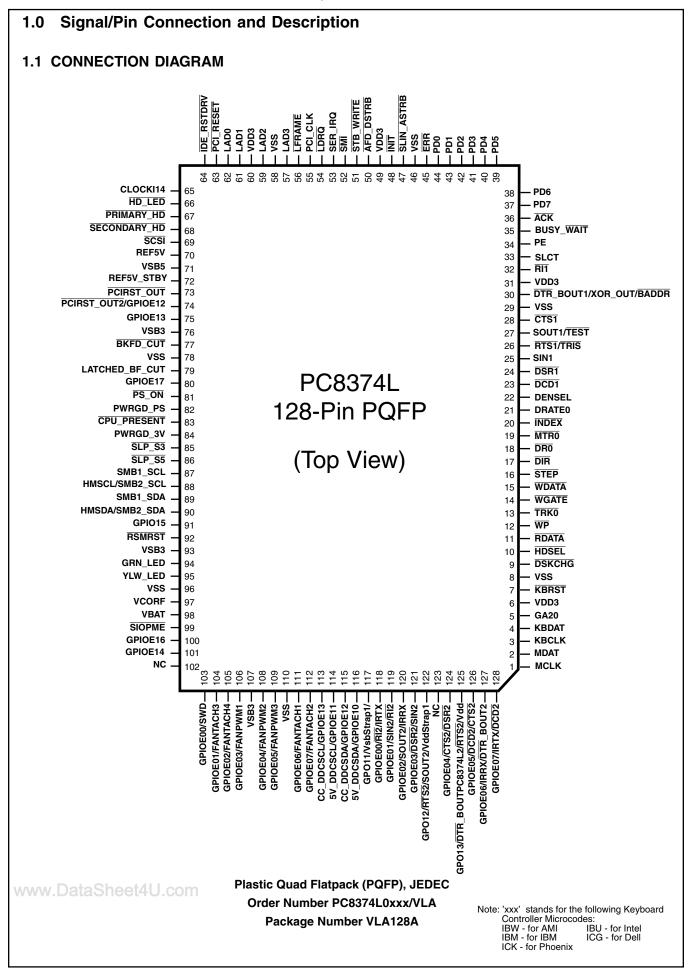

- 128-pin PQFP package

# **Block Diagram**

National Semiconductor and TRI-STATE® are registered trademarks of National Semiconductor Corporation. SensorPath® is a trademark of National Semiconductor Corporation.

All other brand or product names are trademarks or registered trademarks of their respective holders.

#### **Features**

#### System Health Support

- SensorPath interface to sensors optimizes digital/analog partitioning

- Simplifies board design and routing

- Supports distributed sensors and centralized control

- Health monitoring is self-contained and requires minimal host attention

- Faster boot time

- Off loads SMBus, and enables ASF compliance

- Fan Monitor and Control

- Three PWM-based fan controls

- Four 16-bit resolution tachometer inputs

- Software or local temperature feedback control

- Heceta6-compatible register set accessible via the LPC interface and SMBus

- Supports the following combinations of LMxx devices:

- □ LM96011 and optional LM95010

- □ LM96012

- □ LM96010

- Simultaneous read support via LPC interface and SMBus

#### **Glue Functions**

- Generates the power-related signals:

- Main Power good

- Power distribution control (for switching between Main and Standby regulators)

- Resume reset (Master Reset) according to the 5V standby supply status

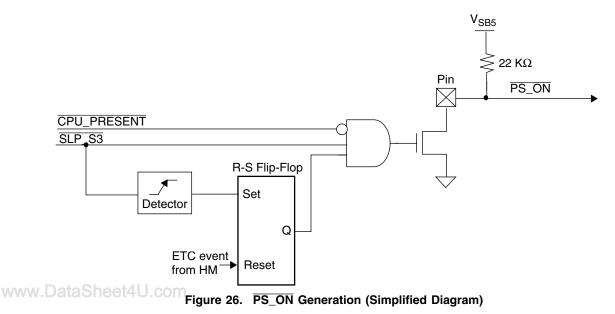

- Main power supply turn on (PS\_ON)

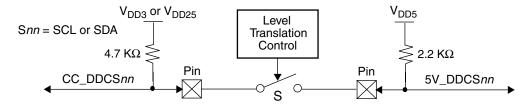

- Voltage translation between 2.5V or 3.3V levels (DDC) and 5V levels (VGA) for the SMBus serial clock and data signals

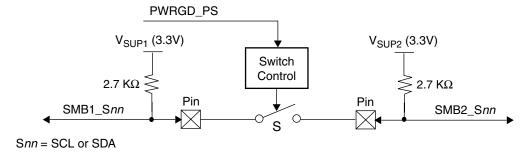

- Isolation circuitry for the SMBus serial clock and data signals

- Buffers PCI\_RESET to generate two reset output signals

- Buffers PCI\_RESET to generate IDE reset output.

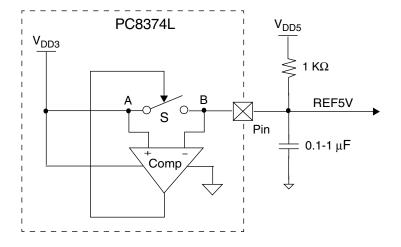

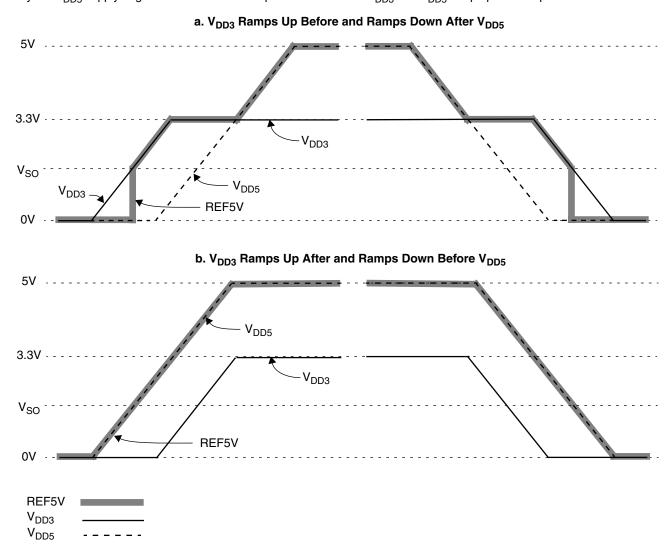

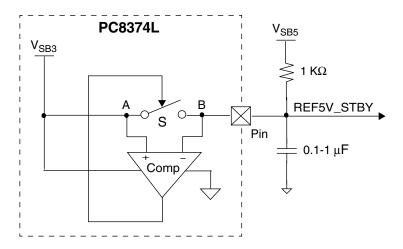

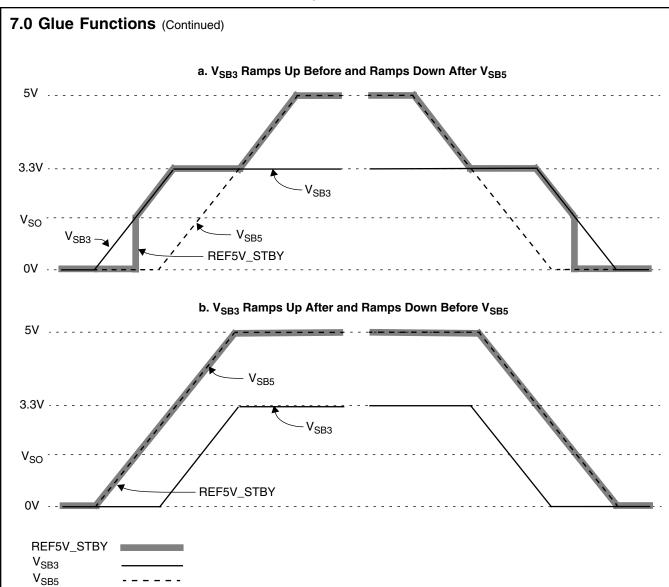

- Generates "highest active supply" reference voltage

- Based on 3.3V and 5V Main supplies

- Based on 3.3V and 5V Standby supplies

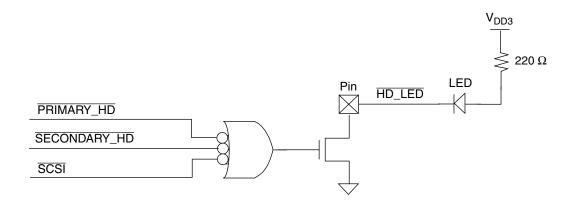

- High-current LED driver control for Hard Disk Drive activity indication

- Software selectable alternative functionality, through pin multiplexing

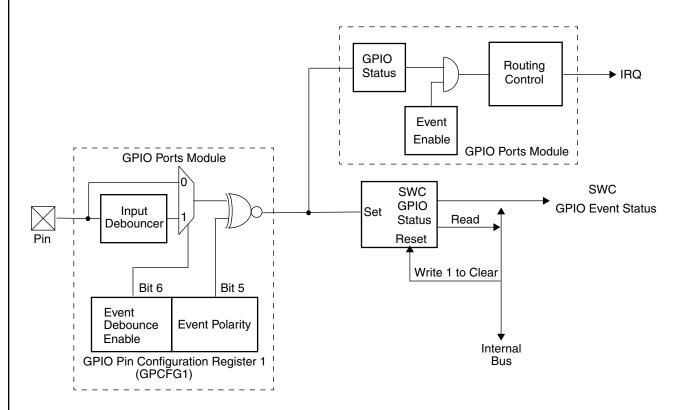

#### General-Purpose I/O (GPIO) Ports

- All 16 GPIO ports powered by V<sub>SB3</sub>

- Each pin individually configured as input or output

- Programmable features for each output pin:

- Drive type (open-drain, push-pull or TRI-STATE<sup>®</sup>)

- TRI-STATE on detection of falling V<sub>DD3</sub> for V<sub>SB3</sub>-powered pins driving V<sub>DD</sub>-supplied devices

- Programmable option for internal pull-up resistor on each input pin (some with internal pull-down resistor option)

- Lock option for the configuration and data of each output pin

- 15 GPIO ports generate IRQ/SIOPME for wake-up events; each GPIO has separate:

- Enable control of event status routing to IRQ

- Enable control of event status routing to SIOPME (via SWC)

- Polarity and edge/level selection

- Programmable debouncing

#### **Power Management**

- Supports ACPI Specification Revision 2.0b, July 27, 2000

- System Wake-Up Control (SWC)

- Optional routing of events to generate SCI (SIOPME) on detection of:

- Keyboard or Mouse events

- $\Box$  Ring Indication  $\overline{RI}$  on each of the two serial ports

- □ General-Purpose Input Events from 15 GPIO pins

- □ IRQs of the Keyboard and Mouse Controller

- IRQs of the other internal modules

- Optional routing of the SCI (SIOPME) to generate IRQ (SERIRQ)

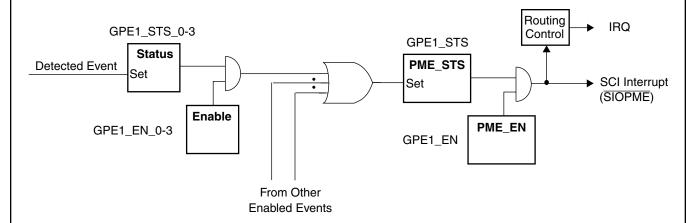

- Implements the GPE1\_BLK of the ACPI General Purpose (Generic) Register blocks with "child" events

- V<sub>SB3</sub>-powered event detection and event-logic configuration

- Enhanced Power Management (PM), including:

- Special configuration registers for power down

- Low-leakage pins

- Low-power CMOS technology

- Ability to disable all modules

- High-current LED drivers control (two LEDs) for power status indication with:

- Standard blinking, controlled by software

- Advanced blinking, controlled by power supply status, sleep state or software

- Special blinking, controlled by power supply status, sleep state and software bit

- V<sub>BAT</sub>-powered indication of the Main power supply state before an AC power failure

- Keyboard Events

- Wake-up on any key

- Supports programmable 8-byte sequence "Password" or "Special Keys" for Power Management

- Simultaneous recognition of three programmable keys (sequences): "Power", "Sleep" and "Resume"

- Wake-up on mouse movement and/or button click

#### **Bus Interface**

- LPC Bus Interface

- Based on Intel's LPC Interface Specification Revision 1.1, August 2002

- I/O, Memory and 8-bit Firmware Memory read and write cycles

- Up to four 8-bit DMA channels

- Serial IRQ (SERIRQ)

- Supports registers memory and I/O mapping

#### Features (Continued)

- Configuration Control

- PnP Configuration Register structure

- PC01 Specification Revision 1.0, 1999-2000 compliant

- Base Address strap (BADDR) to setup the address of the Index-Data register pair (defaults to 2Eh/2Fh)

- Flexible resource allocation for all logical devices:

- Relocatable base address

- 15 IRQ routing options to serial IRQ

- Up to four optional 8-bit DMA channels

- Configurable feature sets:

- Software selectable

- V<sub>SB3</sub>-powered pin multiplexing

#### **Legacy Modules**

- Serial Ports 1 and 2

- Software-compatible with the NS16550A and NS16450

- Support shadow register for write-only bit monitoring

- Data rates up to 1.5 Mbaud

- Serial Infrared Port (SIR)

- Software compatible with the 16550A and the 16450

- Shadow register support for write-only bit monitoring

- HP-SIR

- ASK-IR option of SHARP-IR

- DASK-IR option of SHARP-IR

- Consumer Remote Control supports RC-5, RC-6, NEC, RCA and RECS 80

- IEEE 1284-compliant Parallel Port

- ECP, with Level 2 (14 mA sink and source output buffers)

- Software or hardware control

- Enhanced Parallel Port (EPP) compatible with EPP 1.7 and EPP 1.9

- Supports EPP as mode 4 of the Extended Control Register (ECR)

- Selection of internal pull-up or pull-down resistor for Paper End (PE) pin

- Supports a demand DMA mode mechanism and a DMA fairness mechanism for improved bus utilization

- Protection circuit that prevents damage to the parallel port when a printer connected to it is powered up or is operated at high voltages (in both cases, even if the PC8374L is in power-down state)

- Floppy Disk Controller (FDC)

- Software compatible with the PC8477 (the PC8477 contains a superset of the FDC functions in the μDP8473, NEC μPD765A/B and N82077 devices)

- Error-free handling of data overrun and underrun

- Programmable write protect

- Supports FM and MFM modes

- Supports Enhanced mode command for three-mode Floppy Disk Drive (FDD)

- Perpendicular recording drive support for 2.88 MBytes

- Burst (16-byte FIFO) and Non-Burst modes

- Full support for IBM Tape Drive Register (TDR) implementation of AT and PS/2 drive types

- High-performance digital separator

- Supports fast tape drives (2 Mbps) and standard tape drives (1 Mbps, 500 Kbps and 250 Kbps)

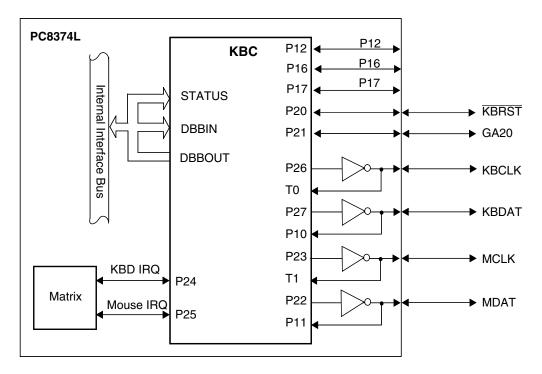

- Keyboard and Mouse Controller (KBC)

- 8-bit microcontroller, software compatible with 8042AH and PC87911

- Standard interface (60h, 64h, IRQ1 and IRQ12)

- Supports two external swapable PS/2 interfaces for keyboard and mouse

- Programmable, dedicated quasi-bidirectional I/O lines (GA20/P21, KBRST/P20)

## Clocking, Supply, and Package Information

- Clocks

- LPC (PCI) clock input (up to 33 MHz)

- On-chip Clock Generator:

- □ Generates 48 MHz clock

- ☐ Generates 32.768 KHz internal clock

- V<sub>SB3</sub> powered

- □ Based on the 14.31818 MHz clock input

- Protection

- All pins are 5V tolerant and back-drive protected (except LPC bus pins)

- High ESD protection of all the pins

- Pin multiplexing selection lock

- Configuration register lock

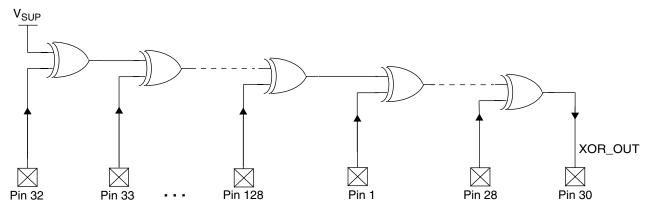

- Testability

- XOR tree structure

- Includes all the pins (except supply, analog and not connected pins)

- □ Selected at power-up by strap input (TEST)

- TRI-STATE pins, selected at power-up by strap input (TRIS)

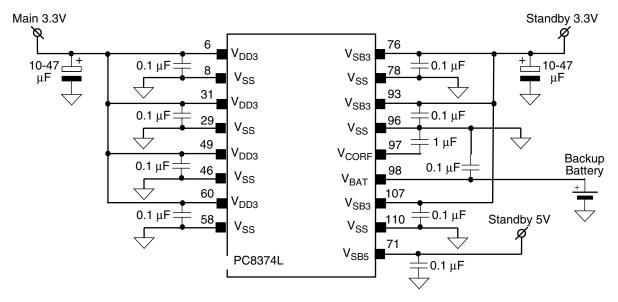

- Power Supply

- 3.3V supply operation

- Separate pin pairs for main (V<sub>DD3</sub>) and standby (V<sub>SB3</sub>) power supplies

- Backup battery input (V<sub>BAT</sub>) for SWC indications

- Low standby power consumption

- Very low power consumption from backup battery (less than 0.5 μA)

- Package

- 128-pin PQFP

# **Revision Record**

| <b>Revision Date</b> | Status              | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 17, 2003       | Draft Revision 0.03 | First Draft of Arch. Spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| April 15, 2003       | Draft Revision 0.1  | Add Serial InfraRed Port<br>Update all sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| June 7, 2003         | Draft Revision 0.3  | Change Clock generator and CLOCKCF register Add Heceta6 Emulation module and complementing configuration registers: H6_SMBCF, SIOCFB, and its logical device (LDN=08h) configuration registers Define ETC (Enhanced Thermal Control) behavior Change DC spec of GPIOE10-13 Add IN <sub>TS2</sub> buffer type Correct LPCPD timing Correct LPCPD timing Correct LPC t <sub>VAL</sub> Rename the following functions: GPO24 to GPO41, GPIOE25 to GPIOE24, GPIOE26 to GPIOE25, GPIOE27 to GPIOE26 Change in GPCFG2 register Correct memory map support for SWC Typos and clarifications                                                                                                                                                                                                                      |

| June 22, 2003        | Draft Revision 0.5  | Rename Port Angeles 3 to PC87374L Rename 3V_DDCSCL, 3V_DDCSDA to CC_DDCSCL, CC_DDCSDA Support 2.5V SMBus on CC_DDCSnn pins Update Clock Domains Section, changes in CLOCKCF register, High-Frequency Clock Timing, Low-Frequency Clock Timing SIOCFB register is changed to be powered by V <sub>BAT</sub> Register 61h for LDN=08h: H6_LPC_EMUL is changed Hecteta6 Emulation: changed Table 62, changed Tachometer Reading registers Changed FMC Registers: FT_CTL, FT_LOW, FT_HYST and FT_RNG Change SOUT2 buffer type to O <sub>4/8</sub> Added XOR Tree delay Update AC spec: V <sub>SB</sub> Power-Up reset, V <sub>DD</sub> Power-Up reset, Main Power Good, Resume Reset, PS_ON Add Power Consumption numbers Add SMBus timing, InfraRed Port timing Typos and clarifications                     |

| August 2, 2003       | Draft Revision 0.6  | Remove HMC and FMC modules Remove SCK_BJT_GATE, LPCPD, GPIOE15, GPIOE26-20, GPIO37-30, GPO41-40 signals Pins 52, 102, 123 are NC (Not Connected) Allow multiple pin locations for GPIO signals and rename pins with GPIOs, change default PU/PD, allow routing of a GPIOE input to a GPIO output Removed SIOCFB register SIOCF4[2:1], CLOCKCF[0] are reserved, change in SIOCF3[1:0], SIOCF4[5:3] Change drive capability of GPIOE00 (on pin 118) and GPIOE07 (on pin 128) Change PWRGD_3V functionality Rename PC87374L to PC8374L Rename Heceta 6 Emulation to Health Management H6_SCL and H6_SDA pins renamed to HMSCL and HMSDA pins, respectively VBAT pin should be connected to VSB3 (and not VSS), when battery backup features are unused LED mode selection is not dependent on VBAT existence |

| ww.DataSneet         | 4U.com              | LED mode selection is not dependent on V <sub>BAT</sub> existence Typos and clarifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# Revision Record (Continued)

| Revision Date     | Status                   | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 12, 2003   | Draft Revision 0.7       | Change PWRGD_3V functionality Add details to SERIAL PORT 2 (SP2) WITH INFRARED Section Change in HMSMBCF register Typos and clarifications Health Management: Added support for more LMxx devices - see overview Section 9.2.2 - added a table of temp channel association. New HM registers: Status Register 3-4, Monitoring Control, Extended FANPWM Control 1-2, Tachometer Monitoring Control, Channels Vdd configuration, Temp Critical Limit Zone1- 3,Temp Zone1-3 Gain and Offset Correction. New HM LPC registers:HMINT_STS3, HMINT_EN#, HMSENS_STS3, HMS_EN1-3, SMI/SCI_ROUT. Functional description updated. Temp Reading registers updated. |

| October 13, 2003  | Draft Revision 0.8       | Maximum PWM duty cycle, Fans setting time to the maximum duty cycle, Changed default mode of LED control Correct Table 3 on page 18 Rename LMxx sensor device Removed FPRST Changed reset value of FANTACH registers to FF Changed reset value of FANOFF to 1 Added Package Thermal Information Typos and clarifications                                                                                                                                                                                                                                                                                                                               |

| November 20, 2003 | Preliminary Revision 0.9 | <ul> <li>Changes to the Health Management Chapter</li> <li>Device Characteristics: Minimum value of t<sub>CH</sub>, t<sub>CL</sub> reduced to 20 ns</li> <li>Typos and Clarifications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| February 3, 2004  | Preliminary Revision 1.0 | <ul> <li>Added LM sensor devices</li> <li>Changed V<sub>BAT</sub> external capacitor requirement to 1 μF</li> <li>Typos and Clarifications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| May 2004          | Preliminary Revision 1.1 | <ul> <li>Glue Functions: Removed 2.5V voltage divider circuit for SM-<br/>Bus Voltage Translation system diagram</li> <li>Typos and Clarifications</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

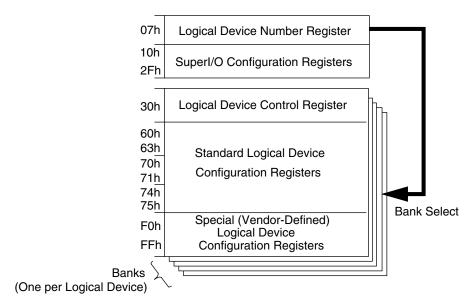

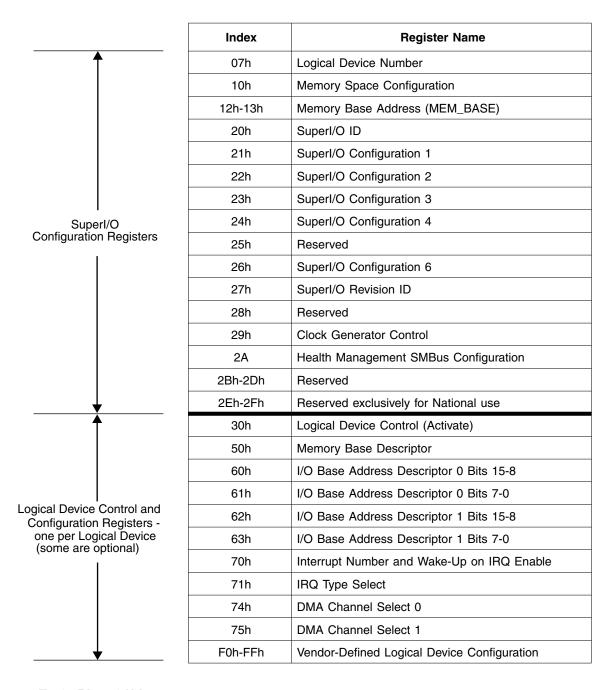

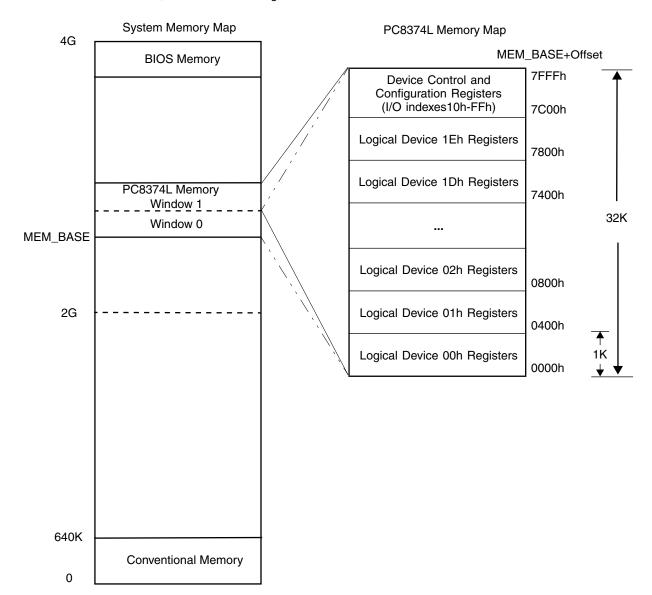

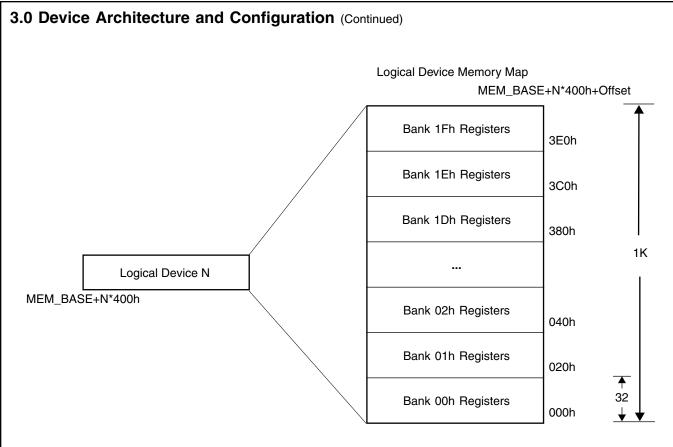

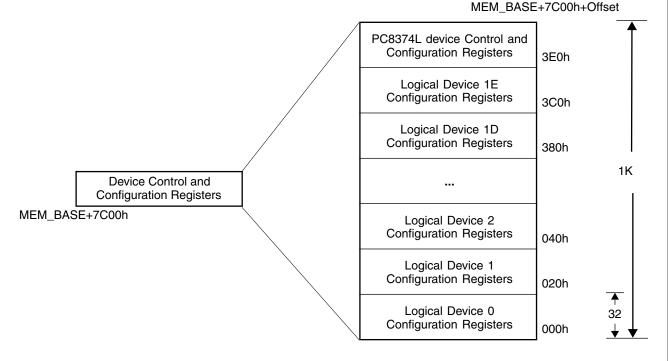

#### Table of Contents Features 2 **Revision Record** 4 Signal/Pin Connection and Description 1.2 1.3 DETAILED SIGNAL/PIN DESCRIPTIONS ......21 1.4 1.4.2 Serial Port 1 and Serial Port 2 (UART1 and UART2) ......21 1.4.3 1.4.4 1.4.5 Keyboard and Mouse Controller (KBC) ......24 1.4.6 1.4.7 General-Purpose I/O (GPIO) ......24 1.4.8 Health Management (HM) ......25 1.4.9 System Wake-Up Control (SWC) ......25 1.4.10 1.4.11 1.4.12 Configuration Straps and Testing .......28 1.4.13 1.5 **Power. Reset and Clocks** 2.0 2.1 Power Planes 32 2.1.1 2.1.2 2.1.3 RESET SOURCES AND TYPES ......34 2.2 V<sub>RAT</sub> Power-Up Reset .......35 2.2.1 2.2.2 VSB Power-Up Reset ......35 2.2.3 2.2.4 2.2.5 2.3 2.3.1 2.3.2 2.3.3 2.4 2.4.1 2.4.2 3.0 **Device Architecture and Configuration** 3.1 CONFIGURATION STRUCTURE AND ACCESS .......38 3.2

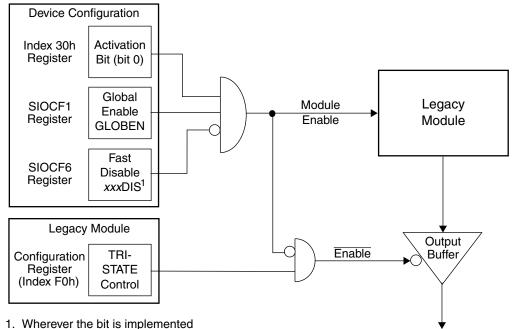

#### Table of Contents (Continued) 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 Default Configuration Setup .......43 3.2.6 3.3 3.3.1 3.3.2 Floating Module Output ......48 3.4 3.5 PROTECTION ......50 3.5.1 3.5.2 GPIO Ports Configuration Lock .......50 3.5.3 3.5.4 3.5.5 Health Management Configuration Lock .......50 3.5.6 3.5.7 REGISTER TYPE ABBREVIATIONS ......51 3.6 PC8374L CONFIGURATION REGISTERS .......52 3.7 Memory Mapping Control Register (MEMMAP) ......52 3.7.1 3.7.2 Memory Base Address Register 1 (MEMADR1) ......53 Memory Base Address Register 2 (MEMADR2) ......53 3.7.3 3.7.4 SuperI/O ID Register (SID) ......53 3.7.5 SuperI/O Configuration 1 Register (SIOCF1) ......54 3.7.6 SuperI/O Configuration 2 Register (SIOCF2) ......55 SuperI/O Configuration 3 Register (SIOCF3) ......56 3.7.7 3.7.8 SuperI/O Configuration 4 Register (SIOCF4) ......57 SuperI/O Configuration 6 Register (SIOCF6) ......57 3.7.9 3.7.10 SuperI/O Revision ID Register (SRID) ......58 Clock Generator Control Register (CLOCKCF) ......59 3.7.11 Health Management SMBus Configuration (HMSMBCF) Register ......59 3.7.12 FLOPPY DISK CONTROLLER (FDC) CONFIGURATION ......60 3.8 3.8.1 General Description ......60 Logical Device 0 (FDC) Configuration ......60 3.8.2 3.8.3 FDC Configuration Register ......61 3.8.4 PARALLEL PORT (PP) CONFIGURATION ......63 3.9 General Description ......63 3.9.1 3.9.2 Parallel Port Standard Configuration Register ......64 3.9.3 3.9.4 Parallel Port Modified Configuration Register .......65 3.10.1 Logical Device 2 (SP2) Configuration ......66 3.10.2

| Tabl | e of C | Contents (Continued)                                              |    |

|------|--------|-------------------------------------------------------------------|----|

|      |        | 3.10.3 Serial Port 2 Configuration 1 Register                     | 67 |

|      | 3.11   | SERIAL PORT 1 CONFIGURATION                                       | 68 |

|      |        | 3.11.1 General Description                                        | 68 |

|      |        | 3.11.2 Logical Device 3 (SP1) Configuration                       | 68 |

|      |        | 3.11.3 Serial Port 1 Configuration Register                       | 69 |

|      | 3.12   | SYSTEM WAKE-UP CONTROL (SWC) CONFIGURATION                        | 70 |

|      |        | 3.12.1 General Description                                        |    |

|      |        | 3.12.2 Logical Device 4 (SWC) Configuration                       | 70 |

|      | 3.13   | KEYBOARD AND MOUSE CONTROLLER (KBC) CONFIGURATION                 | 71 |

|      |        | 3.13.1 General Description                                        | 71 |

|      |        | 3.13.2 Logical Devices 5 and 6 (Mouse and Keyboard) Configuration | 71 |

|      |        | 3.13.3 KBC Configuration Register                                 | 72 |

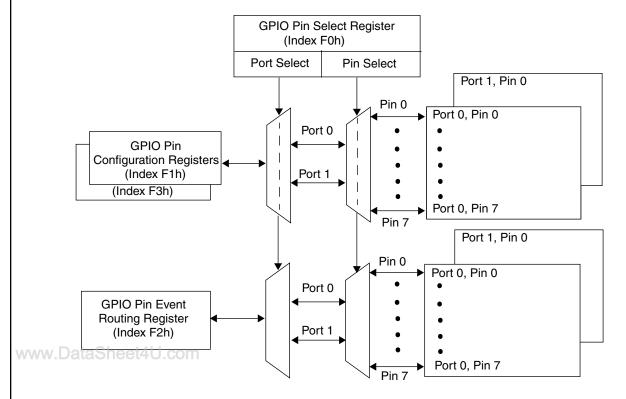

|      | 3.14   | GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORTS CONFIGURATION           | 73 |

|      |        | 3.14.1 General Description                                        | 73 |

|      |        | 3.14.2 Logical Device 7 (GPIO) Configuration                      | 74 |

|      |        | 3.14.3 GPIO Pin Select Register (GPSEL)                           | 75 |

|      |        | 3.14.4 GPIO Pin Configuration Register 1 (GPCFG1)                 | 75 |

|      |        | 3.14.5 GPIO Event Routing Register (GPEVR)                        | 77 |

|      |        | 3.14.6 GPIO Pin Configuration Register 2 (GPCFG2)                 | 77 |

|      |        | 3.14.7 GPIO Mode Select Register (GPMODE)                         | 78 |

|      | 3.15   | HEALTH MANAGEMENT (HM) CONFIGURATION                              | 79 |

|      |        | 3.15.1 General Description                                        | 79 |

|      |        | 3.15.2 Logical Device 8 (HM) Configuration                        | 79 |

|      |        | 3.15.3 Health Management Configuration Register 1 (HMCFG1)        | 79 |

| 4.0  | Syst   | tem Wake-Up Control (SWC)                                         |    |

|      | 4.1    | OVERVIEW                                                          | 81 |

|      | 4.2    | FUNCTIONAL DESCRIPTION                                            | 82 |

|      |        | 4.2.1 External Events                                             | 82 |

|      |        | 4.2.2 Internal Events                                             | 85 |

|      |        | 4.2.3 Sleep States                                                | 86 |

|      |        | 4.2.4 SCI and IRQ Interrupts                                      |    |

|      |        | 4.2.5 LED Control                                                 |    |

|      |        | 4.2.6 Special Power Management Functions                          | 89 |

|      | 4.3    | SWC REGISTERS                                                     |    |

|      |        | 4.3.1 SWC Register Map                                            |    |

|      |        | 4.3.2 Standard LED Control Register (SLEDCTL)                     |    |

|      |        | 4.3.3 SWC Miscellaneous Control Register (SWC_CTL)                |    |

|      |        | 4.3.4 Advanced LED Control Register (ALEDCTL)                     |    |

|      |        | 4.3.5 Special LED Control Register (XLEDCTL)                      |    |

|      |        | 4.3.6 LED Blink Control Register (LEDBLNK)                        |    |

|      |        | 4.3.7 Keyboard Wake-Up Control Register (KBDWKCTL)                |    |

| WWW  | .Data  | 4.3.8 4 PS2 Protocol Control Register (PS2CTL)                    |    |

|      |        | 4.3.9 Keyboard Data Shift Register (KDSR)                         |    |

|      |        | 4.3.10 Mouse Data Shift Register (MDSR)                           | 98 |

|      |        |                                                                   |    |

| Tabl | e of C | Contents (Continued)                                      |     |

|------|--------|-----------------------------------------------------------|-----|

|      |        | 4.3.11 PS2 Keyboard Key Data 0 to 7 Registers (PS2KEY0-7) | 98  |

|      | 4.4    | ACPI REGISTERS                                            | 99  |

|      |        | 4.4.1 ACPI Register Map                                   | 99  |

|      |        | 4.4.2 General-Purpose Status 1 Register (GPE1_STS)        | 100 |

|      |        | 4.4.3 General-Purpose Enable 1 Register (GPE1_EN)         | 100 |

|      |        | 4.4.4 General-Purpose Status 1 Register 0 (GPE1_STS_0)    | 101 |

|      |        | 4.4.5 General-Purpose Status 1 Register 1 (GPE1_STS_1)    |     |

|      |        | 4.4.6 General-Purpose Status 1 Register 2 (GPE1_STS_2)    |     |

|      |        | 4.4.7 General-Purpose Status 1 Register 3 (GPE1_STS_3)    |     |

|      |        | 4.4.8 General-Purpose Enable 1 Register 0 (GPE1_EN_0)     |     |

|      |        | 4.4.9 General-Purpose Enable 1 Register 1 (GPE1_EN_1)     |     |

|      |        | 4.4.10 General-Purpose Enable 1 Register 2 (GPE1_EN_2)    |     |

|      |        | 3 (- = =)                                                 |     |

|      | 4.5    | SYSTEM WAKE-UP CONTROL REGISTER BITMAP                    | 107 |

| 5.0  | LPC    | Bus Interface                                             |     |

|      | 5.1    | OVERVIEW                                                  | 109 |

|      | 5.2    | LPC TRANSACTIONS                                          | 109 |

|      | 5.3    | INTERRUPT SERIALIZER                                      | 109 |

| 6.0  | Gene   | eral-Purpose Input/Output (GPIO) Ports                    |     |

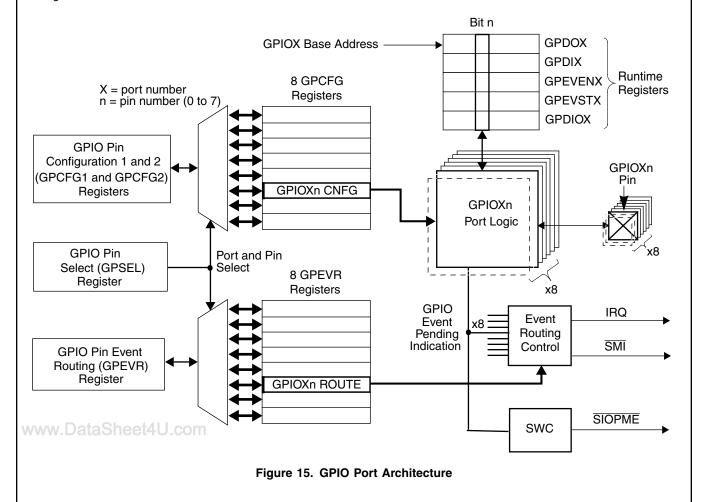

|      | 6.1    | OVERVIEW                                                  | 110 |

|      | 6.2    | BASIC FUNCTIONALITY                                       | 111 |

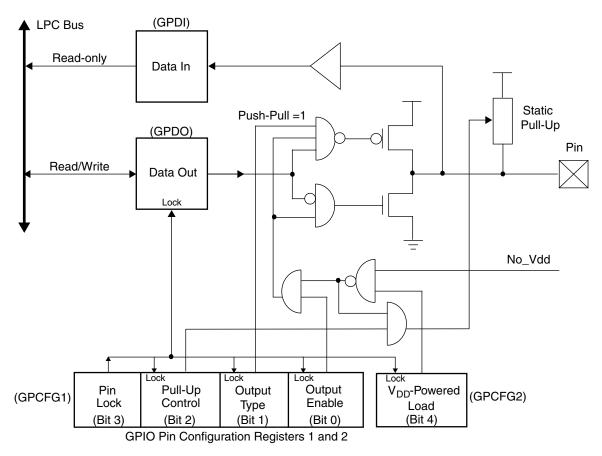

|      |        | 6.2.1 Configuration Options                               |     |

|      |        | 6.2.2 Operation                                           | 112 |

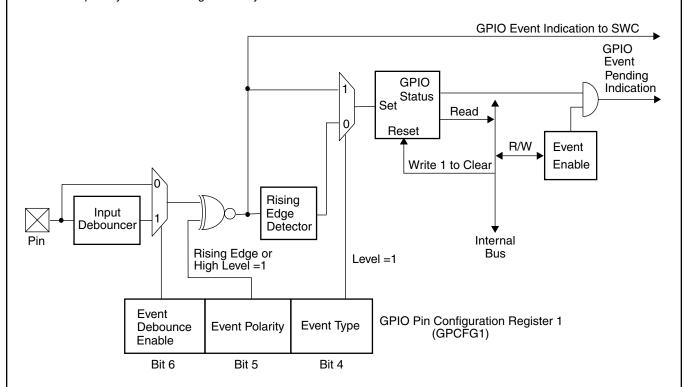

|      | 6.3    | EVENT HANDLING AND SYSTEM NOTIFICATION                    | 113 |

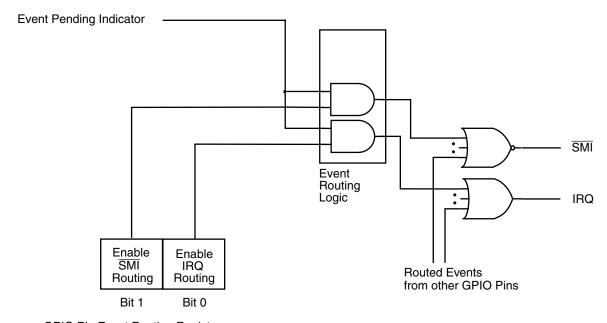

|      |        | 6.3.1 Event Configuration                                 | 113 |

|      |        | 6.3.2 System Notification                                 | 114 |

|      | 6.4    | GPIO PORT REGISTERS                                       | 115 |

|      |        | 6.4.1 GPIO Pin Configuration Registers Structure          | 115 |

|      |        | 6.4.2 GPIO Port Runtime Register Map                      | 115 |

|      |        | 6.4.3 GPIO Data Out Register (GPDO)                       |     |

|      |        | 6.4.4 GPIO Data In Register (GPDI)                        |     |

|      |        | 6.4.5 GPIO Event Enable Register (GPEVEN)                 |     |

|      |        | 6.4.6 GPIO Event Status Register (GPEVST)                 |     |

|      |        | 6.4.7 GPIO Data In/Out Register (GPDIO)                   | 117 |

| 7.0  | Glue   | e Functions                                               |     |

|      | 7.1    | OVERVIEW                                                  | 118 |

|      | 7.2    | FUNCTIONAL DESCRIPTION                                    | 118 |

|      |        | 7.2.1 Highest Active Main Supply Reference                |     |

|      |        | 7.2.2 Highest Active Standby Supply Reference             |     |

| WWW  | .Data  | 7.2.3 Resume Reset                                        |     |

|      |        | 7.2.4 Main Power Good                                     |     |

|      |        | 7.2.5 Power Distribution Control                          |     |

|      |        | 7.2.6 Main Power Supply Control                           | 124 |

| Tabl | e of C | Contents (Continued)                                     |     |

|------|--------|----------------------------------------------------------|-----|

|      |        | 7.2.7 Hard-Disk LED Indicator Control                    | 125 |

|      |        | 7.2.8 SMBus Voltage Translation                          | 125 |

|      |        | 7.2.9 SMBus Isolation                                    | 126 |

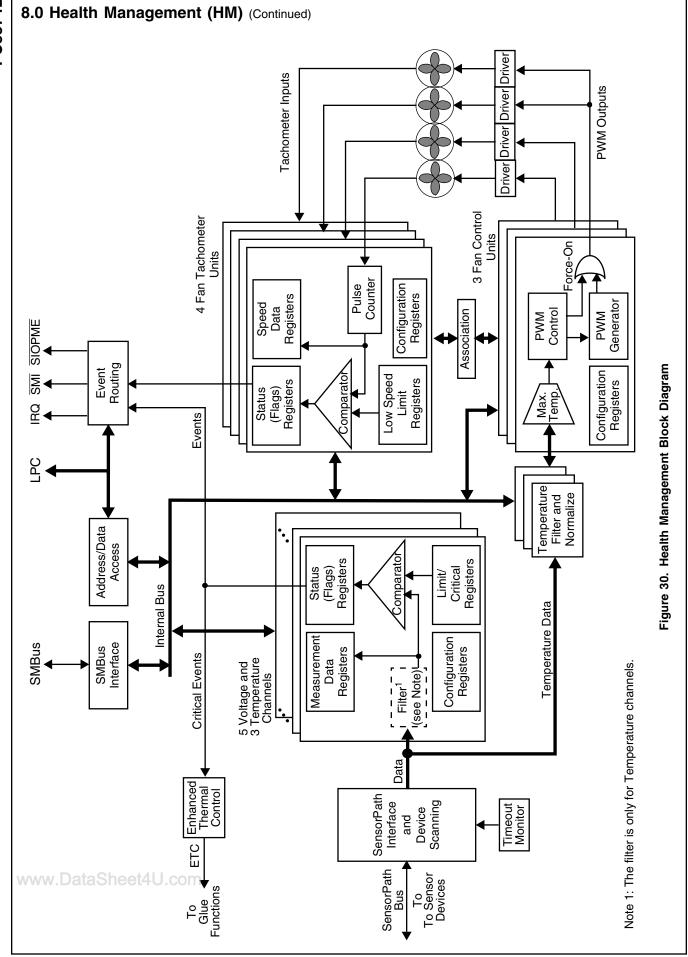

| 8.0  | Heal   | Ith Management (HM)                                      |     |

|      | 8.1    | OVERVIEW                                                 | 127 |

|      | 8.2    | FUNCTIONAL DESCRIPTION                                   | 127 |

|      |        | 8.2.1 Health Management Module Access                    | 127 |

|      |        | 8.2.2 SensorPath Bus                                     | 127 |

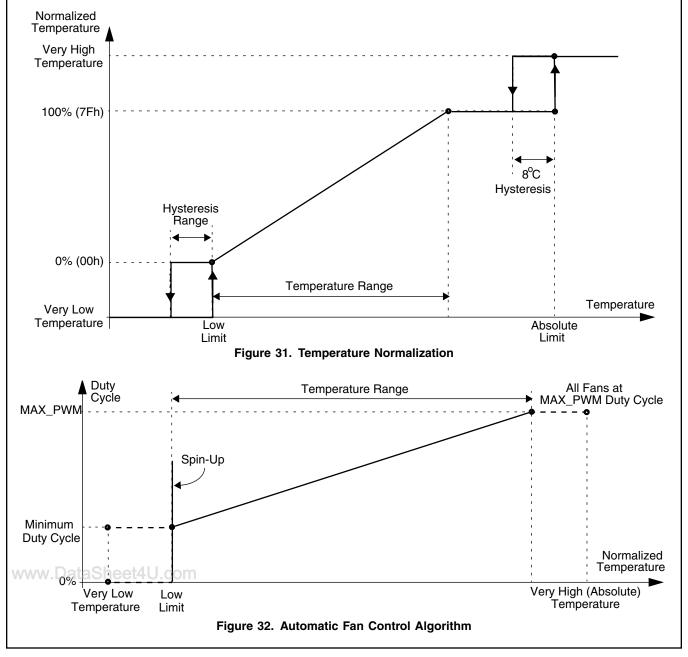

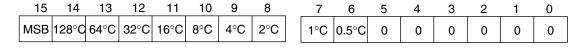

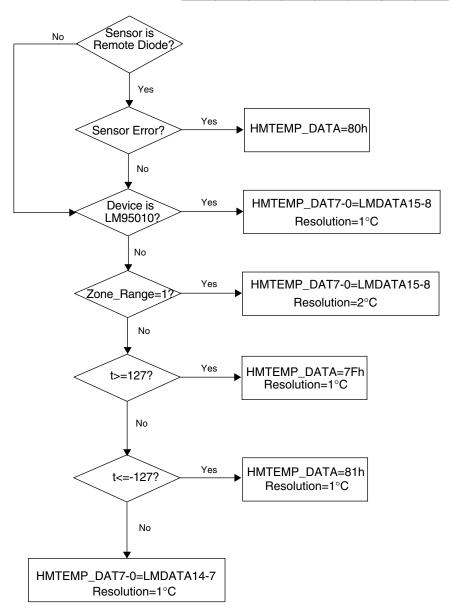

|      |        | 8.2.3 Temperature Monitoring                             | 129 |

|      |        | 8.2.4 Voltage Monitoring                                 |     |

|      |        | 8.2.5 Device Enumeration and HM Channel Association      | 130 |

|      |        | 8.2.6 SensorPath Device Setting and Scanning             |     |

|      |        | 8.2.7 Fan Speed Monitoring                               |     |

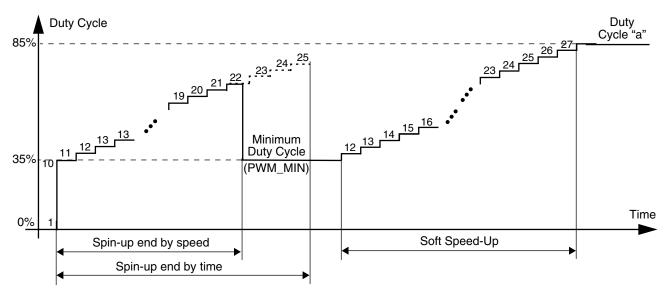

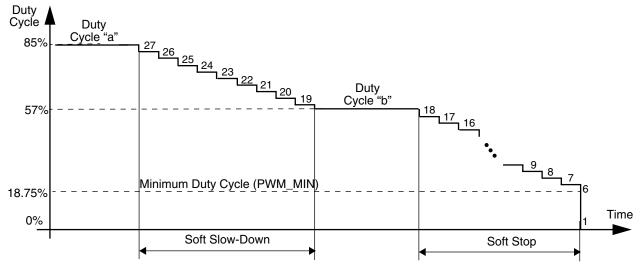

|      |        | 8.2.8 Fan Speed Control                                  |     |

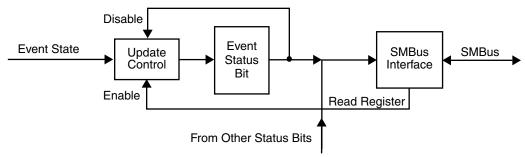

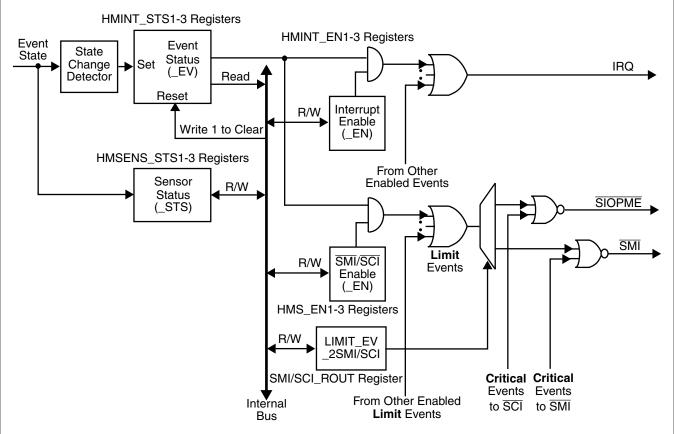

|      |        | 8.2.9 Event Notification                                 |     |

|      |        | 8.2.10 Enhanced Thermal Control (ETC)                    |     |

|      |        | 5                                                        |     |

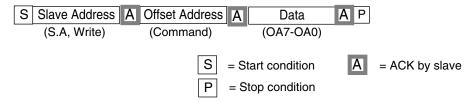

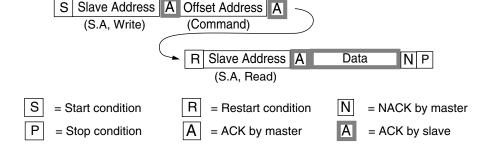

|      | 8.3    | HM SMBUS ACCESS                                          |     |

|      |        | 8.3.1 Write Transaction                                  |     |

|      |        |                                                          |     |

|      | 8.4    | HM LPC ACCESS REGISTERS                                  |     |

|      |        | 8.4.1 HM Address Register (HMADDR)                       |     |

|      |        | 8.4.3 HM Status and Command Register (HMSTS)             |     |

|      |        | 8.4.4 HM Interrupt Status Register 1 (HMINT_STS1)        |     |

|      |        | 8.4.5 HM Interrupt Status Register 2 (HMINT_STS2)        |     |

|      |        | 8.4.6 HM Interrupt Enable Register 1 (HMINT_EN1)         |     |

|      |        | 8.4.7 HM Interrupt Enable Register 2 (HMINT_EN2)         |     |

|      |        | 8.4.8 HM Sensor Status Register 1 (HMSENS_STS1)          |     |

|      |        | 8.4.9 HM Sensor Status Register 2 (HMSENS_STS2)          | 148 |

|      |        | 8.4.10 HM Interrupt Status Register 3 (HMINT_STS3)       | 149 |

|      |        | 8.4.11 HM Interrupt Enable Register 3(HMINT_EN3)         | 149 |

|      |        | 8.4.12 HM Sensor Status Register 3 (HMSENS_STS3)         | 150 |

|      |        | 8.4.13 HM SMI/SCI Enable Register 1 (HMS_EN1)            |     |

|      |        | 8.4.14 HM SMI/SCI Enable Register 2 (HMS_EN2)            |     |

|      |        | 8.4.15 HM SMI/SCI Enable Register 3(HMS_EN3)             |     |

|      | 0.5    | 8.4.16 Events to SMI/SCI Routing Register (SMI/SCI_ROUT) |     |

|      | 8.5    | HEALTH MANAGEMENT REGISTERS                              | 153 |

| 9.0  |        | acy Functional Blocks                                    |     |

|      | 9.1    | FLOPPY DISK CONTROLLER (FDC)                             |     |

|      | Б.     | 9.1.1 General Description                                |     |

| WWW  |        | S9.1.214 FDC Bitmap Summary                              |     |

|      | 9.2    | PARALLEL PORT                                            |     |

|      |        | 9.2.1 General Description                                | 194 |

| Table      | of C  | ontents          | G (Continued)                                            |     |

|------------|-------|------------------|----------------------------------------------------------|-----|

|            |       | 9.2.2            | Parallel Port Register Map                               | 194 |

|            |       | 9.2.3            | Parallel Port Bitmap Summary                             | 195 |

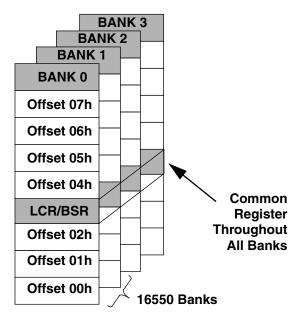

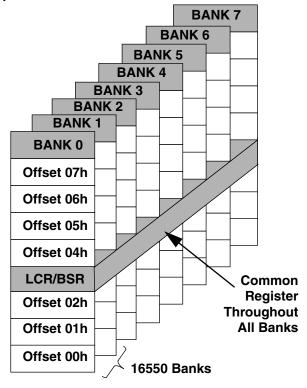

|            | 9.3   | SERIAL           | PORT 1 (SP1)                                             | 196 |

|            |       | 9.3.1            | General Description                                      | 196 |

|            |       | 9.3.2            | Register Bank Overview                                   | 196 |

|            |       | 9.3.3            | SP1 Register Maps                                        | 197 |

|            |       | 9.3.4            | SP1 Bitmap Summary                                       | 199 |

|            | 9.4   | SERIAL           | PORT 2 (SP2)                                             | 200 |

|            |       | 9.4.1            | General Description                                      | 200 |

|            |       | 9.4.2            | Register Bank Overview                                   | 200 |

|            |       | 9.4.3            | SP2 Register Map                                         |     |

|            |       | 9.4.4            | SP2 Bitmap Summary                                       | 204 |

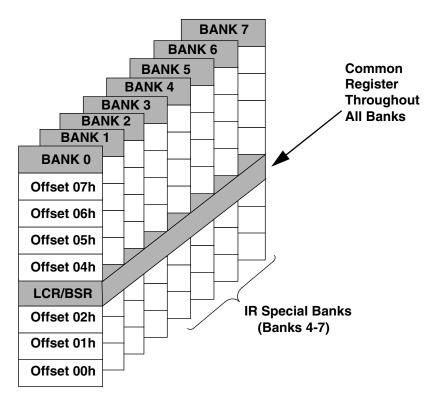

|            | 9.5   | SERIAL           | PORT 2 (SP2) WITH INFRARED                               | 206 |

|            |       | 9.5.1            | General Description                                      |     |

|            |       | 9.5.2            | UART Register Bank Overview                              |     |

|            |       | 9.5.3            | SP2 Register Map                                         | 207 |

|            | 9.6   | KEYBO            | ARD AND MOUSE CONTROLLER (KBC)                           |     |

|            |       | 9.6.1            | General Description                                      |     |

|            |       | 9.6.2            | KBC Register Map                                         |     |

|            |       | 9.6.3            | KBC Bitmap Summary                                       | 211 |

| 10.0       | Devic | e Char           | racteristics                                             |     |

|            | 10.1  | GENER            | AL DC ELECTRICAL CHARACTERISTICS                         | 212 |

|            |       | 10.1.1           | Recommended Operating Conditions                         |     |

|            |       | 10.1.2           | Absolute Maximum Ratings                                 |     |

|            |       | 10.1.3           | Capacitance                                              |     |

|            |       | 10.1.4           | Power Consumption under Recommended Operating Conditions |     |

|            |       | 10.1.5           | Voltage Thresholds                                       |     |

|            | 10.2  |                  | ARACTERISTICS OF PINS, BY I/O BUFFER TYPES               |     |

|            |       | 10.2.1           | Input, TTL Compatible                                    |     |

|            |       | 10.2.2           | Input, TTL Compatible, with Schmitt Trigger              |     |

|            |       | 10.2.3<br>10.2.4 | Input, TTL Compatible, with 200 mV Schmitt Trigger       |     |

|            |       | 10.2.4           | Input, PCI 3.3V Compatible                               |     |

|            |       | 10.2.6           | Input, SMBus Compatible                                  |     |

|            |       | 10.2.7           | Analog Input                                             |     |

|            |       | 10.2.8           | Output, TTL/CMOS Compatible, Push-Pull Buffer            |     |

|            |       | 10.2.9           | Output, TTL/CMOS Compatible, Open-Drain Buffer           |     |

|            |       | 10.2.10          | Output, PCI 3.3V Compatible                              |     |

|            |       | 10.2.11          | Analog Output                                            | 216 |

|            |       | 10.2.12          | Input/Output Switch, SMBus Compatible                    | 216 |

|            |       | 10.2.13          | Exceptions                                               | 217 |

| www.       | Datas | 10.2.14          | Terminology                                              | 217 |

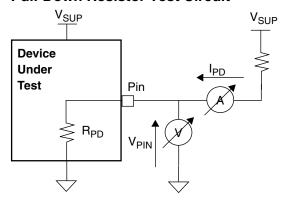

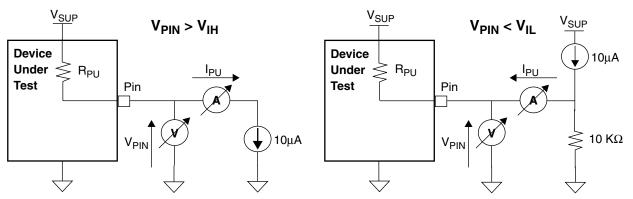

| VV VV VV . | 10.3  | INTERN           | IAL RESISTORS                                            | 218 |

|            |       | 10.3.1           | Pull-Up Resistor                                         | 218 |

|            |       | 10.3.2           | Pull-Down Resistor                                       | 218 |

11

| Table o | of Con  | tents  | 6 (Continued)                                                 |     |

|---------|---------|--------|---------------------------------------------------------------|-----|

| 10      | ).4 AC  | CELEC  | CTRICAL CHARACTERISTICS                                       | 219 |

|         | 10      |        | AC Test Conditions                                            |     |

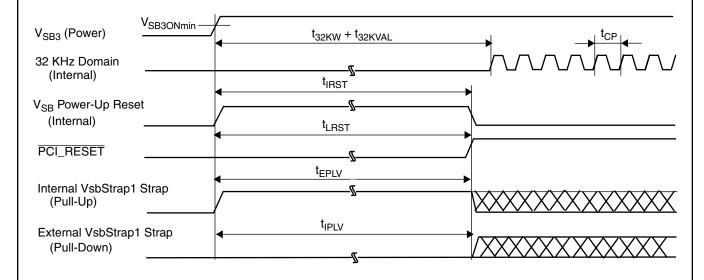

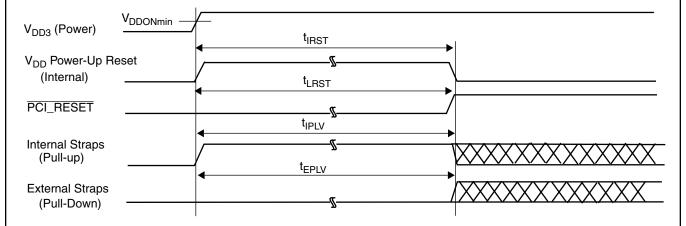

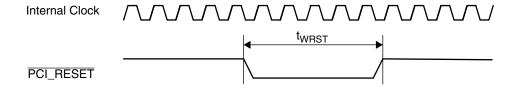

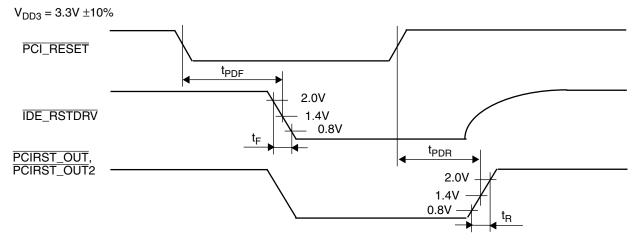

|         | 10      | ).4.2  | Reset Timing                                                  | 219 |

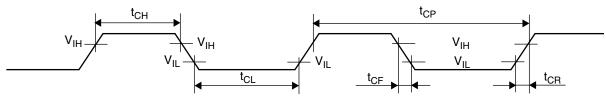

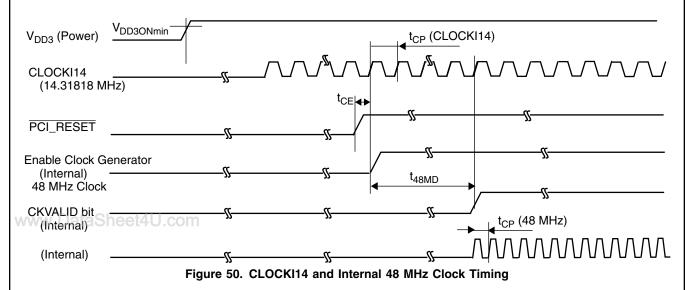

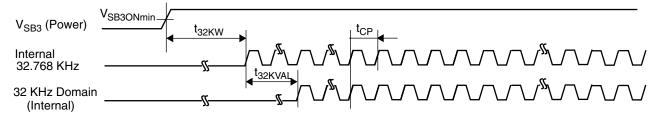

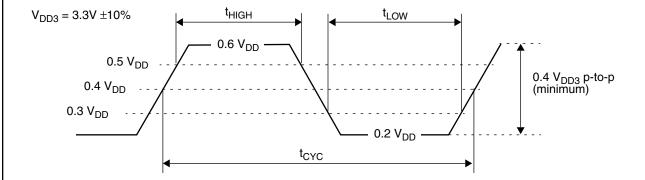

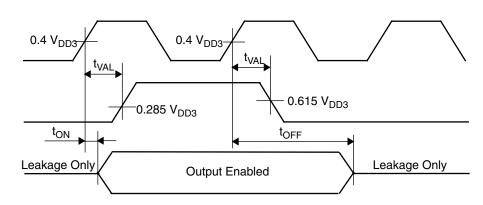

|         | 10      | 0.4.3  | Clock Timing                                                  | 222 |

|         | 10      | 0.4.4  | LPC Interface Timing                                          | 224 |

|         |         |        | FDC Timing                                                    |     |

|         | 10      | 0.4.6  | Parallel Port Timing                                          | 228 |

|         | 10      |        | Serial Ports 1 and 2 Timing                                   |     |

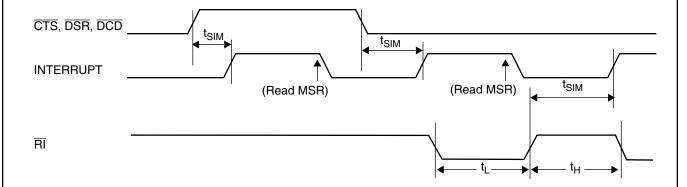

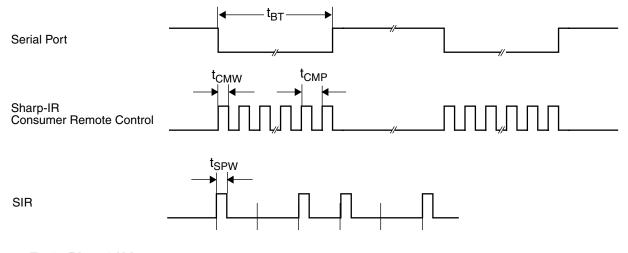

|         | 10      | 0.4.8  | Serial Port, Sharp-IR, SIR and Consumer Remote Control Timing | 231 |

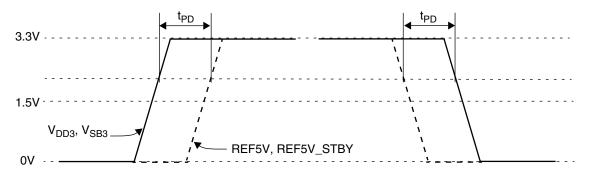

|         | 10      | ).4.9  | Glue Function Timing                                          | 232 |

|         | 10      | 0.4.10 | SWC Timing                                                    | 236 |

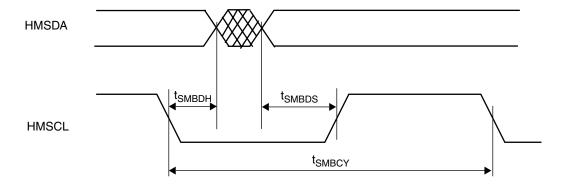

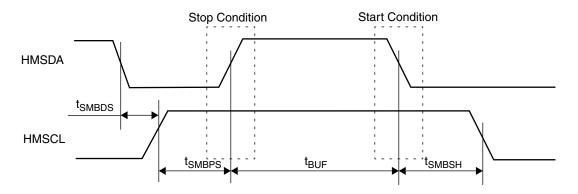

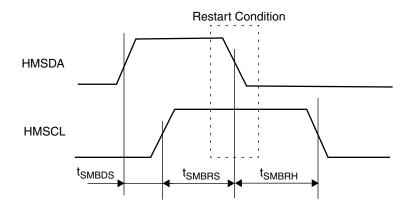

|         |         |        | SMBus Timing                                                  |     |

| 10      | ).5 PA  | ACKAG  | GE THERMAL INFORMATION                                        | 238 |

| Physica | l Dimer | nsions |                                                               | 239 |

| Pin | Pin Name                    | Pin | Pin Name         | Pin | Pin Name            | Pin                                | Pin Name                            |

|-----|-----------------------------|-----|------------------|-----|---------------------|------------------------------------|-------------------------------------|

| 1   | MCLK                        | 33  | SLCT             | 65  | CLOCKI14            | 97                                 | V <sub>CORF</sub>                   |

| 2   | MDAT                        | 34  | PE               | 66  | HD_LED              | 98                                 | V <sub>BAT</sub>                    |

| 3   | KBCLK                       | 35  | BUSY_WAIT        | 67  | PRIMARY_HD          | 99                                 | SIOPME                              |

| 4   | KBDAT                       | 36  | ACK              | 68  | SECONDARY_HD        | 100                                | GPIOE16                             |

| 5   | GA20                        | 37  | PD7              | 69  | SCSI                | 101                                | GPIOE14                             |

| 6   | $V_{DD3}$                   | 38  | PD6              | 70  | REF5V               | 102                                | NC                                  |

| 7   | KBRST                       | 39  | PD5              | 71  | V <sub>SB5</sub>    | 103                                | GPIOE00/SWD                         |

| 8   | V <sub>SS</sub>             | 40  | PD4              | 72  | REF5V_STBY          | 104                                | GPIOE01/FANTACH3                    |

| 9   | DSKCHG                      | 41  | PD3              | 73  | PCIRST_OUT          | 105                                | FANTACH4/GPIOE02                    |

| 10  | HDSEL                       | 42  | PD2              | 74  | PCIRST_OUT2/GPIOE12 | 106                                | GPIOE03/FANPWM1                     |

| 11  | RDATA                       | 43  | PD1              | 75  | GPIOE13             | 107                                | V <sub>SB3</sub>                    |

| 12  | WP                          | 44  | PD0              | 76  | V <sub>SB3</sub>    | 108                                | GPIOE04/FANPWM2                     |

| 13  | TRK0                        | 45  | ERR              | 77  | BKFD_CUT            | 109                                | GPIOE05/FANPWM3                     |

| 14  | WGATE                       | 46  | V <sub>SS</sub>  | 78  | V <sub>SS</sub>     | 110                                | V <sub>SS</sub>                     |

| 15  | WDATA                       | 47  | SLIN_ASTRB       | 79  | LATCHED_BF_CUT      | 111                                | GPIOE06/FANTACH1                    |

| 16  | STEP                        | 48  | ĪNIT             | 80  | GPIOE17             | 112                                | GPIOE07/FANTACH2                    |

| 17  | DIR                         | 49  | V <sub>DD3</sub> | 81  | PS_ON               | 113                                | CC_DDCSCL/GPIOE13                   |

| 18  | DR0                         | 50  | AFD_DSTRB        | 82  | PWRGD_PS            | 114                                | 5V_DDCSCL/GPIOE11                   |

| 19  | MTR0                        | 51  | STB_WRITE        | 83  | CPU_PRESENT         | 115                                | CC_DDCSDA/GPIOE12                   |

| 20  | INDEX                       | 52  | SMI              | 84  | PWRGD_3V            | 116                                | 5V_DDCSDA/GPIOE10                   |

| 21  | DRATE0                      | 53  | SER_IRQ          | 85  | SLP_S3              | 117                                | GPO11/VsbStrap1                     |

| 22  | DENSEL                      | 54  | LDRQ             | 86  | SLP_S5              | 118                                | GPIOE00/RI2/IRTX                    |

| 23  | DCD1                        | 55  | PCI_CLK          | 87  | SMB1_SCL            | 119                                | GPIOE01/SIN2/RI2                    |

| 24  | DSR1                        | 56  | LFRAME           | 88  | SMB2_SCL/HMSCL      | 120                                | GPIOE02/SOUT2/IRRX                  |

| 25  | SIN1                        | 57  | LAD3             | 89  | SMB1_SDA            | 121                                | GPIOE03/DSR2/SIN2                   |

| 26  | RTS1/TRIS                   | 58  | $V_{SS}$         | 90  | SMB2_SDA/HMSDA      | 122 GPO12/RTS2/SOUT2/<br>VddStrap1 |                                     |

| 27  | SOUT1/TEST                  | 59  | LAD2             | 91  | GPIO15              | 123                                | NC                                  |

| 28  | CTS1                        | 60  | $V_{DD3}$        | 92  | RSMRST              | 124                                | GPIOE04/CTS2/DSR2                   |

| 29  | $V_{SS}$                    | 61  | LAD1             | 93  | V <sub>SB3</sub>    | 125                                | GPO13/DTR_BOUT2/<br>RTS2/VddStrap2  |

| 30  | DTR_BOUT1/BADDR/<br>XOR_OUT | 62  | LAD0             | 94  | GRN_LED             | 126                                | GPIOE05/DCD2/CTS2                   |

| 31  | $V_{\mathrm{DD3}}$          | 63  | PCI_RESET        | 95  | YLW_LED             | 127                                | G <u>PIO</u> E06/IRRX/<br>DTR_BOUT2 |

| 32  | RI1                         | 64  | IDE_RSTDRV       | 96  | V <sub>SS</sub>     | 128                                | GPIOE07/IRTX/DCD2                   |

# 1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY

The signal DC characteristics of the pins described in Section 1.4 on page 21 are denoted by buffer type symbols, which are defined in Table 1 and described in further detail in Section 10.2 on page 213.

Table 1. Buffer Types

| Symbol            | Description                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------|

| IN <sub>T</sub>   | Input, TTL compatible                                                                       |

| IN <sub>TS</sub>  | Input, TTL compatible, with 250 mV Schmitt Trigger                                          |

| IN <sub>TS2</sub> | Input, TTL compatible, with 200 mV Schmitt Trigger                                          |

| IN <sub>TS4</sub> | Input, TTL compatible, with 400 mV Schmitt Trigger                                          |

| IN <sub>PCI</sub> | Input, PCI 3.3V compatible                                                                  |

| IN <sub>SM</sub>  | Input, SMBus compatible                                                                     |

| IN <sub>ULR</sub> | Input, power, resistor protected (not characterized)                                        |

| Al                | Input, analog (0-5.5V tolerant)                                                             |

| O <sub>p/n</sub>  | Output, TTL/CMOS compatible, push-pull buffer capable of sourcing $p$ mA and sinking $n$ mA |

| $OD_n$            | Output, TTL/CMOS compatible, open-drain buffer capable of sinking $n$ mA                    |

| O <sub>PCI</sub>  | Output, PCI 3.3V compatible,                                                                |

| AO                | Output, analog (0-5.5V tolerant)                                                            |

| SW <sub>SM</sub>  | Input/Output switch, SMBus compatible                                                       |

| PWR               | Power pin                                                                                   |

| GND               | Ground pin                                                                                  |

# 1.3 PIN MULTIPLEXING

Table 2 shows only multiplexed pins, their associated functional blocks and the configuration bits for the selection of the multiplexed options used in the PC8374L.

Table 2. Pin Multiplexing Configuration

# Table 2. Pin Multiplexing Configuration

|            | Function<br>Block    |      | Config<br>(Straps) |              | Civio            | 3440    | SWC         |                |                |               |               |               | SWC            |                |           |                 |           |           | Strap                  |

|------------|----------------------|------|--------------------|--------------|------------------|---------|-------------|----------------|----------------|---------------|---------------|---------------|----------------|----------------|-----------|-----------------|-----------|-----------|------------------------|

|            | Strap or<br>Wake-Up  | TRIS | TEST               | BADDR        | GPIOE12          | GPIOE13 | GPIOE00     | GPIOE01        | GPIOE02        | GPIOE03       | GPIOE04       | GPIOE05       | GPIOE06        | GPIOE07        | GPI0E13   | GPIOE11         | GPIOE12   | GPIOE10   | VsbStrap1 <sup>1</sup> |

| <b>.</b>   | Configuration Select |      |                    | TEST (strap) | SIOCF4.nPCIRSTO2 |         | SIOCF4.nSWD | SIOCF2.TACH3EN | SIOCF2.TACH4EN | SIOCF3.PWM1EN | SIOCF3.PWM2EN | SIOCF3.PWM3EN | SIOCF2.TACH1EN | SIOCF2.TACH2EN |           | SIOCF2.GPIO03EN |           |           |                        |

|            | Function<br>Block    |      |                    |              |                  |         |             |                |                |               |               |               |                |                |           |                 |           |           |                        |

| Simpordina | Alternate<br>Signal  |      |                    |              |                  |         |             |                |                |               |               |               |                |                |           |                 |           |           |                        |

|            | Function<br>Block    |      |                    | Config       | GPIO             |         | GPIO        |                |                |               | ¥             |               |                |                |           |                 | 2         |           |                        |

|            | Alternate<br>Signal  |      |                    | XOR_OUT      | GPIOE12          |         | GPIOE00     | FANTACH3       | FANTACH4       | FANPWM1       | FANPWM2       | FANPWM3       | FANTACH1       | FANTACH2       | GPIOE13   | GPIOE11         | GPIOE12   | GPIOE10   |                        |

|            | Function<br>Block    |      | Serial<br>Port 1   |              | Glue             | GPIO    | НМ          |                |                |               | GPIO          |               |                |                |           | <u> </u>        | ם<br>ס    |           | GPIO                   |

|            | Default<br>Signal    | RTS1 | SOUT1              | DTR_BOUT1    | PCIRST_OUT2      | GPIOE13 | SWD         | GPIOE01        | GPIOE02        | GPIOE03       | GPIOE04       | GPIOE05       | GPIOE06        | GPIOE07        | CC_DDCSCL | 5V_DDCSCL       | CC_DDCSDA | 5V_DDCSDA | GPO11                  |

| ta         | E<br>Shee            | 92   | 27                 | 30           | 74               | 75      | 103         | 104            | 105            | 106           | 108           | 109           | 111            | 112            | 113       | 114             | 115       | 116       | 117                    |

Table 2. Pin Multiplexing Configuration (Continued)

| Pin | Default<br>Signal | Function<br>Block | Alternate<br>Signal | Function<br>Block                            | Alternate<br>Signal | Function<br>Block | Configuration Select                                  | Strap or<br>Wake-Up    | Function<br>Block  |

|-----|-------------------|-------------------|---------------------|----------------------------------------------|---------------------|-------------------|-------------------------------------------------------|------------------------|--------------------|

| 118 | 118 GPIOE00       |                   | <u>RI2</u>          |                                              | IRTX                | InfraRed          | SIOCF3.373COMP AND<br>SIOCF3.SP2EN AND<br>SIOCF3.IREN | <u>RI2</u>             | SWC                |

| 119 | GPIOE01           |                   | SIN2                |                                              | RIZ                 | Serial<br>Port 2  | SIOCF3.373COMP AND SIOCF3.SP2EN                       | RIZ                    |                    |

| 120 | GPIOE02           |                   | SOUT2               | S. J. S. | IRRX                | InfraRed          | SIOCF3.373COMP AND<br>SIOCF3.SP2EN AND<br>SIOCF3.IREN |                        |                    |

| 121 | GPIOE03           |                   | DSR2                | Port 2                                       | SIN2                |                   |                                                       |                        |                    |

| 122 | GPO12             | GPIO              | RTS2                |                                              | SOUT2               |                   |                                                       | VddStrap1 <sup>2</sup> | Config<br>(Straps) |

| 124 | GPIOE04           |                   | CTS2                |                                              | DSR2                |                   | SIOCF3.373COMP AND SIOCF3.SP2EN                       |                        |                    |

| 125 | GPO13             |                   | DTR_BOUT2           |                                              | RTS2                | Serial<br>Port 2  |                                                       | VddStrap2              | Config<br>(Straps) |

| 126 | GPIOE05           |                   | DCD2                |                                              | CTS2                |                   |                                                       |                        |                    |

| 127 | GPIOE06           |                   | IRRX                | InfraRed                                     | DTR_BOUT<br>2       |                   | SIOCF3.373COMP AND<br>SIOCF3.SP2EN AND                |                        |                    |

| 128 | GPIOE07           |                   | IRTX                |                                              | DCD2                |                   | SIOCF3.IREN                                           |                        |                    |

1.  $V_{SB}$  strap input. Reserved for National use. 2.  $V_{DD}$  strap input. Reserved for National use.

The following table shows the selection of GPIOs on their respective pins:

Table 3. GPIO Selection on Pins

| GPIO    |          | Co       | onfiguration E | Bits     |          | Selected<br>On Pin | Comments |

|---------|----------|----------|----------------|----------|----------|--------------------|----------|

| GPIOE00 | SIOCF4.7 | SIOCF3.0 | SIOCF3.1       | SIOCF3.2 |          |                    |          |

|         | 0        | Х        | 0              | 0        |          | 118                | Default  |

|         | 0        |          | 1              |          |          | None               |          |

|         | 1        |          | 0              |          |          | Undefined          |          |

|         | 1        |          | 1              |          |          | 103                |          |

|         | 0        | 0        | Х              | 1        |          | 118                |          |

|         | 0        | 1        |                |          |          | None               |          |

|         | 1        | 0        |                |          |          | Undefined          |          |

|         | 1        | 1        |                |          |          | 103                |          |

| GPIOE01 | SIOCF2.1 | SIOCF3.1 |                |          |          |                    |          |

|         | 0        | 0        |                |          |          | 104                | Default  |

|         | 0        | 1        |                |          |          | 104                |          |

|         | 1        | 0        |                |          |          | 119                |          |

|         | 1        | 1        |                |          |          | None               |          |

| GPIOE02 | SIOCF4.6 | SIOCF2.2 | SIOCF3.0       | SIOCF3.1 | SIOCF3.2 |                    |          |

|         | 0        | X        | Х              | 0        | 0        | 120                | Default  |

|         | 0        | Χ        |                | 1        |          | None               |          |

|         | 1        | 0        |                | 0        |          | 105                |          |

|         | 1        | 0        |                | 1        |          | 105                |          |

|         | 1        | 1        |                | 0        |          | 120                |          |

|         | 1        | 1        |                | 1        |          | None               |          |

|         | 0        | Х        | 0              | Х        | 1        | 120                |          |

|         | 0        | Х        | 1              |          |          | None               |          |

|         | 1        | 0        | 0              |          |          | 105                |          |

|         | 1        | 0        | 1              |          |          | 105                |          |

|         | 1        | 1        | 0              |          |          | 120                |          |

|         | 1        | 1        | 1              |          |          | None               |          |

| GPIOE03 | SIOCF3.5 | SIOCF3.1 |                |          |          |                    |          |

|         | 0        | 0        |                |          |          | 106                | Default  |

|         | 0        | 1        |                |          |          | 106                |          |

|         | 1        | 0        |                |          |          | 121                |          |

|         | 1        | 1        |                |          |          | None               |          |

Table 3. GPIO Selection on Pins (Continued)

| GPIO              |          | Co       | onfiguration E | Bits     | S | elected<br>On Pin | Comments |

|-------------------|----------|----------|----------------|----------|---|-------------------|----------|

| GPIOE04           | SIOCF3.6 | SIOCF3.1 |                |          |   |                   |          |

|                   | 0        | 0        |                |          |   | 108               | Default  |

|                   | 0        | 1        |                |          |   | 108               |          |

|                   | 1        | 0        |                |          |   | 124               |          |

|                   | 1        | 1        |                |          |   | None              |          |

| GPIOE05           | SIOCF3.7 | SIOCF3.1 |                |          |   |                   |          |

|                   | 0        | 0        |                |          |   | 109               | Default  |

|                   | 0        | 1        |                |          |   | 109               |          |

|                   | 1        | 0        |                |          |   | 126               |          |

|                   | 1        | 1        |                |          |   | None              |          |

| GPIOE06           | SIOCF2.4 | SIOCF3.0 | SIOCF3.1       | SIOCF3.2 |   |                   |          |

|                   | 0        | 0        | Х              | 0        |   | 111               | Default  |

|                   | 0        | 1        |                |          |   | 111               |          |

|                   | 1        | 0        |                |          |   | 127               |          |

|                   | 1        | 1        |                |          |   | None              |          |

|                   | 0        | Х        | 0              | 1        |   | 111               |          |

|                   | 0        |          | 1              |          |   | 111               |          |

|                   | 1        |          | 0              |          |   | 127               |          |

|                   | 1        |          | 1              |          |   | None              |          |

| GPIOE07           | SIOCF2.5 | SIOCF3.0 | SIOCF3.1       | SIOCF3.2 |   |                   |          |

|                   | 0        | 0        | Х              | 0        |   | 112               | Default  |

|                   | 0        | 1        |                |          |   | 112               |          |

|                   | 1        | 0        |                |          |   | 128               |          |

|                   | 1        | 1        |                |          |   | None              |          |

|                   | 0        | Х        | 0              | 1        |   | 112               |          |

|                   | 0        |          | 1              |          |   | 112               |          |

|                   | 1        |          | 0              |          |   | 128               |          |

|                   | 1        |          | 1              |          |   | None              |          |

| GPIOE10           | SIOCF3.4 | SIOCF2.0 |                |          |   |                   |          |

|                   | 0        | 0        |                |          |   | None              | Default  |

|                   |          | 1        |                |          |   | 116               |          |

|                   | 1        | X        |                |          |   | None              |          |

| GPIOE11,<br>GPO11 | SIOCF2.0 |          | <u> </u>       |          |   |                   |          |

| ww.Dat            | aSheet4U | .com     |                |          |   | 117               | Default  |

|                   | 1        |          |                |          |   | 114               |          |

Table 3. GPIO Selection on Pins (Continued)

| GPIO     |          | Co       | onfiguration E | Selected<br>On Pin | Comments |

|----------|----------|----------|----------------|--------------------|----------|

| GPIOE12, | SIOCF2.0 | SIOCF3.1 | SIOCF4.4       |                    |          |

| GPO12    | 0        | 0        | 0              | 122                | Default  |

|          | 0        | Х        | 1              | 74                 |          |

|          | 0        | 1        | 0              | None               |          |

|          | 1        | Х        | 0              | 115                |          |

|          | 1        | Х        | 1              | Undefined          |          |

| GPIOE13, | SIOCF2.0 | SIOCF3.1 | SIOCF4.3       |                    |          |

| GPO13    | 0        | Х        | 0              | 75                 | Default  |

|          | 0        | 0        | 1              | 125                |          |

|          | 0        | 1        | 1              | None               |          |

|          | 1        | Х        | Х              | 113                |          |

# 1.4 DETAILED SIGNAL/PIN DESCRIPTIONS

This section describes all signals of the PC8374L device. The signals are organized by functional group.

# 1.4.1 LPC Interface

| Signal    | Pin(s)           | I/O | Buffer Type                         | Power Well       | Description                                                                                                                                  |

|-----------|------------------|-----|-------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| LAD3-0    | 57, 59,<br>61-62 | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub> | V <sub>DD3</sub> | LPC Address-Data. Multiplexed command, address bi-directional data and cycle status.                                                         |

| PCI_CLK   | 55               | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | LPC Clock. PCI clock used for the LPC bus (up to 33 MHz).                                                                                    |

| LFRAME    | 56               | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | <b>LPC Frame.</b> Low pulse indicates the beginning of a new LPC cycle or termination of a broken cycle.                                     |

| LDRQ      | 54               | 0   | O <sub>PCI</sub>                    | V <sub>DD3</sub> | LPC DMA Request. Encoded DMA request for LPC interface.                                                                                      |

| PCI_RESET | 63               | I   | IN <sub>PCI</sub>                   | V <sub>DD3</sub> | <b>LPC Reset.</b> PCI system reset used for the LPC bus (Hardware Reset).                                                                    |

| SER_IRQ   | 53               | I/O | IN <sub>PCI</sub> /O <sub>PCI</sub> | V <sub>DD3</sub> | <b>Serial IRQ.</b> The interrupt requests are serialized over a single pin, where each IRQ level is delivered during a designated time slot. |

| SMI       | 52               | 0   | OD <sub>6</sub>                     | V <sub>DD3</sub> | System Management Interrupt. Active (low) level indicates that an SMI occurred. External pull-up resistor to $V_{\rm DD3}$ is required.      |

# 1.4.2 Serial Port 1 and Serial Port 2 (UART1 and UART2)

| Signal     | Pin(s)        | I/O  | Buffer Type         | Power Well       | Description                                                                                                                                                                                                                                                                                                                                                                            |

|------------|---------------|------|---------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTS1       | 28            | ı    | IN <sub>TS</sub>    | V <sub>DD3</sub> | Clear to Send. When low, indicates that the modem or other data                                                                                                                                                                                                                                                                                                                        |

| CTS2       | 124 or<br>126 | I    | IN <sub>TS</sub>    | V <sub>DD3</sub> | transfer device is ready to exchange data.                                                                                                                                                                                                                                                                                                                                             |

| DCD1       | 23            | I    | IN <sub>TS</sub>    | V <sub>DD3</sub> | Data Carrier Detected. When low, indicates that the modem or                                                                                                                                                                                                                                                                                                                           |

| DCD2       | 126 or<br>128 | I    | IN <sub>TS</sub>    | V <sub>DD3</sub> | other data transfer device has detected the data carrier.                                                                                                                                                                                                                                                                                                                              |

| DSR1       | 24            | ı    | IN <sub>TS</sub>    | V <sub>DD3</sub> | Data Set Ready. When low, indicates that the data transfer                                                                                                                                                                                                                                                                                                                             |

| DSR2       | 121 or<br>124 | I    | IN <sub>TS</sub>    | V <sub>DD3</sub> | device, e.g., modem, is ready to establish a communications link.                                                                                                                                                                                                                                                                                                                      |

| DTR_BOUT1  | 30            | 0    | O <sub>4/8</sub>    | V <sub>DD3</sub> | Data Terminal Ready. When low, indicates to the modem or                                                                                                                                                                                                                                                                                                                               |

| DTR_BOUT2  | 125 or<br>127 | 0    | O <sub>4/8</sub>    | V <sub>DD3</sub> | other data transfer device that the corresponding UART is ready to establish a communications link. After a system reset, these pins provide the $\overline{\text{DTR}}$ function and set these signals to inactive high. <b>Baud Output.</b> Provides the associated serial channel baud rate generator output signal if test mode is selected, i.e., bit 7 of EXCR1 register is set. |

| RI1        | 32            | ı    | IN <sub>TS</sub>    | V <sub>DD3</sub> | Ring Indicator. When low, indicates that a telephone ring signa                                                                                                                                                                                                                                                                                                                        |

| RI2        | 118 or<br>119 | I    | IN <sub>TS</sub>    | V <sub>DD3</sub> | was received by the modem. These pins are monitored during $V_{DD}$ power-off for wake-up event detection.                                                                                                                                                                                                                                                                             |

| RTS1       | 26            | 0    | O <sub>4/8</sub>    | V <sub>DD3</sub> | Request to Send. When low, indicates to the modem or other                                                                                                                                                                                                                                                                                                                             |

| RTS2       | 122 or<br>125 | 0    | O <sub>4/8</sub>    | V <sub>DD3</sub> | data transfer device that the corresponding UART device is ready to exchange data. A system reset sets these signals to inactive high.                                                                                                                                                                                                                                                 |

| SIN1.DataS | 25eet         | 4U.c | om <sup>IN</sup> TS | V <sub>DD3</sub> | Serial Input. Receives composite serial data from the                                                                                                                                                                                                                                                                                                                                  |

| SIN2       | 119 or<br>121 | I    | IN <sub>TS</sub>    | V <sub>DD3</sub> | communications link (peripheral device, modem or other datransfer device).                                                                                                                                                                                                                                                                                                             |

| Signal | Pin(s)        | I/O | Buffer Type      | Power Well | Description                                                                                                                           |

|--------|---------------|-----|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| SOUT1  | 27            | 0   | O <sub>4/8</sub> |            | Serial Output. Sends composite serial data to the                                                                                     |

| SOUT2  | 120 or<br>122 | 0   | O <sub>4/8</sub> |            | communications link (peripheral device, modem or other data transfer device). These signals are set active high after a system reset. |

# 1.4.3 InfraRed Port