# L84225100BaseTX/FX/10BaseT Physical Layer Device Technical Manual

- Single-chip 100BaseTX/100BaseFX/ 10BaseT physical layer solution

- Four independent Channels in One IC

- 3.3 V power supply with 5 V tolerant I/O

- Dual Speed 10/100 Mbps

- Half and Full Duplex

- MII interface or reduced pin count MII (RMII) interface to Ethernet Controller

- MI interface for configuration and status

- Optional Repeater Interface

- AutoNegotiation for 10/100, Full/Half Duplex hardware controlled advertisement

Meets all applicable IEEE 802.3, 10BaseT, 100BaseTX and 100BaseFX standards

LSI LOGIC

- On-chip wave shaping no external filters required

- Adaptive Equalizer for 100BaseTX

- Baseline Wander Correction

- LED outputs

- Link, Activity, Collision

- Full Duplex

- Far End Fault (for FX)

- 10/100

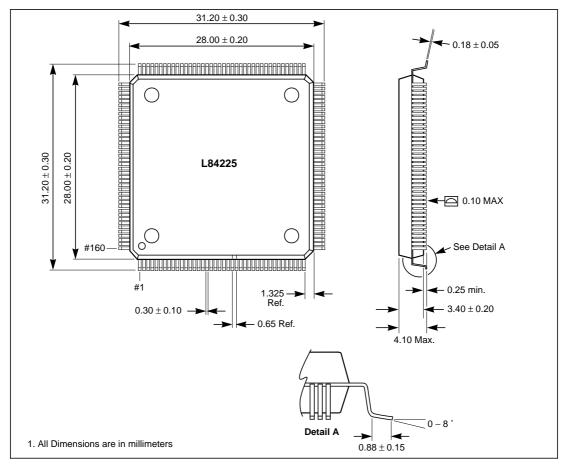

- 160L PQFP

| Contents                   |                            |  |  |  |  |  |  |  |  |  |  |

|----------------------------|----------------------------|--|--|--|--|--|--|--|--|--|--|

| Description 2              | Specifications 87          |  |  |  |  |  |  |  |  |  |  |

| Pin Description 4          | Ordering Information 114   |  |  |  |  |  |  |  |  |  |  |

| Functional Description 13  | Revision History 114       |  |  |  |  |  |  |  |  |  |  |

| Register Description57     | Surface Mount Packages 117 |  |  |  |  |  |  |  |  |  |  |

| Application Information 70 |                            |  |  |  |  |  |  |  |  |  |  |

<u>Note:</u> Check for the latest revision of this document before starting any designs. This document is available on the Web, at www.lsilogic.com

# Description

The L84225 is a highly integrated Ethernet Transceiver for twisted pair and fiber Ethernet applications. The L84225 can be configured for either 100 Mbps (100BaseFX or 100BaseTX) or 10 Mbps (10BaseT) Ethernet operation.

The L84225 consists of four (4) separate and independent channels. Each channel consists of: 4B5B/Manchester encoder, scrambler, transmitter with wave shaping and on-chip filters, transmit output driver, receiver with adaptive equalizer, filters, baseline wander correction, clock and data recovery, descrambler, 4B5B/Manchester decoder, and controller interface (MII or RMII).

The addition of internal output waveshaping circuitry and on-chip filters eliminates the need for external filters normally required in 100BaseTX and 10BaseT applications.

The L84225 can automatically configure itself for 100 or 10 Mbps and Full or Half Duplex operation, for each channel independently, using the on-chip AutoNegotiation algorithm.

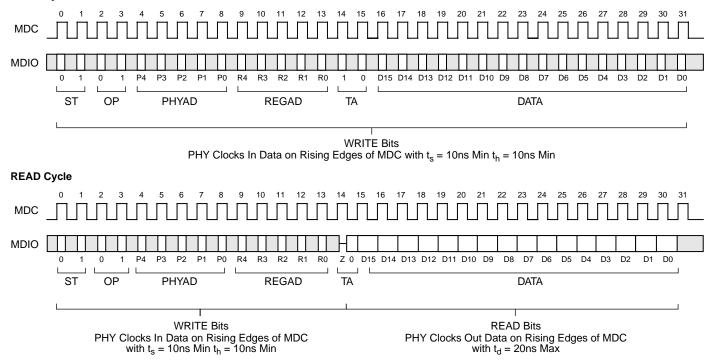

The L84225 can access eleven 16-bit registers for each channel through the Management Interface (MI) serial port. These registers comply with Clause 22 of IEEE 802.3u and contain configuration inputs, status outputs, and device capabilities.

The L84225 is ideal as a media interface for 100BaseTX/ 100BaseFX/10BaseT switching hubs, repeaters, routers, bridges, and other multi port applications.

The L84225 is implemented in a low power CMOS technology and operates with a 3.3V power supply.

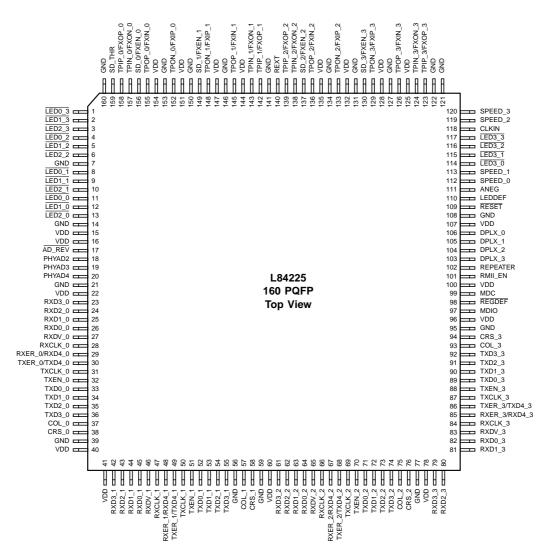

# **Pin Configuration**

# **1** Pin Description

### **Pin Description**

| Power S                                                                                                            | Supplies |     |                                 |

|--------------------------------------------------------------------------------------------------------------------|----------|-----|---------------------------------|

| Pin #                                                                                                              | Pin Name | I/O | Description                     |

| 15<br>16<br>22<br>40<br>41<br>60<br>78<br>96<br>100<br>107<br>125<br>128<br>132<br>135<br>144<br>147<br>151<br>154 | VDD      |     | Positive Supply. +3.3 5% Volts. |

| 7<br>14<br>21<br>39<br>56<br>59<br>77<br>95<br>108<br>121<br>122<br>127<br>131<br>134<br>141<br>146<br>153<br>160  | GND      |     | Ground. 0 Volts.                |

| Media I                  | nterface                  |     |                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|---------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                    | Pin Name                  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                              |

| 126<br>136<br>145<br>155 | TPOP_[3:0]/<br>FXIN_[3:0] | I/O | Twisted Pair Transmit Output, Positive.<br>Fiber Receive Input, Negative.                                                                                                                                                                                                                                                                                                                |

| 129<br>133<br>148<br>152 | TPON_[3:0]/<br>FXIP_[3:0] | I/O | Twisted Pair Transmit Output, Negative.<br>Fiber Receive Input, Positive.                                                                                                                                                                                                                                                                                                                |

| 123<br>139<br>142<br>158 | TPIP_[3:0]/<br>FXOP_[3:0] | I/O | Twisted Pair Receive Input, Positive.<br>Fiber Transmit Output, Positive.                                                                                                                                                                                                                                                                                                                |

| 124<br>138<br>143<br>157 | TPIN_[3:0]/<br>FXON_[3:0] | I/O | Twisted Pair Receive Input, Negative.<br>Fiber Transmit Output, Negative.                                                                                                                                                                                                                                                                                                                |

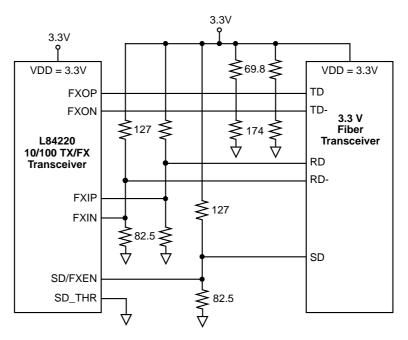

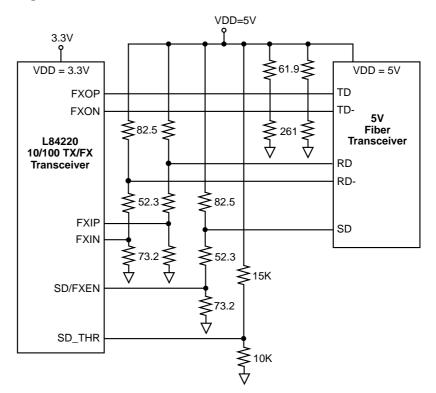

| 130<br>137<br>149<br>156 | SD_[3:0]/<br>FXEN_[3:0]   | I   | Fiber Interface Signal Detect Input.<br>Fiber Interface Enable.<br>When this pin in not tied to GND, the fiber interface is enabled and<br>this pin becomes a Signal Detect ECL input. The trip point for this<br>ECL input is determined by the voltage applied to the SD_THR<br>pin. When this pin is tied to GND, the fiber interface is disabled<br>(i.e., TP Interface is enabled). |

| 159                      | SD_THR                    |     | <b>Fiber Interface Signal Detect Threshold Reference.</b><br>The voltage applied to this pin sets the reference level for the fiber interface SD input pin so that the device can directly connect SD pin to both 3.3V and 5V fiber optic transceivers. Typically, this pin is either tied to GND (for 3.3V) or to an external voltage divider (for 5V).                                 |

| 140                      | REXT                      |     | <b>Transmit Current Set.</b><br>An external resistor connected between this pin and GND will set the level for the transmit outputs.                                                                                                                                                                                                                                                     |

| Control                                  | ler Interface (M                                     | II & RMII) |                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                                    | Pin Name                                             | I/O        | Description                                                                                                                                                                                                                                                                                                                                                            |

| 87<br>69<br>50<br>31                     | TXCLK_[3:0]                                          | 0          | <b>Transmit Clock Output.</b> These interface outputs provide clocks to external controllers. Transmit data from the controller on TXD, TXEN, and TXER is clocked in on the rising edges of TXCLK and CLKIN.                                                                                                                                                           |

| 88<br>70<br>51<br>32                     | TXEN_[3:0]                                           | I          | <b>Transmit Enable Input.</b> These interface inputs must be asserted active high to allow data on TXD and TXER to be clocked in on the rising edges of TXCLK and CLKIN.                                                                                                                                                                                               |

| [92:89]<br>[74:71]<br>[55:52]<br>[36:33] | TXD[3:0]_3<br>TXD[3:0]_2<br>TXD[3:0]_1<br>TXD[3:0]_0 | I          | <b>Transmit Data Input.</b> These interface inputs contain input nibble data to be transmitted on the TP or FX outputs and are clocked in on rising edges of TXCLK and CLKIN. In RMII mode, only TXD[1:0] are used.                                                                                                                                                    |

| 86<br>68<br>49<br>30                     | TXER_[3:0]/<br>TXD4_[3:0]                            | I          | <b>Transmit Error Input.</b> These interface inputs initiate an error pattern to be transmitted on the TP or FX outputs and are clocked in on rising edges of TXCLK when TXEN is asserted. If the channel is placed in the Bypass 4B5B Encoder mode, these pins are reconfigured to be the fifth TXD transmit data input, TXD4. In RMII mode, these pins are not used. |

| 84<br>66<br>47<br>28                     | RXCLK_[3:0]                                          | 0          | <b>Receive Clock Output.</b> These interface outputs provide a clock to the controller. Receive data on RXD, RXDV, and RXER is clocked out to the controller on falling edges of RXCLK.                                                                                                                                                                                |

| 94<br>76<br>58<br>38                     | CRS_[3:0]                                            | 0          | <b>Carrier Sense Output.</b> These interface outputs are asserted active high when valid data is detected on the receive TP or FX inputs and is clocked out on the falling edge of RXCLK.                                                                                                                                                                              |

| 83<br>65<br>46<br>27                     | RXDV_[3:0]                                           | 0          | <b>Receive Data Valid Output.</b> These interface outputs are asserted active high when valid decoded data is present on the RXD outputs and is clocked out on falling edges of RXCLK. In RMII mode, these pins are not used.                                                                                                                                          |

| [79:82]<br>[61:64]<br>[42:45]<br>[23:26] | RXD[3:0]_3<br>RXD[3:0]_2<br>RXD[3:0]_1<br>RXD[3:0]_0 | 0          | <b>Receive Data Output.</b> These interface outputs contain recovered nibble data from the TP or FX inputs and are clocked out on the falling edges of RXCLK. In RMII mode, only RXD[1:0] are used.                                                                                                                                                                    |

| Control              | ler Interface (N          | III & RMII  | ) [Continued]                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                | Pin Name                  | I/O         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 85<br>67<br>48<br>29 | RXER_[3:0]/<br>RXD4_[3:0] | 0           | <b>Receive Error Output.</b> These interface outputs are asserted active high when coding or other specified errors are detected on the TP or FX inputs and are clocked out on falling edges of RXCLK.<br>If the channel is placed in the Bypass 4B5B Decoder mode, these pins are reconfigured to be the fifth RXD receive data output, RXD4.                                                                                                                |

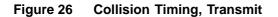

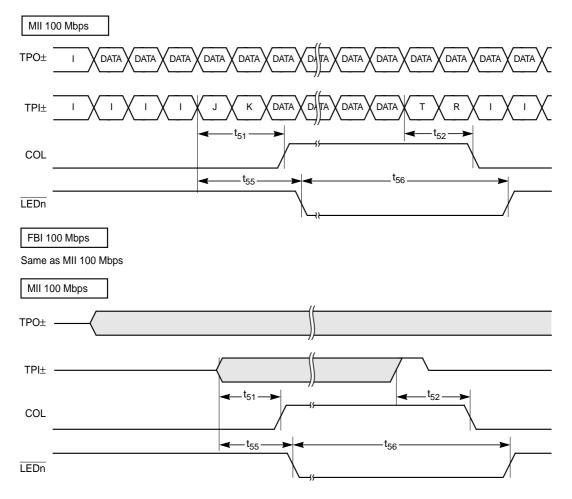

| 93<br>75<br>57<br>37 | COL_[3:0]                 | 0           | <b>Collision Output.</b> These interface outputs are asserted active high when collision between transmit and receive data is detected.                                                                                                                                                                                                                                                                                                                       |

| Manage               | ement Interface           | e (MI)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin #                | Pin Name                  | I/O         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

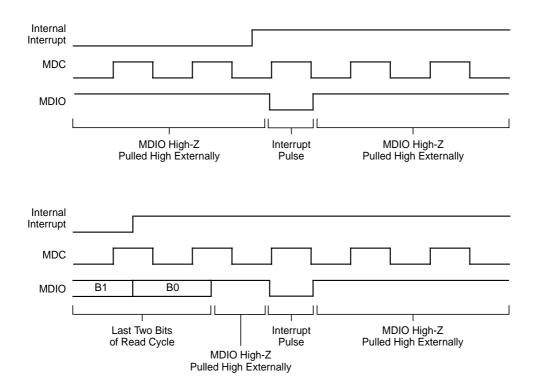

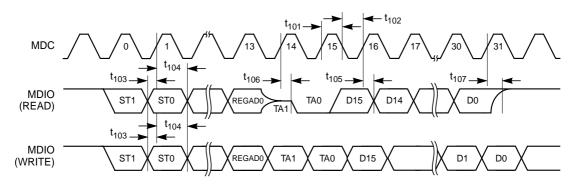

| 99                   | MDC                       | I           | Management Interface (MI) Clock Input. This MI clock shifts serial data into and out of MDIO on rising edges.                                                                                                                                                                                                                                                                                                                                                 |

| 97                   | MDIO                      | I/O         | <b>Management Interface (MI) Data Input/Output.</b> This bidirectional pin contains serial data that is clocked in and out on rising edges of the MDC clock.                                                                                                                                                                                                                                                                                                  |

| 98                   | REGDEF                    | l<br>Pullup | <ul> <li>Invalid Register Read Select This active low input controls the default values that are read from invalid (unused) register locations.</li> <li>1 = All unused register locations return a value of '0000' when read.</li> <li>0 = All unused register locations return a value of 'ffff' when read.</li> <li>Note: Not available on Rev. B product. On Rev. B product all invalid register locations return a value of '0000' when read.</li> </ul> |

| 20<br>19<br>18       | PHYAD[4:2]                | 1           | MI Physical Device Address Input. These pins set the three most significant bits of the PHY address. The two least significant bits of the PHY address are set internally to match the channel number, as shown below:                                                                                                                                                                                                                                        |

|                      |                           |             | PHYAD1PHYAD0Channel 31Channel 21Channel 10Channel 10O0                                                                                                                                                                                                                                                                                                                                                                                                        |

| LED Dr                   | ivers      |     |                                                                                                                                                                                                                      |

|--------------------------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                    | Pin Name   | I/O | Description                                                                                                                                                                                                          |

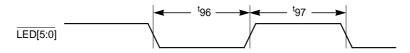

| 117<br>116<br>115<br>114 | LED3_[3:0] | 0   | <b>LED Output.</b> The default functions of these pins are 100 Mbps<br>Link Detect outputs assuming LEDDEF = 0. These pins can drive<br>an LED from both VDD and GND.<br>Please refer to Table 2 for LED description |

| 3<br>6<br>10<br>13       | LED2_[3:0] | 0   | <b>LED Output.</b> The default functions of these pins are Activity<br>Detect outputs assuming LEDDEF = 0. These pins can drive an<br>LED from both VDD and GND.<br>Please refer to Table 2 for LED description      |

| 2<br>5<br>9<br>12        | LED1_[3:0] | 0   | <b>LED Output.</b> The default functions of these pins are Full Duplex<br>Detect outputs assuming LEDDEF = 0. These pins can drive an<br>LED from both VDD and GND.<br>Please refer to Table 2 for LED description   |

| 1<br>4<br>8<br>11        | LED0_[3:0] | 0   | <b>LED Output.</b> The default functions of these pins are 10 Mbps Link<br>Detect outputs assuming LEDDEF = 0. These pins can drive an<br>LED from both VDD and GND.<br>Please refer to Table 2 for LED description. |

| 110                      | LEDDEF     | Ι   | <b>LED Default Select Input.</b> This pin changes the default selection for the LEDs in the MI Serial Port Global Configuration Register.<br>1 = LINK + ACT, COL, FDX, 10/100<br>0 = LINK100, ACT, FDX, LNK10        |

| Miscella                 | aneous      |             |                                                                                                                                                                                                                                                                                               |

|--------------------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                    | Pin Name    | I/O         | Description                                                                                                                                                                                                                                                                                   |

| 111                      | ANEG        | I           | AutoNegotiation Enable Input. This digital input, ANDed with register bit 0.12, enables AutoNegotiation for all channels.<br>1 = AutoNegotiation On & Combined with Speed and Duplex pins, control advertisement. See Table 1 for the different combinations. $0 = Off$                       |

| 120<br>119<br>113<br>112 | SPEED_[3:0] | I           | <b>Speed Selection Input.</b> These digital inputs, ANDed with register bit 0.13, select speed in each corresponding channel. Please refer to Table 1 for the different combinations.<br>1 = 100 Mbps Mode<br>0 = 10 Mbps Mode                                                                |

| 103<br>104<br>105<br>106 | DPLX_[3:0]  | I           | <b>Duplex Selection Input.</b> These digital inputs, ORed with register<br>bit 0.8, select the duplex mode in EACH corresponding channel.<br>They control advertisement when ANEG is enabled. See Table 1<br>for the different combinations.<br>1 = Full Duplex Mode<br>0 = Half Duplex Mode  |

| 102                      | REPEATER    | I           | <b>Repeater Mode Enable Input.</b> This digital input, ORed with register bit 17.14, enables repeater mode for ALL channels.<br>1 = Repeater Mode Enabled<br>0 = Normal Operation                                                                                                             |

| 101                      | RMII_EN     | I           | Reduced Pin Count MII Interface Enable.<br>1 = RMII Mode Enabled<br>0 = MII Enabled                                                                                                                                                                                                           |

| 17                       | AD_REV      | l<br>Pullup | Address Reverse Input.<br>1 = Normal<br>In this mode, physical ports 0-3 are mapped to MI addresses 0-3<br>in the same order.<br>0 = Reverse Address Mode Select<br>In this mode, physical ports 0-3 are mapped to MI addresses 3-0<br>respectively. This is the reverse to the normal order. |

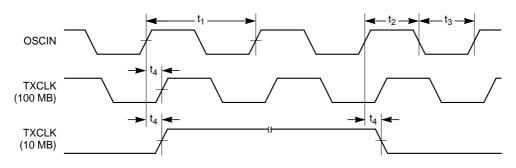

| 118                      | CLKIN       | I           | <b>Clock Input.</b> In MII mode, there must be a 25 MHz clock input to this pin. In RMII mode, there must be a 50 MHz clock input to this pin. TXCLK is generated from the input to this pin.                                                                                                 |

| 109                      | RESET       | l<br>Pullup | Hardware Reset Input.<br>1 = Normal<br>0 = Device In Reset State<br>(Reset is complete 50 ms after RESET goes high).                                                                                                                                                                          |

|      | Input                         | Pins |         | Mode Selected |             |            |               |  |  |  |  |  |

|------|-------------------------------|------|---------|---------------|-------------|------------|---------------|--|--|--|--|--|

|      |                               |      |         | Forced Mo     | des [Note2] | Advertised | Capabilities  |  |  |  |  |  |

| Aneg | [3:0] [3:0] [3:0] [3:0] [3:0] |      | Autoneg | Speed         | DPLX        | Speed      | DPLX          |  |  |  |  |  |

| 0    | 0000                          | 0000 | Off     | 10            | Half        | na         | na            |  |  |  |  |  |

| 0    | 0000                          | 1111 | Off     | 10            | Full        | na         | na            |  |  |  |  |  |

| 0    | 1111                          | 0000 | Off     | 100 Half      |             | na         | na            |  |  |  |  |  |

| 0    | 1111                          | 1111 | Off     | 100           | Full        | na         | na            |  |  |  |  |  |

| 1    | 0000                          | 0000 | On      | na            | na          | 10         | Half          |  |  |  |  |  |

| 1    | 0000                          | 1111 | On      | na            | na          | 10         | Half/Full     |  |  |  |  |  |

| 1    | 1111                          | 0000 | On      | na na         |             | 10/100     | Half/Full [3] |  |  |  |  |  |

| 1    | 1111                          | 1111 | On      | na            | na          | 10/100     | Half          |  |  |  |  |  |

### Table 1 AutoNegotiation, Speed & Duplex Mode Combinations

**Note 1:** The single ANEG pin applies to all four channels. The four Speed and DPLX apply to each individual channel. The pins above are shown for all four channels, but each channel can be individually configured for SPEED and DPLX by appropriately setting the pin for that channel.

**Note 2:** Forced Modes assume that registers 0 and 4 are at default values.

**Note 3:** the L84225 can be controlled either through the software or through the hardware. If the device needs to be controlled through the software (Registers 0 to 4), then these seven pins (ANEG, Speed[3:0], Duplx[3:0]) have to be tied to their default values of 1, 1111, and 0000, respectively.

| Name              | Output State Description                               | LED tied<br>to GND | LED tied<br>to Vdd | LEDDEF     |

|-------------------|--------------------------------------------------------|--------------------|--------------------|------------|

| LED0 <sup>1</sup> | 0 = 100 Mbps Link Detected                             | Off                | On                 | LEDDEF = 1 |

| (10/100)          | 1 = 10 Mbps Link Detected                              | On                 | Off                |            |

|                   | 3-state = No Link                                      | Off                | Off                |            |

| LED1              | 0 = Full Duplex Mode Detect with Link Pass             | Off                | On                 |            |

| (Fdx/Hdx)         | 1 = Half Duplex Mode Detect with Link Pass             | On                 | Off                |            |

|                   | 3-state = No Link                                      | Off                | Off                |            |

| LED2              | 0 = Collision Detect                                   | Off                | On                 |            |

| (Col)             | 1 = No Collision                                       | On                 | Off                |            |

| LED3              | 0 = Link Detect                                        | Off                | On                 |            |

| (Link + Act)      | Blink = Link Detect + Activity                         | Blink              | Blink              |            |

|                   | 1 = No Link Detect or Activity                         | On                 | Off                |            |

| LED0 <sup>1</sup> | 0 = 10 Mbps Link Detected                              | Off                | On                 | LEDDEF = 0 |

| (Link10)          | 1 = No 10 Mbps Link Detected                           | On                 | Off                |            |

| LED1              | 0 = Full Duplex Mode Detect with Link Pass             | Off                | On                 |            |

| (Fdx/Hdx)         | 1 = Half Duplex Mode Detect with Link Pass             | On                 | Off                |            |

|                   | 3-state = No Link                                      | Off                | Off                |            |

| LED2              | Blink = Activity Occurred<br>(Stretch pulse to 100 ms) | Off                | On                 |            |

| (Act)             | 1 = No Activity                                        | On                 | Off                |            |

| LED3              | 0 = Link100 Detected                                   | Off                | On                 |            |

|                   | 1 = No Link100                                         | On                 | Off                |            |

| (Link100)         | Detected                                               |                    |                    |            |

### Table 2 LED Definitions as per the LEDDEF Pin

1. LED 0 becomes FEF when FX Interface is enabled.

0 = FEF detected

1 = No FEF detected

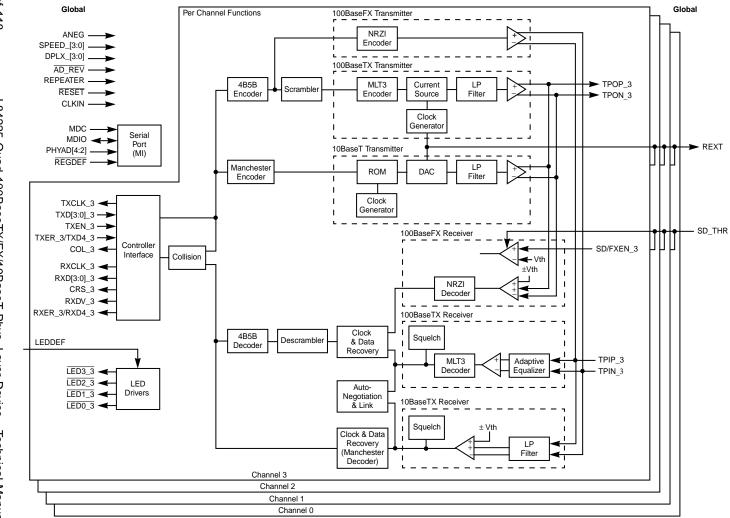

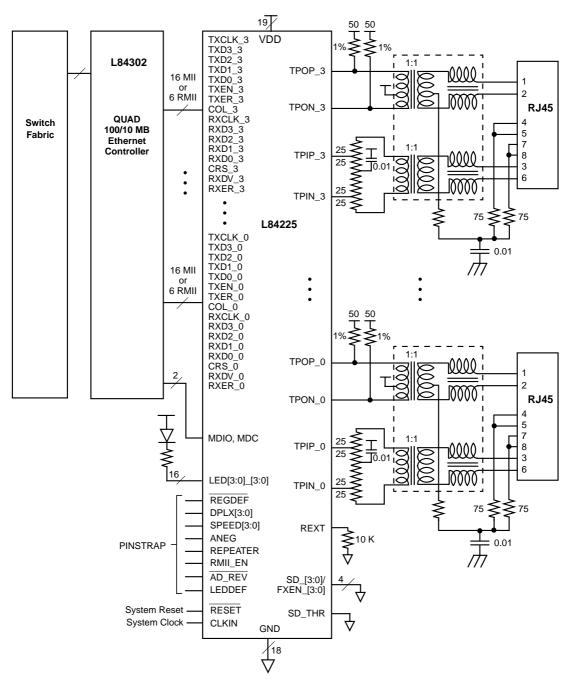

### Figure 1 L84225 Block Diagram

**12 of 118** April, 2002

Copyright © 1999-2002 by LSI Logic Corporation. All rights reserved. L84225 Quad 100BaseTX/FX/10BaseT Phys. Layer Device ÷ Technical Manual

# 2 Functional Description

### 2.1 General

The L84225 is a complete 10/100 Mbps Ethernet Media Interface IC. The L84225 has four separate and independent channels. Each channel has the following main sections: controller interface, encoder, decoder, scrambler, descrambler, clock and data recovery, twisted pair and fiber interface transmitter, twisted pair and fiber interface receiver, and auto negotiation. A Management Interface (MI) serial port, which provides access to eleven registers for each channel, is common to all four channels. Figure 1 shows the L84225 block diagram.

The L84225 can operate as a 100BaseTX or 100BaseFX device (100 Mbps mode) or as a 10BaseT device (10 Mbps mode). The 100 Mbps and 10 Mbps modes differ in data rate, signaling protocol, and allowed wiring as follows:

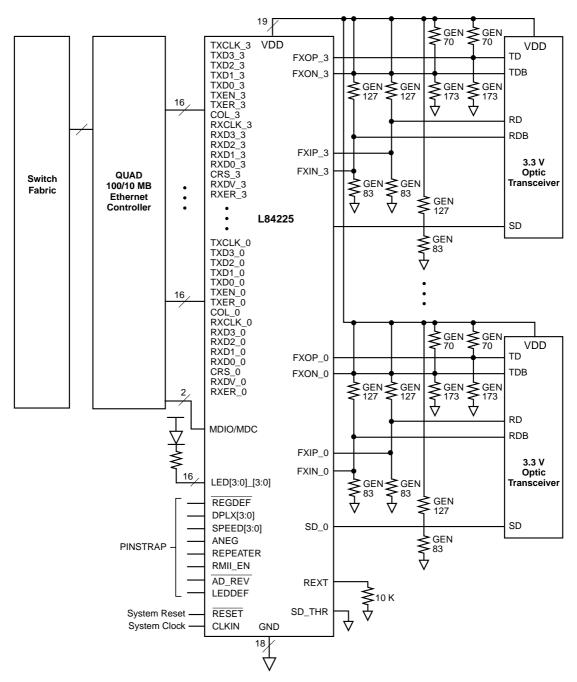

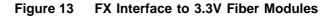

- The 100 Mbps FX mode uses two fiber connections with 4B5B encoded NRZI 125 MHz binary data through an ECL-type driver to achieve a throughput of 100 Mbps.

- The 100 Mbps TX mode uses two pairs of category 5, or better, UTP or STP twisted pair cable with 4B5B encoded, scrambled, and MLT3 coded (ternary) 125 MHz data to achieve a throughput of 100 Mbps.

- The 10 Mbps mode uses two pairs of category 3, or better, UTP or STP twisted pair cable with Manchester encoded 10 MHz binary data to achieve a 10 Mbps thruput.

The data symbol format on the fiber or twisted pair cable for the 100 and 10 Mbps modes is defined in IEEE 802.3 specifications and shown in Figure 2.

| la ta ufua un a   |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Eth    | ernet MAC  | Frame      |    |          |     | المغم ال       | (           |  |  |  |  |  |

|-------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|------------|----|----------|-----|----------------|-------------|--|--|--|--|--|

| Interframe<br>GAP | Pf                                       | REAMBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SFD    | DA         | SA         | LN | LLC Data | FCS |                | frame<br>AP |  |  |  |  |  |

|                   | <br> <br> <br>                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 Ba | ase-TX Dat | ta Symbols |    | -        |     | <br> <br> <br> |             |  |  |  |  |  |

| IDLE              | SSD                                      | PREAMBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SFD    | DA         | SA         | LN | LLC DATA | FCS | ESD            | IDLE        |  |  |  |  |  |

|                   | DA, S                                    | $\label{eq:started} \begin{split} & \text{IDLE} = [\ 1\ 1\ 1\ 1\] \\ & \text{SSD} = [\ 1\ 1\ 0\ 0\ 0\ 1\ 0\ 0\ 0\ 1\ ] \\ & \text{PREAMBLE} = [\ 1\ 0\ 1\ 0\]\ 62\ \text{Bits Long} \\ & \text{SFD} = [\ 1\ 1\ ] \\ & \text{DA, SA, LN, LLC DATA, FCS} = [\ DATA\ ] \\ & \text{ESD} = [\ 0\ 1\ 1\ 0\ 1\ 0\ 0\ 1\ 1\ 1\ ] \\ \end{split} \right] \\ \end{split} \\ \begin{array}{c} \text{Before/After} \\ & \text{4B5B Encoding,} \\ & \text{Scrambling, and} \\ & \text{MLT3 Coding} \\ \end{array}$ |        |            |            |    |          |     |                |             |  |  |  |  |  |

|                   | <br> <br>                                | 100 Base-FX Data Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |            |            |    |          |     |                |             |  |  |  |  |  |

| IDLE              | SSD                                      | PREAMBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SFD    | DA         | SA         | LN | LLC DATA | FCS | ESD            | IDLE        |  |  |  |  |  |

|                   | '<br> <br> <br> <br> <br> <br> <br> <br> | IDLE = [1111]<br>SSD = [1100010001]<br>PREAMBLE = [1010]62 Bits Long<br>SFD = [11]<br>DA, SA, LN, LLC DATA, FCS = [DATA]<br>ESD = [0110100111]                                                                                                                                                                                                                                                                                                                                                        |        |            |            |    |          |     |                |             |  |  |  |  |  |

|                   | I<br>I                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 Ba  | ase-T Data | Symbols    |    |          |     | l<br>I         |             |  |  |  |  |  |

| IDLE              | PR                                       | EAMBLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SFD    | DA         | SA         | LN | LLC DATA | FCS | SOI            | IDLE        |  |  |  |  |  |

### Figure 2 Frame Format

IDLE = [ NoTransitions ] PREAMBLE = [ 1 0 1 0 ...] 62 Bits Long SFD = [ 1 1 ] DA, SA, LN, LLC DATA, FCS = [ DATA ] SOI = [ 1 1 ] With No MID Bit Transition

On the transmit side for 100 Mbps operation, data is received on the controller interface from an external Ethernet controller per the format shown in Figure 3. The data is sent to the encoder for formatting. For TX operation, the encoded data is sent to the scrambler. The encoded and scrambled data is then sent to the TX transmitter. The transmitter converts the encoded and scrambled data into MLT3 ternary format. The transmitter then pre-shapes the output and drives the twisted pair cable.

For FX operation, the encoded data is converted to NRZI format, which drives a binary (two-level) signal to the fiber transceiver interface (PMD).

On the receive side for 100BaseTX operation, the TX receiver removes any high frequency noise from the input, equalizes the input signal to compensate for the low pass effects of the cable, and qualifies the data with a squelch algorithm. The TX receiver then converts the data from MLT3 coded twisted pair levels to internal digital levels. The output of the receiver then goes to a clock and data recovery block which recovers a clock from the incoming data, uses the clock to latch in valid data into the device, and converts the data back to NRZ data. The data is then unscrambled and decoded by the 4B5B decoder and descrambler, respectively, and output to an external Ethernet controller by the controller interface. 100Base FX receiver operation is the same as TX except there is no equalizer, descrambler, and has a separate ECL receiver.

10 Mbps operation is similar to the 100 Mbps operation, except:

- There is no scrambler/descrambler.

- The encoder/decoder is Manchester instead of 4B5B.

- The data rate is 10 Mbps instead of 100 Mbps.

- The twisted pair symbol data is two level Manchester instead of ternary MLT3.

The FX interface is disabled for 10 Mbps operation.

The AutoNegotiation block automatically configures each channel for either 100BaseTX or 10BaseT, and either Full or Half Duplex operation. This configuration is based on the capabilities selected for the channel and capabilities detected from the remote device connected to the channel.

The Management Interface (the MI serial port) is a two-pin bidirectional link through which configuration inputs can be set and channel status outputs read.

Each block plus the operating modes are described in more detail in the following sections. Since the L84225 can operate as a 100BaseFX, 100BaseTX, or 10BaseT device, each of the following sections describes the performance in both 100 and 10 Mbps modes.

# 2.2 Controller Interface

### 2.2.1 General

The L84225 has three interfaces to an external controller: Media Independent Interface (MII), Reduced pin MII (RMII), and Five Bit Interface (FBI). MII is the default interface. RMII is selected by asserting the RMII\_EN pin, a global control (all channels effected). FBI is selected, on a per port basis, by setting the bypass encoder bit in the MI serial port Channel Configuration register (Register 17).

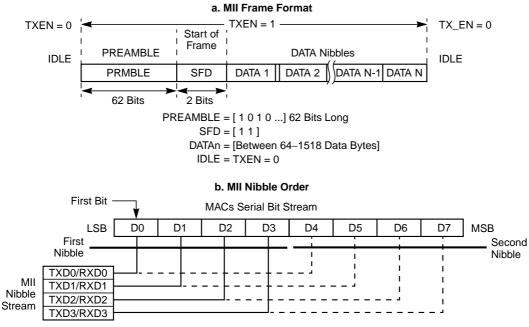

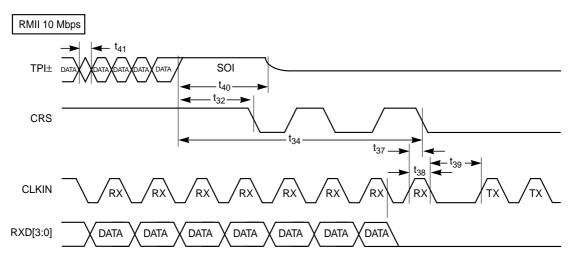

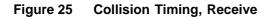

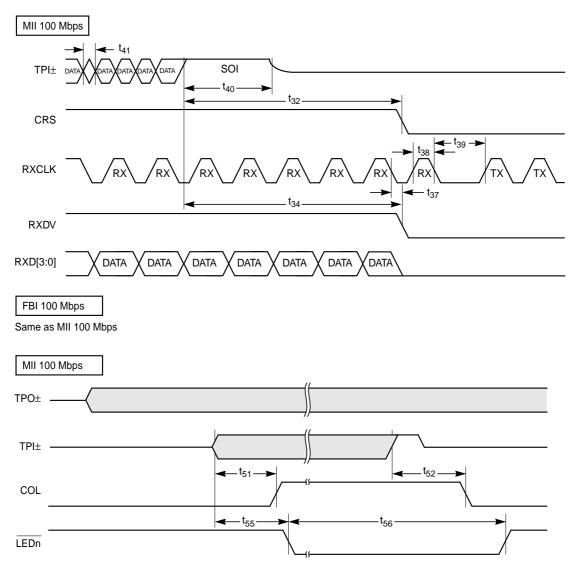

### 2.2.2 MII - 100 Mbps

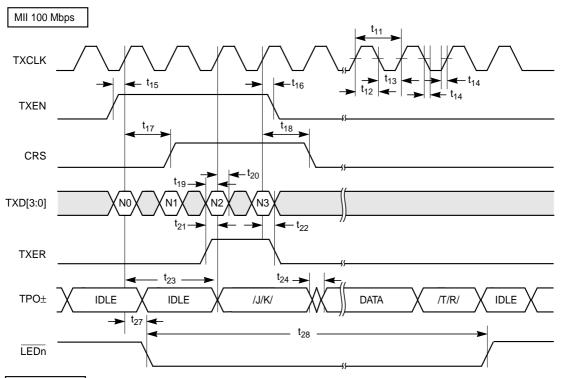

The MII is a nibble-wide packet data interface defined in IEEE 802.3. The L84225 meets all MII requirements outlined in IEEE 802.3. The L84225 can directly connect, without external logic, to any Ethernet controller or other device that also complies with the IEEE 802.3 MII specification. The MII frame format is shown in Figure 3.

#### c. Transmit Preamble and SFD Bits

| Signals |   | Bit Value |                |   |   |   |   |   |   |   |   |   |   |   |   |   |                |   |                 |                 |

|---------|---|-----------|----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------|---|-----------------|-----------------|

| TXD0    | Х | Х         | 1 <sup>1</sup> | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 <sup>2</sup> | 1 | D0 <sup>3</sup> | D4 <sup>3</sup> |

| TXD1    | Х | Х         | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0              | 0 | D1              | D5              |

| TXD2    | Х | Х         | 1              | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1              | 1 | D2              | D6              |

| TXD3    | Х | Х         | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0              | 1 | D3              | D7              |

| TXEN    | 0 | 0         | 1              | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1              | 1 | 1               | 1               |

1. 1st preamble nibble transmitted.

2. 1st SFD nibble transmitted.

3. 1st data nibble transmitted.

4. D0 thru D7 are the first 8 bits of the data field.

#### d. Receive Preamble and SFD Bits

| Signals |   | Bit Value |                |   |   |   |   |   |   |   |   |   |   |   |   |   |                |   |                 |                 |

|---------|---|-----------|----------------|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------|---|-----------------|-----------------|

| RXD0    | Х | Х         | 1 <sup>1</sup> | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 <sup>2</sup> | 1 | D0 <sup>3</sup> | D4 <sup>3</sup> |

| RXD1    | Х | Х         | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0              | 0 | D1              | D5              |

| RXD2    | Х | Х         | 1              | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1              | 1 | D2              | D6              |

| RXD3    | Х | Х         | 0              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0              | 1 | D3              | D7              |

| RXDV    | 0 | 0         | 1              | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1              | 1 | 1               | 1               |

1. 1st preamble nibble received. Depending on mode, device may eliminate either all or some of the preamble nibbles, up to 1st SFD nibble.

2. 1st SFD nibble received.

3. 1st data nibble received.

4. D0 thru D7 are the first 8 bits of the data field.

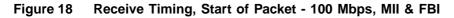

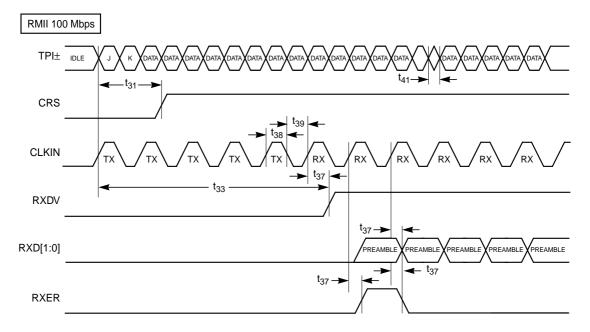

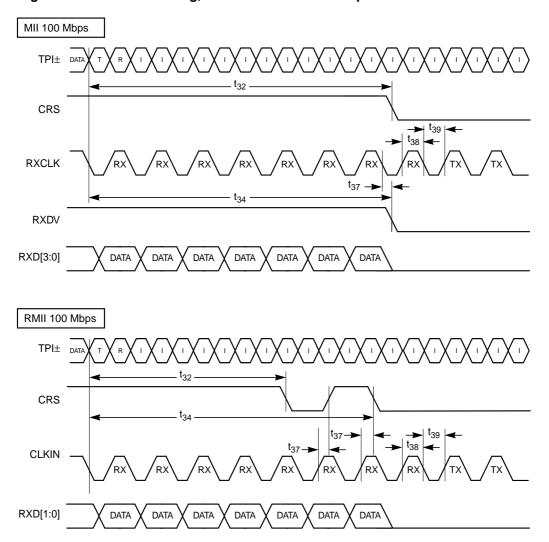

Functional Description Copyright © 1999-2002 by LSI Logic Corporation. All rights reserved. The MII consists of four transmit data bits (TXD[3:0]), transmit clock (TXCLK), transmit enable (TXEN), transmit error (TXER), four receive data bits (RXD[3:0]), receive clock (RXCLK), carrier sense (CRS), receive data valid (RXDV), receive data error (RXER), and collision (COL). The transmit clock (TXCLK) is a common signal for all four channels. All other signals are separate for each channel. The transmit and receive clocks operate at 25 MHz in 100 Mbps mode.

On the transmit side, the TXCLK output runs continuously at 25 MHz. When no data is to be transmitted, TXEN must be deasserted. While TXEN is deasserted, TXER and TXD[3:0] are ignored and no data is clocked into the device. When TXEN is asserted on the rising edge of TXCLK, data on TXD[3:0] is clocked into the device on rising edges of the TXCLK output clock. TXD[3:0] input data is nibble wide packet data whose format is specified in IEEE 802.3 and shown in Figure 3. When all packet data has been latched into the device, TXEN must be deasserted on the rising edge of TXCLK.

TXER is also clocked in on rising edges of the TXCLK clock. TXER is a transmit error signal which, when asserted, will substitute an error nibble in place of the normal data nibble that was clocked in on the TXD[3:0] nibble at the same time as the TXER assertion. The error nibble is the /H/ symbol, as defined in IEEE 802.3 and shown in Table 3.

Since CLKIN (input clock) generates TXCLK (output clock), TXD[3:0], TXEN, and TXER are also clocked in on the rising edges of CLKIN.

On the receive side, as long as a valid data packet is not detected, CRS and RXDV are deasserted and RXD[3:0] is held low. When the start of packet is detected, CRS is asserted on the falling edge of RXCLK. The assertion of RXDV indicates that valid data is available on RXD[3:0]. Data may be externally latched using the rising edge of RXCLK. The RXD[3:0] data has the same frame structure as the TXD[3:0] data, specified in IEEE 802.3 and shown in Figure 3. When the end of packet is detected, CRS and RXDV are deasserted, and RXD[3:0] is held low. CRS and RXDV also stay deasserted if the channel is in Link Fail state.

RXER is a receive error output that is asserted when certain errors are detected on a data nibble. RXER is asserted on the falling edge of RXCLK for the duration of the RXCLK clock cycle during which the nibble containing the error is output on RXD[3:0].

The collision output, COL, is asserted whenever the collision condition is detected.

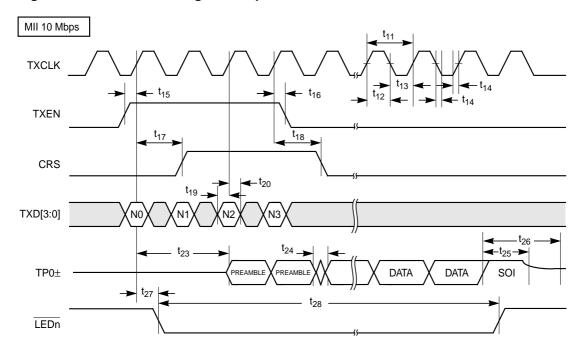

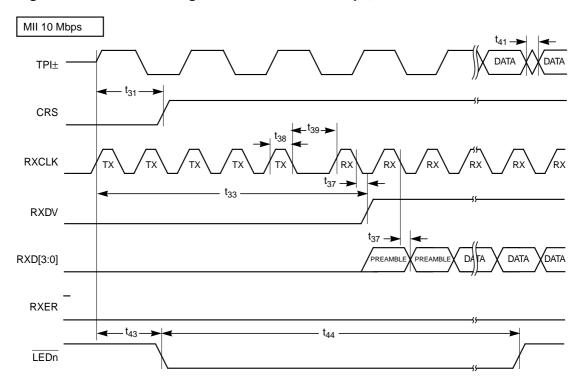

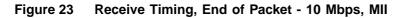

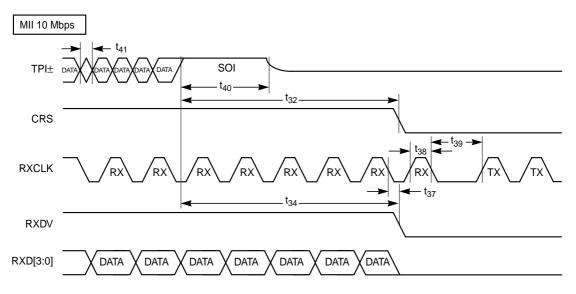

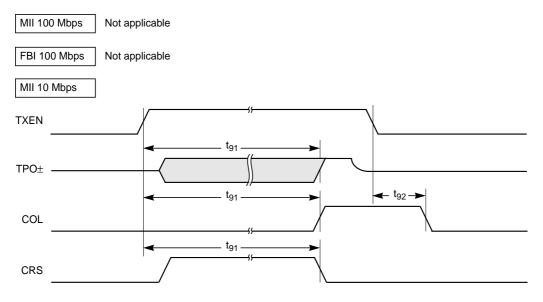

### 2.2.3 MII - 10Mbps

10 Mbps operation is identical to the 100 Mbps operation, except:

- TXCLK and RXCLK clock frequency is 2.5 MHz.

- TXER is ignored.

- RXER is disabled and always held low.

- Receive operation is modified as follows. On the receive side, when the squelch circuit determines that invalid data is present on the TP (Twisted Pair) inputs, the receiver is idle. During idle, RXCLK follows TXCLK, RXD[3:0] is held low, and CRS and RXDV are deasserted. When a start of packet is detected on the TP receive inputs, CRS is asserted and the clock recovery process starts on the incoming TP input data. After the receive clock has been recovered from the data, the RXCLK is switched over to the recovered clock output and the data valid signal RXDV is asserted on a falling edge of RXCLK. Once RXDV is asserted, valid data is clocked out on RXD[3:0] on falling edges of the RXCLK clock. The RXD[3:0] data has the same packet structure as the TXD[3:0] data and is formatted as specified in IEEE 802.3 and shown in Figure 3. When the end of packet is detected, CRS and RXDV are deasserted. CRS and RXDV also stay deasserted as long as the channel is in the Link Fail State.

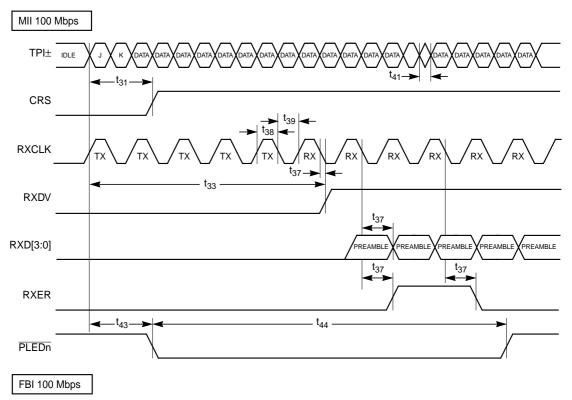

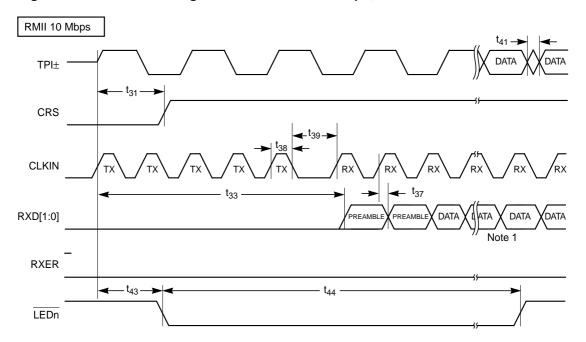

### 2.2.4 RMII - 100 Mbps

The RMII is a reduced pin count version of the MII defined by an industry group, the RMII Consortium. The RMII is a two-bit-wide packet data interface that operates at 50 Mhz. The L84225 meets all the RMII requirements outlined in the RMII Consortium specifications and can directly connect to any Ethernet controller that also complies with the RMII specifications.

The RMII is similar to the MII, except:

- The data path is two bits wide instead of four.

- Transmit and receive data is passed over TXD[1:0] and RXD[1:0] pins, respectively.

- The CLKIN clock frequency must be 50 MHz instead of 25 MHz.

- All timing for both transmit and receive is referenced to a single clock on CLKIN instead of TXCLK for transmit and RXCLK for receive.

- An elastic buffer is present in the receive data path to account for any difference between the CLKIN and receive data frequencies. The elastic buffer is 32 bits in length. Input data from the receiver fills the buffer to a predetermined threshold level before data is passed to the RMII outputs. This threshold level can be configured to either 4 bits or 16 bits by appropriately setting the RMII threshold select bit in the MI serial port Global Configuration register.

- The MII RXDV and CRS inputs are combined into one signal that is outputted on the CRS pin. CRS is asserted active high when incoming packet data is detected on the receive inputs. It stays asserted high until packet data is no longer detected, and it toggles at a 25 MHz rate (low for first di-bit of MII nibble, high for second, etc.) from the end of the packet data detection until end of valid data transfer from the elastic buffer. During this toggling interval, valid data is still being output on RXD[1:0]. CRS is finally deasserted when all data has been output from the internal elastic buffer on RXD[1:0].

- RXD[1:0]=00 from start of CRS until valid data is ready to be output.

- TXEN to CRS loopback is disabled.

- Any packet that contains an error will assert RXER and substitute RXD[1:0]=10 for all the data bits from the error detect point until the end of packet.

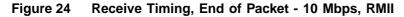

### 2.2.5 RMII - 10 Mbps

10 Mbps RMII operation is identical to 100 Mbps RMII operation, except:

- The CLKIN frequency remains at 50 Mhz (same as 100 Mbps operation).

- Each data di-bit must be input on TXD[1:0] for ten consecutive CLKIN cycles.

- Each data di-bit will be output on RXD[1:0] for ten consecutive CLKIN cycles.

### 2.2.6 FBI - 100 Mbps

The Five Bit Interface (FBI), or Symbol Interface, is a five bit wide interface produced when the 4B5B encoder/ decoder is bypassed. The FBI is primarily used for repeaters or Ethernet controllers that have integrated encoder/decoders.

The FBI is identical to the MII, except:

- The FBI data path is five bits wide, not nibble wide like the MII.

- TXER pin is changed to be the fifth transmit data bit, TXD4.

- RXER pin is changed to be the fifth receive data bit, RXD4.

- CRS is asserted as long as the device is in the Link Pass state (CRS no longer asserted/deasserted at beginning/end of packet).

- COL is not valid.

- RXDV is not valid.

- TXEN is ignored.

### 2.2.7 FBI - 10 Mbps

The FBI is not available in 10 Mbps mode.

### 2.2.8 Selection of MII, RMII, or FBI

MII is the default interface to the MAC controller. RMII is selected by asserting the RMII\_EN pin, a global control.

The FBI is automatically enabled when the 4B5B encoder/ decoder is bypassed. Bypassing the encoder/decoder passes the 5B symbols between the receiver/transmitter directly to the FBI without any alteration or substitutions. The 4B5B encoder/decoder can be bypassed by setting the bypass encoder bit in the MI serial port Channel Configuration register.

When the FBI is enabled, it may also be desirable to bypass the scrambler/descrambler and disable the internal CRS loopback function. The scrambler/ descrambler can be bypassed by setting the bypass scrambler bit in the MI serial port Channel Configuration register. The internal CRS loopback can be disabled by setting the TXEN to CRS loopback disable bit in the MI serial port Channel Configuration register.

### 2.2.9 MII Disable

The MII and FBI inputs and outputs can be disabled by setting the MII disable bit in the MI serial port Control register. When the MII is disabled, the inputs are ignored, the outputs are placed in high impedance state, and the TP output is high impedance.

### 2.2.10 TXEN to CRS Loopback Disable

The internal TXEN to CRS loopback can be disabled by appropriately setting the TXEN to CRS loopback disable bit in the MI serial port Channel Configuration register. TXEN to CRS loopback is disabled in RMII mode.

### 2.3 Encoder

### 2.3.1 4B5B Encoder - 100 Mbps

100BaseTX and 100BaseFX require that the data be 4B5B encoded. 4B5B coding converts the 4-bit data nibbles into 5-bit data words. The mapping of the 4B nibbles to the 5B code words is specified in IEEE 802.3 and shown in Table 3. The 4B5B encoder on the L84225 takes 4B nibbles from the controller interface, converts them into 5B words according to Table 3, and sends the 5B words to the scrambler. The 4B5B encoder also substitutes the first eight bits of the preamble with the SSD delimiters (/J/K/ symbols) and adds an ESD delimiter (/T/R/ symbols) to the end of each packet, as defined in IEEE 802.3 and shown in Figure 2. The 4B5B encoder also fills the period between packets, called the idle period, with a continuous stream of idle symbols, as shown in Figure 2.

| Symbol Name | Description | 5B Code | 4B Code |  |

|-------------|-------------|---------|---------|--|

| 0           | Data 0      | 11110   | 0000    |  |

| 1           | Data 1      | 01001   | 0001    |  |

| 2           | Data 2      | 10100   | 0010    |  |

| 3           | Data 3      | 10101   | 0011    |  |

| 4           | Data 4      | 01010   | 0100    |  |

#### Table 3 4B/5B Symbol Mapping

L84225 Quad 100BaseTX/FX/10BaseT Phys. Layer Device - Technical Manual Copyright © 1999-2002 by LSI Logic Corporation. All rights reserved.

| Symbol Name | Description   | 5B Code                 | 4B Code           |  |

|-------------|---------------|-------------------------|-------------------|--|

| 5           | Data 5        | 01011                   | 0101              |  |

| 6           | Data 6        | 01110                   | 0110              |  |

| 7           | Data 7        | 01111                   | 0111              |  |

| 8           | Data 8        | 10010                   | 1000              |  |

| 9           | Data 9        | 10011                   | 1001              |  |

| A           | Data A        | 10110                   | 1010              |  |

| В           | Data B        | 10111                   | 1011              |  |

| С           | Data C        | 11010                   | 1100              |  |

| D           | Data D        | 11011                   | 1101              |  |

| E           | Data E        | 11100                   | 1110              |  |

| F           | Data F        | 11101                   | 1111              |  |

|             |               |                         |                   |  |

| I           | ldle          | 11111                   | 0000              |  |

|             |               |                         |                   |  |

| J           | SSD #1        | 11000                   | 0101              |  |

| К           | SSD #2        | 10001                   | 0101              |  |

| Т           | ESD #1        | 01101                   | 0000              |  |

| R           | ESD #2        | 00111                   | 0000              |  |

| Н           | Halt          | 00100                   | Undefined         |  |

|             |               |                         |                   |  |

|             | Invalid codes | All others <sup>1</sup> | 0000 <sup>1</sup> |  |

Table 34B/5B Symbol Mapping (Cont.)

1. These 5B codes are not used. For decoder, these 5B codes are decoded to 4B 0000. For encoder, 4B 0000 is encoded to 5B 11110, as shown in symbol Data 0.

### 2.3.2 Manchester Encoder - 10 Mbps

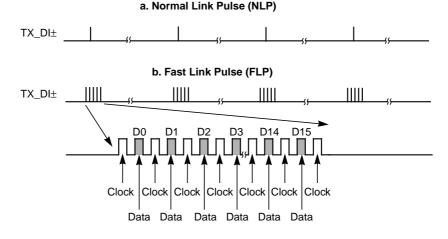

The Manchester encoding process combines clock and NRZ data such that the first half of the data bit contains the complement of the data, and the second half of the data bit contains the true data, as specified in IEEE 802.3. This guarantees that a transition always occurs in the middle of the bit cell. The L84225 Manchester encoder converts the 10 Mbps NRZ data from the controller interface into a single data stream for the TP transmitter and adds a start of idle pulse (SOI) at the end of the packet as specified in IEEE 802.3 and shown in Figure 2. The Manchester encoding process is only done on actual packet data, and the idle period between packets is not Manchester encoded, but filled with link pulses.

### 2.3.3 Encoder Bypass

The 4B5B encoder can be bypassed by setting the bypass encoder/decoder bit in the MI serial port Channel Configuration register. When this bit is set to bypass the encoder/decoder, 5B code words are passed directly from the controller interface to the scrambler without any alterations. Setting this bit automatically places the device in the FBI mode, as described in Section 2.2, "Controller Interface," page 16.

### 2.4 Decoder

### 2.4.1 4B5B Decoder - 100 Mbps

Since the FX or TX input data is 4B5B encoded on the transmit side, it must also be decoded by the 4B5B decoder on the receive side. The mapping of the 5B nibbles to the 4B code words is specified in IEEE 802.3 and shown in Table 3. The L84225 4B5B decoder takes the 5B code words from the descrambler, converts them into 4B nibbles per Table 3, and sends the 4B nibbles to the controller interface. The 4B5B decoder also strips off the SSD delimiter (/J/K/ symbols) and replaces them with two 4B Data 5 nibbles (/5/ symbol), and strips off the ESD delimiter (/T/R/ symbols) and replaces it with two 4B Data 0 nibbles (/I/ symbol), per IEEE 802.3 specifications and shown in Figure 2.

The 4B5B decoder detects SSD, ESD and, codeword errors in the incoming data stream as specified in IEEE 802.3. These errors are indicated by asserting RXER output while the errors are being transmitted across RXD[3:0], and they are also indicated by setting SSD,

ESD, and codeword error bits in the MI serial port Channel Status Output register.

### 2.4.2 Manchester Decoder - 10 Mbps

In Manchester coded data, the first half of the data bit contains the complement of the data, and the second half of the data bit contains the true data. The L84225 Manchester decoder converts the single data stream from the TP receiver into NRZ data for the controller interface by decoding the data and stripping off the SOI pulse. Since the clock and data recovery block has already separated the clock and data from the TP receiver, the Manchester decoding process to NRZ data is inherently performed by that block.

### 2.4.3 Decoder Bypass

The 4B5B decoder can be bypassed by setting the bypass encoder/decoder bit in the MI serial port Channel Configuration register. When this bit is set to bypass the encoder/decoder:

- 5B code words are passed directly to the controller interface from the descrambler without any alterations.

- CRS is asserted whenever the device is in the Link Pass state.

### 2.5 Clock and Data Recovery

### 2.5.1 Clock Recovery - 100 Mbps

Clock recovery is done with a PLL. If there is no valid data present on the receive inputs, the PLL is locked to the 25 MHz TXCLK. When valid data is detected on the receive inputs with the squelch circuit and when the adaptive equalizer has settled, the PLL input is switched to the incoming data stream. The PLL then recovers a clock by locking onto the transitions of the incoming signal. The recovered clock frequency is a 25 MHz nibble clock, and that clock is output as the controller interface signal RXCLK.

For FX operation, when the SD pin is asserted, the PLL input is switched to the incoming data on the input.

### 2.5.2 Data Recovery - 100 Mbps

Data recovery is performed by latching in data from the receive inputs with the recovered clock extracted by the PLL. The data is then converted from a single bit stream into a nibble widedone by latching in valid data from the receiver with the recovered clock extracted by the PLL. The data is then converted from a single bit stream into a nibblewide data word.

### 2.5.3 Clock Recovery - 10 Mbps

The clock recovery process for 10 Mbps mode is identical to the 100 Mbps mode, except:

- The recovered clock frequency is a 2.5 MHz nibble clock.

- The PLL is switched from TXCLK to the TP input when the squelch indicates valid data.

- The PLL locks onto the preamble signal in less than 12 transitions (bit times).

- Some of the preamble data symbols are lost while the PLL is locking onto the preamble. However, the data receiver block recovers enough preamble symbols to pass at least 6 nibbles of preamble to the controller interface, as shown in Figure 3.

### 2.5.4 Data Recovery

The data recovery process for 10 Mbps mode is identical to the 100 Mbps mode, except, the recovered clock frequency is a 2.5 MHz nibble clock. As mentioned in Section 2.4.2, "Manchester Decoder - 10 Mbps," page 25, the data recovery process inherently performs decoding of Manchester encoded data from the TP inputs.

### 2.6 Scrambler

### 2.6.1 100 Mbps

100BaseTX requires scrambling to reduce the radiated emissions on the twisted pair. The L84225 scrambler takes the encoded data from the 4B5B encoder, scrambles it per the IEEE 802.3 specifications, and sends it to the TP transmitter. The scrambler circuitry of the L84225 is designed

so that none of the individual scrambler sections on-chip will be synchronous with the others to minimize EMI issues.

### 2.6.2 10 Mbps

A scrambler is not used in 10 Mbps mode.

### 2.6.3 Scrambler Bypass

The scrambler can be bypassed by setting the bypass scrambler/descrambler bit in the MI serial port Channel Configuration register. When this bit is set, the 5B data bypasses the scrambler and goes directly from the 4B5B encoder to the twisted pair transmitter.

### 2.7 Descrambler

### 2.7.1 100 Mbps

The L84225 descrambler takes the scrambled data from the data recovery block, descrambles it per the IEEE 802.3 specifications, aligns the data on the correct 5B word boundaries, and sends it to the 4B5B decoder.

The algorithm for synchronization of the descrambler is the same as the algorithm outlined in the IEEE 802.3 specification. Once the descrambler is synchronized, it will maintain synchronization as long as enough descrambled idle pattern 1's are detected within a given interval. To stay in synchronization, the descrambler needs to detect at least 25 consecutive descrambled idle pattern 1's in a 1 ms interval. If 25 consecutive descrambled idle pattern 1's are not detected within the 1 ms interval, the descrambler goes out of synchronization and restarts the synchronization process.

If the descrambler is in the unsynchronized state, the descrambler loss of synchronization detect bit is set in the MI serial port Channel Status Output register to indicate this condition. Once this bit is set, then it will stay set until the descrambler achieves synchronization.

A descrambler is not used for FX operation.

### 2.7.2 10 Mbps

A descrambler is not used in 10 Mbps mode.

### 2.7.3 Descrambler Bypass

The descrambler can be bypassed by setting the bypass scrambler/descrambler bit in the MI serial port Channel Configuration register. When this bit is set, the data bypasses the descrambler and goes directly from the TP receiver to the 4B5B decoder.

### 2.8 Twisted Pair Transmitter

### 2.8.1 100 Mbps

The TP transmitter consists of an MLT3 encoder, waveform generator, and line driver.

The MLT3 encoder converts the NRZI data from the scrambler into a three level code required by IEEE 802.3. MLT3 coding uses three levels and converts 1's to transitions between the three levels, and converts 0's to no transitions or changes in level.

The purpose of the waveform generator is to shape the transmit output pulse. The waveform generator takes the MLT3 three level encoded waveform and uses an array of switched current sources to control the shape of the twisted pair output signal in order to meet IEEE 802.3 requirements. The output of the switched current sources then goes through a low pass filter in order to "smooth" the output and remove any high frequency components. In this way, the waveform generator preshapes the output waveform transmitted onto the twisted pair cable to meet the pulse template requirements outlined in IEEE 802.3. The waveform generator eliminates the need for any external filters on the TP transmit output. The line driver converts the shaped and smoothed waveform to a current output that can drive 100 meters of category 5 unshielded twisted pair cable or 150 ohm shielded twisted pair cable.

### 2.8.2 10 Mbps

The TP transmitter operation in 10 Mbps mode is much different from the 100 Mbps transmitter. Even so, the transmitter still consists of a waveform generator and line driver.

28 of 118

L84225 Quad 100BaseTX/FX/10BaseT Phys. Layer Device - Technical Manual

April, 2002

Copyright © 1999-2002 by LSI Logic Corporation. All rights reserved.

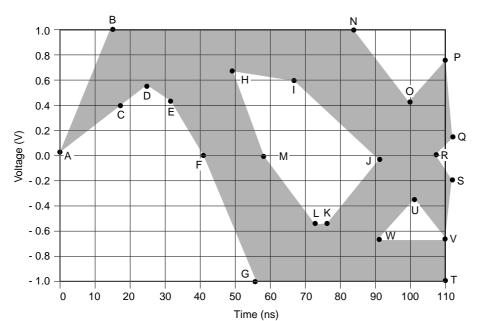

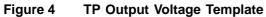

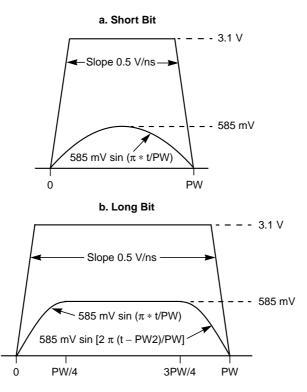

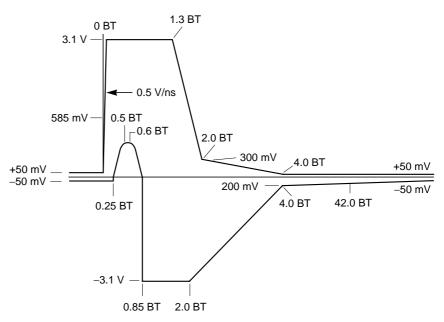

The purpose of the waveform generator is to shape the output transmit pulse. The waveform generator consists of a ROM, DAC, clock generator, and filter. The DAC generates a stair-stepped representation of the desired output waveform. The stairstepped DAC output then goes through a low pass filter in order to "smooth" the DAC output and remove any high frequency components. The DAC values are determined from the ROM output; the ROM outputs are chosen to shape the pulse to the desired template and are clocked into the DAC at high speed by the clock generator. In this way, the waveform generator pre-shapes the output waveform to be transmitted onto the twisted pair cable to meet the pulse template requirements outlined in IEEE 802.3 Clause 14 and also shown in Figure 4. The waveshaper replaces and eliminates external filters on the TP transmit output.

The line driver converts the shaped and smoothed waveform to a current output that can drive 100 meters of category 3/4/5 100 Ohm unshielded twisted pair cable or 150 Ohm shielded twisted pair cable, without any external filters. During the idle period, no output signal is transmitted on the TP outputs (except link pulse).

### 2.9 Twisted Pair Receiver

### 2.9.1 Receiver - 100 Mbps

The TP receiver detects input signals from the twisted pair input and converts it to a digital data bit stream ready for clock and data recovery. The receiver can reliably detect data from a 100Base-TX compliant transmitter that has been passed through 0-100 meters of 100-Ohm category 5 UTP.

The 100 Mbps receiver consists of an adaptive equalizer, baseline wander correction circuit, comparators, and MLT- 3 decoder. The TP inputs first go to an adaptive equalizer. The adaptive equalizer compensates for the low pass characteristic of the cable, and it has the ability to adapt and compensate for 0-100 meters of category 5, 100 Ohm UTP. The baseline wander correction circuit restores the DC component of the input waveform that was removed by external transformers. The comparators convert the equalized signal back to digital levels and are used to qualify the data with the squelch circuit. The MLT-3 decoder takes the three level MLT-3 digital data from the

comparators and converts it back to normal digital data to be used for clock and data recovery.

| Reference | Time (ns)<br>Internal MAU | Voltage (V) | Reference | Time (ns)<br>Internal MAU | Voltage (V) |

|-----------|---------------------------|-------------|-----------|---------------------------|-------------|

| A         | 0                         | 0           | М         | 61                        | 0           |

| В         | 15                        | 1.0         | N         | 85                        | 1.0         |

| С         | 15                        | 0.4         | 0         | 100                       | 0.4         |

| D         | 25                        | 0.55        | Р         | 110                       | 0.75        |

| E         | 32                        | 0.45        | Q         | 111                       | 0.15        |

| F         | 39                        | 0           | R         | 111                       | 0           |

| G         | 57                        | -1.0        | S         | 111                       | -0.15       |

| н         | 48                        | 0.7         | Т         | 110                       | -1.0        |

| I         | 67                        | 0.6         | U         | 100                       | -0.3        |

| J         | 89                        | 0           | V         | 110                       | -0.7        |

| К         | 74                        | -0.55       | W         | 90                        | -0.7        |

| L         | 73                        | -0.55       |           |                           |             |

30 of 118 April, 2002 L84225 Quad 100BaseTX/FX/10BaseT Phys. Layer Device - Technical Manual Copyright © 1999-2002 by LSI Logic Corporation. All rights reserved.

### 2.9.2 Receiver - 10 Mbps

The 10 Mbps mode receiver is much simpler than the 100 Mbps mode receiver and is identical to the 100 Mbps receiver except:

- The adaptive equalizer is disabled and bypassed.

- The baseline wander correction circuit is disabled.

- The 10 Mbps receiver is able to detect input signals from the twisted pair cable that are within the template specified in IEEE 802.3 Clause 14 and shown in Figure 5.

- The output of the squelch comparator is used for squelch, link pulse detect, SOI detect, reverse polarity detect.

- The data comparator is a zero crossing comparator whose output is used for clock and data recovery.

### 2.9.3 Squelch - 100 Mbps

The squelch block determines whether the input contains valid data. The 100 Mbps TX squelch is one of the criteria used to determine link integrity. The squelch comparators compare the TX inputs against fixed positive and negative thresholds, called squelch levels.

The output from the squelch comparator goes to a digital squelch circuit, which determines whether the receive input data on that channel is valid. If the data is invalid, the receiver is in the squelched state. If the input voltage exceeds the squelch levels at least four times with alternating polarity within a 10 us interval, the data is considered to be valid by the squelch circuit and the receiver now enters into the unsquelch state.

In the unsquelch state, the receive threshold level is reduced by approximately 30% for noise immunity reasons and is called the unsquelch level. When the receiver is in the unsquelch state the input signal is considered valid.

The device stays in the unsquelch state until loss of data is detected. Loss of data is detected if no alternating polarity unsquelch transitions are detected during any 10 us interval. When the loss of data is detected, the receive squelch level is re-established.

### 2.9.4 Squelch - 10 Mbps

The TP squelch algorithm for 10 Mbps mode is identical to the 100 Mbps mode, except:

• The 10 Mbps squelch algorithm is not used for link integrity, but to sense the beginning of a packet.

- The receiver goes into the unsquelch state if the input voltage exceeds the squelch levels for three bit times with alternating polarity within a 50-250 ns interval.

- The receiver goes into the squelch state when SOI is detected.

- Unsquelch detection has no affect on link integrity, link pulses are used for that in 10 Mbps mode.

- Start of packet is determined when the receiver goes into the unsquelch state and CRS is asserted.

- The receiver meets the squelch requirements defined in IEEE 802.3 Clause 14.

### 2.9.5 Receive Level Adjust

The receiver squelch and unsquelch levels can be lowered by 4.5 dB by setting the receive level adjust bit in the MI serial port Channel Configuration register. By setting this bit, the device can support cable lengths exceeding 100 meters.

### 2.10 Fiber Interface

### 2.10.1 General

The Fiber Interface implements the 100BaseFX function defined in IEEE 802.3.

The Fiber Interface consists of three signals: (1) a differential PECL data output (FXOP/FXON), (2) a differential PECL data input (FXIP/FXIN), and (3) a PECL signal detect (SD/FXEN).

The Fiber Interface section consists of four blocks: (1) transmitter, (2) receiver, (3) signal detect, and (4) far end fault.

The Fiber Interface can be independently selected for each channel with the SD/FXEN\_[3:0] pins.

The Fiber Interface is disabled in 10Mbps mode. AutoNegotiation and the scrambler/descrambler are disabled when the Fiber Interface is enabled.

The Fiber Interface meets all IEEE 802.3 requirements.

### 2.10.2 Transmitter

The FX transmitter converts data from the 4B5B encoder into binary NRZI data and outputs the data onto the FXOP/FXON pins for each channel. The output driver is a differential current source that will drive a 100-ohm load to ECL levels. The FXOP/FXON pins can directly drive an external fiber optic transceiver. The FX transmitter meets all the requirements defined in IEEE 802.3.

The FX transmit output current level is derived from an internal reference voltage and the external resistor on REXT pin.

### 2.10.3 Receiver

The FX receiver (1) converts the differential ECL inputs on the FXIP/FXIN pins for each channel to a digital bit stream, (2) validates the data on FXIP/FXIN with the SD/ FXEN input pin for each channel, and (3) enable/disables the Fiber Interface with the SD/FXEN pin for each channel. The FX receiver meets all requirements defined in IEEE 802.3.

The input to the FXIP/FXIN pins can be directly driven from a fiber optic transceiver and first goes to a comparator. The comparator compares the input waveform against the internal ECL threshold levels to produce a low jitter serial bit stream with internal logic levels. The data from the comparator output is then passed to the clock and data recovery block provided the signal detect input, SD/FXEN, is asserted. The signal detect function is described in the next section.

### 2.10.4 Signal Detect

The FX receiver has a signal detect input pin, SD/FXEN, for each channel which indicates whether the incoming data on FXIP/FXIN is valid or not for that channel. The SD/FXEN pin can be driven directly from an external fiber optic transceiver and meets all requirements defined in the IEEE 802.3 specifications.

The SD/FXEN input goes directly to a comparator. The comparator compares the input waveform against the internal ECL threshold level to produce a digital signal with internal logic levels. The output of the signal detect comparator then goes to the link integrity and squelch blocks. If the signal detect input is asserted, the channel is placed in the Link Pass state and the input data on FXIP/FXIN is determined to be valid. If the

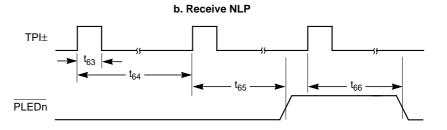

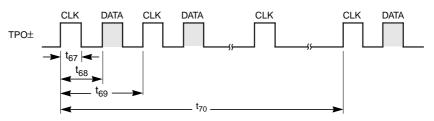

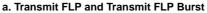

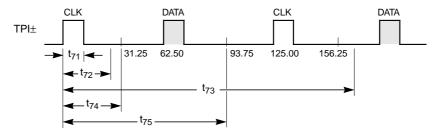

signal detect input is deasserted, the channel is placed in the Link Fail state and the input data on FXIP/FXIN is determined to be invalid.