T-52-33-15

# IMP82C206

# IMP82C206 — Integrated Peripherals Controller

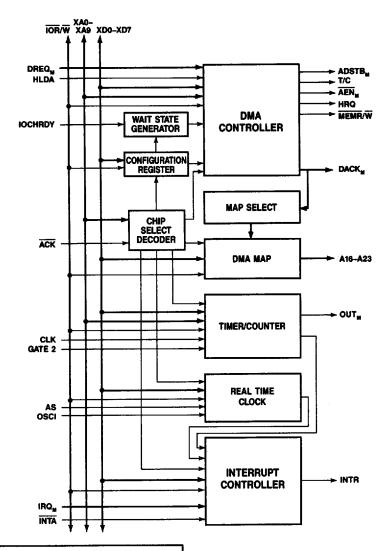

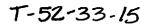

The IMP82C206 Integrated Peripheral Controller is a peripheral interface circuit. It contains two 8237 Direct Memory Access (DMA) Controllers, two 8259 Interrupt Controllers, one 8254 Timer/Counter, one MC146818 Real Time Clock, and a 74LS612 memory chip as well as several other TTL/SSI interface logic chips. In fact, all of the peripherals attached to the peripheral bus (X Bus) of the AT architecture are available in this one chip. External devices transfer information directly from the system memory to improve system performance. This chip also offers improved speed performance and additional enhanced features such as an additional 64 bytes of user RAM for the Real Time Clock and reduced recovery specifications for the DMA Controller, Timer/Counter, and Interrupt Controllers.

#### **Features**

- Compatible with IBM PC/AT

- Provides the fully-compatible equivalent of Intel's 8237 DMA Controller, 8259 Interrupt Controller, 8254 Timer/Counter, and Motorola's 146818 Real Time Clock

- Variable wait state for DMA cycles

- Programmable delays for CPU access to internal registers

- Option to select 4 or 8 MHz clock

- All CMOS implementation

- 16-bit to 8-bit transfers in bus conversion logic

- Detection logic checking and parity generation

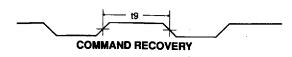

- Accelerated recovery time of 120 ns

IBM, AT are the trademarks of International Business Machines. Intel is the trademark of Intel Corporation. Motorola is a trademark of Motorola Computers and Electronics, Inc.

Pin

35-43

34

Name

XAB-XAO

XA9

Pin

1/0

**Number Type Description**

3. Timer/Counters registers -

contents or states of the

4. Real Time Clock internal registers and RAM

5. Page registers of memory

During the interrupt sequence, the interrupt controllers output

the interrupt vector byte on the

**ADDRESS BUS.** The system

various registers of the IMP82C206. During a non-DMA cycle, A9-A0 are used to address

address bus is used to address

configuration registers and the internal registers of the DMA

Controller, Interrupt Controller,

counters

mapper

data bus.

|         | criptions     |             | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                            |         |      |     | Timer/Counter, RTC, RAM, and Memory Mapper. In the active DMA cycle, A7-A0 are outputs and carry address information for DMA channels 0-3. Correspond-                                                                                                                                                                                                                                                                             |

|---------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                |         |      |     | ingly, A8-A1 are address outputs<br>for 16-bit DMA channels 5-7.                                                                                                                                                                                                                                                                                                                                                                   |

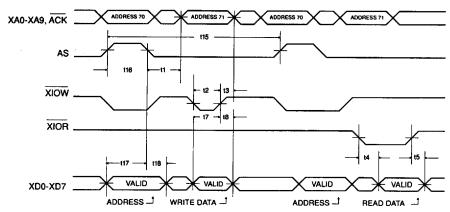

| XD7-XD0 | 24-31         | 1/0         | DATA BUS. The Data Bus lines are tri-state bidirectional lines connected to the system data                                                                                                                                                                                                                                                |         |      |     | They are tied to the external address bus (XA bus) in the PC/AT environment.                                                                                                                                                                                                                                                                                                                                                       |

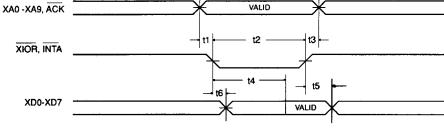

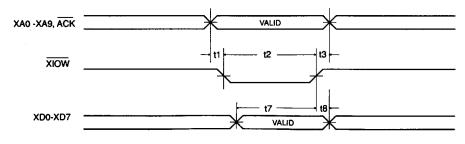

|         |               |             | bus (XD bus in a PC/AT design).  During DMA cycles, the first eight bits of the address are output onto the data bus to be strobed into an external latch by the Address Strobe (ADSTB8 or ADSTB16). During DMA trans-                                                                                                                     | XIOR    | 54   | I/O | I/O READ. As an active low input, this signal is used to access the internal registers of the IMP82C206. During a DMA transfer from a peripheral, the signal becomes an output generated by the DMA Controller.                                                                                                                                                                                                                    |

|         |               |             | fers, data enters the DMA Con-<br>troller on the data bus (read<br>from memory or peripheral) or<br>leaves the DMA Controller on<br>the data bus (write to memory<br>or peripheral).                                                                                                                                                       | XIOW    | . 52 | I/O | I/O WRITE. This active low input is used to write the internal registers of the IMP82C206. During a DMA transfer to a peripheral, the signal becomes an output generated by the DMA Controller.                                                                                                                                                                                                                                    |

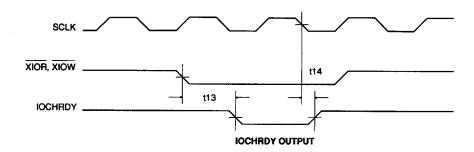

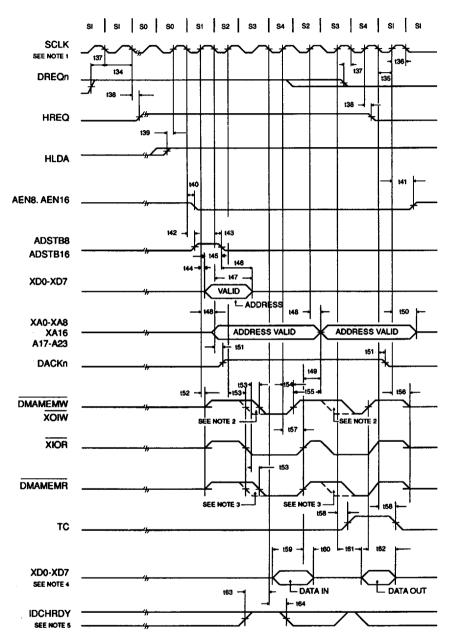

|         |               |             | During I/O operations, the data bus is used as an input (writing) or output (reading) to the following:  1. DMA Controller registers — Address register — Status register — Temporary register — Word Count register  2. Three Interrupt Controller registers — Interrupt Request register — In Service register — Interrupt Mask register | IOCHRDY | 68   | I/O | I/O CHANNEL READY. When used as an input, a low on IOCHRDY causes the internal DMA ready signal to go low asynchronously (not ready). When IOCHRDY goes high, internal DMA Ready goes high one DMA clock cycle later. This signal is used as an input to the wait state generation logic to extend memory read and write pulses during DMA transfers. To ensure reliability, IOCHRDY must satisfy set-up and hold times of DMACLK. |

| Name      | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Name                                          | Pin<br>Number               | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

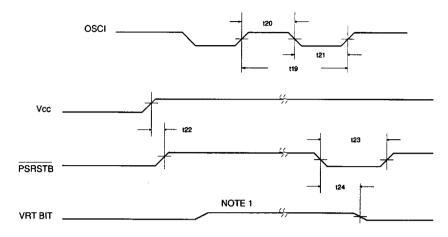

|           |               |             | As an output, this pin is an open drain output and provides an active low output whenever any register is accessed. This output will remain low for a programmed number of SCLK cycles and then go high, if pulled up by an external register. IOCHRDY provides a means of introducing a programmed number of wait-states (determined by bits 7-6 of Configuration Register 0 and bit 2 of Configuration Register 1) for I/O cycles to the IMP82C206.  In the PC/AT's environment, this pin should be wire-ored to the PC/ATS IOCHRDY signal. | PSRSTB                                        | 15                          | l           | POWER SENSE. The Power Sense pin establishes the condition of the control registers when power is applied to the device. When PSRSTB and TEST are low, the following occurs:  — Periodic Interrupt Enable (PIE bit is cleared to zero.  — Periodic Interrupt Flag (PF) bit is cleared to zero.  — Alarm interrupt Enable (AIE) bit is cleared to zero.  — Alarm Interrupt Flag (AF) bit is cleared to zero.  — Update ended Interrupt Enable (UIE) bit is cleared |

| ACK (MSE) | 33            | l           | MODULE SELECT ENABLE. The Module Select Enable signal, when high, enables the select function on one of the modules (DMA Controller, interrupt Controller CTC, RTC, DMA Page register, or the Configuration registers) for I/O reads and writes. When low, the IMP82C206 is essentially disconnected from the                                                                                                                                                                                                                                 |                                               |                             |             | to zero.  — Update ended Interrupt Flag (UF) bit is cleared to zero.  — Interrupt Request status Flag (IRQF) is cleared to zero.  — VRT bit in Register D is cleared to zero.  In the PC/AT environment, this pin should be tied to the battery back-up circuit.                                                                                                                                                                                                  |

|           |               |             | system bus; read and write signals are ignored. The IMP82C206, at this time, could be performing an active DMA or an interrupt cycle.  In the PC/AT environment, this pin is tied to the ACK signal.                                                                                                                                                                                                                                                                                                                                          | PWRGD                                         | 14                          | 1           | POWER GOOD. The Power<br>Good pin must be high for<br>bus cycles in which the CPU<br>accesses the IMP82C206. When<br>PWRGD is low, all input and out-<br>put pins are disconnected from<br>the processor. OSCI remains<br>connected to provide battery-                                                                                                                                                                                                           |

| AS        | 71            | ı           | ADDRESS STROBE. Active high<br>Address Strobe is used to strobe<br>an address pointer into an inter-<br>nal latch. The positive pulse fall-<br>ing edge latches the address                                                                                                                                                                                                                                                                                                                                                                   | TEST                                          | 17                          | ı           | backed timekeeping.  TEST. Active high Test is an input used for test purposes only. It is tied low for normal operation.                                                                                                                                                                                                                                                                                                                                         |

| OSCI      | 72            | ı           | from the XD bus.  OSCILLATOR INPUT. The Oscillator Input is the time base for the clock/calendar. This frequency is determined in Register A of the RTC.                                                                                                                                                                                                                                                                                                                                                                                      | INTA                                          | 16                          | ı           | INTERRUPT ACKNOWLEDGE. The active low Interrupt Acknowledge is issued by the CPU. The interrupt acknowledge sequence enables the Interrupt Controller to place its vector on the data bus.                                                                                                                                                                                                                                                                        |

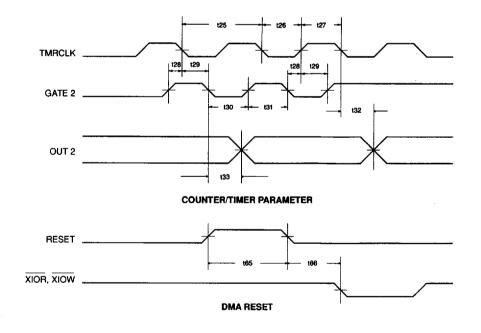

| RESET     | 18            | ı           | External square waves of 32.768 KHz may be connected to this input.  RESET. Active high RESET per-                                                                                                                                                                                                                                                                                                                                                                                                                                            | IRQ15-IRQ9<br>IRQ7, IRQ6<br>IRQ5-IRQ3<br>IRQ1 | 76-82<br>83, 84<br>1-3<br>4 | I           | INTERRUPT REQUESTS. Asynchronous Interrupt Request lines. May be programmed to be edge (low to high) or level (high)                                                                                                                                                                                                                                                                                                                                              |

|           |               |             | forms initialization of the various sections of the IMP82C206.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTR                                          | 70                          | o           | sensitive.  INTERRUPT. Active high INTER-<br>RUPT line indicates to the CPU<br>that an interrupt request is<br>pending                                                                                                                                                                                                                                                                                                                                            |

| Name      | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                        | Name            | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                             |

|-----------|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMRCLK    | 23            | 1           | TIMER CLOCK. The Clock input for the three counters in the CTC.                                                                                                                                                                                                                                    | DREQ0-<br>DREQ3 | 44-47         | 1           | DMA REQUEST. The DMA Requests are individual asynchron-                                                                                                                                                                                                                                                                                 |

| GATE2     | 22            | l           | <b>GATE 2.</b> Gate 2 is the input for Counter 2.                                                                                                                                                                                                                                                  | DREQ5-<br>DREQ7 | 60-58         |             | ous channel request inputs used<br>by peripherals to obtain DMA ser-<br>vice. A request is generated by                                                                                                                                                                                                                                 |

|           |               |             | In the PC/AT environment, it is used for speaker tone generation and is controlled by bit 0 of I/O port 061H.                                                                                                                                                                                      |                 |               |             | activating the DREQ line of a channel. Polarity of DREQ is programmable. DACK will acknowledge the recognition of the                                                                                                                                                                                                                   |

| OUT1      | 20            | 0           | <b>OUT 1.</b> Out 1 is the output of Timer 1.                                                                                                                                                                                                                                                      |                 |               |             | DREQ signal. DREQ must be maintained until the corresponding DACK goes active. In Fixed                                                                                                                                                                                                                                                 |

|           |               |             | In the PC/AT environment, Timer 1 is programmed as a rate generator, which produces a 15 µsec period signal that is used to request a memory refresh cycle.                                                                                                                                        |                 |               |             | Priority, DREQ0 has the highest priority and DREQ7 has the lowest priority. Reset initializes these lines to active high.                                                                                                                                                                                                               |

| OUT2      | 19            | 0           |                                                                                                                                                                                                                                                                                                    |                 |               |             | DREQ is not recognized while the<br>clock is stopped. Unused DREQ<br>inputs should be pulled to their                                                                                                                                                                                                                                   |

|           |               |             | In the PC/AT environment, OUT 2 drives the speaker.                                                                                                                                                                                                                                                |                 |               |             | inactive state and the corresponding mask bit set.                                                                                                                                                                                                                                                                                      |

| SCLK<br>· | 21            |             | CLOCK INPUT. The Clock Input is used to generate the timing signals which control internal operations and DMA operations. This input may be driven from DC to 10 MHz and may be stopped in either state for standby operation. The internal clock to be used in the DMA Controller is set by bit 0 |                 |               |             | DREQ0-DREQ3 support 8-bit transfers between 8-bit I/O and 8-bit or 16-bit system memory. DREQ5-DREQ7 support 16-bit data transfers between 16-bit I/O and 16-bit system memory. DREQ4 is not available for transfers as it is used to cascade DREQ0-DREQ3.                                                                              |

|           |               |             | of Configuration Register 0. It can be SCLK or SCLK/2.                                                                                                                                                                                                                                             | DACKO-<br>DACK3 | 48-51         | 0           | <b>DMA ACKNOWLEDGE.</b> The DMA Acknowledge signal notifies                                                                                                                                                                                                                                                                             |

| HLDA      | 73            | 4 .         | HOLD ACKNOWLEDGE. The active high Hold Acknowledge is a signal from the CPU indicating that control of the system buses has been relinquished.                                                                                                                                                     | DACK5-<br>DACK7 | 57-55         |             | the requesting peripheral when a DMA cycle is granted. The active polarity of these lines is programmable. These signals are used internally for cascading the DMA channels and for DMA page                                                                                                                                            |

| HRQ       | 69            | 0           | HOLD REQUEST. The Hold<br>Request output is a signal<br>requesting control of the system<br>buses. A HRQ is issued by the<br>DMA Controller when a DREQ                                                                                                                                            |                 |               |             | register selection. Due to their use within the System, these signals must be programmed to be active low. Reset initializes the DACK signals to active low.                                                                                                                                                                            |

|           |               |             | occurs and the corresponding mask bit is clear. It is also issued for a software DMA request.                                                                                                                                                                                                      | TC              | 67            |             | TERMINAL COUNT. The active high Terminal Count (TC) output signal contains information concerning the completion of DMA services. When TC is reached, except for Channel 0 in memory-to-memory mode, a pulse is generated by the DMA Controller. The TC pulse is output when TC for channel 1 occurs during memory-to-memory transfers. |

| Name    | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        | Name            | Pin<br>Number | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |               |             | At a TC pulse occurrence, the DMA Controller terminates the service and resets the request. If an automatic initialize is set, the base registers are written to the current registers of that channel. If automatic initialize is not enabled for the channel, the mask bit and TC bit in the status word is set for the currently active channel. If automatic initialize is enabled, the mask bit remains clear.                                | ADSTB16         | 65            | 0           | ADDRESS STROBE for 16-BIT DMA TRANSFERS (channels 5-7). The Address Strobe is an active high signal. It is used to latch the upper address byte (A9 A16) for 16-bit peripherals by driving the strobe input of external transparent octal latches. During block operations, this signal is only issued when the upper address byte must be altered. This eliminates S1 states and provides higher system performance.                            |

| DMAMEMR | 61            | 0           | DMA MEMORY READ. The active low DMA Memory Read is a tri-state output. This output is used to access data from the selected memory location during DMA read or memory-to-memory transfers.  In the PC/AT environment, this                                                                                                                                                                                                                         | AEN8            | 63            | 0           | ADDRESS ENABLE for 8-BIT DMA TRANSFERS. The Address Enable is an active low signal which enables an 8-bit latch. This latch contains the upper eight address bits (A8-A15). When the DMA does not control the system                                                                                                                                                                                                                             |

| DMAMEMW | 62            | Ο           | signal is connected to XMEMR.  DMA MEMORY WRITE. The active low DMA Memory Write is a tri-state output. This output is used to write to the selected memory location during DMA write or memory-to-memory transfers.  In the PC/AT environment, this                                                                                                                                                                                               | AEN16           | 64            | 0           | bus, this signal is inactive.  ADDRESS ENABLE for 16-BIT DMA TRANSFERS. The Address Enable is an active low signal which enables an 8-bit latch. This latch contains the upper eight address bits (A9-A16). When the DMA does not control the system bus, this signal is                                                                                                                                                                         |

| ADSTB8  | 66            | 0           | signal is connected to XMEMW.  ADDRESS STROBE for 8-BIT DMA TRANSFERS (channels 0-3). The Address Strobe is an active high signal. It is used to latch the upper address byte (A8-A15) for 8-bit peripherals by driving the strobe input of external transparent octal latches. During block operations, this signal is only issued when the upper address byte must be altered. This eliminates S1 states and provides higher system performance. | XA16<br>A23-A17 | 13<br>11-5    | 0           | inactive.  DMA PAGE REGISTER  ADDRESS. The DMA Page Reg ster Addresses, XA16 and A17-A23, are tri-state output pins. A17-A23 are the upper seven bits of the DMA page register. XA16 is used for DMA transfers for 8-b peripherals only (Channel 0-3). It is the least significant bit of the DMA page register. XA16 is not used for DMA transfers to 16-bit peripherals (Channel 5-7) as XA9-XA16 are provided by demultiplexing the data bus. |

|         |               |             | portonialist.                                                                                                                                                                                                                                                                                                                                                                                                                                      | Vcc             | 32,75         |             | POWER SUPPLY. DC Power supply connection. (See 'Absolute Maximum Ratings' and 'Operating Conditions' tables.)                                                                                                                                                                                                                                                                                                                                    |

|         |               |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vss             | 12,53,74      | _           | <b>GROUND.</b> Ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                |

# IMP82C206 — Integrated Peripherals Controller

The IMP82C206 contains the equivalent of two 8237A DMA Controllers, a 74LS612 Memory Mapper, two 8259A Interrupt Controllers, an 8254 Counter/Timer, and a MC146818 Real Time Clock with RAM. It is an implementation containing the standard peripherals required to implement an IBM PC/AT system board except the keyboard interface controller.

Two Direct Memory Access (DMA) Controllers are provided. They provide improved system performance as external devices transfer information directly from the system memory.

The controllers are connected to provide the user with a total of seven DMA channels.

DMA1 — 4 channels for 8-bit transfers

DMA2-3 channels for 16-bit transfers

Note: The first 16-bit DMA channel is used for cascading).

Also included in the DMA subsystem is the DMA Page Register. This device provides the A17-A23 addresses during 16-bit DMA transfers.

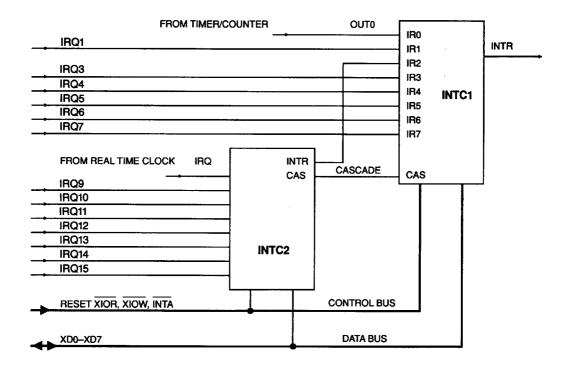

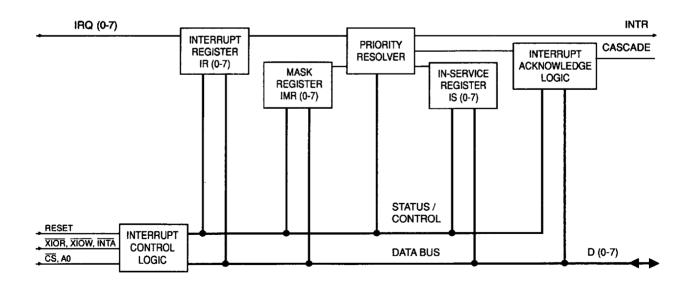

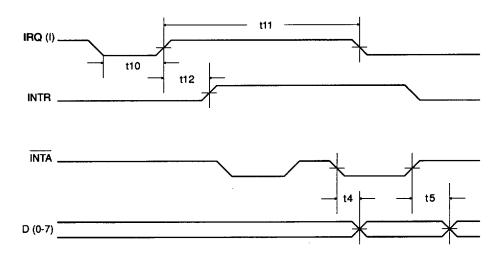

Sixteen interrupt channels, partitioned into two cascaded controllers (INTC1, INTC2) with eight inputs each, are provided in the IMP82C206. Three of these channels are connected internally to various devices.

Channel 0 — Counter/Timer Counter 0 Interrupt

Channel 2 — Cascade to Slave Interrupt Controller (INTC2)

Channel 8 - Real Time Clock Interrupt

The thirteen interrupt channels, not connected internally, may be user defined and utilized to meet specific system requirements.

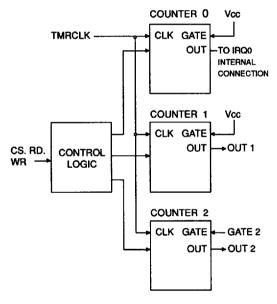

A general purpose Counter/Timer (CTC) subsystem provides the ability to generate accurate time delays under system control. The CTC contains three independent counters. A counter may be individually programmed as a timer or as a counter.

Counter 0 is connected to Interrupt 0 of INTC1. It is intended to be used as a multi-level interrupt to the system for such tasks as timekeeping and task switching.

Counter 1 may be programmed to generate pulses or square waves for use by external devices.

Counter 2 is a full function Counter/Timer which has a gate input for controlling the internal counter. This channel can be used as an interval counter, a timer, or as a gated rate/pulse generator.

All three counters are driven from the same clock input pin. This pin is independent from the other clock inputs to the IMP82C206.

A Real Time Clock (RTC) is included in the IMP82C206. The RTC contains a time-of-day clock with alarm, calendar (one hundred year), programmable periodic interrupt, choice of BCD or binary timekeeping, time-of-day interrupts, 12 hour or 24 hour format for timekeeping, daylight savings time, automatic end-of-month detection, automatic leap year detection, and 114 bytes of low power static RAM with battery backup. This provides protection for RAM and the RTC if subjected to a loss of power.

The Top Level Decode is a multilevel decode scheme which interconnects and controls all of the major subsystems. It performs the generation of enables to the subsystems and the direction of the data bus buffers. It is also used to maintain I/O decode compatibility with the IBM PC/AT.

The Clock and Wait State Control subsystem controls the generation of DMA wait states. If programmed, it handles the negation of IOCHRDY during CPU access. This subsystem performs the generation of enables to the subsystems. Also, the control and direction of the data bus buffers are managed.

#### **Top Level Decode**

The IMP82C206 Top Level Decode provides eight separate enables to various subsystems of the device. Also, the decoder determines the control and enabling of the XD0-XD7 output buffers. These buffers are enabled whenever the internal subsystem generates an enable and the XIOR signal is asserted.

The decoder is enabled by three signals. These three signals are ACK and XA9-XA8. To enable any internal device, ACK must be one and both XA9 and XA8 must be zero. Table 1.1 contains the Top Level Decode Scheme.

| SELECTED<br>DEVICE | ADDRESS<br>RANGE (Hex) | ACK | XA9 | XA8 | XA7 | XA6 | XA5 | XA4 | ХАЗ | XA2 | XA1 | XAO |

|--------------------|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| DMA1               | 000-000F               | 1   | 0   | 0   | 0   | 0   | 0   | 0   | х   | x   | х   | Х   |

| INTC1              | 020-021                | 1   | 0   | 0   | 0   | 0   | 1   | 0   | l 0 | 0   | 0   | Х   |

| CONFIG             | 022-023                | 1   | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | Х   |

| CTC                | 040-043                | 1   | 0   | 0   | 0   | 1   | 0   | 0   | 1 0 | Ιo  | Х   | l x |

| RTC                | 071                    | 1   | 0   | 0   | 0   | 1   | 1   | 1   | 1 0 | Ιo  | 0   | 1   |

| DMAPAGE            | 080-08F                | 1   | 0   | l 0 | 1   | Ιo  | 0   | 0   | Ιx  | Ιx  | Х   | х   |

| INTC2              | 0A0-0A1                | 1   | 0   | l 0 | 1   | l 0 | 1   | 0   | 0   | Ιo  | 0   | X   |

| DMA2               | 0C0-0DF                | 1   | 0   | 0   | 1   | 1 1 | 0   | Х   | Х   | l x | X   | х   |

| DISABLED           | DISABLED               | l 0 | X   | Х   | Х   | Ιx  | Х   | Х   | l x | Ιx  | х   | х   |

| DISABLED           | DISABLED               | l x | 1 1 | Х   | Х   | X   | Х   | Х   | Х   | X   | X   | X   |

| DISABLED           | DISABLED               | Х   | Х   | 1   | Х   | Х   | Х   | Х   | Х   | Х   | X   | Х   |

Table 1.1 Internal Decode Scheme

Selects to the individual subsystems are more fully decoded and designed to comply with the IBM PC/AT requirements. As the IMP82C206 will not respond to unused address spaces established by the Top Level Decoder, the user can take advantage of these areas by inserting additional peripherals in the I/O map. As output buffers are not enabled, unless an internal subsystem is enabled, extra peripherals may be tied directly to the XD0-XD7 data lines.

#### **Clock and Wait State Control**

Four functions are performed by the Clock and Wait State Control subsystem. These are:

- 1. Control of the DMA command width

- 2. Control of the CPU read cycle length

- 3. Control of the CPU write cycle length

- 4. Selection of the DMA clock rate

All of these functions may be selected by writing to the Configuration Registers located at address 023H. A read or write is accomplished by first writing an index to location 022H. This selects one of the IMP82C206 Configuration Registers. Then a read or write may be performed to address 023H.

## Register Configurations

Register 0 (023H) (Index 01H)

| LS | В |

|----|---|

| LS | B |

| B7  | B6  | <b>B</b> 5 | B4   | В3  | B2  | B1  | B0  |

|-----|-----|------------|------|-----|-----|-----|-----|

| RW1 | RW0 | 16W1       | 16W0 | 8W1 | 8W0 | EMR | CLK |

(Read/Write Register)

RW1-RW0-

When higher speed CPU's are accessing the System, the cycle can be extended. By programming up to four wait states into the Configuration Register, a not ready condition on IOCHRDY (low) is asserted whenever a valid decode from the Top Level Decoder is detected and either XIOR or XIOW is asserted. IOCHRDY remains low for the number of wait states specified.

| Read/Write Cycle<br>Wait States | RW1 | RW0    |

|---------------------------------|-----|--------|

| 1 2                             | 0   | 0      |

| 3 4                             | 1   | 0<br>1 |

Wait states are in increments of one SCLK cycle and are not affected by the DMA Clock Divider.

16W1-16W0 - Wait states can be independently controlled for both 8-bit and 16-bit DMA cycles. This allows the user to modify the DMA cycle to more closely fit the application.

| 16-Bit DMA<br>Wait States | 16W1 | 16 <b>W</b> 0 |

|---------------------------|------|---------------|

| 1                         | 0    | 0             |

| 2                         | 0    | 1             |

| 3                         | 1    | 0             |

| 4                         | 1 1  | 1             |

8W1-8W0-

These bits provide the ability to program the register for wait states to be inserted in 8-bit DMA cycles.

| 8-Bit DMA<br>Wait States | 8W1 | 8W0 |

|--------------------------|-----|-----|

| 1                        | 0   | 0   |

| 2                        | 1 0 | 1   |

| 3                        | 1 1 | 0   |

| 4                        | 1   | 1   |

Note: During DMA, the IOCHRDY pin is used as an input to the wait state generation logic. This input is driven low (0) by the peripheral to extend the cycle. When the cycle is completed, IOCHRDY is released allowing it to return high (1).

**EMR**

- -This bit enables the extended DMAMEMR function. In the IBM PC/AT environment, assertion of DMAMEMR is delayed one clock cycle later than XIOR.

- 0: DMAMEMR delayed one DMA clock cycle later than XIOR

- 1: DMAMEMR and XIOR are enabled simultaneously

CLK

- -This bit allows the user to insert a divider between the DMA Controller subsystems and the SCLK input pin, or connect the two directly.

- SCLK input is divided by two and is used to drive both the 8-bit and 16-bit DMA subsystems

- 1: Divider is bypassed and the SCLK input used directly

The Internal synchronizer controls the actual switching of the clock when the state of this bit changes. This prevents a short clock pulse from creating a DMA malfunction when the state changes.

The Configuration Register 0 contents are preloaded by RESET to an initial value of 0C0H. This value establishes a default which is IBM PC/AT compatible and corresponds to:

> Read/Write cycles —4 wait states 16-bit DMA transfers — 1 wait state 8-bit DMA transfers -- 1 wait state DMAMEMR delayed 1 DMA clock cycle later than XIOR DMA clock is equal to SCLK/2

### Register 1 (023H) (Index 02H)

|     | _ |   |

|-----|---|---|

| N.  |   | 2 |

| IVI | • | ┖ |

**LSB**

| <b>B</b> 7 | <b>B6</b> | <b>B</b> 5 | B4 | В3 | B2   | B1    | B0   |

|------------|-----------|------------|----|----|------|-------|------|

| R          | R         | R          | R  | R  | NRWS | N16WS | N8WS |

#### (Read/Write Register)

**B7-B3**

Reserved bits.

**NRWS**

- The high performance of the IMP82C206 allows CPUs, up to 20 MHz, to access the IMP82C206 with zero wait states. Setting this bit to a one allows zero wait state accesses. Setting this bit to zero allows Configuration Register 0, bits RW1-RW0, to control the number of wait states used during an IMP82C206 access. The default setting is a zero after RESET.

- 0: Configuration Register 0 controls number of wait states used during an access (default)

- 1: Zero wait state access

N16WS

- -To allow 16-bit DMA transfers to occur with zero wait states, this bit must be set to a one. Setting the bit to a zero allows Configuration Register 0, bits 16W1-16W0, to govern the wait states for a 16-bit DMA transfer. The default setting is zero after RESET.

- 0: Configuration Register 0 governs wait states (default)

- 1: Zero wait state access

N8WS

- Setting this bit to a one will allow 8-bit DMA transfers to occur with zero wait states. Setting the bit to a zero allows Configuration Register 0, bits 8W1-8W0, to govern the wait states for an 8-bit DMA transfer. The default setting is one after RESET.

- 0: Configuration Register 0 governs the wait states (default)

- 1: Zero wait state access

Note: Setting any of these bits to one requires the system timing to be capable of supporting zero wait state accesses. None of these bits need be changed from their default settings for operations in the PC/AT environment.

### IMP82C206 — DMA Controllers

## **Functional Description**

Two DMA controllers are implemented in the IMP82C206. These devices generate the memory addresses and control signals to transfer information directly between a peripheral device and memory with little CPU intervention.

Through the internal cascade ability, system expansion is implemented. The controllers provide multiple channels for direct memory transfers. The DMA2 Channel 0 is the cascade interconnection for the two DMA devices necessary to maintain IBM PC/AT compatibility. Four channels for transfers to 8-bit peripherals (DMA1) are provided; three channels for transfers to 16-bit peripherals (DMA2).

Cycle length can be controlled by inserting wait states or extending the command strobes. These controls are accessible through the programmable registers.

Each DMA controller has 16 internal registers for programmability and control. These registers include: Base Address, Base Word Count, Current Address, Current Word Count, Command Register, Mode Register, and Status Register. See "Register Description" for a complete list of registers and their functions.

#### **DMA Operation**

During normal operation of the IMP82C206, the DMA subsystem will be in one of the following conditions: Idle, Program, or Active.

Idle State (SI) is the default condition. In the SI condition, the DMA controller will be executing cycles consisting of only one state. As the default, this condition is applicable until the device is initialized and a DMA request is active.

When a DMA request becomes active, the device enters the Active condition and a Hold Request (HRQ) is issued to the System. Once Hold Acknowledge (HLDA) becomes active, the IMP82C206 generates the necessary memory addresses and command signals to accomplish transfers. Memory-to-I/O and I/O-to-Memory transfers occur in one cycle; Memory-to-Memory transfers require two cycles. During transfers between memory and I/O, data is presented on the system bus by either memory or the requesting device and completed in one cycle. Memory-to-Memory transfers, however, require the DMA to store data from the read operation in an internal register. The contents of this register is then written to memory on the subsequent cycle.

#### Idle Condition

The DMA is in an Idle condition when there is no service request pending for a device. While in SI, the DREQ input pins are sampled each clock cycle. Also, to determine if the CPU is attempting to access the internal registers, the internal select and HLDA are also sampled every clock cycle. (Since a CPU cycle is already in effect, the Program condition has priority over the Active condition.) The DMA exits the Idle condition when the status changes.

### **Program Condition**

The Program condition can be entered whenever HLDA is inactive and an internal register is being accessed. The two DMA controllers use different addresses to select the internal registers. For DMA1, address lines XA0-XA3 are used and for DMA2, address lines XA1-XA4 are used. Table 2.1 lists the register address assignments.

Whenever HLDA has been inactive for one DMA clock cycle, the IMP82C206 will enable the Programming condition. It is the responsibility of the System to ensure that programming and HLDA are mutually exclusive. To prevent an attempt to service a device with a partially programmed channel, the channel should be masked or the DMA disabled. If a request for service occurs on an unmasked channel, which is being programmed, erratic operation of the IMP82C206 may occur.

An internal Byte Pointer flip-flop is used to supplement the addressing of the word count and address registers. With the flip-flop cleared, a read or write of a word count or address register will access that register's high byte. The Byte Pointer Flip-Flop will be toggled for any read/write of a word count or address register and will be cleared by a hardware RESET or Master Clear command. Commands are also provided to directly set or reset the flip-flop.

The DMA subsystem supports special commands to control the device while in the Program condition. They are derived from a set of addresses and the read or write strobes (XIOW or XIOR). These commands are:

- Master Clear

- -Clear Mask Register

- -- Clear Mode Register Counter

- Set Byte Pointer Flip-Flop

- Clear Byte Pointer Flip-Flop

| Address Operation                                                                                                                                                                                          |      |      |                  |                  |                  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------------------|------------------|------------------|--|--|--|--|

| Register Function                                                                                                                                                                                          | DMA1 | DMA2 | XIOR             | XIOW             | Flip<br>Flop     |  |  |  |  |

| Read Channel 0 Current Address Low Byte Read Channel 0 Current Address High Byte Write Channel 0 Base and Current Address Low Byte Write Channel 0 Base and Current Address High Byte                      | 000Н | 0C0H | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 0 Current Word Count Low Byte<br>Read Channel 0 Current Word Count High Byte<br>Write Channel 0 Base and Current Word Count Low Byte<br>Write Channel 0 Base and Current Word Count High Byte | 001H | 0C2H | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 1 Current Address Low Byte<br>Read Channel 1 Current Address High Byte<br>Write Channel 1 Base and Current Address Low Byte<br>Write Channel 1 Base and Current Address High Byte             | 002Н | 0C4H | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 1 Current Word Count Low Byte<br>Read Channel 1 Current Word Count High Byte<br>Write Channel 1 Base and Current Word Count Low Byte<br>Write Channel 1 Base and Current Word Count High Byte | 003Н | 0C6H | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 2 Current Address Low Byte<br>Read Channel 2 Current Address High Byte<br>Write Channel 2 Base and Current Address Low Byte<br>Write Channel 2 Base and Current Address High Byte             | 004H | 0C8H | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 2 Current Word Count Low Byte<br>Read Channel 2 Current Word Count High Byte<br>Write Channel 2 Base and Current Word Count Low Byte<br>Write Channel 2 Base and Current Word Count High Byte | 005H | 0CAH | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 3 Current Address Low Byte<br>Read Channel 3 Current Address High Byte<br>Write Channel 3 Base and Current Address Low Byte<br>Write Channel 3 Base and Current Address High Byte             | 006H | 0CCH | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Channel 3 Current Word Count Low Byte<br>Read Channel 3 Current Word Count High Byte<br>Write Channel 3 Base and Current Word Count Low Byte<br>Write Channel 3 Base and Current Word Count High Byte | 007H | 0CEH | 0<br>0<br>1<br>1 | 1<br>1<br>0<br>0 | 0<br>1<br>0<br>1 |  |  |  |  |

| Read Status Register<br>Write Command Register                                                                                                                                                             | 008H | ODOH | 0                | 1<br>0           | X                |  |  |  |  |

| Read DMA Request Register<br>Write DMA Request Register                                                                                                                                                    | 009H | 0D2H | 0                | 0                | X                |  |  |  |  |

| Read Command Register<br>Write Single Bit DMA Request Mask Register                                                                                                                                        | 00AH | 0D4H | 0                | 0                | X                |  |  |  |  |

| Read Mode Register<br>Write Mode Register                                                                                                                                                                  | 00BH | 0D6H | 0                | 1<br>0           | X                |  |  |  |  |

| Set Byte Pointer Flip-Flop<br>Clear Byte Pointer Flip-Flop                                                                                                                                                 | 00CH | OD8H | 0                | 1<br>0           | X                |  |  |  |  |

| Read Temporary Register<br>Master Clear                                                                                                                                                                    | 00DH | 0DAH | 0                | 1<br>0           | X                |  |  |  |  |

| Clear Mode Register Counter<br>Clear all DMA Request Mask Register Bits                                                                                                                                    | 00EH | 0DCH | 0<br>1           | 1<br>0           | X                |  |  |  |  |

| Clear all DMA Request Mask Register Bits<br>Write all DMA Request Mask Register Bits                                                                                                                       | 00FH | ODEH | 0                | 1 0              | X                |  |  |  |  |

Table 2.1 DMA Register Address Assignment

#### **Active Condition**

The IMP82C206 DMA subsystem enters the Active condition when one of the following conditions occur:

- Software request

- DMA request on an unmasked channel; device NOT in Program condition

The IMP82C206 will then begin a DMA transfer cycle.

A hold request is issued to the System after a DREQ request is received. When a Hold Acknowledge is returned, the DMA exits the Idle State and enters the Active Condition. In the Active Condition, memory address and command signals are generated to effect a Memory-to-I/O, I/O-to-Memory, or Memory-to-Memory transfer.

During transfers between memory and I/O, two commands are activated during the same cycle. In Memory-to-I/O transfers, DMAMEMR and XIOW are both asserted during the same cycle to transfer data directly from memory to the requesting device. (Note that IMP82C206 does not latch data from, nor drive data out, on this type of cycle.)

The number of clock cycles necessary to transfer data is varied. Control of the number of clock cycles required to transfer a word of data is dependent upon the peripheral device requirements and/or the DMA programming. During an Active cycle, the DMA will step through a series of states of one DMA clock cycle in length. The number of states in a cycle is dependent upon the type of cycle being performed and, again, how the DMA is programmed.

Memory and I/O data transfers require one cycle. Data is presented on the system bus by either the requesting device or memory. Memory-to-Memory transfers require two cycles as the data is stored from the read operation in an internal register. The contents of this register is then written to memory on the subsequent cycle.

An example of the series of steps necessary in an IMP82C206 read cycle are:

- 1. Receives a DREQ

- 2. Issues a HRQ

- 3. Waits for HLDA (remains in Idle condition)

- 4. DMA exits Idle condition at next clock cycle

- 5. Enters state S0

- a) Device resolves priority

- Issues DACK on the highest priority channel requesting service

- Proceeds to state S1 where the multiplexed addresses are output and latched

- 7. State S2 is entered; DMAMEMR is asserted.

- State S3 is entered; XIOW command is asserted. The IMP82C206 DMA remains in S3 until the Wait State Counter has decremented to zero and IOCHRDY is true. Note: At least one additional S3 will occur unless Compressed Timing is selected.

- Ready condition is detected. The DMA enters S4 where both commands are deasserted.

Note: In Block and Demand Mode, subsequent cycles will begin in S2 unless the intermediate addresses require updating. In these subsequent cycles, the lower addresses are changed in S2.

The DMA can be programmed on a channel-by-channel basis to operate in one of four modes.

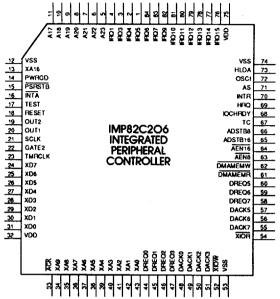

#### **Cascade Mode**

The Cascade mode is used for system expansion by cascading the DMA controllers. This mode determines the priority of the additional device. The master DMA controller does not generate address or control signals. The DREQ and DACK signals are used to interface the HRQ and HLDA signals of the slave DMA devices. This method preserves the priority chain and the new device must wait for a HLDA. After receiving the DREQ from a slave controller and the HLDA from the CPU, the master controller ignores all inputs, except HLDA and DREQ, on the active channel. This prevents conflicts between the DMA devices.

The Cascade mode is not limited to two levels of DMA controllers. Additional devices can be cascaded to the available channels in either DMA1 or DMA2. The Cascade mode interconnection for two levels of DMA devices is depicted in Figure 2.1.

Figure 2.1 Cascade Mode Interconnect

To program cascaded controllers, the slave devices must be programmed first. Each successive device is then programmed. RESET sets the DACK outputs to become active low. The outputs are then placed in the active state. As there is an inversion between DACK 0 of DMA2 and HLDA of DMA1, the DACK active low state should not be modified. Unwanted hold requests during the initialization process, generated by second level devices, are prevented by the first level device DMA request mask bit.

T-52-33-15

#### **Block Transfer Mode**

In the Block Transfer mode, a DREQ or a software request is needed to begin the DMA transfer. The transfer continues until the terminal count (FFFFh) is attained. (DREQ is held active until DACK is asserted.) When the terminal count (T/C) is reached, the T/C is pulsed and the status register terminal count bit is set. If the automatic initialization option has been enabled, the channel will re-initialize itself. If automatic initialize is not enabled, the DMA will set the DMA request bit mask and suspend transferring on that channel.

#### **Demand Transfer Mode**

The Demand Transfer mode allows peripherals with limited buffering ability to control DMA transfers. The peripheral device will assert DREQ to begin a DMA transfer. When the peripheral's buffer is depleted, it will deassert DREQ and pass bus control back to the CPU. Later, when it's buffer has been filled again, it can reassert DREQ to start another transfer cycle.

In the Demand Transfer mode, transfers are initiated in response to the assertion of DREQ and continue until either T/C is reached or DREQ becomes inactive. Once DREQ has been deasserted, higher priority channels are allowed to intervene. A T/C pulse is generated, the terminal count bit in the status registers is reset, and auto-initialization, if enabled, is initiated upon reaching terminal count.

During idle periods between transfers, the CPU is released to operate and can monitor the operation by reading intermediate values from the address and Word Count Registers.

#### **Single Transfer Mode**

In Single Transfer mode, the DMA executes only one transfer cycle at a time. The DREQ is held active until the request is acknowledged (DACK goes active). Once the transfer is complete, HRQ is deasserted and the bus is released. After HLDA has gone inactive, the HRQ is asserted if another cycle is requested. If another cycle, on the same channel is requested, it is executed unless a request from a higher priority channel has been received. This insures that the CPU can execute at least one bus cycle between transfers.

After each transfer, the word count is decremented and the address is incremented or decremented. The terminal count bit in the status register is set and a T/C pulse is generated when the word count decrements from 0000h to FFFFh. If automatic initialization is not enabled, the DMA request bit mask is set and transfers on that channel are suspended; if enabled, the channel is re-initialized.

#### **DMA Transfers**

Multiple transfer types are provided in the IMP82C206 DMA subsystem. They are:

### **Memory-to-Memory Transfer**

A block of memory may be moved from one location in memory to another location using the Memory-to-Memory transfer. By setting a bit in the Command Register, DMA Channel 0 and Channel 1 may be programmed to operate as Memory-to-Memory channels. If Channel 0 is programmed to maintain the same source address on every cycle, the CPU

can initialize large blocks of memory with the same value. The DMA will continue performing transfer cycles until Channel 1 reaches terminal count.

After programming the DMA channels to operate as Memory-to-Memory channels, a transfer is initiated by generating a software or an external request to Channel 0. After the transfer is initiated, Channel 0 provides the address for the source block during the memory read portion of the cycle; Channel 1 generates the address for the memory write cycle. During the read cycle, a byte of data is latched in the internal Temporary Register. The contents of this register are then output on the XD0-XD7 data lines during the write portion of the cycle and, subsequently, written to memory. When Channel 1 reaches terminal count, transfer cycles are suspended.

#### **Verify Transfer**

The DMA operates as though a Read or Write Transfer is being performed. The HRQ, addresses, and DACK are generated but a command signal is not asserted. No actual transfer is performed; thus IOCHRDY is ignored in this cycle. Verify Transfer is a tool which is useful in diagnostics.

#### Read Transfer

Data is copied to an I/O device from memory. The memory address is generated and DMAMEMR and XIOW are asserted during the same cycle.

#### Write Transfer

Data is copied to memory from an I/O device. The memory address is generated and DMAMEMR and XIOR are asserted during the same cycle.

#### **Auto-initialization**

The auto-initialization process reloads the Base Address and Base Word Count Registers into the Current Address and Current Word Count Registers. The base registers may be altered by the CPU only. Thus, in active cycles, these registers remain unchanged.

Each of the four DMA channel Mode Registers contain a bit which enables auto-initialization on the channel after reaching terminal count. When automatic initialization has been programmed for a channel, the request mask bit is not set upon reaching terminal count. This feature provides the DMA with the ability to continue operation without CPU intervention.

To support full auto-initialization in Memory-to-Memory transfers, the Word Count Registers of Channel 0 and Channel 1 must be programmed with the same starting value. If Channel 0 reaches terminal count before Channel 1, Channel 0 reloads the starting address and word count and continues transferring data from the beginning of the source block. If Channel 1 reaches terminal count first, it reloads the current registers and Channel 0 will not be re-initialized.

### **DREQ Priority**

The IMP82C206 supports two methods of establishing DREQ priority. These are Fixed and Rotating priority.

Fixed priority is assigned priority based on channel position.

Rotating priority is based on the rotation assignment of the channels. The ordering of priority from Channel 0 to Channel 3 is maintained but the actual assignment of priority changes. The channel with the most recent DREQ performed is rotated and assigned the lowest priority; as the order of priority is fixed, the remaining three channels rotate accordingly. The rotating priority method is illustrated in Table 2.2.

In instances where multiple requests occur, the IMP82C206 will issue a HRQ but will not freeze the priority logic until HLDA is returned. Once HLDA becomes active, the priority is frozen. DACK is asserted on the highest priority requesting channel. Priority, for the next HRQ, is assigned when HLDA is released.

#### **Address Generation**

The number of pins required by the DMA subsystem are reduced by multiplexing eight intermediate bits of the address with the XD0-XD7 data bus. During state S1, the XD bus is used to output the eight bits of the memory address. For an 8-bit cycle, addresses A8-A15 are output; a 16-bit cycle addresses A9-A16 are output. An external TTL device must be provided with latch and enable signals for the external device.

During DMA1 cycles, the address bits are output as follows:

Lower 8-bits of address — XA0-XA7 Intermediate addresses A8-A15 - XD0-XD7 High 8-bits of address — XA16, A17-A23

ADSTB8 is asserted for one DMA clock cycle and the falling edge is used to latch the intermediate addresses A8-A15. AEN8 controls the output drivers of the external latch. The DMA Page Register generates A16-A23.

During DMA2 cycles, the address bits are output as follows:

Lower 8-bits of address — XA1-XA8 Intermediate addresses A9-A16 - XD0-XD7 High address — A17-A23 ADSTB16 and AEN16 signals provide control for a separate latch. The DMA Page Register generates A17-A23. During 16-bit DMA transfers, XA0 and XA16 remain inactive.

The high order addresses are generated by the DMA Page Register during DMA cycles. The DMA Page Register consists of a set of 16 8-bit registers. Eight of the registers are used but sixteen are provided to maintain IBM PC/AT compatibility. Each DMA channel, excepting Channel 0 of DMA2, has a register with which it is associated. Channel 0 of DMA2 is used for internal cascading to DMA1. The assignment and address of each of these registers is shown in Table 2.3.

Multiple sequential transfers are generated during Demand and Block Transfers. Normally, the external address latches do not need to be relatched as the information is unchanged. When a carry or borrow from the lower 8-bits of the Address Counter occurs, the system updates the latch contents. As S1 cycles are executed only when necessary, the overall through-put performance is improved.

| Register Function            | Address |

|------------------------------|---------|

| Unused                       | 080Н    |

| 8-bit DMA Channel 2 (DACK2)  | 081H    |

| 8-bit DMA Channel 3 (DACK3)  | 082H    |

| 8-bit DMA Channel 1 (DACK1)  | 083H    |

| Unused                       | 084H    |

| Unused                       | 085H    |

| Unused                       | 086H    |

| 8-bit DMA Channel 0 (DACK0)  | 087H    |

| Unused                       | 088H    |

| 16-bit DMA Channel 2 (DACK6) | 089H    |

| 16-bit DMA Channel 3 (DACK7) | HA80    |

| 16-bit DMA Channel 1 (DACK5) | 08BH    |

| Unused                       | 08CH    |

| Unused                       | 08DH    |

| Unused                       | 08EH    |

| Refresh Cycle                | 08FH    |

Table 2.3 DMA Address Extension Register Map

| First<br>Arbitration | Second<br>Arbitration      | Third<br>Arbitration       | Priority |

|----------------------|----------------------------|----------------------------|----------|

| Channel 0            | CHANNEL 2 - Cycle<br>Grant | CHANNEL 3 - Cycle<br>Grant | Highest  |

| CHANNEL 1 - Cycle    | CHANNEL 3                  | Channel 0                  |          |

| Grant<br>Channel 2   | Channel 0                  | Channel 1                  |          |

| Channel 3            | Channel 1                  | Channel 2                  | Lowest   |

|                      | CHANNEL X = Requested      | Channel                    |          |

Table 2.2 Rotating Priority Method

T-52-33-15

# IMP82C206 DMA

## **Compressed Timing**

The DMA subsystem can be programmed to compress the time to transfer a word in three clock cycles instead of four. A normal cycle consists of three states: S2, S3, and S4, State 3 is executed twice due to the one wait state insertion. To achieve greater through-put, the IMP82C206 may be programmed to assert both commands in S2, omitting one of the S3 cycles. Only one S3 cycle is executed, instead of two S3 cycles, and the transfer terminates in S4. The T/C is output in S1 in compressed timing. (Compressed timing is not valid for Memory-to-Memory transfers.) S1 cycles are executed to update the address latch, as needed.

## **Register Description**

### **Current Address Register**

Each DMA channel has a 16-bit Current Address Register. The address value used during transfers is held in this register. The channel can be programmed to increment or decrement this register when a transfer is completed. This register is read or written by the CPU in consecutive 8-bit bytes. Upon reaching terminal count in the Current Word Count Register, this register is reloaded from the Base Address Register if auto-initialization is selected. Channel 0 will not be incremented or decremented if the Address Hold Bit in the Command Register is set.

#### **Current Word Count Register**

The number of transfers to be performed is determined by the Current Word Count Register of each channel. After each transfer, the register is decremented until it goes from zero to FFFFh. When the register goes to FFFFh, the System generates a terminal count. At that time, the channel either auto-initializes or operation is suspended, and the appropriate Request Mask Bit is set. The number of transfers performed is one greater than the value programmed into the register.

### **Base Address Register**

The Base Address Register stores the initial value of the Current Address Register for auto-initialization. It is a write only register and is loaded by the CPU when writing to the Current Address Register. When terminal count is reached and the auto-initialize bit is set, the contents of this register are loaded into the Current Address Register.

#### **Base Word Count Register**

The initial value of the Current Word Count Register is stored in the Base Word Count Register. It is a write only register and is loaded by the CPU when writing to the Current Word Count Register. During auto-initialization, this register is loaded into the Current Word Count Register.

#### **Command Register**

The Command Register controls the overall operation of the DMA subsystem. This register is programmed by the microprocessor in the Program Condition. It is cleared by RESET or the Master Clear command.

| or the Master Clear command. |                     |                                                    |                              |                                |                                 |                            |                                       |

|------------------------------|---------------------|----------------------------------------------------|------------------------------|--------------------------------|---------------------------------|----------------------------|---------------------------------------|

| MSB                          |                     |                                                    |                              |                                |                                 |                            | LSB                                   |

| B7                           | <b>B</b> 6          | <b>B</b> 5                                         | B4                           | В3                             | B2                              | B1                         | В0                                    |

| DAK                          | DRQ                 | EW                                                 | RP                           | СТ                             | CD                              | AH                         | М-М                                   |

| DAK                          | mir<br>0: /         | IA Ackn<br>ned by b<br>Active Io<br>Active h       | oit 7.<br>ow sign            | al.                            | cK) acti                        | ve leve                    | l is deter-                           |

| DRQ                          | det<br>0: /         | IA Requermined<br>Active h                         | l by bit<br>igh sigi         | 6.<br>nal.                     | e (DRE                          | Q) activ                   | ve level is                           |

| EW                           | — Ext<br>ass<br>Wh  | ended \                                            | Write sone DM/               | ets the s<br>A cycle<br>e read | earlier                         | during                     | ds to be<br>a transfer.<br>mands      |

|                              | 1: E                | .ate writ<br>Extende<br>Bit 3 =                    | d write                      |                                | d Timir                         | ng set a                   | ıctive)                               |

| RP                           | reg                 | tating Pristers is adition is                      | detern                       | nined by                       |                                 |                            |                                       |

|                              |                     | Fixed pr<br>Rotating                               |                              |                                |                                 |                            |                                       |

| СТ                           |                     | mpresse<br>ister.                                  | ed Timi                      | ng is de                       | etermin                         | ed by t                    | oit 3 of this                         |

|                              | 1: 0                | Normal t<br>Compres<br>Bit 0 =                     | ssed ti                      | ming                           |                                 | y enab                     | led)                                  |

| CD                           | DM<br>sub<br>nee    | A controsystem                                     | oller. Ti<br>(DMA<br>eprogra | his fund<br>1 or DM<br>Im one  | tion dis<br>IA2) wh<br>of the c | ables the than the channel | for the<br>he DMA<br>CPU<br>s to pre- |

|                              |                     | Controlle<br>Controlle                             |                              |                                |                                 |                            |                                       |