# EVA-X4300

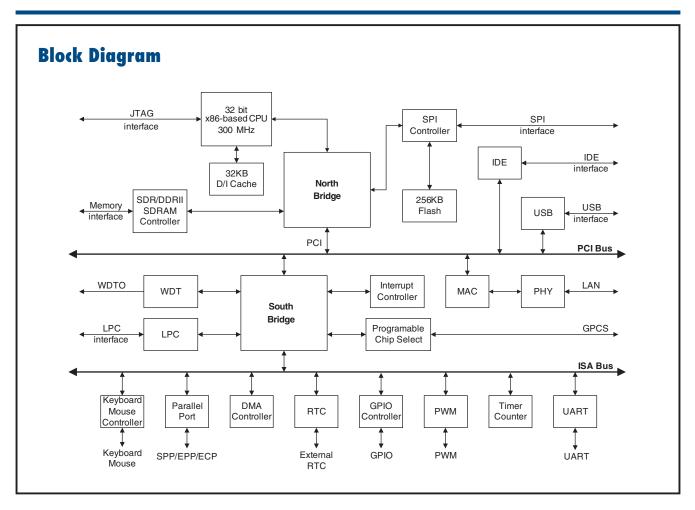

## Embedded 32-bit x86-based SoC with Stacked 256 KB Flash and 10/100 Mbps LAN

#### **Features**

- 32-bit 486SX instruction set compatible SoC

- Operating frequency up to 300 MHz

- Supports both SDR and DDR 2 SDRAM

- Integrate most popular interface PCI, ISA, IDE, Ethernet PHY, USB, SPI and LPC on chip

- Supports up to 40-bit GPIO and 5 UART

- Stacked 256KB Flash and 10/100 Mbps Ethernet PHY

- Low power architecture (Fanless, no heatsink required)

- Wide operating temperature

- Guaranteed product longevity

# Introduction

EVA-X4300 is a fully static 32-bit x86-based processor that powers a wide-range of PC peripherals, applications and OS, such as DOS, Windows CE, Linux and most popular 32-bit RTOS (Real Time OS) for maximum software re-use and legacy compatibility. EVA-X4300 integrates comprehensive features and rich I/O flexibility within a single System on Chip, to reduce board design complexity and shorten product development schedules. Taking advantage of ultra low power consumption, EVA-X4300 is able to operate in wide temperature range environments without thermal designs, making them the perfect x86-based SOC for diverse embedded applications.

# **Specifications**

| specification                           | UNS                                                   |                                          |                                                                             |

|-----------------------------------------|-------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------|

| <ul> <li>Processor Core</li> </ul>      | x86 core, 6 stage pipe-line, 300MHz                   | <ul> <li>Ethernet Controller</li> </ul>  | Integrated 10/100 Mbps Ethernet (MAC + PHY)                                 |

| Embedded L1 Cac                         | he 16 KB I-Cache, 16 KB D-Cache                       |                                          | NE2000 Compatible                                                           |

| SDR / DDR2 SDR/                         | AM 16 bits data bus width                             | IDE Controller                           | Supports 2 channels Ultra-DMA 100 ( PATA x 4 )                              |

| Control Interface                       | Supports DLL for clock phase auto-adjustment          | <ul> <li>Universal Serial Bus</li> </ul> | USB 2.0 Host controller, supports 4 USB ports                               |

|                                         | SDR supports up to 133 MHz, 128 MB                    |                                          | Supports HS, FS and LS mode                                                 |

|                                         | DDR2 supports up to 166 MHz, 256 MB                   | LPC (Low Pin Count)                      | Supports 2 programmable registers to decode LPC                             |

| DMA Controller                          | Provides two 82C37 compatible DMA controllers         | Bus Interface                            | address                                                                     |

|                                         | 4-channel 8-bit DMA transfer and 3-channel 16-bit     | FIFO UART Port                           | Supports up to 5 COM ports                                                  |

|                                         | DMA transfer                                          |                                          | Compatible with 16C550/16C552                                               |

| <ul> <li>Interrupt Controlle</li> </ul> | er Provides two 8259 compatible interrupt controllers |                                          | Default internal pull-high                                                  |

|                                         | Independent programmable level/edge-trigger interrupt |                                          | Supports TXD_En signal on COM1 and COM2                                     |

|                                         | channels                                              |                                          | Supports the programmable baud rate generator with                          |

|                                         | Serial IRQ supported                                  |                                          | the data rate from 50 to 460.8 Kbps                                         |

| <ul> <li>Counter / Timer</li> </ul>     | Two sets of 8254 timer controller                     |                                          | The character options are programmable for 1 start                          |

|                                         | Supports 2 sets Watch Dog Timer (WDT)                 |                                          | bits; 1, 1.5 or 2 stop bits; even, odd or no parity; 5~8                    |

| <ul> <li>General Chip Sele</li> </ul>   | I                                                     |                                          | data bits                                                                   |

|                                         | Configurable I/O-map or Memory-map                    | - Consul Durness I/O                     | Port 80h output data could be redirected to COM1                            |

|                                         | I/O Addressing: From 2 byte to 64 KB                  | <ul> <li>General Purpose I/O</li> </ul>  | Up to 40 GPIO, 8 dedicated and 32 multi-functional<br>programmable I/O pins |

|                                         | Memory Address: From 512 byte to 4 GB                 |                                          | GPIO pins can be individually configured as inputs.                         |

| <ul> <li>PCI Control Interfa</li> </ul> |                                                       |                                          | outputs, or as interrupt trigger sources                                    |

|                                         | Up to 3 individual PCI master devices                 |                                          | Open-drain with a pull-high 75 KW                                           |

|                                         | 3.3 V I/O with 5 V tolerance                          | SPI Interface                            | Supports external SPI flash as data storage                                 |

| <ul> <li>ISA Bus Interface</li> </ul>   | AT clock programmable                                 | <ul> <li>Real Time Clock</li> </ul>      | Internal RTC or External RTC                                                |

|                                         | 8/16 bit ISA device with Zero-Wait-State              |                                          | Under 2 uA power consumption on Internal Mode                               |

|                                         | Generate refresh signals to ISA interface during DRAM | Parallel Port                            | Supports SPP / ECP mode                                                     |

|                                         | refresh cycle                                         |                                          |                                                                             |

|                                         | Complete IRQ set                                      |                                          |                                                                             |

|                                         |                                                       |                                          |                                                                             |

### EVA-X4300

## **Specifications cont.**

- PS/2 Keyboard and Compatible with 8042 controller **Mouse Interface**

- Stacked 256KB Flash Internal SPI interface, for BIOS storage

Buzzer

PCI clock ISA clock SDRAM clock

14.318 MHz, 32.768 KHz

Core Voltage: 1.32 V ± 5 %

24 MHz, 25 MHz, 14.318 MHz

- JTAG Interface

- Speaker Out

- Input Clock

- Output Clock

- Operating Voltage Range

- I/O Voltage: 1.8 V  $\pm$  5 %, 3.3 V  $\pm$  10 %

- Operating temperature -20 °C ~ 85 °C

- Power Consumption Approx. 1.2 Watt PBGA, 581 balls

- Package Type

- Dimension: 27 mm x 27 mm x 2.23 mm Lead-free, RoHS compliant

## **Ordering Information**

- EVA-X4300

- 32-bit x86-based SoC