# Pentium<sup>™</sup> hyperCache<sup>™</sup> Chipset Data-Path/Integrated Cache

#### **Features**

- Supports all 3.3V Pentium™-class processors (ICOMP 735/90, 815/100, etc.), AMD K5, and Cyrix M1 CPUs

- Directly interfaces with CY82C691 and CY82C693 to provide high-performance three-chip Pentium Chipset system

- Provides 64-bit data path between CPU, PCI, and DRAM memory

- 16K by 64 (128-KB) Integrated Pipelined BSRAM

- Direct-mapped or two-way set associative L2 cache mapping configurations

- Two-bit wraparound counter supporting Intel Burst or Linear burst sequence

- Supports 3-1-1-1 Level 2 cache operation up to 66 MHz bus speed

- Fast Clock-to-Data  $(T_{CO}) = 8.5$  ns

- Synchronous self-timed write to L2 cache BSRAM

- Direct interface with the processor and the CY82C691 PCI/Cache/Memory Controller

- 3.3V I/O CPU bus operation

- On-Chip 8-Deep FIFOs support Post-Writing/Pre-Reading PCI data

- Supports Parity checking and generation

- Provides Data steering and Bus size conversion

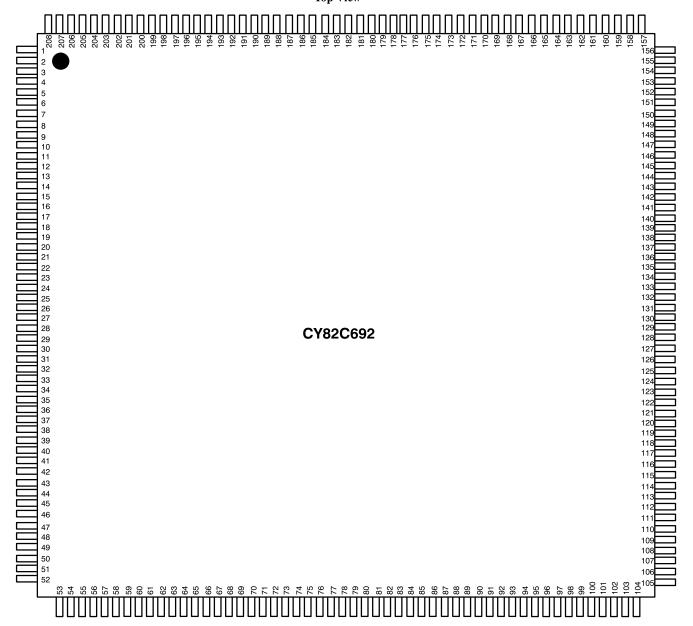

- Packaged in a 208-pin PQFP

Pentium is a trademark of Intel Corporation. hyperCache is a trademark of Cypress Semiconductor Corporation.

**Cypress Semiconductor Corporation**

3901 North First Street

San Jose

CA 95134 •

408-943-2600

## CY82C692 Block Diagram

82C692-97

## **SRAM Section Logic Block Diagram**

## **Pin Configuration**

#### 208-pin PQFP Top View

82C692-99

## **CY82C691** Pin Reference (In Numerical Order by Pin Number)

| Pin No. | Pin Name | Pin No. | Pin Name   | Pin No. | Pin Name |   | Pin No. | Pin Name                  | Ī | Pin No. | Pin Name |

|---------|----------|---------|------------|---------|----------|---|---------|---------------------------|---|---------|----------|

| 1       | VSSQ     | 43      | CY18       | 85      | A5       | 1 | 127     | DQ51                      | 1 | 169     | VDD      |

| 2       | CY10     | 44      | DQ28       | 86      | MD63     | 1 | 128     | DQ50                      | 1 | 170     | MD36     |

| 3       | DQ0      | 45      | CY19       | 87      | A4       | 1 | 129     | DQ49                      | 1 | 171     | VSS      |

| 4       | CY11     | 46      | DQ29       | 88      | MD62     | 7 | 130     | DQ48                      | 1 | 172     | MD35     |

| 5       | DQ1      | 47      | CY20       | 89      | A3       |   | 131     | DQ47                      | 1 | 173     | BW2      |

| 6       | CY12     | 48      | DQ30       | 90      | MD61     | 7 | 132     | DQ46                      | 1 | 174     | MD34     |

| 7       | DQ2      | 49      | CY21       | 91      | VDD      |   | 133     | DQ45                      | 1 | 175     | BW3      |

| 8       | CY13     | 50      | DQ31       | 92      | MD60     |   | 134     | DQ44                      | 1 | 176     | MD33     |

| 9       | DQ3      | 51      | CY22       | 93      | VSS      |   | 135     | DQ43                      | 1 | 177     | GW       |

| 10      | CY14     | 52      | VDDQ       | 94      | MD59     |   | 136     | VDDQ                      | 1 | 178     | MD32     |

| 11      | DQ4      | 53      | VSSQ       | 95      | A2       | 7 | 137     | VSSQ                      | 1 | 179     | BWE      |

| 12      | CY15     | 54      | CY23       | 96      | MD58     |   | 138     | DQ42                      | 1 | 180     | CNTL0    |

| 13      | DQ5      | 55      | CNTL4      | 97      | A1       |   | 139     | DQ41                      | 1 | 181     | CLK      |

| 14      | MP1      | 56      | MP2        | 98      | MD57     | 7 | 140     | DQ40                      | 1 | 182     | CNTL1    |

| 15      | DQ6      | 57      | CNTL5      | 99      | A0       | 1 | 141     | DQ39                      | 1 | 183     | ŌE       |

| 16      | DQ7      | 58      | CY24       | 100     | RESET    |   | 142     | DQ38                      | 1 | 184     | CNTL2    |

| 17      | DQ8      | 59      | NMI        | 101     | MD56     |   | 143     | MP5                       | 1 | 185     | BW4      |

| 18      | DQ9      | 60      | CY25       | 102     | MP6      | 7 | 144     | DQ37                      | 1 | 186     | CNTL3    |

| 19      | DQ10     | 61      | CNTL6      | 103     | MD55     |   | 145     | MD47                      | 1 | 187     | BW5      |

| 20      | VDDQ     | 62      | CY26       | 104     | VDDQ     |   | 146     | DQ36                      | 1 | 188     | CY0      |

| 21      | VSSQ     | 63      | A13        | 105     | VSSQ     | 1 | 147     | MD46                      | 1 | 189     | BW6      |

| 22      | DQ11     | 64      | CY27       | 106     | MD54     | 1 | 148     | DQ35                      |   | 190     | CY1      |

| 23      | DQ12     | 65      | VDD        | 107     | DQ63     | 7 | 149     | MD45                      | 1 | 191     | BW7      |

| 24      | DQ13     | 66      | CY28       | 108     | MD53     |   | 150     | DQ34                      | 1 | 192     | CY2      |

| 25      | DQ14     | 67      | VSS        | 109     | DQ62     | 7 | 151     | MD44                      | 1 | 193     | CE1A     |

| 26      | DQ15     | 68      | CY29       | 110     | MD52     |   | 152     | DQ33                      | 1 | 194     | CY3      |

| 27      | DQ16     | 69      | A12        | 111     | DQ61     |   | 153     | MD43                      |   | 195     | VDD      |

| 28      | DQ17     | 70      | CY30       | 112     | MD51     | 1 | 154     | DQ32                      | 1 | 196     | CY4      |

| 29      | DQ18     | 71      | A11        | 113     | DQ60     |   | 155     | MD42                      |   | 197     | VSS      |

| 30      | DQ19     | 72      | CY31       | 114     | MD50     |   | 156     | VDDQ                      |   | 198     | CY5      |

| 31      | DQ20     | 73      | A10        | 115     | DQ59     |   | 157     | VSSQ                      |   | 199     | CE2      |

| 32      | VDDQ     | 74      | MP3        | 116     | MD49     |   | 158     | MD41                      |   | 200     | CY6      |

| 33      | VSSQ     | 75      | <b>A</b> 9 | 117     | DQ58     |   | 159     | $\overline{\mathrm{ADV}}$ |   | 201     | CE3      |

| 34      | DQ21     | 76      | CNTL7      | 118     | MD48     |   | 160     | MD40                      |   | 202     | CY7      |

| 35      | DQ22     | 77      | A8         | 119     | DQ57     |   | 161     | ADSP                      |   | 203     | CE4      |

| 36      | DQ23     | 78      | CNTL8      | 120     | DQ56     |   | 162     | MP4                       |   | 204     | MP0      |

| 37      | DQ24     | 79      | CNTL9      | 121     | DQ55     |   | 163     | ADSC                      |   | 205     | CE5      |

| 38      | DQ25     | 80      | CNTL10     | 122     | DQ54     |   | 164     | MD39                      |   | 206     | CY8      |

| 39      | CY16     | 81      | A7         | 123     | DQ53     |   | 165     | $\overline{\mathrm{BW0}}$ |   | 207     | CY9      |

| 40      | DQ26     | 82      | CNTL11     | 124     | VDDQ     |   | 166     | MD38                      |   | 208     | VDDQ     |

| 41      | CY17     | 83      | A6         | 125     | VSSQ     | ] | 167     | BW1                       |   |         |          |

| 42      | DQ27     | 84      | MP7        | 126     | DQ52     |   | 168     | MD37                      | L |         |          |

#### Introduction

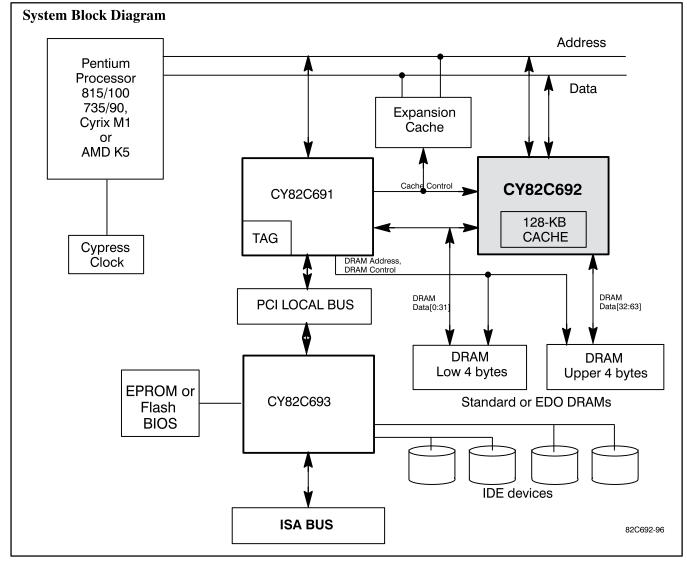

#### **System Overview**

The CY82C691/692/693 hyperCache™ Chipset provides all the functions necessary to implement a 3.3V Pentium-class processor based system with the PCI (Peripheral Component Interconnect) bus and the ISA (Industry Standard Architecture) bus. The chipset consists of the CY82C691 System Controller, the CY82C692 Data Path/Cache chip, and the CY82C693 Peripheral Controller. System designers can exploit the advantages of the PCI bus while maintaining access to the large base of ISA cards in the marketplace.

The Cypress hyperCache Chipset offers system designers several key advantages. With only three chips, CY82C691/692/693, a complete system with a 128-KB, two-way set associative, synchronous pipelined L2 cache can be implemented. The cache size may be increased up to 1 MB with additional CY82C694 16Kx64 SRAMs or other synchronous or pipelined burst SRAMs. Six banks of page-mode or EDO DRAM further increase the system designer's options. The chipset also contains concurrent bus support, PCI enhanced IDE with CD-ROM support, integrated RTC, integrated peripheral control (Interrupts/DMA), and integrated keyboard controller. This chipset is flexible enough to provide the system designer with many cost/performance/function options to provide an optimum solution for a given design.

#### CY82C692 Introduction

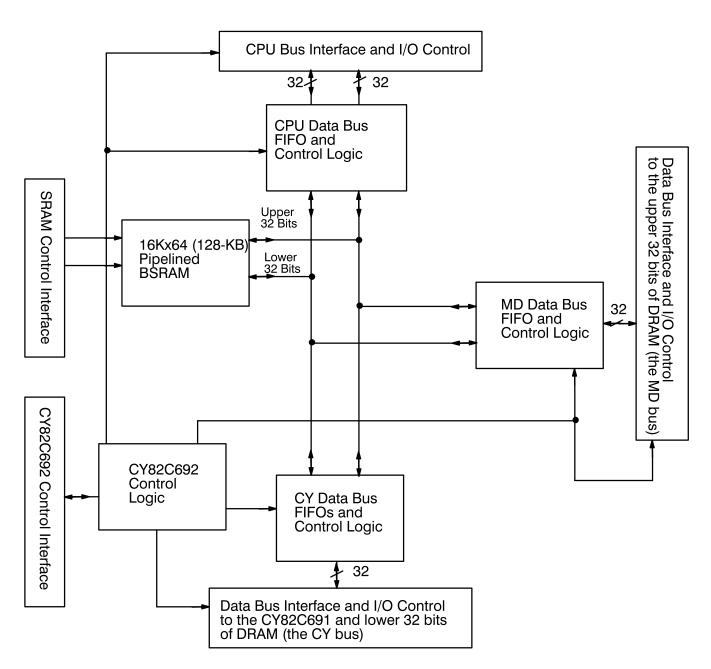

The CY82C692 is a 64-bit data path unit between the DRAM and CPU with an integrated 128-KB (16Kx64) synchronous pipelined Burst SRAM (BSRAM). The CY82C692 serves two main functions: (1) Provides data steering to/from three different interfaces (CPU bus, the DRAM high or MD bus, and the DRAM low or CY bus), and (2) Provides 128 KB of Level 2 cache with an integrated synchronous pipelined BSRAM. With a clock-to-data valid time ( $T_{\rm CO}$ )=8.5 ns, 3-1-1-1 burst cycles are supported at bus frequencies up to 66 MHz.

The CY82C692 contains several sets of FIFOs that serve as Pre-Reading/Post-Writing buffers. These buffers are controlled by signals (Control[11:0]) coming from the CY82C691 System Controller. The Pre-Reading/Post-Writing feature enhances system performance by allowing concurrent transactions on the CPU, PCI, and DRAM buses.

The CY82C692 also contains data parity generation/checking logic for all transactions to/from DRAM memory.

The 3.3V CPU bus interface contains an 8-deep, 64-bit wide FIFO. This FIFO is logically broken into two 32-bit FIFOs in order to properly route data and accommodate for bus size conversions. All data coming from or going to the CPU data bus must pass through the CPU FIFO.

The DRAM interface is divided between the upper 32 bits and lower 32 bits of data. The upper 32 bits (and parity) are transferred on the MD bus. The MD bus is a dedicated connection between the CY82C692 and the upper 32 bits of DRAM memory. The lower 32 bits of data (and parity) are transferred on the CY bus. The CY bus also serves as the data path connecting the PCI bus (via the CY82C691) to the CPU.

The CY82C692 contains an integrated Level 2 cache configured as a 16Kx64 (128-KB) synchronous pipelined BSRAM. The BSRAM can be used as either a direct mappped or two-way set associative L2 cache. The BSRAM is controlled by dedicated control signals coming from the CY82C691 System Controller. The L2 cache can be expanded with additional CY82C694s

(Cypress's 16Kx64 pipelined BSRAM in a 128-pin TQFP) or additional discrete BSRAMs (synchronous or pipelined). Each bank must be comprised of the same type of BSRAM. L2 cache sizes of up to 1 MB are supported, with a maximum of 512 KB per bank.

#### **Pre-Reading/Post-Writing**

The CY82C692 supports Pre-Reading/Post-Writing operations through the use of on-chip 8-deep FIFOs that act as storage buffers. All Pre-Read and Post-Write operations are conducted to/from the on-chip FIFOs. Data is always stored in the FIFO closest to the target interface. By using these buffers in conjunction with on-chip control and routing logic, the CY82C692 is able to support concurrent transactions involving CPU, PCI, and DRAM memory transactions. All of the signals controlling the on-chip FIFOs are generated from the CY82C691 System Controller.

#### Parity Generation/Checking Logic

The CY82C692 contains the logic required for parity generation and checking. When enabled, the CY82C692 will check/generate even byte parity on the DRAM data lines. Generation will be done on all writes to DRAM memory and checking will be performed on all reads. If a parity error is encountered, the CY82C692 will assert an NMI directly to the CPU. Parity generation/checking can be disabled through register settings.

#### **CPU Data Bus Interface**

The CY82C692 interfaces to the CPU data bus through a 3.3V 64-bit interface. On-chip logic divides this interface into two 32-bit words in order to accommodate bus size conversions and concurrent transactions. Each 32-bit word passes through a 8-deep FIFO and three-state buffers.

#### **DRAM Interface**

The CY82C692 connects to DRAM memory through two separate 32-bit data interfaces, the CY and MD buses. The CY bus connects the lower 32-bits of data (and parity) to both the DRAM memory and the CY82C691 System Controller. The CY bus interface contains two 32-bit-wide, 8-deep FIFOs in order to store Pre-Read/Post-Write data. The FIFO is controlled by Control[11:0] from the CY82C691 System Controller. Additionally, all CPU-to-PCI transactions are routed through the CY bus to the CY82C691 System Controller.

The upper 32 bits of DRAM data are transferred on the MD bus. The MD bus is a dedicated interface that connects the CY82C692 with the upper 32 bits of DRAM data (and parity). The MD bus interface contains two 32-bit-wide 8-deep FIFOs that are used to store Pre-Read/Post-Write data destined for upper memory. FIFO control is conducted through Control[11:0].

#### **Integrated Level 2 Cache**

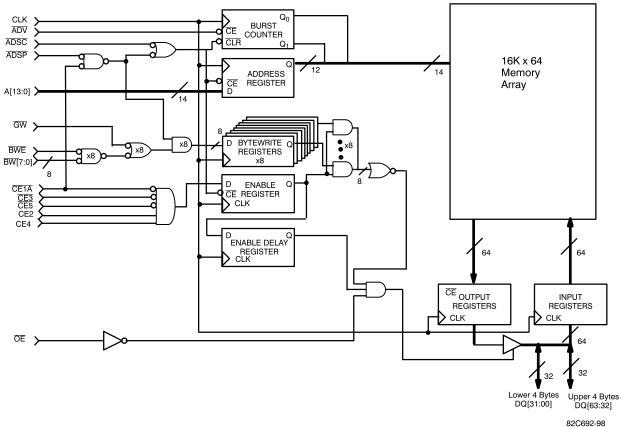

The CY82C692 contains an integrated Level 2 cache configured as a 16Kx64 (128-KB) synchronous pipelined Burst SRAM (BSRAM). The BSRAM operates as a separate device, independent from the other functional blocks of the CY82C692. The BSRAM can be used as either a direct mapped or two-way set associative 128-KB Level 2 cache. Level 2 cache expansion can be accomplished with either additional CY82C694s (up to a total of eight for a 1-MB L2 cache), or additional dedicated BSRAMs (synchronous or pipelined). Each bank must be comprised of the same type of BSRAM. L2 cache sizes of up to 1MB are supported. A maximum of two banks of L2 cache is

allowed, with a maximum of 512 KB per bank. If desired, the BSRAM inside the CY82C692 can also be disabled.

All synchronous inputs to the BSRAM pass through registers controlled by a positive edge triggered single clock (CLK). The synchronous inputs include all addresses, data inputs, write inputs ( $\overline{BW}[7:0]$ ,  $\overline{GW}$ ,  $\overline{BWE}$ ),  $\overline{ADSC}$ ,  $\overline{ADSP}$ ,  $\overline{ADV}$ , and chip enables ( $\overline{CE1A}$ ,  $\overline{CE2}$ ,  $\overline{CE3}$ ,  $\overline{CE4}$ ,  $\overline{CE5}$ ).

All data outputs pass through output registers controlled by the rising edge of the clock. Maximum access delay from the clock rise ( $T_{\rm CO}$ ) is 8.5 ns. A two-bit on-chip wraparound burst counter captures the first address in a burst sequence and automatically increments the address for the rest of the burst access.

The CY82C692 supports secondary cache in systems utilizing either a linear or interleaved burst sequence. The interleaved burst order supports Intel and AMD processors. The linear burst sequence is suited for processors such as the Cyrix M1. The burst order is user selectable, and is determined by writing to a specified register during power-up. Accesses can be initiated with either the processor address strobe  $(\overline{ADSP})$  or the controller address strobe  $(\overline{ADSC})$ . Address advancement through the burst sequence is controlled by the  $\overline{ADV}$  input.

Byte write operations are qualified with the Byte Write Enable  $(\overline{BWE})$  and Byte Write Select  $(\overline{BW0}-7)$  inputs. A Global Write Enable  $(\overline{GW})$  overrides all byte write inputs and writes data to all eight bytes. All writes are simplified with on-chip synchronous self-timed write circuitry.

Five synchronous chip selects  $(\overline{CS1A}, \overline{CS3}, \overline{CS5}, CS2, CS4)$  and an asynchronous output enable  $(\overline{OE})$  provide for easy bank selection and output three-state control.

#### Single Read Accesses

This access is initiated when the following conditions are satisfied at clock rise: (1) ADSP or ADSC is asserted LOW, (2) CS1A, CS3, CS5, CS4, and CS2 are all asserted active, and (3) the write signals (BW0-BW7, GW, BWE) are all deasserted HIGH. The address presented to the address inputs (A0-A13) is stored into the address advancement logic and the Address Register while being presented to the memory core. The corresponding data is allowed to propagate to the input of the Output Registers of the SRAM section. At the rising edge of the next clock the data is allowed to propagate through the output register, through the CPU bus FIFO, and is driven onto the CPU data bus on D[63:00]. The requested data will be available on the CPU bus 8.5 ns after the clock rise. When the asynchronous Output Enable  $(\overline{OE})$  is asserted LOW, the data outputs from the SRAM block are controlled by the Enable and Enable Delay Registers. During the first cycle of an initial read operation the outputs on the CPU bus remain in a three-state condition, regardless of the state of Output Enable (OE). This feature is required in order to support pipelining without creating contention on the data bus when multiple banks of cache are used. Consecutive single read cycles are supported.

#### Single Write Accesses Initiated by ADSP

$\overline{\text{ADSP}}$ -triggered accesses are initiated when both of the following conditions are satisfied at clock rise: (1)  $\overline{\text{ADSP}}$  is asserted LOW, and (2)  $\overline{\text{CS1A}}$ ,  $\overline{\text{CS3}}$ ,  $\overline{\text{CS5}}$ , CS4, and CS2 are all asserted active. The address presented to A0-A13 is loaded into the address register and the address advancement logic while being delivered to the RAM core. The write signals ( $\overline{\text{BW0}}$ - $\overline{\text{BW7}}$ ,  $\overline{\text{GW}}$ ,  $\overline{\text{BWE}}$ ) and  $\overline{\text{ADV}}$  inputs are ignored during this first cycle.

ADSP triggered write accesses require two clock cycles to complete. If the write inputs (BW[7:0] GW, BWE) are asserted LOW on the second clock rise, the data presented to the D0-D63 inputs is written into the corresponding address location in the RAM core. The CY82C692 provides byte write capability. Asserting the appropriate Byte Write (GW, BWE, BW0-BW7) input will selectively write to only the desired bytes. Bytes not selected during a byte write operation will remain unaltered. A Synchronous self-timed write mechanism has also been provided to simplify the write operations.

Since the CY82C692 is a common I/O device, the Output Enable  $(\overline{OE})$  must be deasserted HIGH before presenting data to the D0–D63 inputs. Doing so will three-state the output drivers . As a safety precaution, D0–D63 are automatically three-stated whenever a write cycle is detected, regardless of the state of  $\overline{OE}$ .

#### Single Write Accesses Initiated by ADSC

$\overline{ADSC}$  write accesses in Pipelined mode are initiated when the following conditions are satisfied: (1)  $\overline{ADSC}$  is asserted LOW, (2)  $\overline{ADSP}$  is deasserted HIGH, (3)  $\overline{CS1A}$ ,  $\overline{CS5}$ ,  $\overline{CS3}$ , CS4, and CS2 are all asserted active, and (4) the appropriate write inputs ( $\overline{GW}$ ,  $\overline{BWE}$ ,  $\overline{BW0}$  –  $\overline{BW7}$ ) are asserted active to conduct a write to the desired byte(s).  $\overline{ADSC}$  triggered write accesses require a single clock cycle to complete. The address presented to A0 – A13 is loaded into the address register and the address advancement logic while being delivered to the RAM core. The  $\overline{ADV}$  input is ignored during this cycle. The data presented to to the D0 – D63 is written into the corresponding address location in the RAM core. If a byte write is conducted, only the selected bytes are written. Bytes not selected during a byte write operation will remain unaltered. A Synchronous self-timed write mechanism has also been provided to simplify the write operations.

Since the CY82C692 is a common I/O device, the Output Enable  $(\overline{OE})$  must be deasserted HIGH before presenting data to the D0-D63 inputs. Doing so will three-state the output drivers. As a safety precaution, D0-D63 are automatically three-stated whenever a write cycle is detected, regardless of the state of  $\overline{OE}$ .

#### **Burst Sequences**

The CY82C692 provides a two-bit wraparound counter, fed by A0 and A1, that implement either an interleaved or linear burst sequence. The interleaved burst sequence is designed specifically to support Intel Pentium applications. The linear burst sequence is designed to support processors that follow a linear burst sequence, such as the Cyrix M1. The burst order is determined during bootup by writing to a specific configuration register.

Asserting ADV LOW at clock rise will automatically increment the burst counter to the next address in the burst sequence. Both read and write burst operations are supported.

## **Intel Burst Sequence**

| First Address | Second<br>Address | Third<br>Address | Fourth<br>Address |

|---------------|-------------------|------------------|-------------------|

| Ax+1, $Ax$    | Ax+1, Ax          | Ax+1, Ax         | Ax+1, Ax          |

| 00            | 01                | 10               | 11                |

| 01            | 00                | 11               | 10                |

| 10            | 11                | 00               | 01                |

| 11            | 10                | 01               | 00                |

## **Linear Burst Sequence**

| First Address | Second<br>Address | Third<br>Address | Fourth<br>Address |

|---------------|-------------------|------------------|-------------------|

| Ax+1, Ax      | Ax+1, Ax          | Ax+1, Ax         | Ax+1, Ax          |

| 00            | 01                | 10               | 11                |

| 01            | 10                | 11               | 00                |

| 10            | 11                | 00               | 01                |

| 11            | 00                | 01               | 10                |

## **Cycle Descriptions**

| Next Cycle     | Add. Used | CS2 | CS4 | CS3 | CS5 | CS1A | ADSP | ADSC | ADV | ŌE | DQ   | Writes               |

|----------------|-----------|-----|-----|-----|-----|------|------|------|-----|----|------|----------------------|

| Unselected     | none      | X   | X   | X   | X   | 1    | X    | 0    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | 0   | X   | X   | X   | 0    | 0    | X    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | X   | 0   | X   | X   | 0    | 0    | X    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | X   | X   | 1   | X   | 0    | 0    | X    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | X   | X   | X   | 1   | 0    | 0    | X    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | 0   | X   | X   | X   | 0    | 1    | 0    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | X   | 0   | X   | X   | 0    | 1    | 0    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | X   | X   | 1   | X   | 0    | 1    | 0    | X   | X  | Hi-Z | X                    |

| Unselected     | none      | X   | X   | X   | 1   | 0    | 1    | 0    | X   | X  | Hi-Z | X                    |

| Begin Read     | External  | 1   | 1   | 0   | 0   | 0    | 0    | X    | X   | X  | Hi-Z | X                    |

| Begin Read     | External  | 1   | 1   | 0   | 0   | 0    | 1    | 0    | X   | X  | Hi-Z | Read                 |

| Continue Read  | Next      | X   | X   | X   | X   | X    | 1    | 1    | 0   | 1  | Hi-Z | Read                 |

| Continue Read  | Next      | X   | X   | X   | X   | X    | 1    | 1    | 0   | 0  | DQ   | Read                 |

| Continue Read  | Next      | X   | X   | X   | X   | 1    | X    | 1    | 0   | 1  | Hi-Z | Read                 |

| Continue Read  | Next      | X   | X   | X   | X   | 1    | X    | 1    | 0   | 0  | DQ   | Read                 |

| Suspend Read   | Current   | X   | X   | X   | X   | X    | 1    | 1    | 1   | 1  | Hi-Z | Read                 |

| Suspend Read   | Current   | X   | X   | X   | X   | X    | 1    | 1    | 1   | 0  | DQ   | Read                 |

| Suspend Read   | Current   | X   | X   | X   | X   | 1    | X    | 1    | 1   | 1  | Hi-Z | Read                 |

| Suspend Read   | Current   | X   | X   | X   | X   | 1    | X    | 1    | 1   | 0  | DQ   | Read                 |

| Begin Write    | Current   | X   | X   | X   | X   | X    | 1    | 1    | 1   | X  | Hi-Z | Write <sup>[1]</sup> |

| Begin Write    | Current   | X   | X   | X   | X   | 1    | X    | 1    | 1   | X  | Hi-Z | Write <sup>[1]</sup> |

| Begin Write    | External  | 1   | 1   | 0   | 0   | 0    | 1    | 0    | X   | X  | Hi-Z | Write <sup>[1]</sup> |

| Continue Write | Next      | X   | X   | X   | X   | X    | 1    | 1    | 0   | X  | Hi-Z | Write <sup>[1]</sup> |

| Continue Write | Next      | X   | X   | X   | X   | 1    | X    | 1    | 0   | X  | Hi-Z | Write <sup>[1]</sup> |

| Suspend Write  | Current   | X   | X   | X   | X   | X    | 1    | 1    | 1   | X  | Hi-Z | Write <sup>[1]</sup> |

| Suspend Write  | Current   | X   | X   | X   | X   | 1    | X    | 1    | 1   | X  | Hi-Z | Write <sup>[1]</sup> |

X=Don't Care, 1=Logic HIGH, 0=Logic LOW.

Note:

1. Writes defined by BWE, BW[7:0], and GW, see Write Cycle Description table.

## **Write Cycle Descriptions**

| Function <sup>[2]</sup>  | GW          | BWE         | BW7     | BW6        | BW5   | BW4 | BW3 | BW2 | BW1 | BW0 |

|--------------------------|-------------|-------------|---------|------------|-------|-----|-----|-----|-----|-----|

| Read                     | 1           | 1           | X       | X          | X     | X   | X   | X   | X   | X   |

| Read                     | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 1   | 1   | 1   |

| Write All Byte           | 0           | X           | X       | X          | X     | X   | X   | X   | X   | X   |

| Write Byte 0 – DQ[7:0]   | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 1   | 1   | 0   |

| Write Byte 1 – DQ[15:8]  | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 1   | 0   | 1   |

| Write Byte 2 – DQ[23:16] | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 0   | 1   | 1   |

| Write Byte 3 – DQ[31:24] | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 1   | 1   | 1   |

| Write Byte 4 – DQ[39:32] | 1           | 0           | 1       | 1          | 1     | 0   | 1   | 1   | 1   | 1   |

| Write Byte 5 – DQ[47:40] | 1           | 0           | 1       | 1          | 0     | 1   | 1   | 1   | 1   | 1   |

| Write Byte 6 – DQ[55:48] | 1           | 0           | 1       | 0          | 1     | 1   | 1   | 1   | 1   | 1   |

| Write Byte 7 – DQ[63:56] | 1           | 0           | 0       | 1          | 1     | 1   | 1   | 1   | 1   | 1   |

| Write Byte 1, 0          | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 1   | 0   | 0   |

| Write Byte 2, 1          | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 0   | 0   | 1   |

| Write Byte 2, 0          | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 0   | 1   | 0   |

| Write Byte 2, 1, 0       | 1           | 0           | 1       | 1          | 1     | 1   | 1   | 0   | 0   | 0   |

| Write Byte 3, 0          | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 1   | 1   | 0   |

| Write Byte 3, 1          | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 1   | 0   | 1   |

| Write Byte 3, 1, 0       | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 1   | 0   | 0   |

| Write Byte 3, 2          | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 0   | 1   | 1   |

| Write Byte 3, 2, 0       | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 0   | 1   | 0   |

| Write Byte 3, 2          | 1           | 0           | 1       | 1          | 1     | 1   | 0   | 0   | 1   | 1   |

| The                      | remainder i | follows the | same pa | ttern as a | bove. | •   | -   | -   | •   | -   |

X=Don't Care, 1=Logic HIGH, 0=Logic LOW.

Notes:

2. The SRAM always starts a Read cycle when ADSP is asserted, regardless of the state of GW, BWE, BW[7:0].

## **Pin Descriptions**

| Name      | I/O | Pin Number                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET     | I   | 100                                                                                                                                                                                  | This is the RESET input signal from the CY82C693. It puts the CY82C692 into a known state and invalidates all write-buffer entries.                                                                                                                                                                                                                           |

| CPUCLK    | I   | 181                                                                                                                                                                                  | The CPU clock input. This runs synchronous to the CPU's external clock.                                                                                                                                                                                                                                                                                       |

| D[63:00]  | I/O | 107, 109. 111,<br>113, 115, 117,<br>119-123,<br>126-135,<br>138-142, 144,<br>146, 148, 150,<br>152, 154, 50, 48,<br>46, 44, 42, 40,<br>38-34, 31-22,<br>19-15, 13, 11, 9,<br>7, 5, 3 | The 64-bit CPU data bus interface. These are 3.3V signals.                                                                                                                                                                                                                                                                                                    |

| CY[31:00] | I/O | 72, 70, 68, 66,64, 62, 60, 58, 54, 51, 49, 47, 45, 43, 41, 39, 12, 10, 8, 6, 4, 2, 207, 206, 202, 200, 198, 196, 194, 192, 190, 188                                                  | The CY bus interfaces to the lower 32 DRAM data bits. It also is the data path to pass data to/from the CY82C691 for routing to the PCI bus.                                                                                                                                                                                                                  |

| MD[63:31] | I/O | 86, 88, 90, 92,<br>94, 96, 98, 101,<br>103, 106, 108,<br>110, 112, 114,<br>116, 118, 145,<br>147, 149, 151,<br>153, 155, 158,<br>160, 164, 166,<br>168, 170, 172,<br>174, 176, 178   | The MD bus interfaces to the upper 32 DRAM data bits.                                                                                                                                                                                                                                                                                                         |

| MP[7:0]   | I/O | 84, 102, 143,<br>162, 74, 56, 14,<br>204                                                                                                                                             | Memory parity bits. The CY82C692 generates/checks even byte parity on the DRAM data lines.                                                                                                                                                                                                                                                                    |

| NMI       | О   | 59                                                                                                                                                                                   | Non-maskable interrupt line to the CPU. Used to inform the CPU that a parity error has been detected.                                                                                                                                                                                                                                                         |

| A[13:0]   | I   | 63, 69, 71, 73,<br>75, 77, 81, 83,<br>85, 87, 89, 95,<br>97, 99                                                                                                                      | Address inputs to the cache BSRAM, sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                   |

| GW        | I   | 177                                                                                                                                                                                  | Global Write Enable input. Used in to conduct global writes. When asserted, $\overline{GW}$ overrides all byte writes, and a global write occurs. When used with the CY82C691 and CY82C693, this pin should be tied HIGH through a 1K $\Omega$ resistor.                                                                                                      |

| BWE       | I   | 179                                                                                                                                                                                  | Byte Write Enable input. Used in conjunction with $\overline{BW}[7:0]$ to conduct byte write operations. $\overline{BW}[7:0]$ are qualified with $\overline{BWE}$ . When asserted, $\overline{GW}$ overrides all byte writes, and a global write occurs. When used with the CY82C691 and CY82C693, this pin should be tied LOW through a $1K\Omega$ resistor. |

| BW[7:0]   | I   | 191, 189, 187,<br>185, 175, 173,<br>167, 165                                                                                                                                         | Byte write inputs to the cache BSRAM, synchronous, sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                   |

| CE1A      | I   | 193                                                                                                                                                                                  | Chip enable and ADSP mask.                                                                                                                                                                                                                                                                                                                                    |

## Pin Descriptions (continued)

| Name                                 | I/O    | Pin Number                                          | Description                                                                                                                                                                                                                                                                   |

|--------------------------------------|--------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE2, <u>CE3</u> ,<br>CE4, <u>CE5</u> | I      | 199, 201, 203,<br>205                               | Expansion decode inputs for L2 cache expansion. Used to establish and decode the expansion position of each CY82C692.                                                                                                                                                         |

| ŌE                                   | I      | 183                                                 | Asynchronous Output Enable. Active LOW, used in conjunction with Control[11:00] to control the three-state buffers onto the CPU bus.                                                                                                                                          |

| ADV                                  | I      | 159                                                 | Advance input signal to the BSRAM section only, active LOW, sampled on the rising edge of the clock. When detected active it will cause the on-chip burst counter to increment to the next address in the burst sequence. This signal is ignored if ADSP or ADSC is asserted. |

| ADSC                                 | I      | 163                                                 | Address input strobe from the controller, active LOW, sampled on the rising edge of the clock. When asserted, the address inputs are captured in the address register. A0 and A1 are also loaded into the two-bit burst counter. ADSC is ignored when asserted with ADSP.     |

| ADSP                                 | I      | 161                                                 | Address input strobe from the processor, active LOW, sampled on the rising edge of the clock. When asserted, the address inputs are captured in the address register. A0 and A1 are also loaded into the two-bit burst counter.                                               |

| CONTROL<br>[11:00]                   | I      | 82, 80-78, 76,<br>61, 57, 55, 186,<br>184, 182, 180 | Control inputs. These are the inter-chip communication signals between the CY82C691 and CY82C692. These signals are used to control the FIFOs, logic, three-stating, and data steering inside the CY82C692.                                                                   |

| $V_{\mathrm{DDQ}}$                   | Supply | 20, 32, 52, 104,<br>124, 136, 156,<br>208           | 3.3 or 5V power supply for the I/Os of the to the CY82C692.                                                                                                                                                                                                                   |

| $V_{ m DD}$                          | Supply | 65, 91, 169, 195                                    | 5V power supply to the core of the CY82C692.                                                                                                                                                                                                                                  |

| $ m V_{DDQ}$                         | GND    | 1, 21, 33, 53,<br>105, 125, 137,<br>157             | Ground for the I/Os of the CY82C692.                                                                                                                                                                                                                                          |

| $V_{SS}$                             | GND    | 67, 93, 171, 197                                    | Ground for the core of the CY82C692.                                                                                                                                                                                                                                          |

### **Maximum Ratings**

| (Above which the useful life may be impaired. For user guidelines, not tested.)           |

|-------------------------------------------------------------------------------------------|

| Storage Temperature $-65^{\circ}$ C to $+150^{\circ}$ C                                   |

| Ambient Temperature with Power Applied                                                    |

| Supply Voltage on $V_{\mbox{\scriptsize DD}}$ Relative to GND $\ldots$ –0.5V to +7.0V     |

| DC Voltage Applied to Outputs in High Z State <sup>[3]</sup> $-0.5$ V to $V_{DD} + 0.5$ V |

| DC Input Voltage <sup>[2]</sup> $-0.5$ V to $V_{DD} + 0.5$ V                              |

| Current into Outputs (LOW) | 20 mA   |

|----------------------------|---------|

| Static Discharge Voltage   | >2001V  |

| Latch-Up Current           | >200 mA |

## **Operating Range**

| Range | Ambient<br>Temperature <sup>[4]</sup> | $V_{ m DD}$ | $V_{ m DDQ}$          |

|-------|---------------------------------------|-------------|-----------------------|

| Com'l | $0^{\circ}$ C to $+70^{\circ}$ C      | 5V ± 5%     | $3.0V$ to $V_{ m DD}$ |

### Electrical Characteristics Over the Operating Range

| Parameter       | Description                                      | Test Conditions                                                                                                                                                                                                                                 |       | Min. | Max.                | Unit |

|-----------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------------------|------|

| V <sub>OH</sub> | Output HIGH Voltage                              | $V_{DD} = Min., I_{OH} = -5.0 \text{ mA}$                                                                                                                                                                                                       |       | 2.4  | $V_{\mathrm{DDQ}}$  | V    |

| $V_{OL}$        | Output LOW Voltage                               | $V_{DD} = Min., I_{OL} = 5.0 \text{ mA}$                                                                                                                                                                                                        |       |      | 0.4                 | V    |

| $V_{IH}$        | Input HIGH Voltage                               |                                                                                                                                                                                                                                                 |       | 2.0  | $V_{\rm DD} + 0.3V$ | V    |

| $V_{IL}$        | Input LOW Voltage <sup>[2]</sup>                 |                                                                                                                                                                                                                                                 |       | -0.3 | 0.8                 | V    |

| I <sub>X</sub>  | Input Load Current                               | $GND \le V_I \le V_{DD}$                                                                                                                                                                                                                        | -1    | 1    | μΑ                  |      |

| $I_{OZ}$        | Output Leakage Current                           | $GND \le V_I \le V_{DD,}$ Output Disable                                                                                                                                                                                                        | -5    | 5    | μΑ                  |      |

| I <sub>OS</sub> | Output Short Circuit Current <sup>[5]</sup>      | V <sub>DD</sub> =Max., V <sub>OUT</sub> =GND                                                                                                                                                                                                    |       |      | -300                | mA   |

| $I_{CC}$        | V <sub>DD</sub> Operating Supply Current         | $V_{DD}$ =Max., Iout=0mA,<br>$f=f_{MAX} = 1/t_{CYC}$                                                                                                                                                                                            | Com'l |      | 350                 | mA   |

| $I_{SB1}$       | Automatic CS Power-Down<br>Current—TTL Inputs    | $\begin{array}{l} \text{Max. V}_{\text{DD}}, \overline{\text{CS}} \geq \text{V}_{\text{IH}}, \text{V}_{\text{IN}} \geq \text{V}_{\text{IH}} \\ \text{or V}_{\text{IN}} \leq \text{V}_{\text{IL}}, \text{f} = \text{f}_{\text{MAX}} \end{array}$ | Com'l |      | 100                 | mA   |

| $I_{SB2}$       | Automatic CS Power-Down<br>Current – CMOS Inputs | Max. $V_{DD}$ , $\overline{CS} \ge V_{DD} - 0.3V$ , $V_{IN} \ge V_{DD} - 0.3V$ or $V_{IN} \le 0.3V$ , $f = 0^{[6]}$                                                                                                                             | Com'l |      | 45                  | mA   |

#### Capacitance<sup>[7]</sup>

| Parameter                      | Description        | Test Conditions                         | Max. | Unit |

|--------------------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub> : Addresses    | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 4.5  | pF   |

| C <sub>IN</sub> : Other Inputs |                    | $V_{\rm DD} = 5.0 V$                    | 5    | pF   |

| C <sub>OUT</sub>               | Output Capacitance |                                         | 8    | pF   |

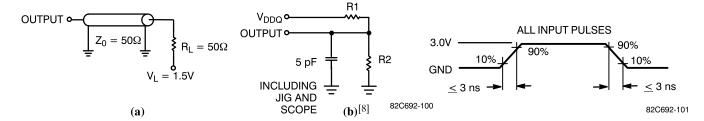

#### **AC Test Loads and Waveforms**

### **Ordering Information**

| Speed (ns) | Ordering Code | Package<br>Name | Package Type                    | Operating<br>Range |

|------------|---------------|-----------------|---------------------------------|--------------------|

| 8          | CY82C692-XXX  | TBD             | 208-Lead Plastic Quad Flat Pack | Commercial         |

| 10         | CY82C692-XXX  | TBD             | 228-Lead Plastic Quad Flat Pack | Commercial         |

#### **Notes:**

- 2. Minimum voltage equals -2.0V for pulse durations of less than 20 ns.

- 3. T<sub>A</sub> is the "instant on" case temperature.

- 5. Not more than one output should be shorted at one time. Duration of the short circuit should not exceed 30 seconds.

- 6. Inputs are disabled, clock is allowed to run at speed.

- Tested initially and after any design or process changes that may affect these parameters.

- 8. Resistor values for  $V_{DDQ}$ =5V are: R1=1179 $\Omega$  and R2=868 $\Omega$  Resistor values for  $V_{DDQ}$ =3.3V are R1=317 $\Omega$  and R2=348 $\Omega$

Document #: 38-00458

<sup>©</sup> Cypress Semiconductor Corporation, 1995. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.