**CIS8201**

SimpliPHY<sup>™</sup> Gigabit Ethernet PHY Series

Single Port, Low Power, 10 / 100 / 1000BASE-T PHYwith GMII / MII, RGMII, TBI and RTBI MAC Interfaces

# **1** General Description

Enabling widespread, low-cost, Gigabit-to-the-Desktop deployment, Cicada's low-power, single chip CIS8201 integrates a complete triple speed (10BASE-T, 100BASE-TX, and 1000BASE-T) Ethernet physical layer transceiver in two small footprint package options. RJ-45 footprint compatible options are a 128-pin Plastic Low-Profile Quad Flat Pack (LQFP) package, and a 11x11mm footprint 100-ball LBGA package.

The 1000BASE-T transceiver features the industry standard GMII/MII, plus the pin-saving RGMII / RTBI system interfaces. Unlike competitors' products, the CIS8201 integrates self-calibrating series termination resistors on MAC interface pins, simplifying system design significantly by eliminating more than a dozen external components. These innovative terminations also reduce PCB layout complexity, increase system timing margins, and minimize EMI engineering challenges. In addition, the CIS8201 includes innovative on-chip RGMII timing compensation circuits on the MAC interface pins to simplify PCB design.

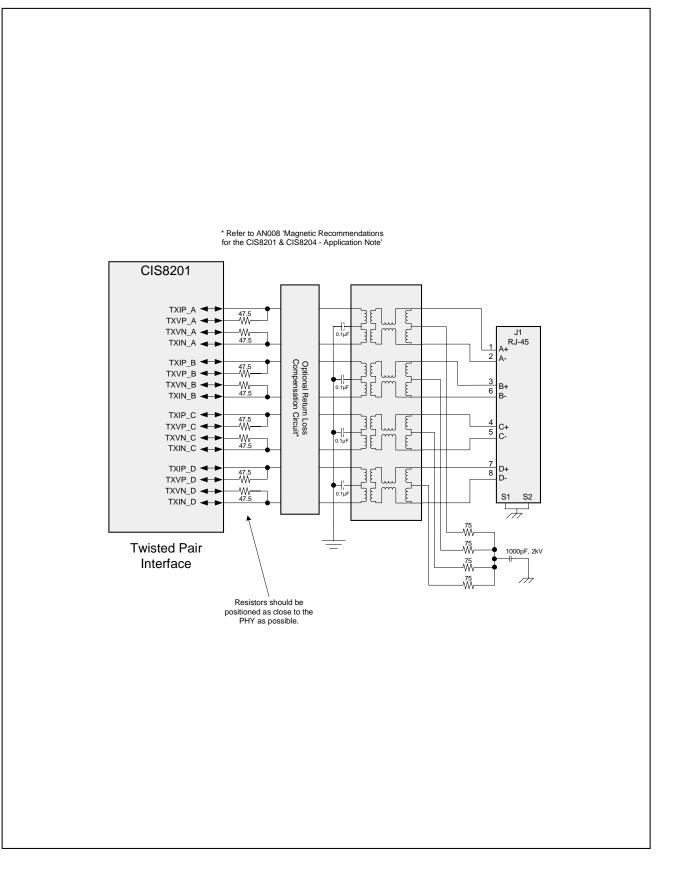

The twisted pair interface includes an innovative internal hybrid and a very low EMI line driver with robust Cable Sourced ESD (CESD) performance, allowing the use of the lowest-cost 1:1 magnetic modules, minimum external components, and less complex PCB traces. To further reduce system complexity and cost, the CIS8201 can optionally be powered from a single 3.3V power supply when utilizing the device's on-chip regulator control circuit to produce the 1.5V core power supply voltage.

The CIS8201 leverages Cicada's proprietary **2nd generation SimpliPHY™ DSP Technology**, key to enabling an extremely low-power Gigabit PHY on a single chip. Cicada's mixed signal and DSP architecture yields robust performance, supporting both full- and half-duplex 10BASE-T, 100BASE-TX, and 1000BASE-T Ethernet over unshielded twisted pair (UTP) cable, with more than 5dB of design margin with respect to all worst-case impairments (NEXT, FEXT, Echo, and system noise). The industry's highest-performance, low-power DSP-based transceiver utilizes an optimum trellis decoding algorithm in concert with all digital gain control and timing recovery.

To enable maximum network management feedback to the host system and the user, Cicada-provided software routines, referred to as the VeriPHY<sup>™</sup> Link Management Suite, allow extensive network and cable plant operating and status information, such as the cable length and the effective Bit Error Rate (BER), to be easily integrated with NIC or switch software, greatly simplifying Gigabit Ethernet network deployment and management.

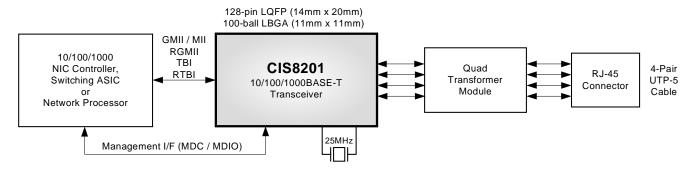

# 2 System Diagram

## 3 Features

- <1.0W power consumption

- · Optional on-chip regulator control circuit

- Advanced Power Management complies with PC99/ PC2000, Wake on LAN<sup>™</sup>, & PCI 2.2 power requirements

- Fully IEEE 802.3, 802.3u (10BASE-T, 100BASE-TX), & 802.3ab (1000BASE-T) compliant

- Automatic detection & correction of cable pair swaps, pair skew, & pair polarity, along with an Auto MDI/MDI-X crossover function

- Choice of standard GMII/MII or TBI, or pin-saving RGMII/RTBI interfaces

- Self-calibrating, series termination resistors on MAC interface pins

- Unique on-chip RGMII timing compensation supports both 2.5V and 3.3V RGMII operation

- Optional integrated oscillator circuit

- >10KB jumbo frame support with programmable synchronization FIFOs

- Six direct drive LED pins

- Low EMI line drivers with robust CESD performance

- Manufactured in mainstream, 3.3V/1.5V digital CMOS process

- · Choice of two small footprint packages:

- 14x20mm LQFP

- 11x11mm LBGA

# **4** Applications

- Desktop and Server NICs

- · LAN-on-Motherboard and Mobile PC NICs

## **Benefits**

- · Eliminates expensive regulators, heat sinks & fans

- Enables a single 3.3V supply design for lowest cost

- Enables widespread, low-cost, 1000BASE-T deployment in desktop LOM, NICs, & switches

- Ensures full specification compliance & seamless deployment throughout Category-5 networks with the industry's highest performance & noise immunity

- Compatible with first generation 1000BASE-T PHYs, allowing trouble-free migration to 1000BASE-T by minimizing common interoperability problems

- Connects to existing GMII and TBI-based MACs, or significantly reduces pin-count requirements on MAC & switching ASICs from 24 (GMII) to 12 (RGMII).

- Eases board designs & EMI challenges, improves MAC I/F signal integrity, lowers power consumption, & eliminates >12 external components on a system board

- Decreases board design efforts, increases PCB timing margins & yields, & shortens time to market

- Supports single low-cost 25MHz crystal, or either a 25MHz or 125MHz standard reference clock input

- Provides for maximum jumbo frame sizes in custom SAN & LAN systems

- · LED flexibility with minimum external components

- Reduces EMI & qualification engineering risks & efforts

- Minimizes costs & enables highest PHY integration levels & process portability

- Low cost plastic packaging compatible with compact PC LAN-on-Motherboards

- · Workgroup and Desktop Switches/Routers

- SAN Switches and NAS Appliances

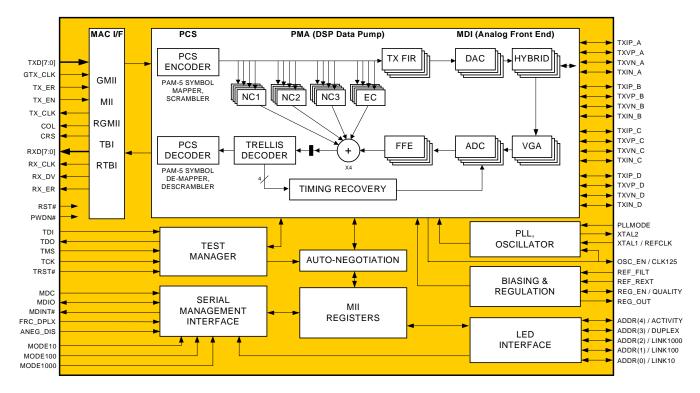

# 5 Device Block Diagram

Figure 5-1. CIS8201 Block Diagram

# **Table of Contents**

| 1  | Gene              | RAL DESCRIPTION                                                                                                                                   | 1         |

|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2  | Syste             | ем Diagram                                                                                                                                        | 1         |

| 3  | FEATU             | JRES & BENEFITS                                                                                                                                   | 2         |

| 4  | Appli             | CATIONS                                                                                                                                           | 2         |

| 5  | DEVIC             | E BLOCK DIAGRAM                                                                                                                                   | 3         |

| 6  | RELE              | VANT SPECIFICATIONS & DOCUMENTATION                                                                                                               | 11        |

| 7  | Data              | SHEET CONVENTIONS                                                                                                                                 | 12        |

| 8  | Func <sup>-</sup> | TIONAL OVERVIEW                                                                                                                                   |           |

|    | 8.1               | MAC INTERFACE (GMII / RGMII / MII, OR TBI / RTBI)                                                                                                 |           |

|    | 8.2               | Twisted Pair Interface (TPI)                                                                                                                      | 13        |

|    | 8.3               | Serial Management Interface (SMI)                                                                                                                 |           |

|    | 8.4               | Parallel LED Interface (PLI)                                                                                                                      |           |

|    | 8.5               | SYSTEM CLOCK INTERFACE (SCI)                                                                                                                      |           |

|    | 8.6               | Test Mode Interface (TMI)                                                                                                                         |           |

|    | 8.7               | ANALOG FRONT END (AFE)                                                                                                                            |           |

|    | 8.8               | DSP DATA PUMP CORE                                                                                                                                |           |

|    | 8.9               | Physical Coding Sublayer (PCS)                                                                                                                    | 15        |

|    | 8.10              | SYNCHRONIZATION FIFOs                                                                                                                             | 16        |

|    | 8.11              | OPTIONAL FIXED POWER SUPPLY REGULATOR                                                                                                             | 16        |

| 9  | Раск              | AGE PIN ASSIGNMENTS & SIGNAL DESCRIPTIONS                                                                                                         |           |

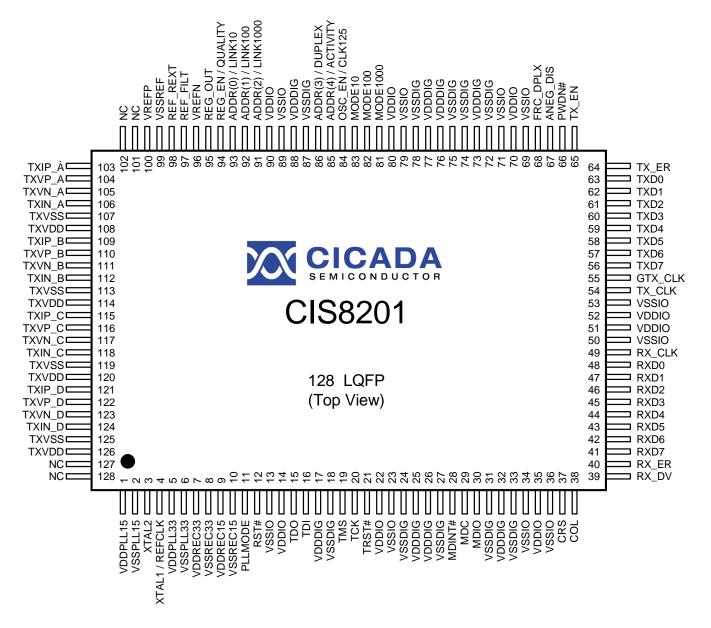

| -  | 9.1               | 128 Pin LQFP Package Pinout Diagram                                                                                                               |           |

|    | 9.2               | 11 x 11mm 100 Ball LBGA Package Ballout Diagram.                                                                                                  |           |

|    | 9.3               | PIN DESCRIPTIONS                                                                                                                                  |           |

|    | 9.4               | SIGNAL TYPE DESCRIPTIONS                                                                                                                          |           |

|    | 9.5               | MAC TRANSMIT INTERFACE PINS (MAC TX)                                                                                                              |           |

|    | 9.6               | MAC Receive Interface Pins (MAC RX)                                                                                                               |           |

|    | 9.7               | Twisted Pair Interface Pins (TPI)                                                                                                                 |           |

|    | 9.8               | Serial Management Interface Pins (SMI)                                                                                                            |           |

|    | 9.9               | CONFIGURATION AND CONTROL PINS (CONFIG)                                                                                                           | 27        |

|    | 9.10              | SYSTEM CLOCK INTERFACE PINS (SCI)                                                                                                                 |           |

|    | 9.11              | Parallel LED Interface Pins (PLI)                                                                                                                 |           |

|    | 9.12              | JTAG TEST ACCESS PORT (TAP)                                                                                                                       |           |

|    | 9.13              | REGULATOR CONTROL AND ANALOG BIAS PINS (AP)                                                                                                       |           |

|    | 9.14              | No Connects (NC)                                                                                                                                  |           |

|    | 9.15              | DIGITAL POWER SUPPLY PINS FOR LQFP PACKAGE                                                                                                        |           |

|    | 9.16              | DIGITAL POWER SUPPLY PINS FOR LBGA PACKAGE                                                                                                        |           |

|    | 9.17              | Analog Power Supply Pins for LQFP Package                                                                                                         |           |

|    | 9.18              | Analog Power Supply Pins for LBGA Package                                                                                                         |           |

| 40 | C.VOT             | EM SCHEMATICS                                                                                                                                     |           |

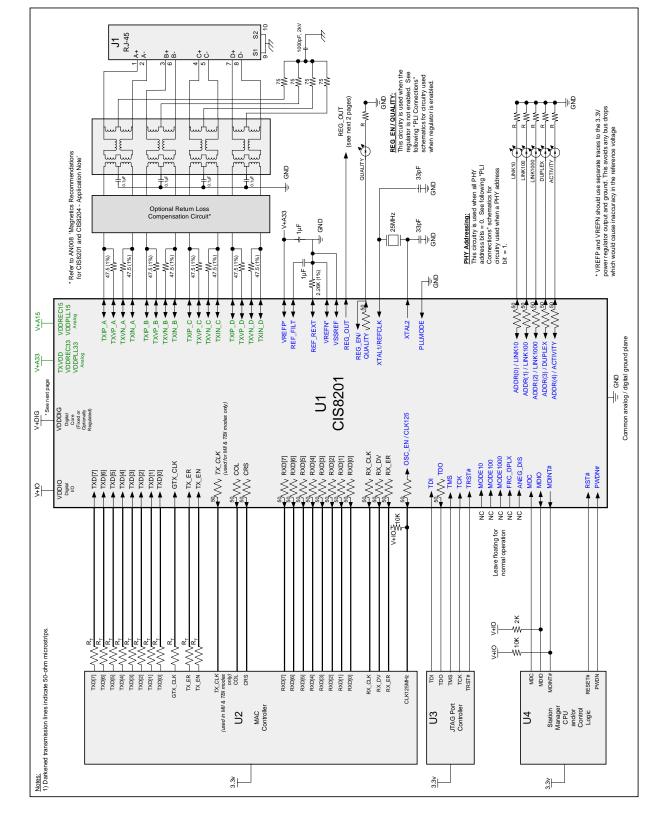

| 10 |                   | EM SCHEMATICS<br>GENERAL SYSTEM SCHEMATIC (SEPARATE 3.3V AND 1.5V SUPPLY APPLICATION WITH REGULATOR DISABLED)                                     | <b>33</b> |

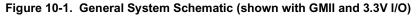

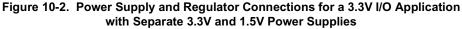

|    | 10.1              | GENERAL SYSTEM SCHEMATIC (SEPARATE 3.3V AND 1.5V SUPPLY APPLICATION WITH REGULATOR DISABLED)<br>SEPARATE 3.3V AND 1.5V POWER SUPPLY CONFIGURATION | کک<br>م د |

|    | 10.2<br>10.3      | 3.3V Power Supply with Optional Fixed Regulator at 1.5V                                                                                           |           |

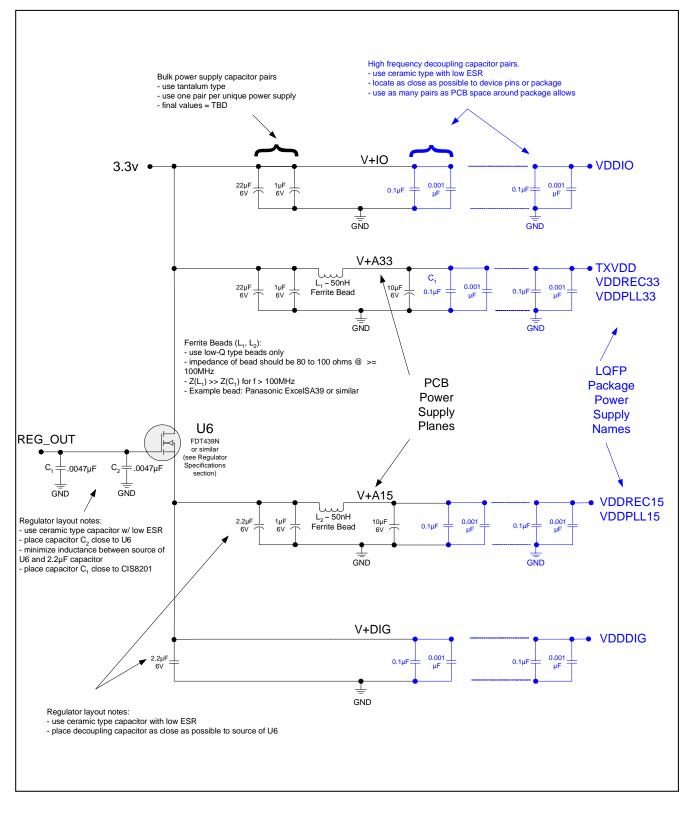

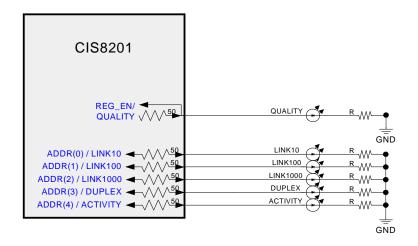

|    | 10.3              | 2.3V POWER SUPPLY WITH OPTIONAL FIXED REGULATOR AT 1.5V<br>PLI CONNECTIONS                                                                        |           |

| -  |                   |                                                                                                                                                   |           |

| 11 | MAC               | INTERFACES                                                                                                                                        |           |

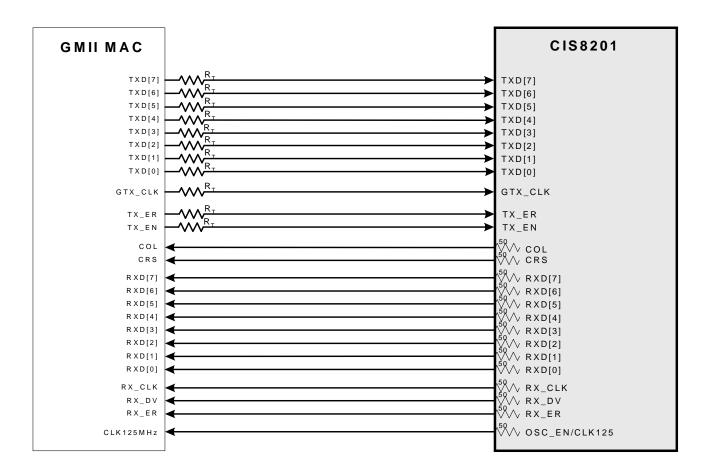

|    | 11.1              | GMII MAC I/F                                                                                                                                      | -         |

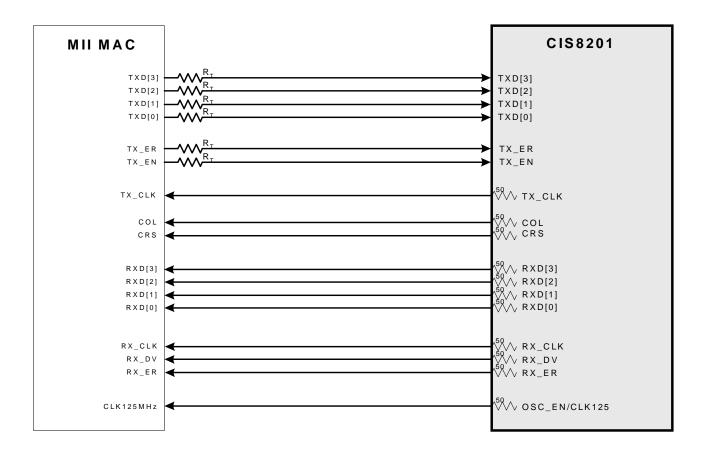

|    |                   | MII MAC I/F                                                                                                                                       |           |

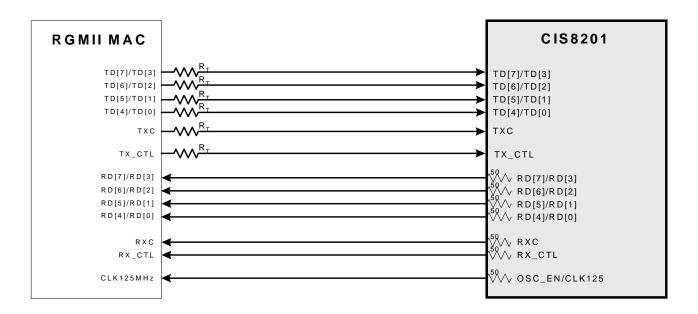

|    | 11.3              | RGMII MAC I/F                                                                                                                                     |           |

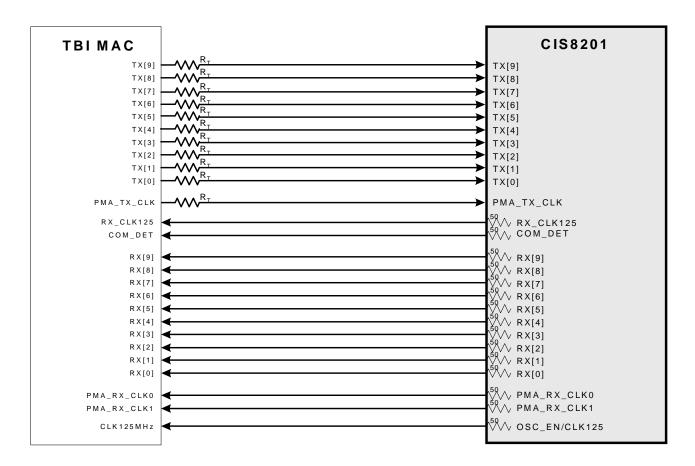

|    | 11.4              | TBI MAC I/F                                                                                                                                       |           |

|    | 11.5              | RTBI MAC I/F                                                                                                                                      | 41        |

| 12 |                   | L MANAGEMENT INTERFACE (SMI)                                                                                                                      |           |

| -  | 12.1              | SMI INTERRUPT                                                                                                                                     |           |

| 12 |                   | LLEL LED INTERFACE                                                                                                                                |           |

|    |                   |                                                                                                                                                   |           |

| 14 |                   | Mode Interface (JTAG)                                                                                                                             |           |

|    | 14.1              | SUPPORTED INSTRUCTIONS AND INSTRUCTION CODES                                                                                                      |           |

|    | 14.2              | BOUNDARY-SCAN REGISTER CELL ORDER                                                                                                                 |           |

|    | 14.3              | NAND TREE TEST MODE                                                                                                                               |           |

| 15 | ΙΝΙΤΙΑΙ      | IZATION & CONFIGURATION                                                                                                 |      |

|----|--------------|-------------------------------------------------------------------------------------------------------------------------|------|

|    | 15.1         | RESETS                                                                                                                  |      |

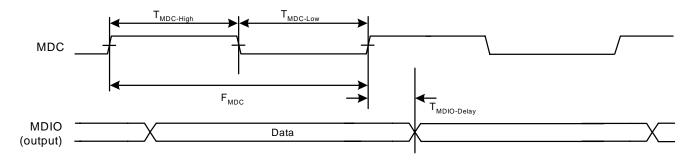

|    | 15.2         | Power-Up Sequence                                                                                                       |      |

|    | 15.3         | MANUAL CONFIGURATION                                                                                                    |      |

|    |              |                                                                                                                         |      |

|    | 15.5         | MAC I/F CONFIGURATION                                                                                                   |      |

|    | 15.6<br>15.7 | SYSTEM CLOCK INTERFACE (SCI)<br>Auto MDI / MDI-X Function                                                               |      |

|    | 15.7<br>15.8 | Parallel LED I/F                                                                                                        |      |

|    |              | ACTIPHYTM POWER MANAGEMENT                                                                                              |      |

|    | 15.10        | Power Supply Decoupling and Board Layout Guidelines                                                                     | .54  |

|    |              | EGISTER SET CONVENTIONS                                                                                                 |      |

|    |              | MII REGISTER NAMES & ADDRESSES                                                                                          |      |

|    | 16.1<br>16.2 | RESET-STICKY BITS                                                                                                       |      |

|    |              | MII REGISTER MAP QUICK REFERENCE (SHEET 1 OF 2)                                                                         |      |

|    | 16.4         | MII REGISTER MAP QUICK REFERENCE (SHEET 2 OF 2)                                                                         | .07  |

|    |              |                                                                                                                         |      |

|    |              |                                                                                                                         |      |

|    | 17.1<br>17.2 | REGISTER 0 (00H) – MODE CONTROL REGISTER<br>REGISTER 1 (01H) – MODE STATUS REGISTER                                     |      |

|    | 17.2<br>17.3 | REGISTER T (0TH) – MODE STATUS REGISTER<br>REGISTER 2 (02H) – PHY IDENTIFIER REGISTER #1                                |      |

|    | 17.4         | REGISTER 2 (02H) – PHY IDENTIFIER REGISTER #1                                                                           | .03  |

|    | 17.5         | REGISTER 4 (04H) – AUTO-NEGOTIATION ADVERTISEMENT REGISTER                                                              | .00  |

|    | 17.6         | REGISTER 5 (05H) – AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER                                                       |      |

|    | 17.7         | REGISTER 6 (06H) – AUTO-NEGOTIATION EXPANSION REGISTER                                                                  | 66   |

|    | 17.8         | REGISTER 7 (07H) – AUTO-NEGOTIATION NEXT-PAGE TRANSMIT REGISTER                                                         | . 67 |

|    | 17.9         | REGISTER 8 (08H) – AUTO-NEGOTIATION LINK PARTNER NEXT-PAGE RECEIVE REGISTER                                             |      |

|    |              | REGISTER 9 (09H) – 1000BASE-T CONTROL REGISTER                                                                          |      |

|    |              | REGISTER 10 (0AH) – 1000BASE-T STATUS REGISTER                                                                          |      |

|    |              | REGISTER 11 (0BH) – RESERVED REGISTER                                                                                   |      |

|    |              | REGISTER 12 (0CH) – RESERVED REGISTER                                                                                   |      |

|    |              | REGISTER 13 (0DH) – RESERVED REGISTER<br>REGISTER 14 (0EH) – RESERVED REGISTER                                          |      |

|    |              | REGISTER 14 (0EH) – RESERVED REGISTER<br>REGISTER 15 (0FH) – 1000BASE-T STATUS EXTENSION REGISTER #1                    |      |

|    |              | REGISTER 15 (0FH) – 1000BASE-T STATUS EXTENSION REGISTER #1<br>REGISTER 16 (10H) – 100BASE-TX STATUS EXTENSION REGISTER |      |

|    | 17.18        | REGISTER 17 (11H) – 1000BASE-T STATUS EXTENSION REGISTER #2                                                             | .77  |

|    |              | REGISTER 18 (12H) – BYPASS CONTROL REGISTER                                                                             |      |

|    |              | REGISTER 19 (13H) – RECEIVE ERROR COUNTER REGISTER                                                                      |      |

|    |              | REGISTER 20 (14H) – FALSE CARRIER SENSE COUNTER REGISTER                                                                |      |

|    |              | REGISTER 21 (15H) – DISCONNECT COUNTER REGISTER                                                                         |      |

|    |              | REGISTER 22 (16H) – 10BASE-T CONTROL & STATUS REGISTER                                                                  |      |

|    |              | REGISTER 23 (17H) – EXTENDED PHY CONTROL REGISTER #1                                                                    |      |

|    | 17.25        | REGISTER 24 (18H) – EXTENDED PHY CONTROL REGISTER #2                                                                    | .87  |

|    |              | REGISTER 25 (19H) – INTERRUPT MASK REGISTER                                                                             |      |

|    | 17.27        | REGISTER 26 (1AH) – INTERRUPT STATUS REGISTER<br>REGISTER 27 (1BH) – PARALLEL LED CONTROL REGISTER                      | .91  |

|    | 17.20        | REGISTER 27 (1DH) – TARALLEL LED CONTROL REGISTER<br>REGISTER 28 (1CH) – AUXILIARY CONTROL & STATUS REGISTER            | 95   |

|    |              | REGISTER 29 (1DH) – DELAY SKEW STATUS REGISTER                                                                          |      |

|    |              | REGISTER 30 (1EH) – RESERVED REGISTER                                                                                   |      |

|    |              | REGISTER 31 (1FH) – RESERVED REGISTER                                                                                   |      |

| 18 | ELECT        | RICAL SPECIFICATION                                                                                                     | 100  |

|    | 18.1         | Absolute Maximum Ratings                                                                                                |      |

|    | 18.2         | RECOMMENDED OPERATING CONDITIONS.                                                                                       |      |

|    | 18.3         | THERMAL APPLICATION DATA                                                                                                |      |

|    | 18.4         | THERMAL SPECIFICATIONS                                                                                                  |      |

|    | 18.5         | CURRENT AND POWER CONSUMPTION - APPLICATION SCENARIOS                                                                   | 103  |

|    | 18.6         | CRYSTAL SPECIFICATIONS                                                                                                  |      |

|    | 18.7         | REGULATOR SPECIFICATIONS                                                                                                | 105  |

| 19 | DC S         | PECIFICATIONS                                                                                                           | 106  |

|    | 19.1         | Digital Pins                                                                                                            |      |

|    | 19.2         | Twisted Pair Interface Pins                                                                                             | 106  |

| 20 |              | MING SPECIFICATIONS                                                                                                     |      |

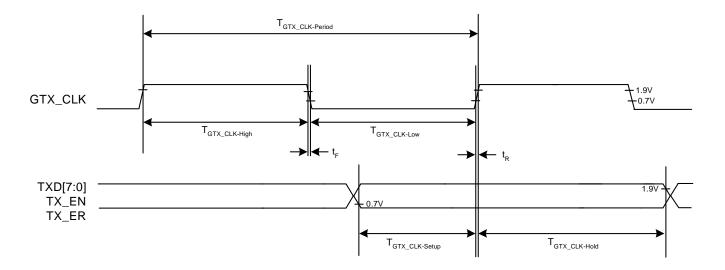

|    | 20.1         | GMII MODE TRANSMIT TIMING (1000BASE-T)                                                                                  |      |

|    | 20.2         | GMII MODE TRANSMIT TIMING (1000DASE-T)                                                                                  |      |

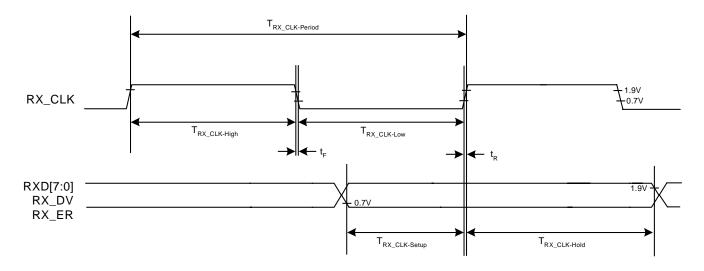

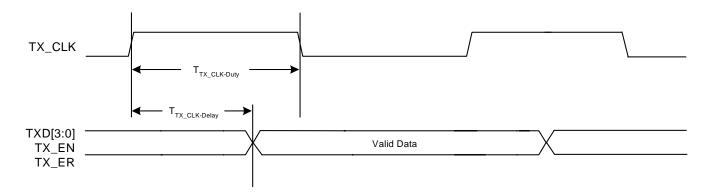

|    | 20.3         | MII TRANSMIT TIMING (100MB/S)                                                                                           |      |

|    |              |                                                                                                                         |      |

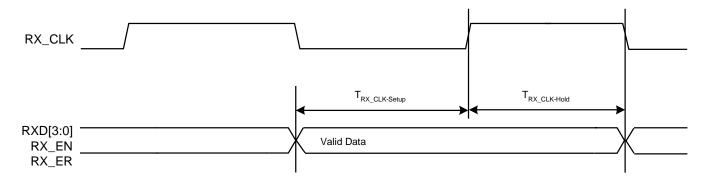

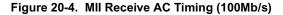

| 20.4 MII RECEIVE TIMING (100MB/s)                   |     |

|-----------------------------------------------------|-----|

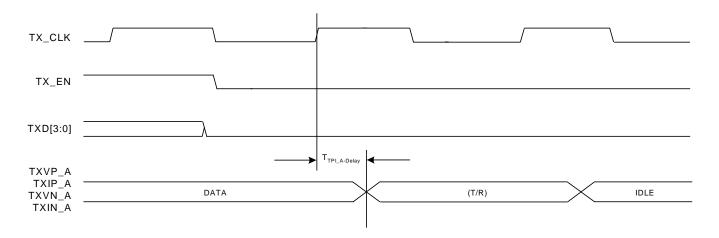

| 20.5 100BASE-TX TRANSMIT PACKET DEASSERTION TIMING  |     |

| 20.6 100BASE-TX Transmit Timing (TR/F & JITTER)     |     |

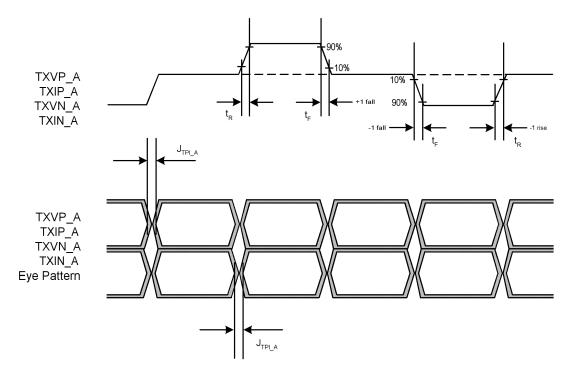

| 20.7 100BASE-TX RECEIVE PACKET LATENCY TIMING       |     |

| 20.8 100BASE-TX RECEIVE PACKET DEASSERTION TIMING   |     |

| 20.9 RGMII/RTBI Mode Timing                         |     |

| 20.9.1 RGMII/RTBI-UNCOMPENSATED MODE TIMING         |     |

| 20.9.2 RGMII/RTBI-COMPENSATED MODE TIMING           |     |

| 20.10 TBI Mode Transmit Timing                      |     |

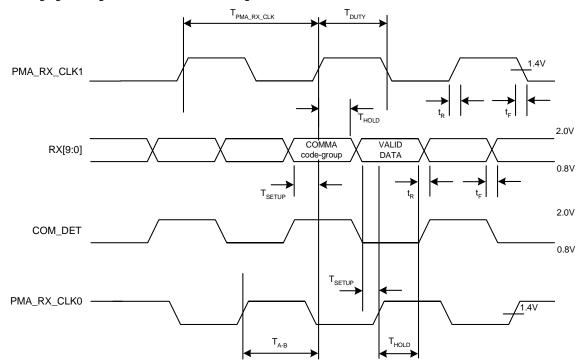

| 20.11 TBI Mode Receive Timing                       |     |

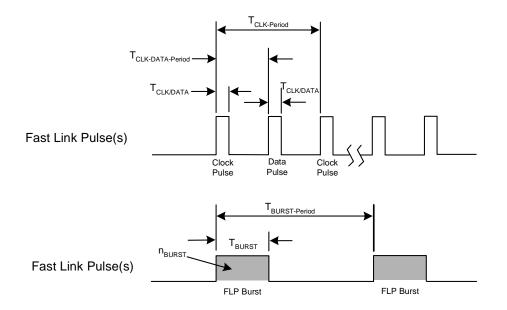

| 20.12 Auto-Negotiation Fast Link Pulse (FLP) Timing |     |

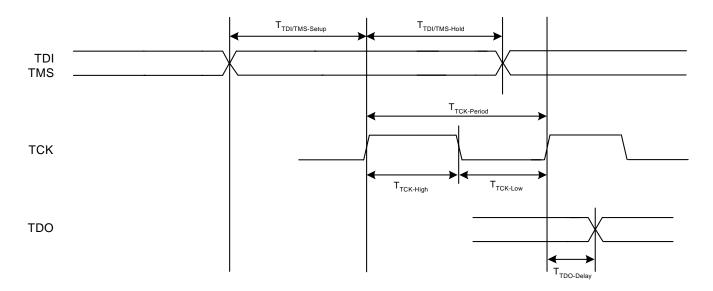

| 20.13 JTAG TIMING                                   |     |

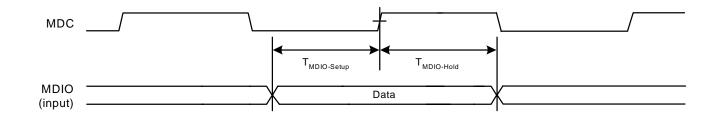

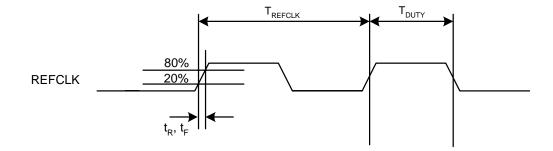

| 20.14 SMI TIMING                                    |     |

| 20.15 MDINT# TIMING                                 |     |

| 20.16 Power-Down and Reset Timing                   |     |

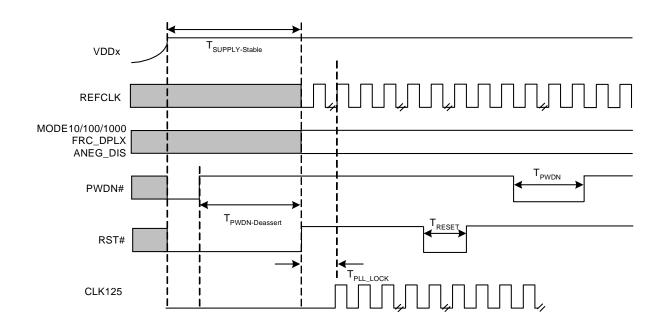

| 20.17 REFCLK TIMING                                 |     |

| 20.18 CLK125 TIMING                                 |     |

| 20.19 REGULATOR TIMING                              |     |

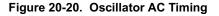

| 20.20 Oscillator Timing                             |     |

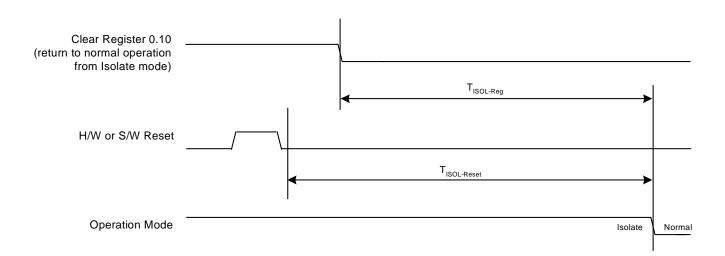

| 20.21 ISOLATION TIMING                              |     |

| 21 MAGNETICS SPECIFICATIONS                         |     |

| 22 IMPORTANT DESIGN CONSIDERATIONS                  | 120 |

| 22.1 GMII TRANSMIT AND RECEIVE                      |     |

| 22.1 Givin Transmit and Receive                     |     |

| 22.3 Shorted Center Taps on TPI Interface           |     |

| 22.4 Isolate Bit Considerations                     |     |

| 22.5 TRANSMIT WAVEFORMS                             | -   |

| 22.5 TRANSMIT WAVEFORMS                             |     |

| 22.0 CAS LATENCY                                    |     |

|                                                     |     |

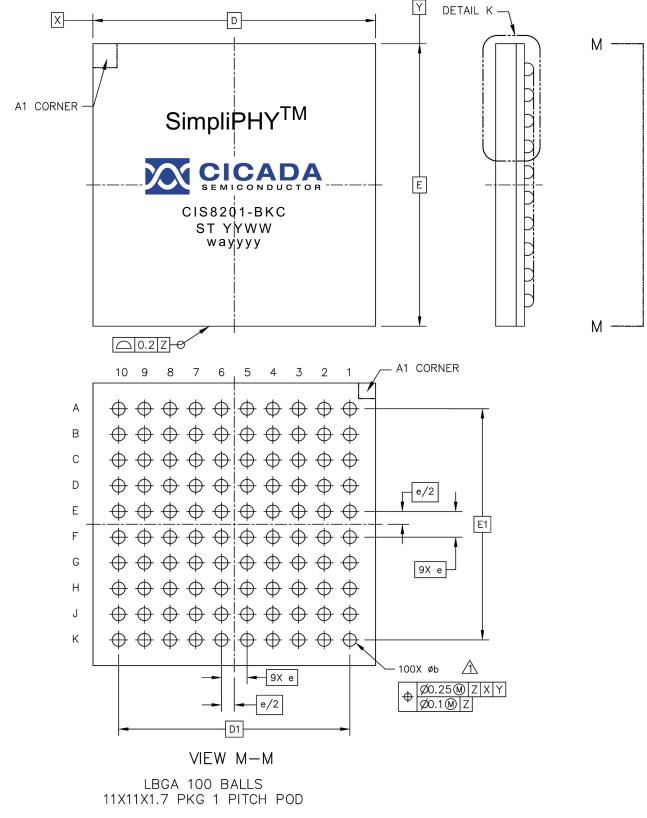

| 24 100-BALL LBGA MECHANICAL SPECIFICATION           | 132 |

| 25 ORDERING INFORMATION                             |     |

| 26 PRODUCT SUPPORT                                  |     |

| 26.1 Available Documents and Application Notes      |     |

| 26.2 CONTACT INFORMATION.                           |     |

| 27 DOCUMENT HISTORY & NOTICES                       |     |

# List of Figures

| FIGURE 2-1.   | CIS8201 System Diagram                                                                                      | 1   |

|---------------|-------------------------------------------------------------------------------------------------------------|-----|

| FIGURE 5-1.   | CIS8201 BLOCK DIAGRAM                                                                                       | 3   |

| FIGURE 9-1.   | CIS8201 PACKAGE PINOUT                                                                                      | 17  |

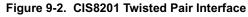

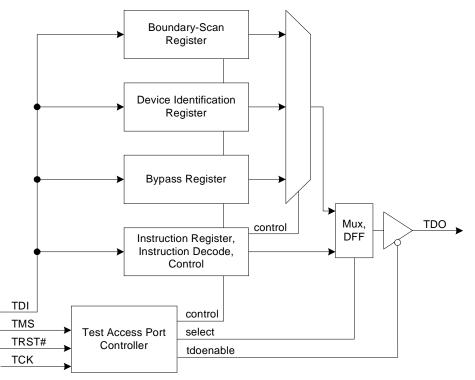

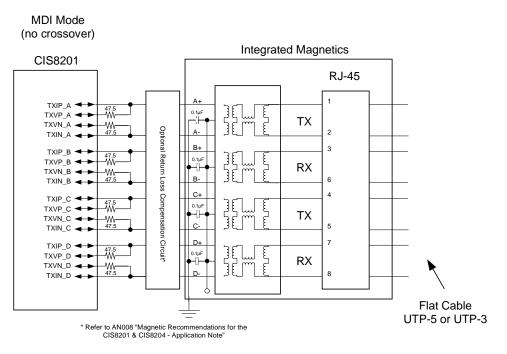

| FIGURE 9-2.   | CIS8201 Twisted Pair Interface                                                                              | 26  |

| FIGURE 10-1.  | GENERAL SYSTEM SCHEMATIC (SHOWN WITH GMII AND 3.3V I/O)                                                     | 33  |

| FIGURE 10-2.  | POWER SUPPLY AND REGULATOR CONNECTIONS FOR A 3.3V I/O APPLICATION WITH SEPARATE 3.3V AND 1.5 POWER SUPPLIES |     |

| FIGURE 10-3.  | POWER SUPPLY CONNECTIONS FOR A 3.3V I/O APPLICATION WITH A SINGLE 3.3V SUPPLY AND OPTIONAL FIXE REGULATOR   |     |

| FIGURE 10-4.  | PLI CONNECTIONS FOR ALL PHY ADDRESS AND REG_EN BITS = 0                                                     | 36  |

| FIGURE 10-5.  | PLI CONNECTIONS FOR ALL PHY ADDRESS AND REG_EN BITS = 1                                                     | 36  |

| FIGURE 11-1.  | GMII MAC INTERFACE                                                                                          | 37  |

| FIGURE 11-2.  | MII MAC INTERFACE                                                                                           | 38  |

| FIGURE 11-3.  | RGMII MAC INTERFACE                                                                                         | 39  |

| FIGURE 11-4.  | TBI MAC INTERFACE                                                                                           | 40  |

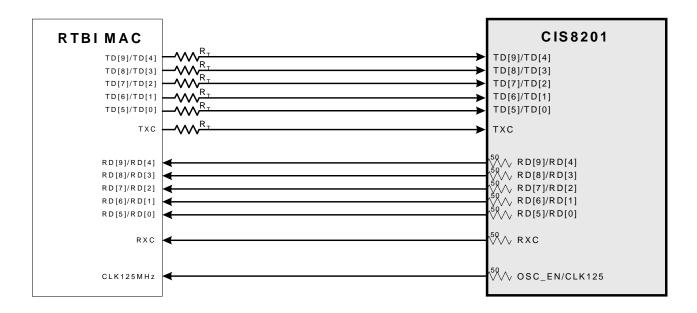

| FIGURE 11-5.  | RTBI MAC INTERFACE                                                                                          | 41  |

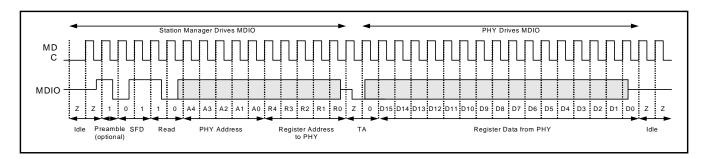

| FIGURE 12-1.  | MDIO READ FRAME                                                                                             | 43  |

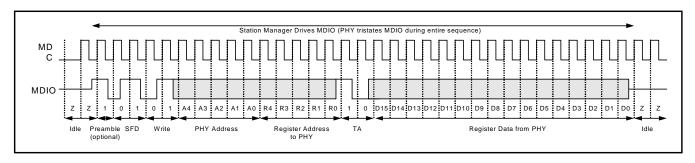

| FIGURE 12-2.  | MDIO WRITE FRAME                                                                                            | 43  |

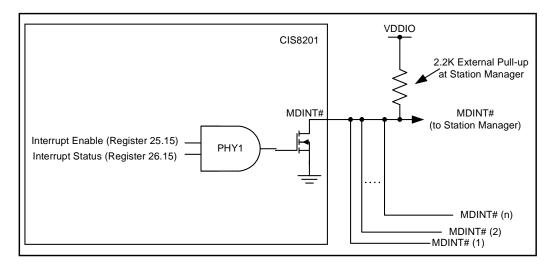

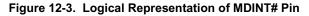

| FIGURE 12-3.  | LOGICAL REPRESENTATION OF MDINT# PIN                                                                        | 43  |

| FIGURE 13-1.  | LED OUTPUT PIN EQUIVALENT CIRCUIT                                                                           | 44  |

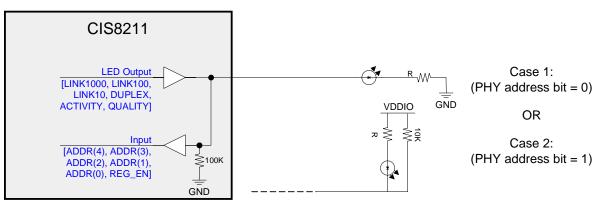

| FIGURE 14-1.  | TEST ACCESS PORT AND BOUNDARY SCAN ARCHITECTURE                                                             | 45  |

| FIGURE 14-2.  | NAND TREE LOGIC DIAGRAMS                                                                                    | 49  |

| FIGURE 15-1.  | MDI / MDI-X CROSSOVER EXAMPLE                                                                               | 54  |

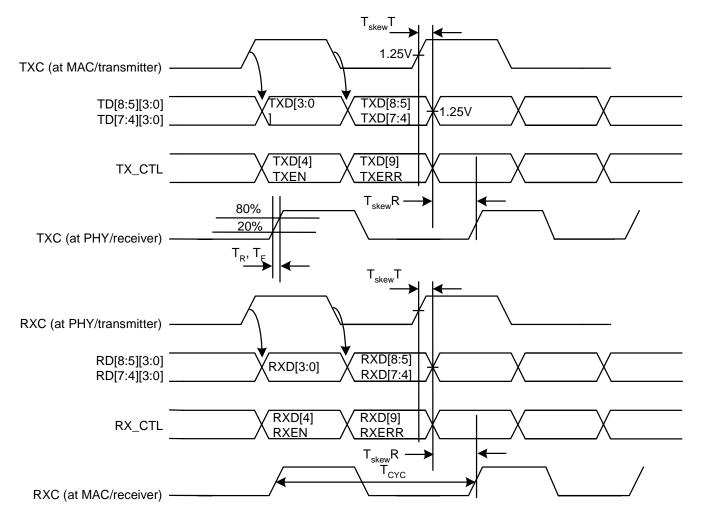

| FIGURE 20-1.  | GMII TRANSMIT AC TIMING IN 1000BASE-T MODE                                                                  | 107 |

| FIGURE 20-2.  | GMII RECEIVE AC TIMING IN 1000BASE-T MODE                                                                   | 108 |

| FIGURE 20-3.  | MII TRANSMIT AC TIMING (100MB/S)                                                                            | 109 |

| FIGURE 20-4.  | MII RECEIVE AC TIMING (100MB/S)                                                                             | 109 |

| FIGURE 20-5.  | 100BASE-TX TRANSMIT PACKET DEASSERTION AC TIMING                                                            | 110 |

| FIGURE 20-6.  | 100BASE-TX TRANSMIT AC TIMING (TR/F & JITTER)                                                               | 111 |

| FIGURE 20-7.  | 100BASE-TX RECEIVE PACKET LATENCY AC TIMING                                                                 | 112 |

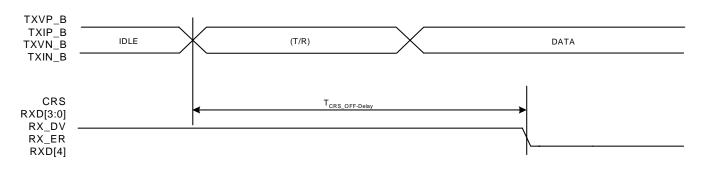

| FIGURE 20-8.  | 100BASE-TX RECEIVE PACKET DEASSERTION AC TIMING                                                             | 113 |

| FIGURE 20-9A. | RGMII/RTBI UNCOMPENSATED AC TIMING AND MULTIPLEXING                                                         | 115 |

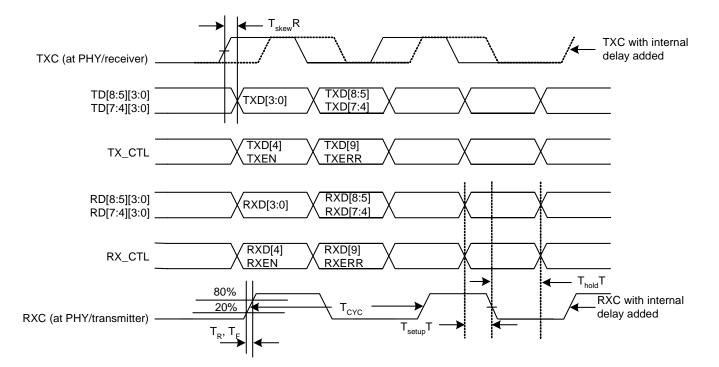

| FIGURE 20-9B. | RGMII/RTBI COMPENSATED AC TIMING AND MULTIPLEXING                                                           | 116 |

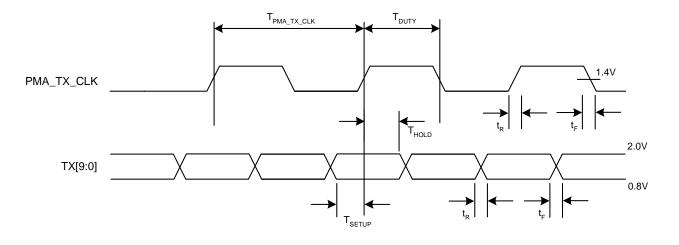

| FIGURE 20-10. | TBI TRANSMIT AC TIMING                                                                                      | 118 |

| FIGURE 20-11. | TBI RECEIVE AC TIMING                                                                                       | 119 |

| FIGURE 20-12. | AUTO-NEGOTIATION FLP AC TIMING                                                                              | 120 |

| FIGURE 20-13. | JTAG INTERFACE AC TIMING                                                                                    | 121 |

| FIGURE 20-14. | SMI AC TIMING                                                                                               | 122 |

| FIGURE 20-16. | POWER-DOWN AND RESET AC TIMING                                                                              | 123 |

| FIGURE 20-17. | REFCLK AC TIMING                                                                                            | 124 |

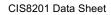

| FIGURE 20-18. | CLK125 AC TIMING                                                                                            | 125 |

| FIGURE 20-19. | REGULATOR AC TIMING                             | 126 |

|---------------|-------------------------------------------------|-----|

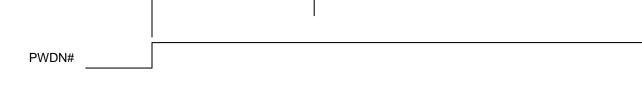

| FIGURE 20-20. | OSCILLATOR AC TIMING                            | 126 |

| FIGURE 20-21. | ISOLATION AC TIMING                             | 127 |

| FIGURE 21-1.  | INTEGRATED MAGNETICS                            | 129 |

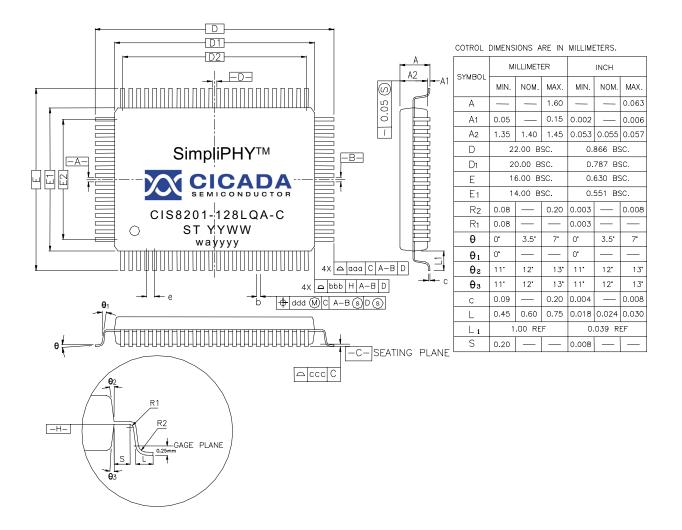

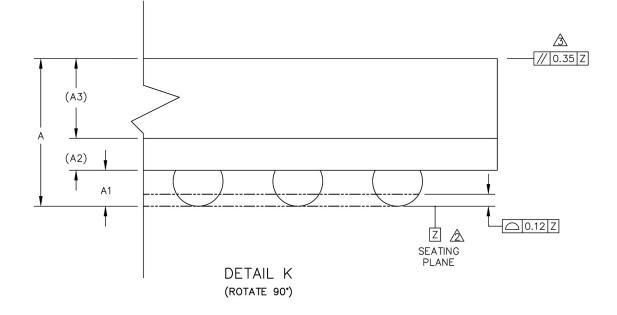

| FIGURE 23-1.  | 128 LQFP MECHANICAL SPECIFICATION               | 131 |

| FIGURE 24-1.  | 100 LBGA MECHANICAL SPECIFICATION - PAGE 1 OF 2 | 132 |

| FIGURE 24-2.  | 100 LBGA MECHANICAL SPECIFICATION - PAGE 2 OF 2 | 133 |

|               |                                                 |     |

# **List of Tables**

| TABLE 6-1.  | CIS8201 RELEVANT SPECIFICATIONS                               | 11  |

|-------------|---------------------------------------------------------------|-----|

| TABLE 7-1.  | DATA SHEET CONVENTIONS                                        | 12  |

| TABLE 8-1.  | SYNCHRONIZATION FIFOS                                         | 16  |

| TABLE 9-1.  | SIGNAL TYPE DESCRIPTIONS                                      | 19  |

| TABLE 9-2.  | MAC TX SIGNAL DESCRIPTIONS                                    | 20  |

| TABLE 9-3.  | MAC RX SIGNAL DESCRIPTIONS                                    | 22  |

| TABLE 9-4.  | TPI SIGNAL DESCRIPTIONS                                       | 25  |

| TABLE 9-5.  | SMI SIGNAL DESCRIPTIONS                                       | 27  |

| TABLE 9-6.  | CONFIG SIGNAL DESCRIPTIONS                                    | 27  |

| TABLE 9-7.  | SCI SIGNAL DESCRIPTIONS                                       | 29  |

| TABLE 9-8.  | PLI SIGNAL DESCRIPTIONS                                       | 29  |

| TABLE 9-9.  | JTAG TAP SIGNAL DESCRIPTIONS                                  |     |

| TABLE 9-10. | AP SIGNAL DESCRIPTIONS                                        |     |

| TABLE 9-11. | NC SIGNAL DESCRIPTIONS                                        | 31  |

| TABLE 9-12. | DIGITAL POWER SUPPLY SIGNAL DESCRIPTIONS FOR LQFP PACKAGE     | 31  |

| TABLE 9-13. | DIGITAL POWER SUPPLY SIGNAL DESCRIPTIONS FOR LBGA PACKAGE     | 31  |

| TABLE 9-14. | ANALOG POWER SUPPLY SIGNAL DESCRIPTIONS FOR LQFP PACKAGE      |     |

| TABLE 9-15. | ANALOG POWER SUPPLY SIGNAL DESCRIPTIONS FOR LBGA PACKAGE      |     |

| TABLE 12-1. | SMI FRAME FORMAT                                              | 42  |

| TABLE 13-1. | PLI BIT DEFINITIONS                                           | 44  |

| TABLE 14-1. | JTAG DEVICE IDENTIFICATION REGISTER DESCRIPTION               | 45  |

| TABLE 14-2. | JTAG INTERFACE INSTRUCTION CODES                              | 46  |

| TABLE 14-3. | JTAG BOUNDARY-SCAN PORT ORDER                                 | 48  |

| TABLE 14-4. | NAND TREE CHAINS                                              | 49  |

| TABLE 15-1. | INITIALIZATION TYPES                                          | 50  |

| TABLE 15-2. | MAC I/F Mode Descriptions                                     | 52  |

| TABLE 15-3. | ACCEPTED MDI PAIR CONNECTION COMBINATIONS                     | 53  |

| TABLE 16-1. | MII REGISTER BIT MODES                                        | 55  |

| TABLE 16-2. | MII REGISTER NAMES & ADDRESSES                                | 55  |

| TABLE 16-3. | RESET-STICKY BITS                                             | 56  |

| TABLE 17-1. | 1000BASE-T TRANSMITTER/RECEIVER TEST MODES                    | 69  |

| TABLE 17-2. | 1000BASE-T TRANSMITTER/RECEIVER TEST MODE 4 – QUINARY SYMBOLS | 70  |

| TABLE 17-3. | CLK125 PIN MULTIPLEXED CLOCK SIGNALS                          | 80  |

| TABLE 17-4. | 10BASE-T CURRENT REFERENCE TRIM VALUES                        | 84  |

| TABLE 17-5. | GMII TRANSMIT PIN ORDERING                                    | 86  |

| TABLE 17-6. | 100/1000BASE-T TRANSMIT VOLTAGE REFERENCE TRIM VALUES         |     |

| TABLE 17-7. | CONFIGURATION CONTROL PIN SETTINGS                            | 97  |

| TABLE 18-1. | Absolute Maximum Ratings                                      | 100 |

| TABLE 18-2. | RECOMMENDED OPERATING CONDITIONS                              | 101 |

| TABLE 18-3. | THERMAL APPLICATION DATA                                      | 102 |

| TABLE 18-4. | THERMAL SPECIFICATIONS - 128 PIN LQFP                         | 102 |

|             |                                                               |     |

| TABLE 18-5.  | THERMAL SPECIFICATIONS - 100 BALL LBGA                          |     |

|--------------|-----------------------------------------------------------------|-----|

| TABLE 18-6.  | CURRENT AND POWER CONSUMPTION - APPLICATION I                   |     |

| TABLE 18-7.  | CURRENT AND POWER CONSUMPTION - APPLICATION II                  |     |

| TABLE 18-8.  | CURRENT AND POWER CONSUMPTION - APPLICATION III                 |     |

| TABLE 18-9.  | CURRENT AND POWER CONSUMPTION - APPLICATION IV                  |     |

| TABLE 18-10. | CRYSTAL SPECIFICATIONS                                          |     |

| TABLE 18-11. | REGULATOR SPECIFICATIONS                                        |     |

| TABLE 19-1.  | DIGITAL PINS SPECIFICATIONS                                     |     |

| TABLE 19-2.  | TPI TRANSMITTER DC SPECIFICATIONS                               |     |

| TABLE 20-1.  | GMII MODE TRANSMIT AC TIMING SPECIFICATIONS (1000BASE-T)        |     |

| TABLE 20-2.  | GMII MODE RECEIVE AC TIMING SPECIFICATIONS (1000BASE-T)         |     |

| TABLE 20-3.  | MII TRANSMIT AC TIMING SPECIFICATIONS (100MB/S)                 |     |

| TABLE 20-4.  | MII RECEIVE AC TIMING SPECIFICATIONS (100MB/S)                  |     |

| TABLE 20-5.  | 100BASE-TX TRANSMIT PACKET DEASSERTION AC TIMING SPECIFICATIONS | 110 |

| TABLE 20-6.  | 100BASE-TX TRANSMIT AC TIMING SPECIFICATIONS (TR/F & JITTER)    | 111 |

| TABLE 20-7.  | 100BASE-TX RECEIVE PACKET LATENCY AC TIMING SPECIFICATIONS      | 112 |

| TABLE 20-8.  | 100BASE-TX RECEIVE PACKET DEASSERTION AC TIMING SPECIFICATIONS  |     |

| TABLE 20-9A. | RGMII/RTBI-UNCOMPENSATED MODE AC TIMING SPECIFICATIONS          | 114 |

| TABLE 20-9B. | RGMII/RTBI-COMPENSATED MODE AC TIMING SPECIFICATIONS            | 116 |

| TABLE 20-10. | TBI MODE TRANSMIT AC TIMING SPECIFICATIONS                      | 118 |

| TABLE 20-11. | TBI MODE RECEIVE AC TIMING SPECIFICATIONS                       | 119 |

| TABLE 20-12. | AUTO-NEGOTIATION FLP AC TIMING SPECIFICATIONS                   |     |

| TABLE 20-13. | JTAG INTERFACE AC TIMING SPECIFICATIONS                         |     |

| TABLE 20-14. | SMI AC TIMING SPECIFICATIONS                                    |     |

| TABLE 20-15. | MDINT# AC TIMING SPECIFICATIONS                                 |     |

| TABLE 20-16. | POWER-DOWN AND RESET AC TIMING SPECIFICATIONS                   |     |

| TABLE 20-17. | REFCLK AC TIMING SPECIFICATIONS                                 |     |

| TABLE 20-18. | CLK125 AC TIMING SPECIFICATIONS                                 |     |

| TABLE 20-19. | REGULATOR AC TIMING SPECIFICATIONS                              |     |

| TABLE 20-20. | OSCILLATOR AC TIMING SPECIFICATIONS                             |     |

| TABLE 20-21. | ISOLATION AC TIMING SPECIFICATIONS                              |     |

| TABLE 21-1.  | MAGNETICS SPECIFICATIONS                                        |     |

| TABLE 25-1.  | DEVICE ORDERING INFORMATION                                     |     |

| TABLE 25-2.  | EVALUATION SYSTEM ORDERING INFORMATION                          |     |

| TABLE 27-1.  | DOCUMENT HISTORY & NOTICES                                      |     |

# 6 Relevant Specifications & Documentation

The CIS8201 conforms to the following specifications. Please refer to these documents for additional information.

| Specification - Revision                      | Description                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE 802.3-2000                               | Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications. IEEE 802.3-2000 consolidates and supersedes the following specifications: 802.3ab (1000BASE-T), 802.3z (1000BASE-X), 802.3u (Fast Ethernet), with references to ANSI X3T12 TP-PMD standard (ANSI X3.263 TP-PMD). |

| IEEE 1149.1-1990                              | Test Access Port and Boundary Scan Architecture <sup>1</sup> .<br>Includes IEEE Standard 1149.1a-1993 and IEEE Standard 1149.1b-1994.                                                                                                                                                                                              |

| JEDEC EIA/JESD8-5                             | 2.5V±0.2V (Normal Range), and 1.8V to 2.7V (Wide Range) Power Supply Voltage and Interface Stan-<br>dard for Nonterminated Digital Integrated Circuits.                                                                                                                                                                            |

| JEDEC JESD22-A114-B                           | Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM).<br>Revision of JESD22-A114-A.                                                                                                                                                                                                                            |

| JEDEC JESD22-A115-A                           | Electrostatic Discharge (ESD) Sensitivity Testing Machine Model (MM).<br>Revision of EIA/JESD22-A115.                                                                                                                                                                                                                              |

| JEDEC EIA/JESD78                              | IC Latch-Up Test Standard.                                                                                                                                                                                                                                                                                                         |

| MIL-STD-883E                                  | Miltary Test Method Standard for Microcircuits.                                                                                                                                                                                                                                                                                    |

| RGMII Specification <sup>2</sup> - v1.3, v2.0 | Reduced Pin-Count Interface for Gigabit Ethernet Physical Layer Devices (per Hewlett Packard).<br>Includes both RGMII and RTBI standards.                                                                                                                                                                                          |

| PICMG 2.16                                    | IP Backplane for CompactPCI.                                                                                                                                                                                                                                                                                                       |

<sup>1</sup> Often referred to as the "JTAG" test standard.

<sup>2</sup> The CIS8201 RGMII interface is timing and electrically compatible with the RGMII v1.3 specification. The CIS8201 RGMII interface is timing only and not electrically compatible with the RGMII v2.0 specification.

# 7 Data Sheet Conventions

Conventions used throughout this data sheet are specified in the following table.

| Table 7-1. Data Sheet Conver | ntions |

|------------------------------|--------|

|------------------------------|--------|

| Convention                   | Syntax                                              | Examples          | Description                                                                           |

|------------------------------|-----------------------------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Register<br>number           | RegisterNumber.Bit<br>or<br>RegisterNumber.BitRange | 23.10<br>23.12:10 | Register 23 (address 17h), bit 10.<br>Register 23 (address 17h), bits 12, 11, and 10. |

| Signal name<br>(active high) | SIGNALNAME <sup>1</sup>                             | PLLMODE           | Signal name for PLLMODE.                                                              |

| Signal name<br>(active low)  | SIGNALNAME# <sup>1</sup>                            | RST#              | Active low reset signal.                                                              |

| Signal bus<br>name           | BUSNAME[MSB:LSB] <sup>1</sup>                       | PHYADD[4:2]       | PHY Address bus, bits 4, 3, and 2.                                                    |

<sup>1</sup> All signal names are in all CAPITAL LETTERS.

## 8 Functional Overview

Cicada's single chip CIS8201 is a complete triple speed (10BASE-T, 100BASE-TX, and 1000BASE-T) low-power Ethernet physical layer transceiver. The CIS8201 transceiver is based on a highly robust DSP Data Pump architecture with a triple speed capable Analog Front End (AFE).

A number of innovative features have been engineered into the device with the primary goal of simplifying overall systems design and reducing power consumption, leading to reduced system complexity and cost.

At the systems level, the following components are required to interface to the CIS8201:

- A MAC device supporting any of the following interfaces: a GMII, MII, RGMII, TBI, or RTBI interface

- An optional Station Manager

- A single reference clock (either 25MHz or 125MHz), or an optional single 25MHz crystal

- One to three fixed power supplies, depending on the MAC I/F mode and the use of the optional on-chip regulator control circuit:

- GMII mode: 3.3V and 1.5V (or only 3.3V with use of regulator)

- RGMII<sup>1</sup> and RTBI modes: 3.3V, 2.5V, and 1.5V (or only 3.3V and 2.5V with use of regulator)

- A simple, external series pass type MOSFET transistor for supply regulation (optional)

- A 1:1 guad transformer module<sup>2</sup>

- Line termination resistors (on MAC TX and Media side only)

- Reference capacitor and resistor

- Power supply decoupling capacitors

The configurable PHY includes all the required physical layer functionality to support 1000BASE-T, 100BASE-TX, and 10BASE-T, in either half-duplex or full-duplex operation at each speed. The PHY port can be configured to connect with virtually any triple speed Ethernet MAC or Network Processor by individually selecting one of four available MAC interfaces: GMII (including MII for 10M/100Mb modes), RGMII, RTBI, or TBI.

#### 8.1 MAC Interface (GMII / RGMII / MII, or TBI / RTBI)

- Connects the CIS8201 PHY port to the appropriate layer 2 function, such as a triple speed Ethernet MAC.

- Supports both the IEEE standard Gigabit Media Independent Interface (GMII), or the more pin-efficient Reduced Gigabit Media Independent Interface (RGMII), without requiring a SERDES type interface to a MAC.

- All MAC interface output pins feature integrated, adaptively calibrated, 50 ohm series termination resistors to simplify PC board design, resulting in improved signal quality, elimination of all external series termination resistors, and lower on-chip power consumption.

- · Supports operation in 10BASE-T and 100BASE-TX modes via the IEEE standard MII.

- Supports operation in 1000BASE-T via the IEEE Standard TBI or more pin-efficient RTBI interface.

### 8.2 Twisted Pair Interface (TPI)

- Connects the CIS8201 PHY port's four dual-duplex channels to an external 1:1 magnetic module.

- Implements an internal hybrid, which minimizes the number of external passive components and easily interfaces to several, readily available, quad transformer modules to support all three operating modes.

The CIS8201 also includes four shared interfaces, used for chip and board testing, in addition to configuring the PHY port's operating modes, or monitoring the status of the port.

<sup>&</sup>lt;sup>1</sup>The RGMII interface is timing compatible with the v1.3 and v2.0 specifications. The RGMII interface is not electrically compatible with the v2.0 specifications as this requires HSTL voltage levels which the CIS8201 does not support.

<sup>&</sup>lt;sup>2</sup>For PICMG 2.16 applications, the transformer can be removed. See PICMG 2.16 Applications Note for more information.

#### 8.3 Serial Management Interface (SMI)

- Enables communication- and standards-specified configuration of the CIS8201 PHY port via a system controller, such as an external CPU or ASIC.

- Fully compliant with the IEEE 802.3 MII Management Interface specifications.

- Supports Management Data Clock (MDC) operating speeds from 0MHz to approximately 12.5MHz

- Provides a shared, open drain, interrupt pin (MDINT#) to signal the Station Manager of any change in the operating conditions of the PHY port.

- Optional configuration pins, MODE (10, 100, and 1000), FRC\_DPLX, and ANEG\_DIS, provide an alternative, direct method for presetting the operating mode (speed and duplex) of the PHY port without the need for a dedicated station manager.

### 8.4 Parallel LED Interface (PLI)

• Enables the PHY port to communicate its operating conditions (e.g., duplex, link, speed, activity, collision, and quality) by directly driven status LEDs.

### 8.5 System Clock Interface (SCI)

- Generates all internal and external clocks from the internal PLL, maintaining clock synchronization throughout the device with very low jitter.

- Allows either a single 25MHz or 125MHz reference clock (or an optional reference crystal, used with the on-chip oscillator) to be used as the reference clock for the PHY.

### 8.6 Test Mode Interface (TMI)

- Enables IC manufacturing test and standard board-level testing through an industry standard JTAG 1149.1 Boundary Scan controller

- Facilitates the operation of several innovative analog and digital Built-in-Self-Test functions, which simplify and improve manufacturing test coverage, leading to reduced component and systems costs

The three major sub-functions for the CIS8201 PHY port are described in the following sections.

## 8.7 Analog Front End (AFE)

The CIS8201 employs an advanced, low-power, hybrid "PHY" architecture, utilizing a high speed AFE and an extremely gateand power-efficient, compact DSP core.

The analog front end, or "AFE", performs the following functions in each operating mode:

- Receive and transmit signal separation (via on-chip hybrid circuitry)

- Transmit wave filtering and shaping (PMA Transmit Filter and AFE TX DAC)

- Automatic gain control (VGA)

- Receive signal quantization (ADC)

- Digital timing recovery (ADC and VGA, in concert with DSP Data Pump Core)

- Link pulse detection

In the receive data path, digital words quantized by the PHY port's four ADCs are supplied to the PMA (Physical Media Attachment) for further processing by the various DSP Data Pump elements (Adaptive equalization, Echo cancellation, NEXT and FEXT cancellation, trellis decoder, and the digital timing recovery loop).

On the transmit data path, the digital transmit filters in the PMA provide digital transmit words in 3-bit PAM5 (1000BASE-T), 2-level MLT-3 (100BASE-TX), or Manchester-encoded format to the triple speed, pulse-shaping transmit DACs.

The AFE also includes an analog PLL, which generates all internal and externally-sourced clocks from either a 25MHz or 125MHz reference clock (or a reference crystal, used with the on-chip oscillator). The PLL also provides an optional, freerunning 125MHz output clock for use as a highly accurate, low-jitter clock for use by other ICs in the system.

#### 8.8 DSP Data Pump Core

Due to its robust, low-power DSP architecture, the CIS8201 eases interoperability concerns by maintaining error-free operation in the presense of extreme noise and interference and in substandard cabling environments. It aslo supports link partner frequency offset tolerances well outside the Ethernet specifications (typically ±450ppm of local and link partner frequency offset tolerances).

The primary Receive functions performed within the DSP Data Pump include:

- · Echo cancellation

- Crosstalk cancellation (near and far end)

- · Baseline wander correction and cancellation

- Adaptive receive equalization

- Receive signal slicing

- Digital timing recovery

- · Cable pair skew compensation

- Trellis decoding (or forward error correction)

Other functions performed by the DSP core include:

- Automatic pair swap detection and correction

- Automatic cable pair polarity compensation

- Automatic MDI crossover for all three speeds

The primary transmit function implemented by the DSP core is:

Transmit pulse shaping

#### 8.9 Physical Coding Sublayer (PCS)

The PCS is responsible for controlling all transmit and receive data interchanges with external MACs. Depending on which MAC interface is enabled on the PHY port, the PCS transfers data to and from the MAC at various word widths, in conjunction with several MAC interface-specific control signals.

For example, in 1000BASE-T mode, the PCS receive path includes three primary functions:

- Trellis decoding

- Symbol descrambling

- 4D-PAM5 symbol demapping

These elements serve together to:

- Convert PAM-5 symbols from the DSP core into 8-bit receive data symbols for transmission to the MAC on the RXD[7:0] output pins (GMII mode)

- Generate the associated receive data control and status signals (RX\_DV, RX\_ER) for use by the MAC

In 1000BASE-T mode, the PCS transmit path includes the following functions:

- Trellis encoding

- Symbol scrambling

- 4D-PAM5 symbol encoding

From a functional perspective, these elements serve together to:

Convert transmit data words from the MAC on the TXD[7:0] pins (GMII mode) to PAM-5 symbols, which are sent to the transmit filters and DACs in the DSP core and AFE, respectively

#### 8.10 Synchronization FIFOs

The PCS is also ultimately responsible for managing clock domain synchronization between the various clocks within, and delivered to, the CIS8201. For this purpose, the PHY port of the 8201 contains a synchronizing transmit FIFO to absorb frequency differences between the local PHY clock and transmit clocks delivered by a MAC in TBI, GMII, and RGMII/RTBI modes. In TBI/RTBI modes, the device also includes a receive synchronization FIFO. The following table summarizes available synchronization FIFOs for the various MAC interface operating modes. See MII Register 24 (Extended PHY Control Register #2) for more information.

| MAC I/F Mode | RX FIFO | TX FIFO |

|--------------|---------|---------|

| GMII         | N/A     | Yes     |

| MII          | N/A     | N/A     |

| RGMII        | N/A     | Yes     |

| ТВІ          | Yes     | Yes     |

| RTBI         | Yes     | Yes     |

Table 8-1.

Synchronization FIFOs

#### 8.11 Optional Fixed Power Supply Regulator

The CIS8201 can optionally be powered from a single 3.3V power supply when utilizing the device's on-chip regulator control circuit to produce the 1.5V core power supply voltage. The optional on-chip regulator control circuit drives a simple, external series pass type MOSFET transistor for supply regulation, enabling a single 3.3V supply design for lowest cost. See Section 10: "System Schematics" for more information.

# 9 Package Pin Assignments & Signal Descriptions

## 9.1 128 Pin LQFP Package Pinout Diagram

For complete specifications, refer to Figure 23-1: "128 LQFP Mechanical Specification".

Figure 9-1. CIS8201 Package Pinout

# 9.2 11 x 11mm 100 Ball LBGA Package Ballout Diagram.

|   | 1       | 2                  | 3                    | 4                  | 5                    | 6                    | 7                   | 8        | 9       | 10     |   |

|---|---------|--------------------|----------------------|--------------------|----------------------|----------------------|---------------------|----------|---------|--------|---|

| A | TXIP_A  | TXVP_A             | REG_EN or<br>QUALITY | REF_FILT           | REG_OUT              | ADDR4 or<br>ACTIVITY | OSC_EN or<br>CLK125 | TX_EN    | TX_ER   | TXD0   | A |

| в | TXIN_A  | TXVN_A             | VREFP                | REF_REXT           | ADDR2 or<br>LINK1000 | ADDR3 or<br>DUPLEX   | MODE10              | MODE1000 | TXD1    | TXD2   | в |

| с | TXIP_B  | TXVP_B             | NC                   | ADDR0 or<br>LINK10 | ADDR1 or<br>LINK100  | VDDDIG               | MODE100             | ANEG_DIS | TXD3    | TXD4   | с |

| D | TXIN_B  | TXVN_B             | NC                   | VSS                | VSS                  | VSS                  | VDDDIG              | PWDN#    | TXD5    | TXD6   | D |

| Е | TXIP_C  | TXVP_C             | TXVDD                | VSS                | VSS                  | VSS                  | VSSIO               | VDDIO    | TXD7    | TX_CLK | Е |

| F | TXIN_C  | TXVN_C             | TXVDD                | VSS                | VSS                  | VSS                  | VSSIO               | VDDIO    | GTX_CLK | RX_CLK | F |

| G | TXIP_D  | TXVP_D             | VDDA33               | VSS                | VSS                  | VSS                  | VSSIO               | VDDIO    | RXD0    | RXD1   | G |

| н | TXIN_D  | TXVN_D             | VDDA33               | VDDA15             | VDDA15               | VDDDIG               | VDDDIG              | VDDIO    | RXD2    | RXD3   | н |

| J | PLLMODE | RESET#             | TDI                  | тск                | MDINT#               | MDIO                 | COL                 | RX_DV    | RXD4    | RXD5   | J |

| к | XTAL2   | XTAL1 or<br>REFCLK | TDO                  | TMS                | TRST#                | MDC                  | CRS                 | RX_ER    | RXD6    | RXD7   | к |

|   | 1       | 2                  | 3                    | 4                  | 5                    | 6                    | 7                   | 8        | 9       | 10     |   |

#### 9.3 Pin Descriptions

Where applicable, all electrical specifications will adhere to the GMII/MII, RGMII/RTBI, and TBI specifications found in their respective standards documents (IEEE 802.3-2000 and RGMII Specification version 1.2a), unless otherwise noted.

## 9.4 Signal Type Descriptions

| Symbol              | Signal Type                               | Description                                                                                                                                                                                                        |

|---------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                   | Digital Input                             | Standard digital input signal. No internal pull-up or pull-down.                                                                                                                                                   |

| I <sub>PU</sub>     | Digital Input with Pull-up                | Standard digital input. Includes on-chip 100k $\Omega$ pull-up to VDDIO.                                                                                                                                           |

| I <sub>PU(5V)</sub> | 5V-Tolerant Digital Input with<br>Pull-Up | 5V-tolerant digital input. Includes on-chip 100k $\Omega$ pull-up to VDDIO.                                                                                                                                        |

| I <sub>PD</sub>     | Digital Input with Pull-down              | Standard digital input. Includes on-chip 100k $\Omega$ pull-down to VSSIO.                                                                                                                                         |

| O <sub>ZC</sub>     | Impedance Controlled Output               | $50\Omega$ integrated (on-chip) source series terminated, digital output signal. Used primarily for timing-sensitive MAC I/F and 125MHz clock output pins, in addition to high speed manufacturing test mode pins. |

| I/O                 | Digital Bidirectional                     | Tristate-able, digital input and output signal.                                                                                                                                                                    |

| I <sub>PU</sub> /O  | Digital Bidirectional                     | Tristate-able, digital input and output signal. Includes on-chip $100k\Omega$ pull-up to VDDIO.                                                                                                                    |

| I <sub>PD</sub> /O  | Digital Bidirectional                     | Tristate-able, digital input and output signal. Includes on-chip 100k $\Omega$ pull-down to VSSIO.                                                                                                                 |

| OD                  | Digital Open Drain Output                 | Open drain digital output signal. Must be pulled to VDDIO through an external pull-up resistor.                                                                                                                    |

| A <sub>DIFF</sub>   | Analog Differential                       | Analog differential signal pair for twisted pair interface.                                                                                                                                                        |

| A <sub>BIAS</sub>   | Analog Bias                               | Analog bias or reference signal. Must be tied to external resistor and/or capacitor bias network, as shown in System Schematic.                                                                                    |

| NC                  | No Connect                                | No connect signal. Must be left floating.                                                                                                                                                                          |

#### Table 9-1. Signal Type Descriptions

# 9.5 MAC Transmit Interface Pins (MAC TX)

| LQFP                 |                        |         |                           | ignal Nam<br>Interface I |          |                           | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------------------|------------------------|---------|---------------------------|--------------------------|----------|---------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin #                | Ball #                 | TBI     | RTBI                      | GMII                     | MII      | RGMII                     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 60<br>61<br>62<br>63 | C9<br>B10<br>B9<br>A10 | TX[3:0] | TD[8:5]<br>and<br>TD[3:0] | TXD[3:0]                 | TXD[3:0] | TD[7:4]<br>and<br>TD[3:0] | I <sub>PD</sub> | <ul> <li>Transmit Data Inputs (All modes). Transmit code-<br/>group data is input on these pins synchronously to<br/>GTX_CLK in GMII mode, TXC in RTBI/RGMII<br/>modes, or PMA_TX_CLK in TBI mode.</li> <li>Multiplexed Transmit Data Nibbles (RTBI mode).<br/>Bits [3:0] are synchronously input on the rising edge<br/>of TXC, and bits [8:5] on the falling edge of TXC.</li> <li>Multiplexed Transmit Data Nibbles (RGMII mode).<br/>Bits [3:0] are synchronously input on the rising edge<br/>of TXC, and bits [7:4] on the falling edge of TXC.</li> </ul>                                                                                                                                                                                                                                                                                  |  |

| 56<br>57<br>58<br>59 | E9<br>D10<br>D9<br>C10 | TX[7:4] | Not used                  | TXD[7:4]                 | Not used | Not used                  | I <sub>PD</sub> | Transmit Data Inputs (TBI mode). Transmit data is<br>input on these pins synchronously to PMA_TX_CLK<br>in TBI mode.<br>Transmit Data Inputs (GMII mode). Transmit data<br>is input on these pins synchronously to GTX_CLK in<br>GMII mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                      |                        |         |                           |                          |          |                           |                 | Transmit Data Code Group, bit [8] (TBI mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 65                   | A8                     | TX[8]   | Not used                  | TX_EN                    | TX_EN    | Not used                  | I <sub>PD</sub> | Transmit Enable Input (GMII, MII modes).<br>Synchronized to the rising edge of GTX_CLK<br>(1000Mb mode) or TX_CLK (100Mb mode), this<br>input indicates valid data is present on the TXD bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                      |                        |         |                           |                          |          |                           |                 | Transmit Data Code Group, bit [9] (TBI mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 64                   | A9                     | TX[9]   | TD[9]<br>and<br>TD[4]     | TX_ER                    | TX_ER    | TX_CTL                    | IPD             | Multiplexed Transmit Data (RTBI mode). Bit [4] is<br>synchronously input on the rising edge of TXC, and<br>bit [9] on the falling edge of TXC.<br>Transmit Error Input (GMII, MII modes). When<br>asserted, this synchronous input causes error<br>symbols to be transmitted from the PHY when<br>operating in 1000Mb or 100Mb modes.<br>Transmit Enable, Transmit Error Multiplexed<br>Input (RGMII mode). This input is sampled by the<br>PHY on opposite edges of TXC to indicate two<br>transmit conditions of the MAC: 1) On the rising edge<br>of TXC, this input serves as TXEN, indicating valid<br>data is available on the TD input data bus. 2) On the<br>falling edge of TXC, this input signals a transmit error<br>from the MAC based on a logical derivative of TXEN<br>and TXERR, per RGMII Specification v1.2a (section<br>3.4). |  |

# Table 9-2. MAC TX Signal Descriptions (Sheet 1 of 2)

| LQFP<br>Pin # | LBGA<br>Ball # | Signal Name<br>MAC Interface Mode |      | Туре    | Description           |       |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|----------------|-----------------------------------|------|---------|-----------------------|-------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIII #        | Dall #         | TBI                               | RTBI | GMII    | MII                   | RGMII |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |