M1644

# Slot-1/Socket-370 Super Northbridge Internal 4XAGP, PCI and SDR/DDR Memory Controller **DX7 Integrated Graphics**

# **Product Brief**

# INTRODUCTION

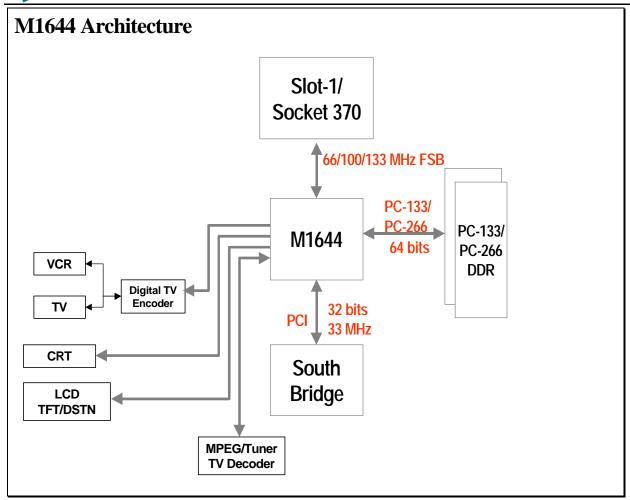

The M1644 is ALi and Trident's new generation of PCI Northbridge chip supporting all Intel Slot-1/Socket 370 Pentium  $\mathrm{II}^{\mathrm{TM}}$ , Pentium  $\mathrm{III}^{\mathrm{TM}}$ , and Celeron Processors. The M1644 is a single chip solution which interfaces with the 66/100/133 front side bus (FSB) and provides a high performance memory interface for 66/100/133 SDR and 133/200/266 DDR memory devices. The PC-266 DDR memory enables 2.1 GB/s peak bandwidth between the system memory and Northbridge to boost system performance to the next higher level.

On the graphics side, the M1644 integrates the DirectX 7 (DX7) ready graphic core (Cyberblade XP) from Trident Microsystems. The Cyberblade XP core has dual pixel pipes and a hardware transform and a lighting (T&L) unit which provide enough rendering power to satisfy high end graphics requirements. ALi also manufactures a series of feature-rich, highly integrated Southbridge devices (M1535 and M1535+) which seamlessly work with the M1644 to create a complete, flexible and cost-effective solution for notebook designers. The M1644 also incorporates ALi's proven power management support, which is crucial for mobile applications.

#### **FEATURES**

# **ALi PCI Northbridge Core Logic Processor Support**

- Supports all Intel Slot-1/Socket 370 Pentium IITM, Pentium III<sup>TM</sup>, and Celeron<sup>TM</sup> processors.

- Host bus frequency can be either 66, 100MHz, or 133 MHz double data rate

- 64-bit data bus and 32-bit addressing

- Optimum buffering architecture design for CPU to memory, internal AGP and PCI read/write

- Supports 8 outstanding processor commands

- Supports 8 outstanding system probe commands

- Flexible configured to support back to back read transfer in 1QW or 2QW

- Support back to back write transfers

- Optimized processor command scheduling and reordering

- Supports synchronous / asynchronous clock mode between processor and memory interface with optimized latency

# **Memory Support**

- Supports SDRAM/DDR w/ 66, 100, 133MHz

- Supports symmetrical and asymmetrical SDRAM/ DDR addressing

- Supports 4, 16, 64, 128, 256, 512Mbit SDRAM / DDR

- Maximum memory size: 3 GB

- Supports 6 memory rows with per byte access on each row

- Supports memory shadowing

- x-1-1-1-1-1 back-to-back page hit

- CAS before RAS and self refresh for SDRAM

- Pipelined SDRAM / DDR cycle control with hidden pre-charge

- Dynamic switching CKE algorithm

- Supports LVTTL / SSTL2 signal level

# **PCI Bus Support**

- Supports synchronous / asynchronous clock mode between the processor bus and the PCI bus

- 32-bit Address / Data PCI bus using PCI bus driver technology

- Supports up to 6 PCI masters excluding the M1644 and PCI-to-ISA bridge

- Parity protection on all PCI bus signals

- Fully supports PCI Configuration Space Enable (CSE) protocol

- Fully compliant with PCI Rev. 2.2

- Supports delayed transaction

- Dynamic memory prefetch algorithm and programmable post write flush algorithm

- Data Collection/Write assembly of line bursts

- Supports concurrent PCI bus burst transfer at zero wait-states

- 133 MB/sec data streaming for PCI bus to SDRAM / DDR access with minimum latency

# **Trident Cyberblade XP Graphic Core Highly Integrated Graphics Engine**

- Advanced Blade™ Dual-Pixel, Single-pass 3D and 2D rendering engine

- 128-bit bus interface to external SGRAM/SDRAM

- Support of Microsoft DirectX 7.0 with cubic mapping

- Dual Panel interface to both external LVDS & TMDS

- Digital interface to external TV encoder

- DVD hardware assist with Motion Compensation (MC) and Inverse Discrete Cosine Transform (IDCT)

- TrueVideo® with Advanced Video De-interlacing

- Linear display memory addressing up to 4GB memory

- 256 Raster Operations (ROPs) up to 32-bit True Color

- 270 MHz built-in RAMDAC™ and frequency synthesizer

- Two four-color hardware cursor and pop-up icons

- PC2001 Compliant

Acer Laboratories Inc., USA Ver 0.61

# M1644: Slot-1/Socket-370 Super Northbridge

# **High Performance DirectX 7.0 3D Engine**

- Dual-Pixel, Single-Pass 3D rendering engine

- Supports all DirectX 7.0 feature set and vertex format

- Special hardware support for DirectX 7.0 cubic mapping and bump mapping

- Optimized 32-bit IEEE floating point setup engine

- 128-bit texture engine with 4KB texture cache

- Simultaneous diffuse, Specular lighting, Gouraud Shading, Z-buffering and fog with no performance

- Perspective correct mip-mapped texturing

- Bilinear, trilinear and Anisotropic filtering

- Texture compression and tiling

- Point sampled or bi-linear filtered texture maps are palletized and/or perspective corrected

- Chroma key, Alpha blending and color key operations

- OpenGL compliant

#### **Enhanced Bus Interface**

- 66/133/266 MHz internal 4X AGP

- DMA mastering with Scatter Gather

- Execute mode for Direct Textures, Video and DVD

# MPEG2/DVD Hardware Assist Playback

- THAMA™(Trident Hardware-Assisted MPEG-2 Acceleration) architecture enables full DVD player support with AC3 and subpicture support 30 fps playback of 9.8 Mbps VBR MPEG-2 video with 40-60% CPU headroom for other applications

- Hardware Alpha blending for subpicture

- Advanced error recovery and concealment for handling poor quality video clips

- Programmable multi-tap filtering

- Supports DVD v.1.0 and VCD v.2.0

- Pan and Scan Support

# **True Video Accelerator**

- TrueVideo® provides horizontal vertical interpolation with proprietary edge recovery scaling

- Dual apertures for simultaneous access to graphics and video display memory areas

- Dual color space converters (CSC)

- Field rendering for interlace support on NI display

- Accelerates YUV planar format

#### **Motion Video Capture Port**

- ZV port accepting RGB, YUV 4:2:2, and YUV planar 4:2:0 formats

- VIP bus 2.0 support

- **CCIR 656/CCIR 601**

VBI (Intercast) interface can separate vertical blank interval data for transmission to CPU using PCI Bus Masterina

#### **Advanced Mobile Power Management**

- Low power cell design

- 8 GPIOs, suspend and standby modes

- Internal clock gating on each functional block

- PCIPM (H/W PCI initiated)

- AGP Busy#/Stop# and PCI Clock Run#

- ACPI and DPMS support

### Multiple/Simultaneous Display

- Different/same images with independent refresh rates on separate displays (panels, CRT or TV)

- Vertical/horizontal virtual desktop

- Microsoft® Windows 98 Multi-Head and Multi-Monitor support

- Supports up to 3 displays

# **Advanced Flat Panel Support**

- Frame rate modulation and spatial dithering for increased color depth

- Gamma correction for color enhancement

- Auto expansion and centering

- 16/24-bit interface to TFT panel

- Straight or double pixel/clock interface for up to 1280x1024 SXGA TFT panels

- External Spread Spectrum support for significantly reduced EMI at high frequency clock rates

#### Integrated LVDS support

- Integrated high-speed single channel LVDS for substantial power, space and EMI reduction

- Wide Frequency range of 32-112MHz MHz suited for SVGA, XGA and SXGA panels

- 392Mbps/channel throughput with 28:4 bits Data Channel Compression

- Compatible with receivers from Thine, National Semiconductor and Texas Instrument

#### **CRT**

- Supports high quality CRT display up to 1600x1200

- VESA™ DDC2B compliance

# TV Presentation/Game Ready

- Direct interface to Trident's TVXpress digital TV encoder offering

- Better text quality

- Macrovision 7.0x compliant

- Low cost, high quality PC to TV output

- NTSC and PAL outputs

- Composite, S-Video and SCART interface Support

555 balls 35x35mm BGA package

Acer Laboratories Inc., USA Ver 0.61 Page 2

# For more information contact:

# Acer Laboratories Inc., USA

525 E. Brokaw Road, San Jose, CA 95112 Tel: 408-544-3100, Fax: 408-544-3135 www.acerlabs.com

# Trident Technologies Inc.

18F, no.202 Sec.2, Yen Ping N. Rd., Taipei, Taiwan Tel: 886-2-2550-6616, Fax: 886-2-2550-3901 www.trident.com.tw

ALi is a registered trademark of Acer Laboratories Inc. Other trademarks are property of their respective companies.