93C488 5x86/486 Single Chip

Revision changes:

Rev. 08/02/96-6:57 PM Correct the meanings of configuration register 23H Bit 7 and Bit 6.

Rev. 08/05/96-11:12 AM Index C6H bit 4 definition change from I/O address decode to ROMCS decode in memory write cycle.

Rev. 08/28/09-4:21 PM Add DC characteristics table.

Rev. 09/04/96-10:42 AM Add introduction page.

Rev. 09/21/96-12:00 PM Add control bit to support Cyrix burst write back cycle. (Index 12H bit 0) Correct the default setting of 80H bit 2.

# Notice

This data sheet is provided for the general information of the customer. ALD Technology Ltd.(ALD) makes no warranty for the use of its products and bears no responsibility for any errors which may appear in this document. ALD retains the right to make changes to those specifications at any time without notice. ALD makes no commitment to update or keep the current information contained in this document.

ALD subjects its products to normal quality control sampling techniques which are intended to provide and assurance of high quality products suitable for the usual commercial applications. ALD does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental damages arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.

## 1. Introduction

ALD93C488 is the world first single chip 486/5x86 core logic that supports Pipeline Burst/Burst (PB) Synchronous SRAM for L2 cache implementation. This innovative feature results in much superior performance than the previous generation core logic design that uses Asynchronous SRAM for L2 cache. ALD93C488 also features one of the highest integration in the market and requires only DRAM, BIOS and 9 pieces TTL to complete a cost-effective PCI/ISA system that supports all available 486 pinout CPUs up to bus speed of 50 MHz.

Employing state-of-the-art 0.6 Micron CMOS technology, ALD93C488 integrates the PB Cache Controller, DRAM Controller, ISA Peripheral Controllers (Interrupt Controller, DMA Controller, Timer/Counter, Real-time Clock and Keyboard Controller), PCI and ISA Interface and an Enhanced Local Bus IDE Interface into a single 208 QFP (Quad Flat Pack) IC.

Applying the same technique as the latest Pentium systems, the PB Cache Controller achieves 3,1,1,1 burst cycle with Pipeline Burst Synchronous SRAM. Write Back Cache Policy is employed for better CPU bandwidth utilization. Cache size can range from 128 KB to 1 MB. The DRAM Controller supports Page, Fast Page and EDO DRAM for maximum compatibility and ultimate performance. Four banks of DRAM, from 1 MB to 256 MB, can be accessed, with Auto-detection of memory type and size.

The PCI Interface meets the requirements of PCI Specifications 2.1 (5 V). To support PCI cards that have on-board intelligence, two PCI Bus Masters can be used. In addition to Host- to- PCI Byte Merging, a 4-level Host- to- PCI Write Buffer is designed to ensure maximum system throughput.

The built-in Enhanced Local Bus IDE Interface supports up to 4 IDE devices (PIO Mode 4 timing). Advanced features like Address Swapping between Primary and Secondary IDE Ports and separate Master/Slave modes are implemented. To make computers environmentally friendly, ALD93C488 is equipped with integrated power management technique to stop or slow down the CPU.

- 2. Features

- ÿ Support processor bus up to 50MHz.

- AMD 5x86-133, 486DX4-120/100, 486DX2-80/66, 486DX-50/40/33/25

- Cyrix/IBM/ST 5x86-120/100, 486DX4-120/100, 486DX2-80/66/50, 486DX-40/33/25

- TI 486DX4-100, 486DX2-80/66

- Intel 486DX4-100/75, 486DX2-66, 486DX-40/33/25, 486SX

- ÿ Integrated DRAM controller

- 1Mbyte to 256Mbyte main memory

- Non-page mode, Fast page mode, Nibble mode, Write per bit mode, EDO mode DRAM providing flexible timing control

- Supports for auto detection of memory type including size, refresh cycle.

- 4 RAS lines for 4 DRAM banks

- Supports for symmetrical and asymmetrical DRAM addressing

- Supports RAS only, CBR hidden refresh

- Supports shadow memory and 384K relocated memory

- ÿ Integrated synchronous cache controller

- 128Kbyte to 1Mbyte cache

- Support pipeline/non-pipeline burst SSRAM

- Support X,1,1,1/X,2,2,2 burst cycle

- ÿ Fast IDE interface

- Supports up to PIO mode 4 Timings

- Separate master/slave IDE mode support

- Supports primary/secondary port address swapping

- ÿ PCI bus controller

- 4 level host to PCI write buffer

- Supports host to PCI byte merging

- Supports two PCI bus master

- ÿ Integrated IPC includes

- Two 8259 interrupt controllers

- Two 8237 DMA controllers

- One 8254 timer/counter

- RTC

- Keyboard controller

- ÿ Power management

- Programmable hardware events

- Programmable CPU clock control (STPCLK#)

- Slow down system clock speed (SLOWDWN#)

- ÿ Single chip 208 pin QFP

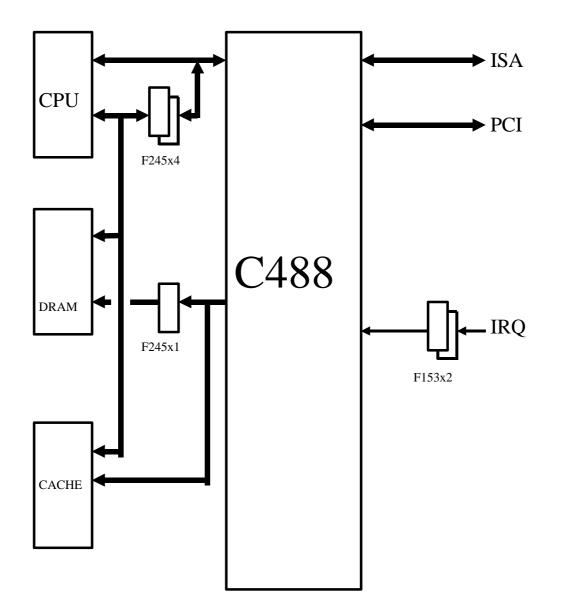

3. System block diagram

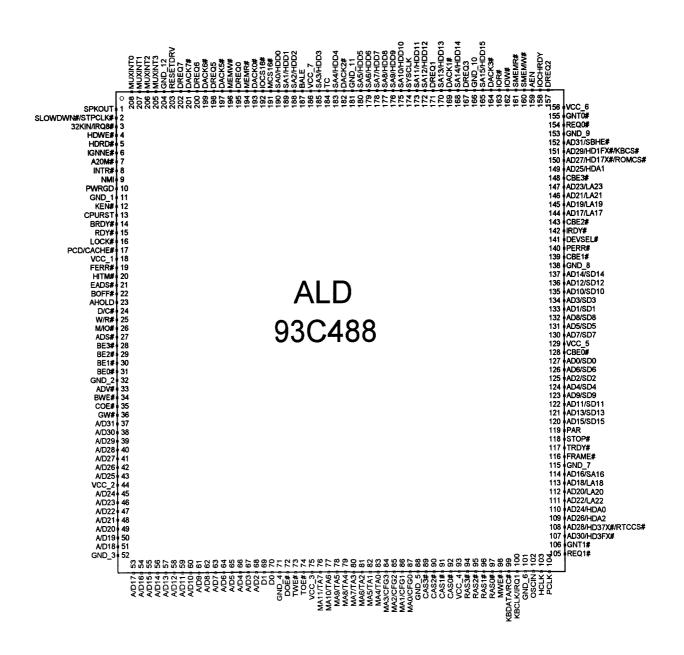

4. Pin diagram

## 5. Pin description

| Signal Name              | Pin<br>Number        | I/O        | Description                                           | Driving<br>Capability |

|--------------------------|----------------------|------------|-------------------------------------------------------|-----------------------|

| Host interface signals:- | Ivalloci             |            |                                                       | Cupuolinty            |

| D[1:0]                   | 69,70                | I/O        | Host data lines D0 and D1.                            | 8mA                   |

| A/D[31:2]                | 37 - 43,             | I/O<br>I/O | Multiplexed Host address and data bus.                |                       |

| A/D[31:2]                | 37 - 43,<br>45 - 51, | 1/0        | Multiplexed Host address and data bus.                | 8mA                   |

|                          |                      |            |                                                       |                       |

|                          | 53 - 68              | L/O        | Hard a ddurae aturk a                                 | Q A                   |

| ADS#                     | 27                   | I/O        | Host address strobe.                                  | 8mA                   |

|                          | 2.                   | T/O        | External 10Kohm pull-up is required.                  | 0.1                   |

| M/IO#                    | 26                   | I/O        | The memory/input-output, data/control and             | 8mA                   |

| D/C#                     | 24                   |            | write/read lines are the primary bus definition       |                       |

| W/R#                     | 25                   |            | signals. These signal is sampled when ADS# is         |                       |

|                          |                      |            | asserted.                                             |                       |

|                          |                      |            | M/IO# D/C# W/R# Bus Cycle type                        |                       |

|                          |                      |            | 0 0 0 Interrupt acknowledge                           |                       |

|                          |                      |            | 0 0 1 Halt/Special cycle                              |                       |

|                          |                      |            | 0 1 0 I/O Read                                        |                       |

|                          |                      |            | 0 1 1 I/O Write                                       |                       |

|                          |                      |            | 1 0 0 Code Read                                       |                       |

|                          |                      |            | 1 0 1 Reserved                                        |                       |

|                          |                      |            | 1 1 0 Memory Read                                     |                       |

|                          |                      | 0          | 1 1 1 Memory Write                                    | 0.1                   |

| AHOLD                    | 23                   | 0          | Address hold request. Host should float its address   | 8mA                   |

|                          |                      | _          | bus in the clock following this signal going active.  |                       |

| BOFF#                    | 22                   | 0          | Bus off request. Host should float the                | 8mA                   |

|                          |                      |            | control/address/data bus in the clock following this  |                       |

|                          |                      |            | signal going active.                                  |                       |

| EADS#                    | 21                   | 0          | This signal indicates that a valid external address   | 8mA                   |

|                          |                      |            | has been driven onto the host address pins to         |                       |

|                          |                      |            | perform a cache invalidation cycle.                   |                       |

| HITM#                    | 20                   | Ι          | In write-back mode, HITM# indicate that an            |                       |

|                          |                      |            | external snoop cache tag comparison hit a modified    |                       |

|                          |                      |            | line. CPU will then drive this pin to low two clock   |                       |

|                          |                      |            | after EADS# is asserted to initiate a write-back      |                       |

|                          |                      |            | cycle.                                                |                       |

|                          |                      |            | External 10Kohm pull-up is required.                  |                       |

| PCD/CACHE#               | 17                   | Ι          | PCD of write-through CPU or CACHE# of a write-        |                       |

|                          |                      |            | back CPU. When this pin acts as PCD pin, it is        |                       |

|                          |                      |            | used with LOCK#, M/IO#, and W/R# pins to              |                       |

|                          |                      |            | determine whether the bus cycle is cacheable or       |                       |

|                          |                      |            | not. When this pin acts as CACHE# pin, a low on       |                       |

|                          |                      |            | this pin indicates that the current read cycle is     |                       |

|                          |                      |            | cacheable, or that the current cycle is a burst write |                       |

|                          |                      |            | or copy-back cycle.                                   |                       |

| LOCK#                    | 16                   | Ι          | Bus lock. This signal is used with PCD, M/IO#         |                       |

|                          |                      |            | and W/R# to determine whether the current cycle is    |                       |

|                          |                      |            | cacheable or not. For write-through CPU, a            |                       |

|                          |                      |            | cacheable cycle is defined as a Unlocked memory       |                       |

|                          |                      |            | read cycle with PCD de-asserted. For write-back       |                       |

|                          |                      |            | CPU and PCD/CACHE# pin is selected as                 |                       |

|               |         |     | CACHE# signal, this pin is not used.                                                                  |       |

|---------------|---------|-----|-------------------------------------------------------------------------------------------------------|-------|

| RDY#          | 15      | 0   | Non-burst Ready. A low on this pin indicates that                                                     | 12mA  |

|               |         |     | the current bus cycle is completed, and valid data                                                    |       |

|               |         |     | has been presented in response to a read, or data                                                     |       |

|               |         |     | has been accepted in response to a write in a non-                                                    |       |

|               |         |     | burst cycle.                                                                                          |       |

| BRDY#         | 14      | 0   | Burst Ready. A Low on this pin indicates that valid                                                   | 12mA  |

|               |         |     | data has been presented in response to a read, or                                                     |       |

|               |         |     | data has been accepted in response to a write in a                                                    |       |

|               |         |     | burst cycle.                                                                                          |       |

| CPURST/SRESET | 13      | 0   | CPU Reset for a write-through CPU or Soft Reset                                                       | 4mA   |

|               | -       |     | for a write-back CPU. It will assert when PWRGD                                                       |       |

|               |         |     | is low, or a shutdown cycle is detected, or a reset                                                   |       |

|               |         |     | processor signal(RC#) is activated. This signal will                                                  |       |

|               |         |     | assert at least 16 HCLK after both PWRGD and                                                          |       |

|               |         |     | RC# return to logic ONE. For proper operation, an                                                     |       |

|               |         |     | external 10K pull-up resister is required.                                                            |       |

| KEN#          | 12      | 0   | Cache Enable. It is asserted when the current bus                                                     | 8mA   |

|               | 12      | Ŭ   | cycle is determined as a cacheable DRAM cycle. It                                                     | onn r |

|               |         |     | is always asserted when the bus is idle or at the                                                     |       |

|               |         |     | first clock of a bus cycle.                                                                           |       |

| BE[3:0]#      | 28 - 31 | I/O | Byte Enable. They indicate which bytes are enabled                                                    | 8mA   |

| DL[3.0]#      | 20-51   | 1/0 | and active during read or write cycles. They are                                                      | onia  |

|               |         |     | ignored and assume all byte are active during the                                                     |       |

|               |         |     | cache fill cycle.                                                                                     |       |

| FERR#         | 19      | I   | Floating-Point Error. A low on this pin indicates an                                                  |       |

| FERR#         | 19      | 1   | error occurs in the floating-point unit. Upon the                                                     |       |

|               |         |     | reception of this signal, hardware interrupt IRQ13                                                    |       |

|               |         |     | is generated internally and, if not masked, will                                                      |       |

|               |         |     | cause processor to enter the error-handling routine.                                                  |       |

| IGNNE#        | -       | 0   | ^*                                                                                                    | 4 4   |

| IGNNE#        | 6       | 0   | Ignore Numeric Error. This pin is normally high,<br>after a write to I/O location 03F0H or 03F1H when | 4mA   |

|               |         |     |                                                                                                       |       |

|               |         |     | FERR# is asserted, it will set to low. It will go high                                                |       |

| ND G          |         | -   | after FERR# returns to a high state.                                                                  |       |

| NMI           | 9       | 0   | Non-maskable Interrupt. It is asserted when a                                                         | 4mA   |

|               |         |     | parity error occurs during PCI transfer cycle, or a                                                   |       |

|               |         |     | power management interrupt occur when the power                                                       |       |

|               |         | -   | management interrupt is routed to this output.                                                        |       |

| INTR          | 8       | 0   | Interrupt Request. It is asserted by the internal                                                     | 4mA   |

|               |         |     | interrupt controller when it receives a interrupt                                                     |       |

|               |         |     | request from the peripherals.                                                                         |       |

| Signal Name              | Pin<br>Number                                                                                       | I/O | Description                                                                                                                                                                                                                                                                                                                                     | Driving<br>Capability |

|--------------------------|-----------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| PCI Interface signals:-  |                                                                                                     |     |                                                                                                                                                                                                                                                                                                                                                 |                       |

| AD[31]/SBHE#             | 152                                                                                                 | I/O | During PCI cycle, it is the address/data line 31.<br>During ISA cycle, it is the byte high enable signal.                                                                                                                                                                                                                                       | 12mA                  |

| AD[30]/HD3FX#/<br>P70CS# | 107                                                                                                 | I/O | During PCI cycle, it is the offer high endore signal.<br>During on-chip IDE access, it is the primary IDE<br>chip select signal.<br>During ISA cycle, it is the I/O port 70 chip select<br>signal.                                                                                                                                              | 12mA                  |

| AD[29]/HD1FX#/<br>KBCS#  | 151                                                                                                 | I/O | During PCI cycle, it is the address/data line 29.<br>During on-chip IDE access, it is the primary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>external keyboard controller.                                                                                                                         | 12mA                  |

| AD[28]/HD37X#/<br>RTCCS# | 108                                                                                                 | I/O | During PCI cycle, it is the address/data line 28.<br>During on-chip IDE access, it is the secondary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>external real time clock.                                                                                                                           | 12mA                  |

| AD[27]/HD17X#/<br>ROMCS# | 150                                                                                                 | I/O | During PCI cycle, it is the address/data line 27.<br>During on-chip IDE access, it is the secondary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>BIOS ROM.                                                                                                                                           | 12mA                  |

| AD[26:24]/HDA[2:0]       | 109, 149,<br>110                                                                                    | I/O | During PCI cycle, it is the address/data line 26:24.<br>During on-chip IDE access, it is the IDE address<br>line 2:0.                                                                                                                                                                                                                           | 12mA                  |

| AD[23:17]/LA[23:17]      | 147, 111,<br>146, 112,<br>145, 113,<br>144                                                          | I/O | During PCI cycle, it is the address/data line 23:17.<br>During ISA cycle, it is the address line LA[23:17].                                                                                                                                                                                                                                     | 12mA                  |

| AD[16]/SA[16]            | 114                                                                                                 | I/O | During PCI cycle, it is the address/data line 16.<br>During ISA cycle, it is the address line SA[16].                                                                                                                                                                                                                                           | 12mA                  |

| AD[15:0]/SD[15:0]        | 120, 137,<br>121, 136,<br>122, 135,<br>123, 132,<br>130, 126,<br>131, 124,<br>134, 125,<br>133, 127 | I/O | During PCI cycle, it is the address/data line 15:0.<br>During ISA cycle, it is the data line SD[15:0].                                                                                                                                                                                                                                          | 12mA                  |

| CBE[3:0]#                | 148, 143,<br>139, 128                                                                               | I/O | PCI Command/Byte Enable signals. During addressphase of a transaction, they define the bus command(Refer to following table for bus commanddefinitions.) During data phase they are used asByte Enables. The Byte Enables determine whichbyte lanes carry meaningful data.CBE#Description0000Interrupt Acknowledge0001Special Cycle0010I/O Read | PCI spec.             |

| 1            |           | 1   | 0011 I/O Write                                        |            |

|--------------|-----------|-----|-------------------------------------------------------|------------|

|              |           |     | 0100 Reserved                                         |            |

|              |           |     | 0101 Reserved                                         |            |

|              |           |     | 0110 Memory Read                                      |            |

|              |           |     | 0111 Memory Write                                     |            |

|              |           |     | 1000 Reserved                                         |            |

|              |           |     |                                                       |            |

|              |           |     | 1001 Reserved                                         |            |

|              |           |     | 1010 Configuration Read                               |            |

|              |           |     | 1011 Configuration Write                              |            |

|              |           |     | 1100 Memory Read Multiple                             |            |

|              |           |     | 1101   Dual Address Cycle                             |            |

|              |           |     | 1110 Memory Read line                                 |            |

|              |           |     | 1111 Memory Write and Invalidate                      |            |

| FRAME#       | 116       | I/O | Frame is driven by the current master to indicate the | PCI spec.  |

|              |           |     | beginning and duration of an access.                  |            |

|              |           |     | External 10Kohm pull-up is required.                  |            |

| IRDY#        | 142       | I/O | Initiator Ready. This signal indicates the PCI bus    | PCI spec.  |

|              |           |     | master ability to complete the current data phase     | _          |

|              |           |     | of the transaction. This pin is output when C488      |            |

|              |           |     | acts as a PCI master.                                 |            |

|              |           |     | External 10Kohm pull-up is required.                  |            |

| TRDY#        | 117       | I/O | Target Ready. This indicates the target ability to    | PCI spec.  |

| IND I #      | 117       | 1/0 | complete the current data phase of transaction. This  | i ei spee. |

|              |           |     | pin is output when C488 acts as a slave.              |            |

|              |           |     |                                                       |            |

| (TOD)        | 110       | T/O | External 10Kohm pull-up is required.                  | DCI        |

| STOP#        | 118       | I/O | This indicates the current target is requesting the   | PCI spec.  |

|              |           |     | master to stop the current transaction. This pin is   |            |

|              |           |     | output in PCI master cycle when multiple data         |            |

|              |           |     | transfer is disable.                                  |            |

|              |           |     | External 10Kohm pull-up is required.                  |            |

| DEVSEL#      | 141       | I/O | Device Select. This indicates the target device has   | PCI spec.  |

|              |           |     | decoded the address as its own cycle. This is output  |            |

|              |           |     | when C488 acts as a PCI slave.                        |            |

|              |           |     | External 10Kohm pull-up is required.                  |            |

| GNT[1:0]#    | 106, 155  | 0   | PCI Grant. These indicate to the requesting device    | 12mA       |

|              |           |     | that access to the bus has been granted.              |            |

| REQ[1:0]#    | 105, 154  | Ι   | PCI Master Request. These indicate that the           |            |

|              | , -       |     | corresponding PCI device desires to use the bus.      |            |

|              |           |     | External 10Kohm pull-up is required.                  |            |

| PAR          | 119       | I/O | PCI Parity. It is even parity across AD[31:0] and     | PCI spec.  |

|              |           | 10  | CB[3:0]#. C488 generates parity bit when :-           | i ei spee. |

|              |           |     | 1. It acts as a PCI slave in read cycle data phase.   |            |

|              |           |     | • •                                                   |            |

|              |           |     | 5                                                     |            |

|              |           |     | 3. It acts as a PCI master in read cycle address      |            |

|              |           |     | phase.                                                |            |

| PERR#        | 140       | I/O | Parity Error. This pin may be pulsed by target        | PCI spec.  |

|              |           |     | device which detects a data parity error. C488 will   |            |

|              |           |     | generate NMI when PERR# is sampled low.               |            |

|              |           |     | External 10Kohm pull-up is required.                  |            |

| MUXINT[3:0]# | 205 - 208 | Ι   | Multiplexed Interrupt input. C488 will use OSC and    |            |

|              |           |     | SYSCLK to de-multiplex these signals and forms        |            |

|              |           |     | the IRQ and INT# signals as:-                         |            |

|              |           |     | SYS- OSC MUX- MUX- MUX- MUX-                          |            |

|              |           |     | CLK INT[3] INT[2] INT[1] INT[0]                       |            |

|              |           |     | 0 0 IRQ12 IRQ7 IRQ3 INTA#                             |            |

|  | 0<br>1 | 1<br>0 | IRQ14<br>IRQ15 | IRQ9<br>IRQ10 | IRQ4<br>IRQ5 | INTB#<br>INTC# |  |

|--|--------|--------|----------------|---------------|--------------|----------------|--|

|  | 1      | 1      | KBINH#         | IRQ11         | IRQ6         | INTD#          |  |

| Signal Name             | Pin                    | I/O | Description                                                                         | Driving    |

|-------------------------|------------------------|-----|-------------------------------------------------------------------------------------|------------|

|                         | Number                 |     |                                                                                     | Capability |

| ISA Interface signals:- |                        | 1   |                                                                                     |            |

| AD[23:17]/LA[23:17]     | 147, 111,              | I/O | During PCI cycle, it is the address/data line 23:17.                                | 12mA       |

|                         | 146, 112,              |     | During ISA cycle, it is the address line LA[23:17].                                 |            |

|                         | 145, 113,              |     |                                                                                     |            |

|                         | 144                    |     |                                                                                     |            |

| AD[16]/SA[16]           | 114                    | I/O | During PCI cycle, it is the address/data line 16.                                   | 12mA       |

|                         |                        |     | During ISA cycle, it is the address line SA[16].                                    |            |

| AD[15:0]/SD[15:0]       | 120, 137,              | I/O | During PCI cycle, it is the address/data line 15:0.                                 | 12mA       |

|                         | 121, 136,              |     | During ISA cycle, it is the data line SD[15:0].                                     |            |

|                         | 122, 135,              |     |                                                                                     |            |

|                         | 123, 132,              |     |                                                                                     |            |

|                         | 130, 126,              |     |                                                                                     |            |

|                         | 131, 124,              |     |                                                                                     |            |

|                         | 134, 125,              |     |                                                                                     |            |

| DDE0[7:5 2:0]           | 133, 127               | Ι   | DMA Domost DDEO[2:01 is 9 kit DMA shares                                            |            |

| DREQ[7:5,3:0]           | 202, 200,              | 1   | DMA Request. DREQ[3:0] is 8-bit DMA channel<br>and DREQ[7:5] is 16-bit DMA channel. |            |

|                         | 198, 167,<br>157, 171, |     | External 10Kohm pull-down is required.                                              |            |

|                         | 195                    |     | External Tokonin pun-down is required.                                              |            |

| DACK[7:5, 3:0]#         | 201, 199,              | 0   | DMA Acknowledge.                                                                    | 8mA        |

| $DACK[7.5, 5.0]^{\pi}$  | 197, 164,              | 0   | DWA Acklowiczge.                                                                    | onia       |

|                         | 182, 169,              |     |                                                                                     |            |

|                         | 193                    |     |                                                                                     |            |

| SMEMR#                  | 161                    | 0   | System Memory Read. This is a output signal which                                   | 12mA       |

|                         |                        | -   | is driven low only when the system read ISA                                         |            |

|                         |                        |     | memory resided below 1Mbyte address range.                                          |            |

| SMEMW#                  | 160                    | 0   | System Memory Write. This is a output signal                                        | 12mA       |

|                         |                        |     | which is driven low only when the system write ISA                                  |            |

|                         |                        |     | memory resided below 1Mbyte address range.                                          |            |

| IOR#                    | 163                    | I/O | I/O read. This is driven by C488 in Processor or                                    | 12mA       |

|                         |                        |     | DMA cycle. During ISA bus master cycle, it                                          |            |

|                         |                        |     | becomes a input.                                                                    |            |

|                         | 1                      |     | External 10Kohm pull-up is required.                                                |            |

| IOW#                    | 162                    | I/O | I/O write. This is driven by C488 in Processor or                                   | 12mA       |

|                         |                        |     | DMA cycle. During ISA bus master cycle, it                                          |            |

|                         |                        |     | becomes a input.                                                                    |            |

|                         |                        |     | External 10Kohm pull-up is required.                                                |            |

| MEMR#                   | 194                    | I/O | Memory Read. This is driven by C488 in Processor                                    | 12mA       |

|                         |                        |     | or DMA cycle. During ISA bus master cycle, it                                       |            |

|                         |                        |     | becomes a input.                                                                    |            |

|                         | 100                    | T/O | External 10Kohm pull-up is required.                                                | 10 4       |

| MEMW#                   | 196                    | I/O | Memory Write. This is driven by C488 in Processor                                   | 12mA       |

|                         |                        |     | or DMA cycle. During ISA bus master cycle, it                                       |            |

|                         |                        |     | becomes a input.                                                                    |            |

| SYSCLK                  | 174                    | 0   | External 10Kohm pull-up is required.                                                | 12m A      |

| SISULK                  | 174                    | 0   | System Clock. This is a 7.159MHz clock signal.                                      | 12mA       |

| BALE                    | 187                    | 0   | Bus Address Latch enable. A high pulse with halt                                    | 8mA        |

|                         |                        |     | SYSCLK is generated at the beginning of Processor                                   |            |

|                         |                        |     | ISA cycle. During ISA DMA or bus master cycle. It                                   |            |

|                         |                        |     | is kept at high level.                                                              |            |

| AEN                | 159                                                                    | 0   | DMA address enable. During DMA cycle, it is driven high to inhibit I/O device to decode the                                                                                                                                                                                                | 8mA  |

|--------------------|------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                    |                                                                        |     | address.                                                                                                                                                                                                                                                                                   |      |

| TC                 | 184                                                                    | 0   | DMA Terminal Count. It is driven high to indicate the last transfer in multiple DMA transfer cycle.                                                                                                                                                                                        | 8mA  |

| IOCS16#            | 192                                                                    | Ι   | I/O chip select 16. It is driven low by a 16 bit I/O device.<br>External 3300hm pull-up is required.                                                                                                                                                                                       |      |

| RESETDRV           | 203                                                                    | 0   | System Reset output. It is driven high only when<br>PWRGD input is low. This is used to initialize the<br>Peripheral to a known state. It will go to CPU reset<br>pin for Supporting CPU L1 write-back function. For<br>proper operation, an external 10K pull-up resister is<br>required. | 16mA |

| SA[15:0]/HDD[15:0] | 165, 168,<br>170, 172,<br>173,<br>175 - 180,<br>183, 185,<br>188 - 190 | I/O | For ISA cycle, these are the address line 15 to 0.<br>For On-chip IDE cycle, these are data line 15 to 0 for<br>the IDE port.<br>External 10Kohm pull-up is required.                                                                                                                      | 12mA |

| IOCHRDY            | 158                                                                    | I/O | This pin is driven low by ISA device to extend the<br>ISA command cycle.<br>External 4.7Kohm pull-up is required.                                                                                                                                                                          | 16mA |

| Signal Name            | Pin<br>Number | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Driving<br>Capability |

|------------------------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Memory Interface signa | als:-         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| MA[11:4]/TA[7:0]       | 76 - 83       | I/O | Memory Address line 11:4 or L2 cache Tag 7:0.<br>When L2 cache is not enable, they are the memory<br>address lines for DRAM interface. When L2 cache is<br>enable, they are the multiplex bus for both cache tag<br>data and DRAM address. Signal pin TOE# high<br>represents they are carrying memory address<br>information; TOE# low represents they are carrying<br>tag data information.                                                                                                                                                 | 24mA                  |

| MA[3:0]/CFG[3:0]       | 84 - 87       | ľO  | <ul> <li>Memory Address line 3:0 and Configuration line</li> <li>3:0. During PWRGD is low, they are the hardware configuration input, it is recommend to connect to the hardwire jumper through 10Kohm resisters.</li> <li>After RESETDRV returns to low, They become memory address line 3:0.</li> <li>CFG[0] Set high to enable internal keyboard controller.</li> <li>CFG[1] Set high to enable internal real time clock.</li> <li>CFG[2] Reserved, must be high.</li> <li>CFG[3] Test mode, must be high for normal operation.</li> </ul> | 24mA<br>Note *        |

| MWE#                   | 73            | 0   | DRAM Write. It is driven low to enable write data<br>to memory, for EDO memory, it is pulse low to<br>terminate the read cycle. During memory refresh, it<br>will be driven high.                                                                                                                                                                                                                                                                                                                                                             | 24mA                  |

| RAS[3:0]#              | 94 - 97       | 0   | DRAM Row Address Strobe. The negate going edge<br>of these signals are used to latch the row address on<br>the MA lines to the DRAM banks. RAS[3] applies<br>to bank 3, RAS[2] applies to bank2 and so on.                                                                                                                                                                                                                                                                                                                                    | 16mA                  |

| CAS[3:0]#              | 89 - 92       | 0   | DRAM Column Address Strobe. The negate going<br>edge of these signals are used to latch the column<br>address on the MA lines to the DRAM banks and<br>enable the DRAM banks' output buffer if it is a read<br>cycle or store the data into DRAM banks if is a write<br>cycle. CAS[3] applies to byte 3, CAS[2] applies to<br>byte 2 and so on.                                                                                                                                                                                               | 16mA                  |

Note \* Correction made after Rev. 07/05/96-2:01 PM

| Signal Name              | Pin<br>Number                                                          | I/O | Description                                                                                                                                                                                                             | Driving<br>Capability |

|--------------------------|------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Hard Disk Interface sign | als:-                                                                  |     |                                                                                                                                                                                                                         |                       |

| AD[30]/HD3FX#/<br>P70CS# | 107                                                                    | I/O | During PCI cycle, it is the address/data line 30.<br>During on-chip IDE access, it is the primary IDE<br>chip select signal.<br>During ISA cycle, it is the I/O port 70 chip select<br>signal.                          | 12mA                  |

| AD[29]/HD1FX#/<br>KBCS#  | 151                                                                    | I/O | During PCI cycle, it is the address/data line 29.<br>During on-chip IDE access, it is the primary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>external keyboard controller. | 12mA                  |

| AD[28]/HD37X#/<br>RTCCS# | 108                                                                    | I/O | During PCI cycle, it is the address/data line 28.<br>During on-chip IDE access, it is the secondary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>external real time clock.   | 12mA                  |

| AD[27]/HD17X#/<br>ROMCS# | 150                                                                    | I/O | During PCI cycle, it is the address/data line 27.<br>During on-chip IDE access, it is the secondary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>BIOS ROM.                   | 12mA                  |

| AD[26:24]/HDA[2:0]       | 109, 149,<br>110                                                       | I/O | During PCI cycle, it is the address/data line 26:24.<br>During on-chip IDE access, it is the IDE address<br>line 2:0.                                                                                                   | 12mA                  |

| SA[15:0]/HDD[15:0]       | 165, 168,<br>170, 172,<br>173, 175 -<br>180, 183,<br>185, 188 -<br>190 | I/O | For ISA cycle, these are the address line 15 to 0.<br>For On-chip IDE cycle, these are data line 15 to 0 for<br>the IDE port.<br>External 10Kohm pull-up is required.                                                   | 12mA                  |

| HDRD#                    | 5                                                                      | 0   | On-chip IDE Read. This is an active low output which enables data to be read from the IDE drive.                                                                                                                        | 12mA                  |

| HDWE#                    | 4                                                                      | 0   | On-chip IDE write. This is an active low output which enables data to be written to the IDE drive.                                                                                                                      | 12mA                  |

| Signal Name             | Pin<br>Number | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                   | Driving<br>Capability |

|-------------------------|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| L2 Cache Interface sign | nals:-        |     |                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| MA[11:4]/TA[7:0]        | 76 - 83       | I/O | Memory Address line 11:4 or L2 cache Tag 7:0.<br>When L2 cache is not enable, they are the memory<br>address lines for DRAM interface. When L2 cache is<br>enable, they are the multiplex bus for both cache tag<br>data and DRAM address. Signal pin TOE# high<br>represents they are carrying memory address<br>information; TOE# low represents they are carrying<br>tag data information. | 24mA                  |

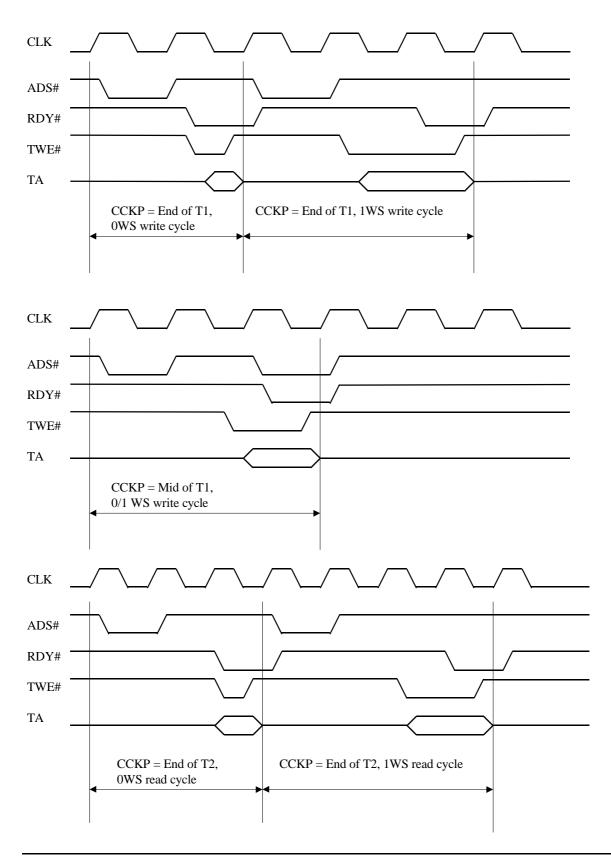

| TWE#                    | 73            | I/O | Cache Tag RAM Write enable. This is an active low<br>signal which enables TAG data to be written to the<br>external TAG RAM. It is asserted during L2 cache<br>burst fill, or write hit clean cycle in 7+1 TAG mode.                                                                                                                                                                          | 12mA                  |

| COE#                    | 35            | 0   | Cache data Output Enable. It is always asserted in<br>memory read cycle if L2 cache is enabled. If the cycle<br>is not a cache hit cycle, it will be driven in-active at<br>the following clock.                                                                                                                                                                                              | 8mA                   |

| TOE#                    | 74            | 0   | Tag RAM Output Enable. This signal is use to enable<br>the external TAG RAM output the TAG information<br>on TA[7:0]. During DRAM access, it is driven high to<br>prevent the bus conflict between TA and MA lines.                                                                                                                                                                           | 8mA                   |

| BWE#                    | 34            | 0   | Cache byte Write Enable. This is an active low signal which enables data to be written to the external cache.                                                                                                                                                                                                                                                                                 | 8mA                   |

| GW#                     | 36            | 0   | Cache global Write. This is an active low signal which enables a 32-bit date to be written to the external cache.                                                                                                                                                                                                                                                                             | 8mA                   |

| ADV#                    | 33            | 0   | Cache Advance. This is an active low signal which instructs the burst cache to advance to next address.                                                                                                                                                                                                                                                                                       | 8mA                   |

| Signal Name              | Pin<br>Number | I/O | Description                                                                                                                                                                                                                                              | Driving<br>Capability |

|--------------------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| MISC signals:-           |               |     |                                                                                                                                                                                                                                                          |                       |

| AD[30]/HD3FX#/<br>P70CS# | 107           | I/O | During PCI cycle, it is the address/data line 30.<br>During on-chip IDE access, it is the primary IDE chip<br>select signal.<br>During ISA cycle, it is the I/O port 70 chip select<br>signal.                                                           | 12mA                  |

| AD[29]/HD1FX#/<br>KBCS#  | 151           | I/O | During PCI cycle, it is the address/data line 29.<br>During on-chip IDE access, it is the primary IDE chip<br>select signal.<br>During ISA cycle, it is the chip select signal for the<br>external keyboard controller.                                  | 12mA                  |

| AD[28]/HD37X#/<br>RTCCS# | 108           | I/O | During PCI cycle, it is the address/data line 28.<br>During on-chip IDE access, it is the secondary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>external real time clock.                                    | 12mA                  |

| AD[27]/HD17X#/<br>ROMCS# | 150           | I/O | During PCI cycle, it is the address/data line 27.<br>During on-chip IDE access, it is the secondary IDE<br>chip select signal.<br>During ISA cycle, it is the chip select signal for the<br>BIOS ROM.                                                    | 12mA                  |

| KBDATA/RC#               | 99            | I/O | For internal keyboard controller, it is the keyboard<br>data pin., an external 10Kohm pull-up resister is<br>required.<br>For external keyboard controller, it is the estet CPU"<br>signal coming from external keyboard controller.                     | 12mA                  |

| KBCLK/IRQ1               | 100           | I/O | For internal keyboard controller, it is the keyboard<br>clock pin, an external 10Kohm pull-up resister is<br>required.<br>For external keyboard controller, it is the u <b>c</b> put<br>buffer fill" signal coming from external keyboard<br>controller. | 12mA                  |

| PWRGD                    | 10            | I   | Power Good. This is an active a high signal which<br>tells the system that the power supply is stable. C488<br>use this signal to reset the internal logic to a known<br>state.                                                                          |                       |

| OSCIN                    | 102           | Ι   | 14.31818MHz input. This signal is used to drive the<br>8254 timer counter inside C488 to generate the<br>speaker tone, refresh request signal, and DOS timer<br>interrupt. It is also used to drive the timer counter of<br>the power management unit.   |                       |

| HCLK                     | 103           | Ι   | Host Clock. Same as CPU clock.                                                                                                                                                                                                                           |                       |

| PCLK                     | 104           | Ι   | PCI Clock. PCI controller clock, it should be the same as or one half of the HCLK. This clock must synchronize with the HCLK.                                                                                                                            |                       |

| SLOWDWN#/<br>STPCLK#     | 2             | 0   | This signal is used to control either the clock chip slow down or CPU stop clock.                                                                                                                                                                        | 4mA                   |

| SPKOUT                   | 1             | 0   | Speaker output. it drive the speaker through an external NPN transistor.                                                                                                                                                                                 | 4mA                   |

| RTCLK/IRQ8# | 3                                                                    | Ι | Clock input for internal RTC, or alarm interrupt input for external RTC.                                                                                                                                    |     |

|-------------|----------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| DOE#        | 72                                                                   | 0 | Data Output Enable. This is an active low signal<br>which enables data flow from host data bus to address<br>bus. C488 uses this signal with AHOLD to<br>multiplex the address and data bus onto A/D[31:2]. | 8mA |

| GND         | 11, 32,<br>52, 71,<br>88, 101,<br>115, 138,<br>153, 166,<br>181, 204 |   |                                                                                                                                                                                                             |     |

| VCC         | 18, 44,<br>75, 93,<br>129, 156,<br>186                               |   |                                                                                                                                                                                                             |     |

Configuration register Index port : 8-bit I/O port at 24H Data port: 8-bit I/O port at 28H

| Index       | Description                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory cont | trol unit                                                                                                                                                           |

| 00H - 03H   | Bank 0 - 3 configuration                                                                                                                                            |

|             | Bit 7-6 Access mode [ExD]                                                                                                                                           |

|             | 00 Non page mode/Nibble mode DRAM (default)                                                                                                                         |

|             | 01 Fast page mode DRAM                                                                                                                                              |

|             | 10 EDO DRAM                                                                                                                                                         |

|             | 11 Burst EDO RAM(not supported in this revision)                                                                                                                    |

|             | Bit 5 Not used                                                                                                                                                      |

|             | Bit 4-3 Page mode type [BxM]. (See Appendix 1 for details)                                                                                                          |

|             | 00 Page I (default)                                                                                                                                                 |

|             | 01 Page II                                                                                                                                                          |

|             | 10 Page III                                                                                                                                                         |

|             | 11 Reserved                                                                                                                                                         |

|             | Bit 2-0 Memory size                                                                                                                                                 |

|             | 000 None (default for bank 1-3)                                                                                                                                     |

|             | 001 256Kbyte                                                                                                                                                        |

|             | 010 512Kbyte                                                                                                                                                        |

|             | 011 1Mbyte (default for bank 0)                                                                                                                                     |

|             | 100 2Mbyte                                                                                                                                                          |

|             | 101 4Mbyte                                                                                                                                                          |

|             | 110 8Mbyte                                                                                                                                                          |

|             | 111 16Mbyte                                                                                                                                                         |

| 04H         | Shadow control 1, access control                                                                                                                                    |

|             | Bit 7 Segment 0A000H, 128Kbyte [S7]                                                                                                                                 |

|             | Bit 6 Segment 0C000H, 32Kbyte [S6]                                                                                                                                  |

|             | Bit 5 Segment 0C800H, 32Kbyte [S5]                                                                                                                                  |

|             | Bit 4 Segment 0D000H, 32Kbyte [S4]                                                                                                                                  |

|             | Bit 3 Segment 0D800H, 32Kbyte [S3]                                                                                                                                  |

|             | Bit 4 Segment 0E000H, 32Kbyte [S2]                                                                                                                                  |

|             | Bit 1 Segment 0E800H, 32Kbyte [S1]                                                                                                                                  |

|             | Bit 0 Segment 0F000H, 64Kbyte [S0]                                                                                                                                  |

|             | <ul> <li>0 Disable shadow RAM, all access will forward to PCI bus. (default)</li> <li>1 Enable shadow RAM, access cycle will process by DRAM controller.</li> </ul> |

| 0511        |                                                                                                                                                                     |

| 05H         | Shadow control 2, write protected control                                                                                                                           |

|             | Bit 7Segment 0A000H, Read/write control [R7]Bit 6Segment 0C000H, Read/write control [R6]                                                                            |

|             | Bit 5 Segment 0C000H, Read/write control [R6]<br>Bit 5 Segment 0C800H, Read/write control [R5]                                                                      |

|             | Bit 4 Segment 0D000H, Read/write control [R4]                                                                                                                       |

|             | Bit 3 Segment 0D800H, Read/write control [R4]                                                                                                                       |

|             | Bit 2 Segment 0E000H, Read/write control [R2]                                                                                                                       |

|             | Bit 1 Segment 0E800H, Read/write control [R1]                                                                                                                       |

|             | Bit 0 Segment 0F000H, Read/write control [R0]                                                                                                                       |

|             | 0 Disable write protect, host can read or write to this area. (default)                                                                                             |

|             | 1 Enable write protect, host can only read from this area.                                                                                                          |

| 06H         | 384K relocation control                                                                                                                                             |

|             | Bit 7 Global control [RC7]                                                                                                                                          |

|             | 0 Disable relocation (default)                                                                                                                                      |

|             | 1 Enable relocation                                                                                                                                                 |

|             | Bit 6 Segment 0A000H [RC6]                                                                                                                                          |

| •           |                                                                                                                                                                     |

| II  | Bit 5    | Segment 0B000H [RC5]                                                                |

|-----|----------|-------------------------------------------------------------------------------------|

|     | Bit 4    | Segment 0C000H [RC4]                                                                |

|     | Bit 3    | Segment 0D000H [RC3]                                                                |

|     | Bit 2    | Segment 0E000H [RC2]                                                                |

|     | Bit 1    | Segment 0F000H [RC1]                                                                |

|     |          | 0 Don relocate this segment (default)                                               |

|     |          | 1 Relocate this segment                                                             |

|     | Bit 0    | Refresh address test [TESTRMA]. For proper operation, do not write "1" to this bit. |

|     |          | 0 normal operation (default)                                                        |

|     |          | 1 enable the address test                                                           |

| 07H | Reserved |                                                                                     |

| Index | Descripti | on                                                                                   |

|-------|-----------|--------------------------------------------------------------------------------------|

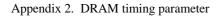

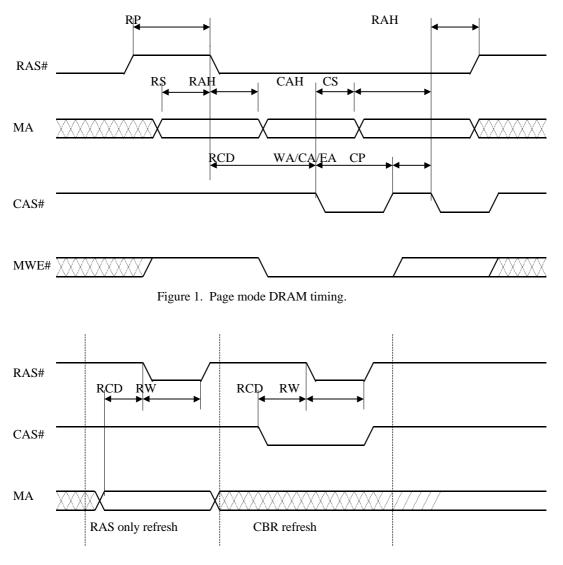

|       | -         | e Appendix 2 for details)                                                            |

| 08H   | Refresh t | iming                                                                                |

|       | Bit 7-6   | Refresh period [REP]                                                                 |

|       |           | 00 15.6uS (default)                                                                  |

|       |           | 01 31.2uS                                                                            |

|       |           | 10 46.8uS                                                                            |

|       |           | 11 62.4uS                                                                            |

|       | Bit 5     | Refresh mode [REFM]. Select CBR refresh mode will consume less power during refresh. |

|       |           | 0 CBR refresh mode                                                                   |

|       |           | 1 RAS only refresh mode (default)                                                    |

|       | Bit 4     | Staggered refresh mode [STAGREF]. Enable this mode can low RAS switch noise, but     |

|       | 2         | 4 more clocks are needed in one refresh cycle.                                       |

|       |           | 0 Disable                                                                            |

|       |           | 1 Enable (default)                                                                   |

|       | Bit 3-2   | CAS to RAS delay for CBR refresh, or MA setup timer for RAS only refresh. [CRD1].    |

|       |           | 001CLK for CBR refresh2CLKs for RAS only refresh                                     |

|       |           | 01 2 CLKs 3 CLKs                                                                     |

|       |           | 10  3  CLKs                                                                          |

|       |           | 11 4 CLKs 5 CLKs (default)                                                           |

|       | Bit 1     | Refresh option [REFHOLD]. When external cache is used with DRAM refresh mode set     |

|       | DRI       | to RAS only, This bit MUST be "0" in order to preserve the memory address line for   |

|       |           | refresh cycle.                                                                       |

|       |           | 0 Hold CPU during refresh                                                            |

|       |           | 1 Select hidden refresh (default)                                                    |

|       | Bit 0     | Not used                                                                             |

| 09H   | DRAM t    |                                                                                      |

|       | Bit 7-5   | RAS pre-charge time [RP]                                                             |

|       |           | 000 1 CLK                                                                            |

|       |           | 001 2 CLKs                                                                           |

|       |           | 010 3 CLKs                                                                           |

|       |           | 011 4 CLKs                                                                           |

|       |           | 100 5 CLKs                                                                           |

|       |           | 101 6 CLKs                                                                           |

|       |           | 110 7 CLKs                                                                           |

|       |           | 111 8 CLKs (default)                                                                 |

|       | Bit 4-3   | Row address setup time [RS]                                                          |