## Serial ATA Bridge Chip Solutions 88i8030

## **PRODUCT OVERVIEW**

The 88i8030 family of Serial ATA (SATA) bridge chips, the first offering in the Marvell® family of high-speed interface input/output (I/O) solutions, allows storage OEMs to take advanced data storage systems to the next level of performance. By converting Parallel ATA to SATA, the Marvell 88i8030 bridge solution allows Hard Disk Drive (HDD), motherboard and storage subsystem manufacturers to utilize their current Parallel ATA electronics for faster time-to-market prior to full industry transition to SATA. The 88i8030 devices are designed to interface to traditional Parallel ATA HDD controllers as well as to host chipsets running up to 150 MBps. Since the bridge allows parallel connectivity over short trace distances, the 88i8030 product allows for 150 MBps transfer rates with low noise and high reliability. The devices employ the latest SATA Physical Layer (PHY) technology, starting with the SATA Working Group-defined Generation I speed of 1.5 Gbps, and scalable to 3.0 Gbps to support the future Generation II, Phase II, SATA speed. The 88i8030's PHY leverages four generations of production-proven Serializer/Deserializer (SERDES) technology from its industry-leading Alaska® Gigabit PHY products. The Marvell bridge device implements user-selectable SSC for reduced EMI in storage systems. This makes the interface attractive not only as an inside-the-box technology, but also potentially increases its usefulness for out-of-the-box interconnects in many consumer electronics applications. The 88i8030 products offer premphasis and amplitude settings with programmable coefficients to help ensure signal integrity over extended trace and cable lengths. This advanced signaling capability allows for optimal performance in many varieties of storage applications.

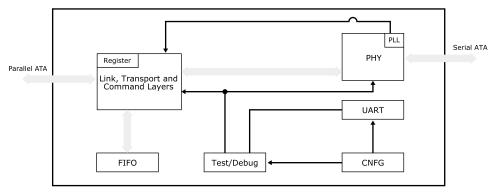

Fig 1. 88i8030 Block Diagram

| FEATURES | BENEFITS |

|----------|----------|

|          |          |

| Supports both host and device operation                                   | Enables faster system development                                                                                                 |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>User-selectable maximum speeds of 66/100/133/150 MBps</li> </ul> | Provides flexibility in system design                                                                                             |

| Ultra low power consumption                                               | <ul> <li>Helps to extend battery life in mobile applications and lessen cooling<br/>requirements in storage enclosures</li> </ul> |

| <ul> <li>Supports spec-defined power management</li> </ul>                | Efficient power consumption control                                                                                               |

| • Advanced design tolerates +/- 1.5% frequency offset                     | <ul> <li>Allows for the use of less expensive ceramic resonators, lowering<br/>system cost</li> </ul>                             |

| User-selectable Spread Spectrum Clocking (SSC) support                    | <ul> <li>Reduces Electro Magnetic Interference (EMI), key for both storage<br/>systems and PC motherboards</li> </ul>             |

| Programmable reference clock settings                                     | Increase design flexibility                                                                                                       |

| Fully-digital Phase Locked Loop (PLL)                                     | <ul> <li>Reduces sensitivity to process variations, increasing manufacturability</li> </ul>                                       |

| Pre-emphasis and amplitude settings with programmable coefficients        | <ul> <li>Ensure signal integrity over extended backplane distances up to<br/>20+ inches of FR4 trace</li> </ul>                   |

## Serial ATA Bridge Chip Solutions

**FEATURES BENEFITS**

- Supports ATA command queuing · Significantly increases system performance

- · Master/Slave support · Allows two SATA ports to connect to every Parallel port

## **APPLICATIONS**

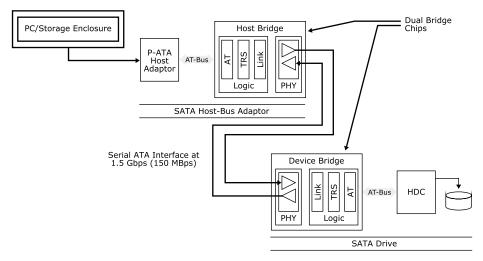

The 88i8030 products can be used in a variety of storage system applications. In conjunction with host chipsets or with PCIbased ATA host controllers, the 88i8030 devices enable immediate introduction of SATA-enabled motherboards. When used with ATA RAID controllers, the 88i8030 devices enable the deployment of SATA RAID. The 88i8030 bridge chip can also be used to externally convert Parallel ATA HDDs to SATA. In addition, two 88i8030 devices can be used in conjunction with dual-port Parallel ATA drives for fail-over applications.

Fig 2. 88i8030 Host and Device Bridge System Diagram

THE MARVELL ADVANTAGE: The Marvell 88i8030 family of SATA bridge chips comes with a complete set of hardware development tools to assist storage networking hardware engineers with product evaluation. Marvell's worldwide field applications engineers collaborate closely with network storage equipment vendors to develop and deliver new competitive products to market on time. Marvell utilizes recognized world-leading semiconductor foundry and packaging services to reliably deliver high-volume and low cost total solutions.

For more information, visit our website at www.marvell.com.

Marvell Semiconductor, Inc.

700 First Avenue Sunnyvale, CA 94089

Phone 408.222.2500

www.marvell.com

©2002 Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, the Galileo logo, and GalNet are registered trademarks of Marvell. Discovery, Fastwriter, Galileo Technology, GalTis, Horizon, Libertas, Prestera, and Virtual Cable Tester are trademarks of Marvell. All other trademarks are the property of their respective owners

100500-001 05/02

This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.