# 82562GX 10/100 Mbps Platform LAN Connect (PLC)

**Networking Silicon**

### Datasheet

# **Product Features**

- IEEE 802.3 10BASE-T/100BASE-TX compliant physical layer interface

- IEEE 802.3u Auto-Negotiation support

- Digital Adaptive Equalization control

- Link status interrupt capability

- XOR tree mode support

- 3-port LED support (speed, link and activity)

- 10BASE-T auto-polarity correction

- LAN Connect interface

- 82547/82541 layout compatible

- PHY detects polarity, MDI-X, and cable lengths. Auto MDI, MDIX crossover at all speeds

- Diagnostic loopback mode

- 1:1 transmit transformer ratio support

- Low power (less than 300 mW in active transmit mode)

- Reduced power in "unplugged mode" (less than 50 mW)

- Automatic detection of "unplugged mode"

- 3.3 V device

- Basic ASF level manageability known as Alert on LAN\* (AoL) in conjunction with ICH5/6

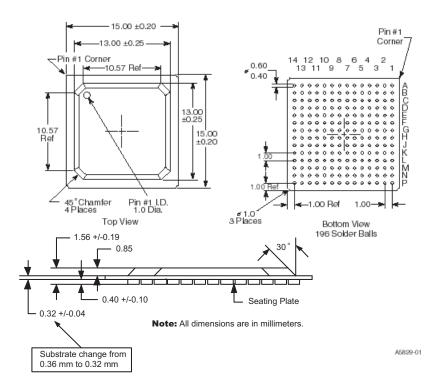

- Leaded and lead-free<sup>a</sup> 196-pin Ball Grid Array (BGA). (Devices that are lead-free are marked with a circled "e1" and have the product code prefix: LUxxxxxx.)

a. This device is lead-free. That is, lead has not been intentionally added, but lead may still exist as an impurity at <1000 ppm. The Material Declaration Data Sheet, which includes lead impurity levels and the concentration of other Restriction on Hazardous Substances (RoHS)-banned materials, is available at:

ftp://download.intel.com/design/packtech/material\_content\_IC\_Package.pdf#pagemode=bookmark

In addition, this device has been tested and conforms to the same parametric specifications as previous versions of the device.

For more information regarding lead-free products from Intel Corporation, contact your Intel Field Sales representative

# **Additional Features**

- The 82562GX PLC supports drop-in replacement with the 82562EX. If it is not used as a drop-in replacement, strapping options enable new operating modes:

- -LED support for three logic configurations.

- -LAN disable function using one pin.

- -Increased transmit strength.

- The receive BER performance increases the margin for cable length.

- Return Loss performance is improved.

# **Revision History**

| Revision | Revision Date | Description                                                                                                                                                                                                              |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.75     | May 2004      | Initial release (confidential status).                                                                                                                                                                                   |

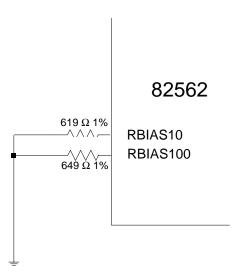

| 1.0      | Sept 2004     | Updated resistor values for RBIAS10 (new value is 619 $\Omega$ ) and RBIAS100 (new value is 649 $\Omega$ ).and added information about the lead-free device.                                                             |

| 1.1      | Oct 2004      | Updated Table 1 and Table 2 to reflect correct hardware configurations and LED logic functionality.                                                                                                                      |

|          |               | Corrected signal names to match design guide and reference schematics.                                                                                                                                                   |

| 1.2      | Nov 2004      | <ul> <li>Added information about migrating from a 2-layer 0.36 mm wide-trace sub-<br/>strate to a 2-layer 0.32 mm wide-trace substrate. Refer to the section on<br/>Package and Pinout Information.</li> </ul>           |

|          |               | <ul> <li>Added statement that no changes to existing soldering processes are<br/>needed for the 2-layer 0.32 mm wide-trace substrate change in the section<br/>describing "Package Information".</li> </ul>              |

| 1.3      | Jan 2005      | Added a note for PHY signals RBIAS100 and RBIAS10 to Section 4.3.                                                                                                                                                        |

| 1.4      | Apr 2005      | <ul> <li>Added internal/external pull-up/pull-down resistor values to the Hardware<br/>Configuration table and signal definition tables for TESTEN, ISOL_EXEC,<br/>ISOL_TI, ISOL_TCK, and ADV10/LAN_DISABLE#.</li> </ul> |

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 82562GX PLC may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © 2005, Intel Corporation

\* Other product and corporate names may be trademarks of other companies and are used only for explanation and to the owners' benefit, without intent to infringe.

# int<sub>el®</sub> Contents

| 1.0 | Introd | duction1                                                                                                                                                                                              |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 1.1    | Overview1                                                                                                                                                                                             |

|     | 1.2    | References1                                                                                                                                                                                           |

|     | 1.3    | Product Codes1                                                                                                                                                                                        |

| 2.0 | 82562  | 2GX Architectural Overview3                                                                                                                                                                           |

|     | 2.1    | LAN Connect Interface32.1.1Reset/Synchronize Operations2.1.2Reset Considerations42.1.3LAN Connect Clock Operations5                                                                                   |

|     | 2.2    | Hardware Configuration5                                                                                                                                                                               |

| 3.0 | Perfo  | rmance Enhancements7                                                                                                                                                                                  |

|     | 3.1    | New Usage Modes: 1, 2, 3, and 4         7           3.1.1         Pin Usage for Modes 1, 2, 3, and 4         7           3.1.2         Enhanced Tx Mode         8                                     |

|     | 3.2    | Management Data Interface MDI/MDI-X8                                                                                                                                                                  |

| 4.0 | 82562  | 2GX Signal Descriptions9                                                                                                                                                                              |

|     | 4.1    | Signal Type Definitions9                                                                                                                                                                              |

|     | 4.2    | Twisted Pair Ethernet (TPE) Pins9                                                                                                                                                                     |

|     | 4.3    | External Bias Pins9                                                                                                                                                                                   |

|     | 4.4    | Clock Pins10                                                                                                                                                                                          |

|     | 4.5    | Platform LAN Connect Interface Pins10                                                                                                                                                                 |

|     | 4.6    | LED Pins10                                                                                                                                                                                            |

|     | 4.7    | Miscellaneous Control Pins11                                                                                                                                                                          |

|     | 4.8    | Power and Ground Connections11                                                                                                                                                                        |

| 5.0 | AoL F  | Functionality13                                                                                                                                                                                       |

|     | 5.1    | 4.1 Supported Alerts.145.1.1 ICH4 Input Signal, INTRUDER# (Cover Tamper)145.1.2 Thermal Event145.1.3 CPU Dead on Arrival155.1.4 Operating System Hang155.1.5 BIOS Error Reporting155.1.6 Heartbeats15 |

|     | 5.2    | BIOS R                                                                | equirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15                         |

|-----|--------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|     | 5.3    | EEPRO                                                                 | M Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                         |

| 6.0 | Phys   | ical Layer                                                            | Interface Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17                         |

|     | 6.1    | 100BAS<br>6.1.1<br>6.1.2                                              | SE-TX Mode<br>100BASE-TX Transmit Blocks<br>100BASE-TX Receive Blocks                                                                                                                                                                                                                                                                                                                                                                                                             | 17                         |

|     | 6.2    | 10BASE<br>6.2.1<br>6.2.2                                              | E-T Mode<br>10BASE-T Transmit Blocks<br>10BASE-T Receive Blocks                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                         |

|     | 6.3    | Analog                                                                | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21                         |

|     | 6.4    | 6.4.1<br>6.4.2                                                        | c Reduced Power & Auto Plugging Detection<br>Auto Plugging Detection<br>Dynamic Reduced Power<br>Configuration                                                                                                                                                                                                                                                                                                                                                                    | 22<br>22                   |

| 7.0 | Platfo | orm LAN C                                                             | Connect Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23                         |

|     | 7.1    | Medium<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7 | Dependent Interface Registers 0 through 7<br>Register 0: Control Register Bit Definitions<br>Register 1: Status Register Bit Definitions<br>Register 2: PHY Identifier Register Bit Definitions<br>Register 3: PHY Identifier Register Bit Definitions<br>Register 4: Auto-Negotiation Advertisement Register Bit Definitions<br>Register 5: Auto-Negotiation Link Partner Ability<br>Register Bit Definitions<br>Register 6: Auto-Negotiation Expansion Register Bit Definitions | 23<br>24<br>25<br>25<br>26 |

|     | 7.2    | Medium                                                                | Dependent Interface Registers 8 through 15                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27                         |

|     | 7.3    | 7.3.1<br>7.3.2                                                        | Dependent Interface Registers 16 through 31     Register 16: PHY Status and Control Register Bit Definitions     Register 17: PHY Unit Special Control Bit Definitions     Register 18: Reserved     Register 19: 100BASE-TX Receive False Carrier     Counter Bit Definitions     Register 20: 100BASE-TX Receive Disconnect     Counter Bit Definitions     Register 21: 100BASE-TX Receive Error Frame     Counter Bit Definitions                                             | 27<br>28<br>29<br>29<br>29 |

|     |        | 7.3.7                                                                 | Register 22: Receive Symbol Error Counter Bit Definitions                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |

|     |        | 7.3.8                                                                 | Register 23: 100BASE-TX Receive Premature<br>End of Frame Error Counter Bit Definitions                                                                                                                                                                                                                                                                                                                                                                                           | 30                         |

|     |        | 7.3.9                                                                 | Register 24: 10BASE-T Receive End of Frame<br>Error Counter Bit Definitions                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|     |        | 7.3.10                                                                | Register 25: 10BASE-T Transmit Jabber Detect<br>Counter Bit Definitions                                                                                                                                                                                                                                                                                                                                                                                                           | 30                         |

|     |        |                                                                       | Register 27: PHY Unit Special Control Bit Definitions<br>Register 28: MDI/MDI-X Control Bit Definitions                                                                                                                                                                                                                                                                                                                                                                           |                            |

| 8.0  | 82562                | CX Test Port Functionality                                                                                                                                                                                                                                                                                                                                                                                        | 33                               |

|------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|      | 8.1                  | Asynchronous Test Mode                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

|      | 8.2                  | Test Function Description                                                                                                                                                                                                                                                                                                                                                                                         | 33                               |

| 9.0  | Volta                | ge and Temperature Specifications                                                                                                                                                                                                                                                                                                                                                                                 | 35                               |

|      | 9.1                  | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                          | 35                               |

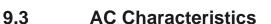

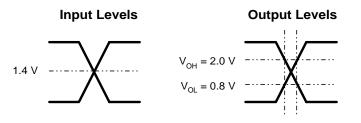

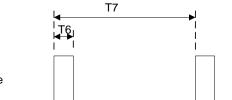

|      | 9.2<br>9.3           | DC Characteristics         9.2.1       X1 Clock DC Specifications         9.2.2       LAN Connect Interface DC Specifications         9.2.3       LED DC Specifications         9.2.4       10BASE-T Voltage and Current DC Specifications         9.2.5       100BASE-TX Voltage and Current DC Specifications         AC Characteristics         9.3.1       10BASE-T Normal Link Pulse (NLP) Timing Parameters | 35<br>36<br>36<br>36<br>37<br>38 |

| 10.0 | <b>Packa</b><br>10.1 | 9.3.2 Auto-Negotiation Fast Link Pulse (FLP) Timing Parameters<br>9.3.3 100BASE-TX Transmitter AC Specifications<br>9.3.4 Reset (JRSTSYNC) AC Specifications<br>age and Pinout Information<br>Package Information                                                                                                                                                                                                 | 39<br>40<br>40                   |

|      | 10.1                 | Pinout Information                                                                                                                                                                                                                                                                                                                                                                                                |                                  |

82562GX — Networking Silicon

# intel®

# 1.0 Introduction

This document is applicable to the Intel<sup>®</sup> 82562GX 10/100 Mbps Platform LAN Connect (PLC) device, a member of the 82562G Fast Ethernet device family.

### 1.1 Overview

The 82562GX is a highly-integrated Platform LAN Connect device designed for 10 or 100 Mbps Ethernet systems. It is based on the IEEE 10BASE-T and 100BASE-TX standards. The IEEE 802.3u standard for 100BASE-TX defines networking over two pairs of Category 5 unshielded twisted pair cable or Type 1 shielded twisted pair cable.

The 82562GX complies with the IEEE 802.3u Auto-Negotiation standard and the IEEE 802.3x Full Duplex Flow Control standard. The 82562GX also includes a PHY interface compliant to the current platform LAN connect interface.

### 1.2 References

- IEEE 802.3 Standard for Local and Metropolitan Area Networks, Institute of Electrical and Electronics Engineers.

- 82541PI(ER) and 82562GZ(GX) Dual Footprint LOM Design Guide. Intel Corporation.

- Intel<sup>®</sup> I/O Controller Hub 6 (ICH6) Family External Design Specification (EDS), Volume 1, Revision 1.5V1. Intel Corporation.

- Intel<sup>®</sup> I/O Controller Hub 6 (ICH6) Family External Design Specification (EDS), Volume 2, Revision 1.5V2. Intel Corporation.

- I/O Control Hub 2, 3, and 4 EEPROM Map and Programming Information. Intel Corporation.

- I/O Control Hub 5, 6, and 7 EEPROM Map and Programming Information. Intel Corporation.

Programming information can be obtained through your local Intel representatives.

### 1.3 Product Codes

The product ordering code for the 82562GX is: GD82562GX.

The product ordering code for the 82562GX lead-free version is: LU82562GX.

*Note:* This page intentionally left blank.

# 2.0 82562GX Architectural Overview

أ**nt**

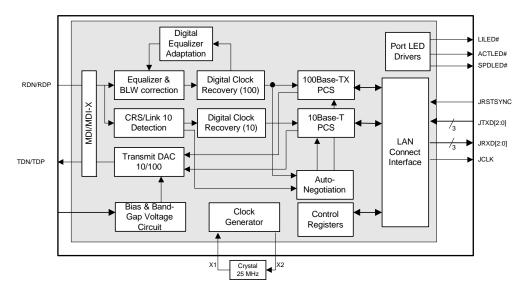

The 82562GX PLC is a 3.3 V device in a 196-pin Ball Grid Array (BGA) that is designed to work only in Data Terminal Equipment (DTE) mode. In normal operating mode, the 82562GX incorporates all active circuitry required to interface with the Intel<sup>®</sup> ICHx device with an integrated 10/100 Mbps LAN controller. The 82562GX supports a direct interface to all Media Access Control (MAC) components that meet the Platform LAN connect interface specification. Figure 1 shows a block diagram of the 82562GX architecture.

Figure 1. 82562GX PLC Block Diagram

### 2.1 LAN Connect Interface

The 82562GX supports a LAN Connect Interface (LCI) as specified in the LCI Specification. The LAN Connect is the I/O Control Hub 2 (ICH2) interface to the 82562GX. The LCI uses an 8-pin interface, which reduces the pin count from 15, for an Media Independent Interface (MII) PHY. In addition, its signaling protocol provides greater functionality, such as dynamic power reduction, from a PLC in comparison to a standard MII PHY.

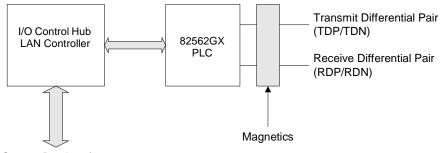

Figure 2 shows how the 82562GX can be used in a 10/100 Mbps ICHx design.

System Bus Interface

#### Figure 2. 82562GX PLC 10/100 Mbps Ethernet Solution

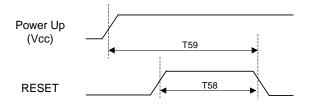

#### 2.1.1 Reset/Synchronize Operations

The Reset/Synchronize signal used by the LAN Connect Interface is driven by the ICHx integrated LAN device. It has two functions:

- Synchronize. When this pin is activated synchronously for only one LAN connect clock, it is used for synchronization between the ICHx integrated LAN and PHY on LAN connect word boundaries.

- Reset. When this pin is asserted beyond one LAN connect clock, the 82562GX uses this signal as a reset signal. To ensure a reset of the 82562GX, the reset should remain active for at least 500 µs.

#### 2.1.2 Reset Considerations

When the 82562GX Reset signal (JRSTSYNC) is asserted for at least 500  $\mu$ s, all internal circuits are reset. The 82562GZ can also be reset by setting the MII register Reset bit equal to 1 (Register 0, bit 15).

The 82562GX filters out JRSTSYNC pulses with a width of less than 200 ns to distinguish between a reset and synchronize pulse. Again, the Reset signal should be longer than 500  $\mu$ s to reset the 82562GX.

### 2.1.3 LAN Connect Clock Operations

The 82562GX drives the Platform LAN Connect clock (JCLK) at one of two possible frequencies depending upon its operation speed. When the 82562GX is in 100BASE-TX mode it drives JCLK at 50 MHz. When the 82562GX is in 10BASE-T mode it drives JCLK at 5 MHz. The LAN Connect clock does not stop during normal operation under any conditions. In reduced power mode, the 82562GX drives JCLK at 5 MHz, which is required for proper filtering of incoming packets for applications such as Wake on LAN (WoL).

## 2.2 Hardware Configuration

Four pins, Test Enable (TESTEN), Test Clock (ISOL\_TCK), Test Input (ISOL\_TI), and Test Execute (ISOL\_EXEC), define the general operation of the 82562GX. Table 1 lists the pin settings for the different modes of operation.

#### Table 1. 82562GX Hardware Configuration

| TESTEN | ISOL<br>_TCK | ISOL<br>_TI | ISOL_<br>EXEC | Mode                                                                                                                                                                                                                                                                                     | Comments                                                                                                                                                                                                                                                                                |

|--------|--------------|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0            | 0           | 0             | <ul> <li>82562G family Mode 0:</li> <li>LEDs are 82562E-compatible<br/>("A" configuration)</li> <li>LAN_DISABLE# pin is used as<br/>ADV10 (auto-negotiation<br/>advertise 10M only)</li> <li>Alternative Mode: drop-in<br/>replacement for existing 82562E-<br/>based designs</li> </ul> | The ISOL_TCK, ISOL_TCI, and ISOL_EXEC, and ADV10/<br>LAN_DISABLE# pins have internal 10 K $\Omega$ pull-down resistors and should not be connected for Mode 0 (refer to Table 2).<br>For the alternative 82562E drop-in replacement mode, pins may optionally be used as a LAN disable. |

| 0      | 0            | 1           | 1             | <ul> <li>82562G family Mode 1:</li> <li>LEDs are in configuration B</li> <li>LAN_DISABLE# pin is single pin LAN disable (tri-state and full power down function)</li> </ul>                                                                                                              | The ISOL_TCK pin has an internal 10 K $\Omega$ pull-down resistor and should not be connected for Mode 1 (refer to Table 2).                                                                                                                                                            |

| 0      | 1            | 1           | 1             | Isolate                                                                                                                                                                                                                                                                                  | Tri-state and power down.                                                                                                                                                                                                                                                               |

| 1      | 0            | 1           | 0             | Testing Mode                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                         |

| 1      | 0            | 0           | 0             | XOR Tree                                                                                                                                                                                                                                                                                 | Board testing plus tri-state.                                                                                                                                                                                                                                                           |

| 1      | 0            | 0           | 1             | 82562G family Mode 2:<br>Same as 0011 except that LEDs<br>are in configuration C                                                                                                                                                                                                         | The ISOL_TCK and ISOL_TI pins<br>have 10 K $\Omega$ internal pull-down<br>resistors and should not be<br>connected for Mode 2 (refer to<br>Table 2).                                                                                                                                    |

| 1      | 0            | 1           | 1             | 82562G family Mode 3:<br>Same as 0011 except enhance Tx<br>rise and fall times.                                                                                                                                                                                                          | The ISOL_TCK pin has an internal 10 K $\Omega$ pull-down resistor and should not be connected for Mode 3.                                                                                                                                                                               |

| 1      | 1            | 0           | 0             | 82562G family Mode 4:<br>Same as 1001 except Enhance Tx<br>rise and fall times.                                                                                                                                                                                                          | The ISOL_TI and ISOL_EXEC pins have internal 10 K $\Omega$ pull-down resistors and should not be connected for Mode 4.                                                                                                                                                                  |

#### Table 1. 82562GX Hardware Configuration

| TESTEN | ISOL<br>_TCK | ISOL<br>_TI | ISOL_<br>EXEC | Mode             | Comments                                                                                        |

|--------|--------------|-------------|---------------|------------------|-------------------------------------------------------------------------------------------------|

| 1      | 1            | 0           | 1             | Reserved         | The ISOL_TI pin has an internal 10 K $\Omega$ pull-down resistor and should not be connected.   |

| 1      | 1            | 1           | 0             | Reserved Testing | The ISOL_EXEC pin has an internal 10 K $\Omega$ pull-down resistor and should not be connected. |

| 1      | 1            | 1           | 1             | Power-down Mode  | Tri-state and power down.                                                                       |

**NOTE:** Combinations not shown in Table 1 are reserved and should not be used.

Table 2.

LED Logic Functionality

| Mode/Configuration                     | ACTLED#  | SPDLED#               | LILED#                                               |

|----------------------------------------|----------|-----------------------|------------------------------------------------------|

| Configuration A:<br>82562ET-compatible | Activity | Speed 100 Mb          | Asserted if valid link is present at 10 Mb or 100 Mb |

| Configuration B: Intel<br>GbE mode     | Activity | Link and Speed 100 Mb | Asserted if valid link is present at 10 Mb or 100 Mb |

| Configuration C:<br>Alternative mode   | Activity | Link and Speed 100 Mb | Link and Speed 10 Mb                                 |

# 3.0 Performance Enhancements

### 3.1 New Usage Modes: 1, 2, 3, and 4

82562GX supports several new features that offer design flexibility and reduced BOM cost compared to the 82562ET PLC device. To implement these new features, a board design must include the proper pull-up and/or pull-down strapping resistor options. Refer to the 82562GT/ 82562GZ/82562GX/82562G LAN on Motherboard Design Guide for more information. Table 3 lists the four new modes.

#### Table 3. Usage Modes 1, 2, 3, and 4

| Mode                                                                                      | Benefit                                                                                 |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Mode 0: 82562ET compatible.                                                               | No BOM changes necessary for equivalent performance to 82562ET.                         |

| Mode 1: LED configuration B and single-<br>pin LAN disable.                               | Usability and reduced BOM cost.                                                         |

| Mode 2: Same as mode 1, except LED configuration C.                                       | Usability and reduced BOM cost.                                                         |

| Mode 3: LED configuration B, Single Pin<br>LAN Disable, and enhanced Tx mode <sup>a</sup> | Usability, reduced BOM cost, and stronger Tx drive strength.<br>Refer to Section 3.1.2. |

| Mode 4: Same as mode 3, except LED configuration C.<br>See table note a.                  | Usability, reduced BOM cost, and stronger Tx drive strength.<br>Refer to Section 3.1.2. |

a. Only use this mode if advised to do so by an Intel representative to compensate for board design issues affecting IEEE compliance.

#### 3.1.1 Pin Usage for Modes 1, 2, 3, and 4

To use modes 1, 2, 3, or 4, the following pins need to be reviewed (refer to Table 1):

- ISOL\_TCK

- ISOL\_TI

- ISOL\_EX

- TESTEN

- ADV10/LAN\_DISABLE# and supporting circuits

- ACTLED#, SPDLED#, and LILED# and supporting circuits

#### 3.1.2 Enhanced Tx Mode

The enhanced Tx mode speeds up the rise and fall times of the 100 Mb signal. This was done so the 82562GX can have improved IEEE PHY conformance requirements over a more capacitive Analog Front End (AFE); usually caused by long traces or differential switches that customers use, usually on mobile platforms. However, running an 82562GX device in enhanced mode increases the radiated emissions seen from the LAN solution. The increase in radiated emissions may or may not impact the DUT's ability to pass regulatory requirements, as it will depend largely on the design of the AFE. The enhanced mode should only be used when 100Base-TX rise/fall times cannot be met in the normal 82562GX mode. Consult an Intel representative if you are considering using this mode.

### 3.2 Management Data Interface MDI/MDI-X

MDI/MDI-X provides the ability to automatically detect the required cable connection type and configure the controller-side MAU to the cable type. MDI/MDI-X effectively allows all properly wired Ethernet cables usable with any Ethernet device to be connected to the 82562GX without any additional external logic.

MDI/MDI-X enables auto-correction of incorrect cabling with respect to cross-over versus straight-through cables. The 82562GX can identify the cable connection type and adjust its MDI port to the cable by switching between the TD and RD pairs. The auto-switching is done prior to the start of the hardware auto negotiation algorithm.

In a standard straight-through RJ-45 port configuration, the transmit pair is on contacts 1 and 2, and the receive pair on contacts 3 and 6. These are defined by Clause 23.7.1 of the IEEE 802.3u standard.

Table 4 lists the connections for both straight-through and cross-over RJ-45 ports for comparison.

| RJ-45<br>Contact | Straight-Through<br>MDI Signal <sup>a</sup> | Cross-Over MDIX<br>Signal <sup>b</sup> |

|------------------|---------------------------------------------|----------------------------------------|

| 1                | TD+                                         | RD+                                    |

| 2                | TD-                                         | RD-                                    |

| 3                | RD+                                         | TD+                                    |

| 4                | Not Used                                    | Not Used                               |

| 5                | Not Used                                    | Not Used                               |

| 6                | RD-                                         | TD-                                    |

| 7                | Not Used                                    | Not Used                               |

| 8                | Not Used                                    | Not Used                               |

#### Table 4. RJ-45 Connections

a. Straight-through connections used on Data Terminal Equipment (DTE) applications.

b. Cross-over connections used on Hub and Switch applications.

# 4.0 82562GX Signal Descriptions

# 4.1 Signal Type Definitions

| Туре | Name                      | Description                                                                              |

|------|---------------------------|------------------------------------------------------------------------------------------|

| I    | Input                     | Input pin to the 82562GX.                                                                |

| 0    | Output                    | Output pin from the 82562GX.                                                             |

| I/O  | Input/Output              | Multiplexed input and output pin to and from the 82562GX.                                |

| MLT  | Multi-level<br>analog I/O | Multi-level analog pin used for input and output.                                        |

| В    | Bias                      | Bias pin used for ground connection through a resistor or an external voltage reference. |

| DPS  | Digital Power<br>Supply   | Digital power or ground pin for the 82562GX.                                             |

| APS  | Analog Power<br>Supply    | Analog power or ground pin for the 82562GX.                                              |

### 4.2 Twisted Pair Ethernet (TPE) Pins

| Pin Name   | Туре | Description                                                                                                                                                                                                                                                                                                                              |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDP<br>TDN | MLT  | <b>Transmit Differential Pair.</b> The transmit differential pair sends serial bit streams to the unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in 10BASE-T (Manchester) mode and a three-level signal in 100BASE-TX mode (MLT-3). These signals directly interface with the isolation transformer.   |

| RDP<br>RDN | MLT  | <b>Receive Differential Pair.</b> The receive differential pair receive the serial bit stream from an unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in 10BASE-T mode (Manchester) or a three-level signal in 100BASE-TX mode (MLT-3). These signals directly interface with an isolation transformer. |

### 4.3 External Bias Pins

| Pin Name | Туре | Description                                                                                                   |

|----------|------|---------------------------------------------------------------------------------------------------------------|

| RBIAS10  | В    | <b>Reference Bias Resistor (100 Mbps).</b> This pin should be connected to a pull-down resistor. <sup>a</sup> |

| RBIAS100 | В    | <b>Reference Bias Resistor (10 Mbps).</b> This pin should be connected to a pull-down resistor. <sup>a</sup>  |

a. Based on some board designs, RBIAS100 and RBIAS10 values may need to be increased/decreased to compensate for high/ low MDI transmit amplitude. See the 82541PI(ER) and 82562GZ(GX) Dual Footprint LOM Design Guide for more information.

# 4.4 Clock Pins

| Pin Name | Туре | Description                                                                                                                                                                                                           |  |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| X1       | I    | <b>Crystal Input Clock.</b> X1 and X2 can be driven by an external 25 MHz crystal of 30 PPM. Otherwise, X1 is driven by an external metal-oxide semiconductor (MOS) level 25 MHz oscillator when X2 is left floating. |  |

| X2       | 0    | <b>Crystal Output Clock.</b> X1 and X2 can be driven by an external 25 MHz crystal of 30 PPM.                                                                                                                         |  |

### 4.5 Platform LAN Connect Interface Pins

| Pin Name  | Туре | Description                                                                                                                                                                                                                                                                                                                       |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JCLK      | 0    | LAN Connect Clock. The LAN Connect Clock is driven by the<br>82562GX on two frequencies depending on operation speed. When the 82562GX is<br>in 100BASE-TX mode, JCLK drives a 50 MHz clock. Otherwise, JCLK drives a 5<br>MHz clock for 10BASE-T. The JCLK does not stop during normal operation.                                |

| JRSTSYNC  | I    | <b>Reset/Synchronize.</b> This is a multiplexed pin and is driven by the Media Access Control (MAC) layer device. Its functions are:                                                                                                                                                                                              |

|           |      | <ul> <li>Reset. When this pin is asserted beyond one LAN Connect clock period, the<br/>82562GX uses this signal Reset. To ensure reset of the 82562GX, the Reset<br/>signal should remain active for at least 500 µseconds.</li> </ul>                                                                                            |

|           |      | • Synchronize. When this pin is activated synchronously, for only one LAN Connect clock period, it is used to synchronize the MAC and PHY on LAN Connect word boundaries.                                                                                                                                                         |

| JTXD[2:0] | I    | LAN Connect Transmit Data. The LAN Connect transmit pins are used to transfer data from the MAC device to the 82562GX. These pins are used to move transmitted data and real time control and management data. They also transmit out of band control data from the MAC to the PHY. The pins should be fully synchronous to JCLK. |

| JRXD[2:0] | 0    | <b>LAN Connect Receive Data.</b> The LAN Connect receive pins are used to transfer data from the 82562GX to the MAC device. These pins are used to move received data and real time control and management data. They also move out of band control data from the PHY to the MAC. These pins are synchronous to JCLK.             |

### 4.6 LED Pins

| Pin Name | Туре | Description                                                                                                                                                                                                                                                        |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LILED#   | 0    | Link Integrity LED. The LILED# signal has three logic modes. The LED configurations are listed in Table 2, "LED Logic Functionality".                                                                                                                              |

| ACTLED#  | 0    | Activity LED. The LED is active low and the Activity LED signal indicates either receive or transmit activity. When no activity is present, the LED is off. The Activity LED will flicker when activity is present. The flicker rate depends on the activity load. |

|          |      | If Address Matching mode is enabled by the MAC, this pin will also indicate address match events on previously received frames.                                                                                                                                    |

| SPDLED#  | 0    | <b>Speed LED.</b> The SPDLED# signal has three logic modes. The LED configurations are listed in Table 2, "LED Logic Functionality".                                                                                                                               |

# 4.7 Miscellaneous Control Pins

| Pin Name                 | Туре | Description                                                                                                                                                                                                                                 |

|--------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISABLE# the 82562GX adv |      | Advertise 10 Mbps Only. The Advertise 10 Mbps Only signal is asserted high, and the 82562GX advertises only 10BASE-T technology during Auto-Negotiation processes in this state. Otherwise, the 82562GX advertises all of its technologies. |

|                          |      | Note: ADV10 has an internal 10 K $\Omega$ pull-down resistor.                                                                                                                                                                               |

|                          |      | LAN Disable in 82562G Mode. In the 82562G operating mode, this pin is used as a LAN disable signal. When it is driven low, the device is fully powered down.                                                                                |

| ISOL_TCK                 | I    | <b>Test Clock.</b> The Test Clock signal sets the device into various modes in conjunction with the Test Input, Test Execute and Test Enable pins (refer to Table 1, "82562GX Hardware Configuration").                                     |

|                          |      | In the manufacturing test mode, it acts as the test clock.                                                                                                                                                                                  |

|                          |      | Note: ISOL_TCK has an internal 10 K $\Omega$ pull-down resistor.                                                                                                                                                                            |

| ISOL_TI                  | I    | <b>Test Input.</b> The Test Input signal sets the device into various modes in conjunction with the Test Clock, Test Execute and Test Enable pins (refer to Table 1, "82562GX Hardware Configuration").                                     |

|                          |      | In the manufacturing test mode, it acts as the test data input pin.                                                                                                                                                                         |

|                          |      | Note: ISOL_TI has an internal 10 K $\Omega$ pull-down resistor.                                                                                                                                                                             |

|                          |      | <b>Test Execute.</b> The Test Execute signal sets the device into various modes in conjunction with the Test Clock, Test Input, and Test Enable pins (refer to Table 1, "82562GX Hardware Configuration").                                  |

|                          |      | In the manufacturing test mode, it places the command that was entered through the TI pin in the instruction register.                                                                                                                      |

|                          |      | Note: ISOL_EXEC has an internal 10 K $\Omega$ pull-down resistor.                                                                                                                                                                           |

| TOUT                     | 0    | <b>Test Output.</b> The Test Output pin is used for Boundary XOR scan output. In the manufacturing test mode, it acts as the test output port.                                                                                              |

| TESTEN                   | I    | <b>Test Enable.</b> The Test Enable pin is used to enable test mode and should be externally pulled up to $V_{cc}$ using a 200 $\Omega$ resistor to allow XOR Tree test mode.                                                               |

## 4.8 **Power and Ground Connections**

| Pin Name | Туре | Description                                                                                  |  |

|----------|------|----------------------------------------------------------------------------------------------|--|

| VCC      | DPS  | <b>Digital 3.3 V Power.</b> These pins should be connected to the main digital power supply. |  |

| VSS      | DPS  | Digital Ground. These pins should be connected to the main digital ground.                   |  |

*Note:* This page intentionally left blank.

# 5.0 AoL Functionality

The 82562GX is designed to provide basic ASF level manageability known as Alert on LAN\*. This functionality is exclusive to the 82562GX.

AoL technology is supported by Intel solutions in four distinct configurations:

- The 82559 and AoL 2 ASIC. These two components make the second generation of AoL technology (known as AoL 2) and introduced the concept of "receive" capabilities. AoL 2 solutions have the ability to receive incoming packets and act accordingly based on its content.

- 82559 and I/O Control Hub 1 (ICH1). The next generation of alerting technologies (called basic AoL) introduced a higher level of integration in both the chipset and LAN controller. The devices used, the 82559 and ICH1, communicate through a System Management Bus (SMB) interface known as SMB link.

- 82562GX and I/O Control Hub 4 (ICH4). This is the latest generation of the alerting technology. The ICH4 device integrates a LAN controller and alerting capabilities to enable the 82562GX PLC to provide basic AoL functionality.

- 82550 or future LAN controller. IP Security, AoL 2 and LAN functionality are integrated into one component. This single device solution relieves board space constraints.

Table 5 lists a comparison of features between several AoL solutions:

Table 5.

AoL Solutions and Features

| Feature                    | 82550 or<br>future LAN<br>Controller  | 82562GX and<br>ICH4 | 82559 and<br>ICH1 | 82559 and<br>AoL 2 ASIC |

|----------------------------|---------------------------------------|---------------------|-------------------|-------------------------|

| CPU dead on arrival        | Yes with ICH                          | Yes                 | Yes               | Yes with ICH            |

| Intruder detection         | Yes                                   | Yes                 | Yes               | Yes                     |

| Temperature event          | Yes                                   | Yes                 | Yes               | Yes                     |

| CPU missing                | Yes                                   | N/A                 | N/A               | 2                       |

| Link loss                  | Yes                                   | No                  | No                | Yes                     |

| Number of GPIO inputs      | 0                                     | 0                   | 0                 | 6                       |

| Heartbeat                  | Yes                                   | Yes                 | Yes               | Yes                     |

| Watchdog timer             | Yes                                   | Yes                 | Yes               | Yes                     |

| Software message size      | 2 bytes                               | 2 bytes             | 2 bytes           | 2 bytes                 |

| Event acknowledge          | Yes                                   | No                  | No                | Yes (3 pin)             |

| Presence pong              | Yes                                   | No                  | No                | Yes (3 pin)             |

| Advanced receive functions | Yes                                   | No                  | No                | Yes (3 pin)             |

| SMB polling                | Yes                                   | No                  | No                | Yes                     |

| Host interface             | SMB                                   | LCI                 | PCI               | SMB                     |

| Packet storage             | 82550 (or<br>future device)<br>EEPROM | ICH4 LAN<br>EEPROM  | 82559<br>EEPROM   | AoL 2 ASIC<br>EEPROM    |

لمأالا

#### Table 5. AoL Solutions and Features

| Feature               | 82550 or<br>future LAN<br>Controller | 82562GX and<br>ICH4 | 82559 and<br>ICH1 | 82559 and<br>AoL 2 ASIC |

|-----------------------|--------------------------------------|---------------------|-------------------|-------------------------|

| Polarity configurable | Yes                                  | No                  | No                | Yes                     |

| Event maskable        | Yes                                  | No                  | No                | Yes                     |

| SNMP packets          | Yes                                  | No                  | No                | Yes                     |

### 5.1 4.1 Supported Alerts

The 82562GX, when used in conjunction with the I/O Control Hub 4 (ICH4) device, provides a complete AoL solution that includes:

- Cover tamper alert

- Thermal event alert

- CPU Dead on Arrival (DOA) alert

- Operating System (OS) hang alert

- BIOS error reporting

- Heartbeat

#### 5.1.1 ICH4 Input Signal, INTRUDER# (Cover Tamper)

The ICH4 has an input signal, INTRUDER#, that can be attached to a switch activated by the opening of a system's case. This input has a 2 Real Time Clock (RTC) debounce. If the Intruder signal is asserted (after the debouncer), the Intruder Detection (INTRD\_DET) bit is set in the Total Cost of Ownership (TCO) Status register. The Intruder Selection (INTRD\_SEL) bits in the TCO Count register enable the ICH4 to cause a the System Management Interrupt signal (SMI#) to be asserted or interrupt. The BIOS or interrupt handler transitions to the S5 power state by writing to the Sleep Enable (SLP\_EN) bit. Software can directly read the status of the INTRUDER# signal by clearing and reading the INTRD\_DET bit. This allows the signal to be used as a general purpose input if the intruder function is not required.

- *Note:* The INTRD\_DET bit is also located in the ICH4's RTC well. It is set and cleared synchronously with the RTC. When software attempts to clear the INTRD\_DET bit (write a 1b to the bit location), there may be a 2 RTC (about 65 ms) delay before the bit is actually cleared. INTRUDER# should be asserted for a minimum of 1 ms in order to guarantee that the INTRD\_DET bit is set.

- *Note:* If the Intruder signal is still active when software attempts to clear the INTRD\_DET bit, the bit remains set and an SMI is generated immediately. The SMI handler can clear the INTRD\_SEL bits to avoid further SMIs. However, if the Intruder signal becomes inactive and then active again, no further SMIs are generated because the INTRD\_SEL bits force SMI# to be de-asserted.

#### 5.1.2 Thermal Event

An external thermal sensor asserting the thermal signal (THRM# pin) on the ICH4 device triggers this event. An LM75 or ADM1024 are common sensors used for this function.

#### 5.1.3 CPU Dead on Arrival

The CPU Dead on Arrival (DOA) feature detects if the CPU fails to execute the first instruction properly after the system is powered on. If a failure is detected, the ICH4 must send out an alert to the remote management console through the 82562GX.

#### 5.1.4 Operating System Hang

An Operating System (OS) hang is detected when AoL software does not refresh the watchdog timer at the specified time. The watchdog timer needs to be refreshed to avoid expiration and cause an alert on the network.

#### 5.1.5 BIOS Error Reporting

AoL technology allows a system to send alerts regarding BIOS level errors or status to a remote management console in real time as the events occur. This is one of the most flexible features of AoL technology. The BIOS can be customized to include any number of Power On Self Test (POST) code hooks that help troubleshoot a problematic system from a remote management console.

#### 5.1.6 Heartbeats

Heartbeats are used to notify a remote management console the system is still present on the network. The heartbeat also functions as a periodic status indicator for monitoring and security purposes. A heartbeat packet contains system health information useful for tracking and identifying a system at risk.

### 5.2 BIOS Requirements

To enable the 82562GX AoL capability, changes are required in the system BIOS. The Alert on LAN 2 Software Developer's Manual, Revision 2.2 (OR-2020), which may be obtained through your local Intel representative, provides detailed information for the required BIOS modifications. General BIOS requirements include:

- System Management BIOS (SMBIOS) 2.3 compliant

- ICH initialization code for AoL support (Alert on LAN 2 Software Developer's Manual, Revision 2.2)

- Addition of Type 128 structure for 82562GX support

- Addition of Type 7 structure for PCI slot upgrade support

#### 5.3 **EEPROM** Requirements

The 82562GX requires a 256-word EEPROM for storage of the alert envelope in addition to the usual information found in the 64-word EEPROM. Detailed information for EEPROM requirements and content is available in the *I/O Control Hub 2, 3, 4, 5, and 6 EEPROM Map and Programming Information*.

*Note:* This page intentionally left blank.

# 6.0 Physical Layer Interface Functionality

The 82562GX supports a direct glueless interface to all components that comply with the LAN Connect specification.

### 6.1 100BASE-TX Mode

#### 6.1.1 100BASE-TX Transmit Blocks

The transmit subsection of the 82562GX accepts 3 bit wide data from the LAN Connect unit. Another subsection passes data unconditionally to the 4B/5B encoder.

The 4B/5B encoder accepts nibble-wide data (4 bits) from the CSMA unit and compiles it into 5bit-wide parallel symbols. These symbols are scrambled and serialized into a 125 Mbps bit stream, converted by the analog transmit driver into a MLT-3 waveform format, and transmitted onto the Unshielded Twisted Pair (UTP) or Shielded Twisted Pair (STP) wire.

#### 6.1.1.1 100BASE-TX 4B/5B Encoder

The 4B/5B encoder complies with the IEEE 802.3u 100BASE-TX standard. Four bits are encoded according to the transmit 4B/5B lookup table. The lookup table matches a 5-bit code to each 4-bit code. The table below illustrates the 4B/5B encoding scheme associated with the given symbol.

| Symbol | 5B Symbol Code | 4B Nibble Code                      |

|--------|----------------|-------------------------------------|

| 0      | 11110          | 0000                                |

| 1      | 01001          | 0001                                |

| 2      | 10100          | 0010                                |

| 3      | 10101          | 0011                                |

| 4      | 01010          | 0100                                |

| 5      | 01011          | 0101                                |

| 6      | 01110          | 0110                                |

| 7      | 01111          | 0111                                |

| 8      | 10010          | 1000                                |

| 9      | 10011          | 1001                                |

| А      | 10110          | 1010                                |

| В      | 10111          | 1011                                |

| С      | 11010          | 1100                                |

| D      | 11011          | 1101                                |

| Е      | 11100          | 1110                                |

| F      | 11101          | 1111                                |

| I      | 11111          | Inter Packet Idle Symbol<br>(No 4B) |

#### Table 6. 4B/5B Encoder

| Symbol | 5B Symbol Code | 4B Nibble Code                               |

|--------|----------------|----------------------------------------------|

| J      | 11000          | 1st Start of Packet Symbol<br>0101           |

| К      | 10001          | 2nd Start of Packet Symbol<br>0101           |

| Т      | 01101          | 1st End of Packet Symbol                     |

| R      | 00111          | 2nd End of Packet Symbol<br>and Flow Control |

| V      | 00000          | INVALID                                      |

| V      | 00001          | INVALID                                      |

| V      | 00010          | INVALID                                      |

| V      | 00011          | INVALID                                      |

| Н      | 00100          | INVALID                                      |

| V      | 00101          | INVALID                                      |

| V      | 00110          | INVALID                                      |

| V      | 01000          | INVALID                                      |

| V      | 01100          | INVALID                                      |

| V      | 10000          | Flow Control S                               |

| V      | 11001          | INVALID                                      |

#### 6.1.1.2 100BASE-TX Scrambler and MLT-3 Encoder

Data is scrambled in 100BASE-TX in order to reduce electromagnetic emissions during long transmissions of high-frequency data codes. The scrambler logic accepts 5 bits from the 4B/5B encoder block and presents the scrambled data to the MLT-3 encoder. The 82562GX implements the 11-bit stream cipher scrambler as adopted by the ANSI XT3T9.5 committee for UTP operation. The cipher equation used is:

$X[n] = X[n-11] + X[n-9] \pmod{2}$

The MLT-3 encoder receives the scrambled Non-Return to Zero (NRZ) data stream from the scrambler and encodes the stream into MLT-3 for presentation to the driver. MLT-3 is similar to NRZ1 coding, but three levels are output instead of two. The three output levels are positive, negative and zero. When an NRZ "0" arrives at the input of the encoder, the last output level is maintained (either positive, negative or zero). When an NRZ "1" arrives at the input of the encoder, the output steps to the next level. The order of steps is negative-zero-positive-zero which continues periodically. Refer to IEEE 802.3 Specification for further details.

#### 6.1.1.3 100BASE-TX Transmit Framing

The 82562GX does not differentiate between the fields of the MAC frame containing preamble, start of frame delimiter, data and Cyclic Redundancy Check (CRC). The 82562GX encodes the first byte of the preamble as the "JK" symbol, encodes all other pieces of data according to the 4B/5B lookup table, and adds the "TR" code after the end of the packet. The 82562GX scrambles and serializes the data into a 125 Mbps stream, encodes it as MLT-3, and drives it onto the wire.

#### 6.1.1.4 Transmit Driver

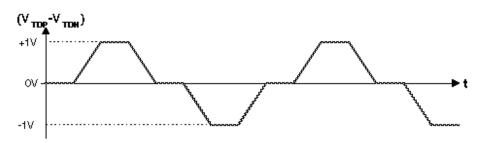

The transmit differential lines are implemented with a digital slope controlled current driver that meets Twisted Pair Physical Media Device (TP-PMD) specifications. Current is sunk from the isolation transformer by the transmit differential pins. The conceptual transmit differential waveform for 100 Mbps is illustrated in the following figure.

#### Figure 3. Conceptual Transmit Differential Waveform

The magnetics module external to the 82562GX converts  $I_{TDP}$  and  $I_{TDN}$  to 2.0  $V_{PP}$  as required by the TP-PMD specification. The same magnetics used for 100BASE-TX mode can also work in 10BASE-T mode.

#### 6.1.2 100BASE-TX Receive Blocks

The receive subsection of the 82562GX accepts 100BASE-TX MLT-3 data on the receive differential pair. Due to the advanced digital signal processing design techniques employed, the 82562GX will accurately receive valid data from Category 5 (CAT5) UTP and Type 1 STP cable of length well in excess of 100 meters.

#### 6.1.2.1 Adaptive Equalizer

The distorted MLT-3 signal at the end of the wire is restored by the equalizer. The equalizer performs adaptation based on the shape of the received signal, equalizing the signal to meet superior data dependent jitter performance.

#### 6.1.2.2 Receive Clock and Data Recovery

The clock recovery circuit uses advanced digital signal processing technology to compensate for various signal jitter causes. The circuit recovers the 125 MHz clock and data and presents the data to the MLT-3 decoder.

#### 6.1.2.3 MLT-3 Decoder, Descrambler, and Receive Digital Section

The 82562GX first decodes the MLT-3 data, and then the descrambler reproduces the 5B symbols originated in the transmitter. The descrambling is based on synchronization to the transmission of the 11-bit Linear Feedback Shift Register (LFSR) during an idle phase. The data is decoded at the 4B/5B decoder. After the 4B symbols are obtained, the 82562GX outputs the receive data to the CSMA unit.

In 100BASE-TX mode, the 82562GX can detect errors in receive data in a number of ways. Any of the following conditions is considered an error:

- Link integrity fails in the middle of frame reception.

- The start of stream delimiter "JK" symbol is not fully detected after idle.

- An invalid symbol is detected at the 4B/5B decoder.

- Idle is detected in the middle of a frame (before "TR" is detected).

#### 6.2 10BASE-T Mode

#### 6.2.1 10BASE-T Transmit Blocks

#### 6.2.1.1 10BASE-T Manchester Encoder

After the 2.5 MHz clocked data is serialized in a 10 Mbps serial stream, the 20 MHz clock performs the Manchester encoding. The Manchester code always has a mid-bit transition. The boundary transition occurs only when the data is the same from bit to bit. For example, if the value is 11b, then the change is from low to high within the boundary.

#### 6.2.1.2 10BASE-T Driver and Filter

Since 10BASE-T and 100BASE-TX have different filtration needs, both filters are implemented inside the chip. The 82562GX supports both technologies through one pair of transmit differential pins and by externally sharing the same magnetics.

In 10 Mbps mode the line drivers use a pre-distortion algorithm to improve jitter tolerance. The line drivers reduce their drive level during the second half of "wide" (100 ns) Manchester pulses and maintain a full drive level during all narrow (50 ns) pulses and the first half of the wide pulses. This reduces line overcharging during wide pulses, a major source of jitter.

#### 6.2.2 10BASE-T Receive Blocks

#### 6.2.2.1 10BASE-T Manchester Decoder

The 82562GX performs Manchester decoding and timing recovery in 10BASE-T mode. The Manchester encoded data stream is decoded from the receive differential pair. This data is transferred to the controller at 2.5 MHz/nibble. The high-performance circuitry of the 82562GX exceeds the IEEE 802.3 jitter requirements.

#### 6.2.2.2 10BASE-T Twisted Pair Ethernet (TPE) Receive Buffer and Filter

In 10 Mbps mode, data is expected to be received on the receive differential pair after passing through isolation transformers. The filter is implemented inside the 82562GX for supporting single magnetics that are shared with the 100BASE-TX side. The input differential voltage range for the Twisted Pair Ethernet (TPE) receiver is greater than 585 mV and less than 3.1 V. The TPE receive buffer distinguishes valid receive data, link test pulses, and the idle condition, according to the requirements of the 10BASE-T standard.

The following line activity is determined to be inactive and is rejected as invalid data:

- Differential pulses of peak magnitude less than 300 mV.

- Continuous sinusoids with a differential amplitude less than 6.2  $\rm V_{PP}$  and frequency less than 2 MHz.

- Sine waves of a single cycle duration starting with  $0^{\circ}$  or  $180^{\circ}$  phase that have a differential amplitude less than 6.2 V<sub>PP</sub> and a frequency of at least 2 MHz and not more than 16 MHz. These single-cycle sine waves are discarded only if they are preceded by 4 bit times (400 ns) of silence.

All other activity is determined to be either data, link test pulses, Auto-Negotiation fast link pulses, or the idle condition.

### 6.3 Analog References

The 82562GX has two inputs, RBIAS100 and RBIAS10, that require external resistor connections to set biases for its internal analog section. The input pins are sensitive to the resistor value and experimentation is required to determine the correct values for any given layout. Note that the values listed in Figure 4 are starting values. Also, resistors of 1% tolerance should be used.

#### Figure 4. Analog References

### 6.4 Dynamic Reduced Power & Auto Plugging Detection