# **Intel740™ Graphics Accelerator**

**Design Guide**

August 1998

Order Number: 290619-003

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The Intel740™ graphics accelerator may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Such errata are not covered by Intel's warranty. Current characterized errata are available upon request.

$l^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by:

calling 1-800-548-4725 or

by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 Contents

| 1 | Introd | luction |             |                                            | 1-1  |

|---|--------|---------|-------------|--------------------------------------------|------|

|   | 1.1    | About   | This Design | gn Guide                                   | 1-1  |

|   | 1.2    |         |             |                                            |      |

| 2 | Addin  | Card De | sign        |                                            | 2-1  |

|   | 2.1    | Introdu | uction      |                                            | 2-1  |

|   |        | 2.1.1   |             | -<br>eatures                               |      |

|   |        |         | 2.1.1.1     | Intel740 <sup>™</sup> Graphics Accelerator |      |

|   |        | 2.1.2   |             | - Video Decoder                            |      |

|   |        |         | 2.1.2.1     | BT869 - TV Encoder                         |      |

|   |        | 2.1.3   |             | logy                                       |      |

|   |        | 20      | 2.1.3.1     | Power Sources                              |      |

|   |        |         | 2.1.3.2     | Fences                                     |      |

|   |        |         | 2.1.3.3     | Stitching                                  |      |

|   | 2.2    | Lavou   | t and Rout  | ing Guidelines                             |      |

|   |        | 2.Ź.1   |             | ent                                        |      |

|   |        | 2.2.2   |             | escription                                 |      |

|   |        | 2.2.3   |             | mponent                                    |      |

|   |        |         | 2.2.3.1     | Layout Requirements                        |      |

|   |        |         | 2.2.3.2     | Ground Connections                         |      |

|   |        |         | 2.2.3.3     | Power Connections                          |      |

|   |        |         | 2.2.3.4     | Decoupling                                 |      |

|   |        |         | 2.2.3.5     | General Signal Routing                     |      |

|   |        | 2.2.4   | Voltage     | Regulator                                  |      |

|   |        | 2.2.5   |             | ideo Decoder                               |      |

|   |        |         | 2.2.5.1     | Ground Planes                              |      |

|   |        |         | 2.2.5.2     | Power Planes                               |      |

|   |        |         | 2.2.5.3     | Passive Components and Signal Routing      |      |

|   |        | 2.2.6   | Bt869 V     | ideo Encoder                               | 2-12 |

|   |        |         | 2.2.6.1     | Ground Planes                              |      |

|   |        |         | 2.2.6.2     | Power Planes                               | 2-13 |

|   |        |         | 2.2.6.3     | Passive Components and Signal Routing      | 2-13 |

|   |        |         | 2.2.6.4     | AGP Layout and Routing Guidelines          | 2-13 |

|   |        |         | 2.2.6.5     | Intel740™ Graphics Accelerator Memory      |      |

|   |        |         |             | Layout and Routing Guidelines              | 2-14 |

|   |        |         | 2.2.6.6     | Intel740™ Graphics Accelerator Memory      |      |

|   |        |         |             | Configurations                             | 2-17 |

|   |        |         | 2.2.6.7     | TV Out Interface                           |      |

|   |        |         | 2.2.6.8     | Analog Signals                             |      |

|   |        | 2.2.7   |             | FCC Considerations                         |      |

|   | 2.3    | Addin   | Card Sche   | ematics                                    | 2-21 |

# int<sub>e</sub>l<sub>®</sub>

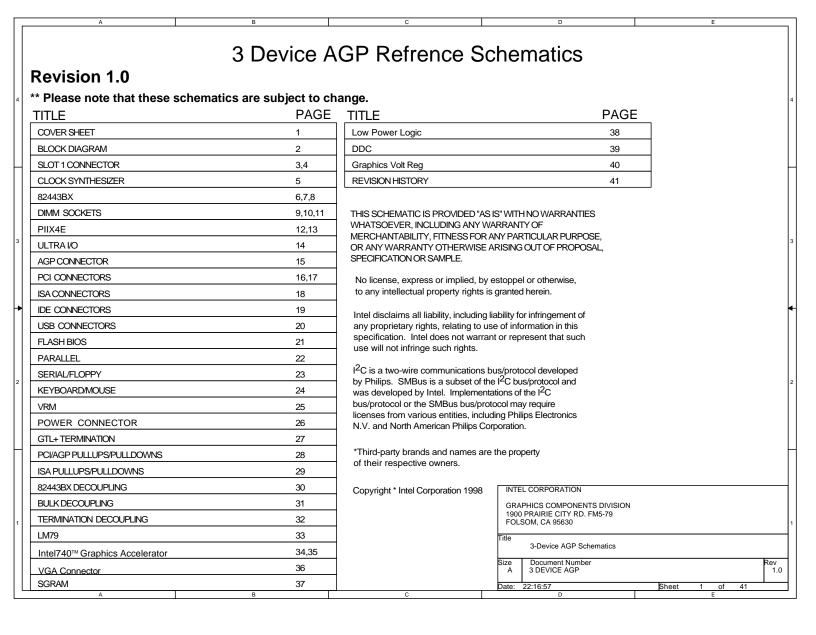

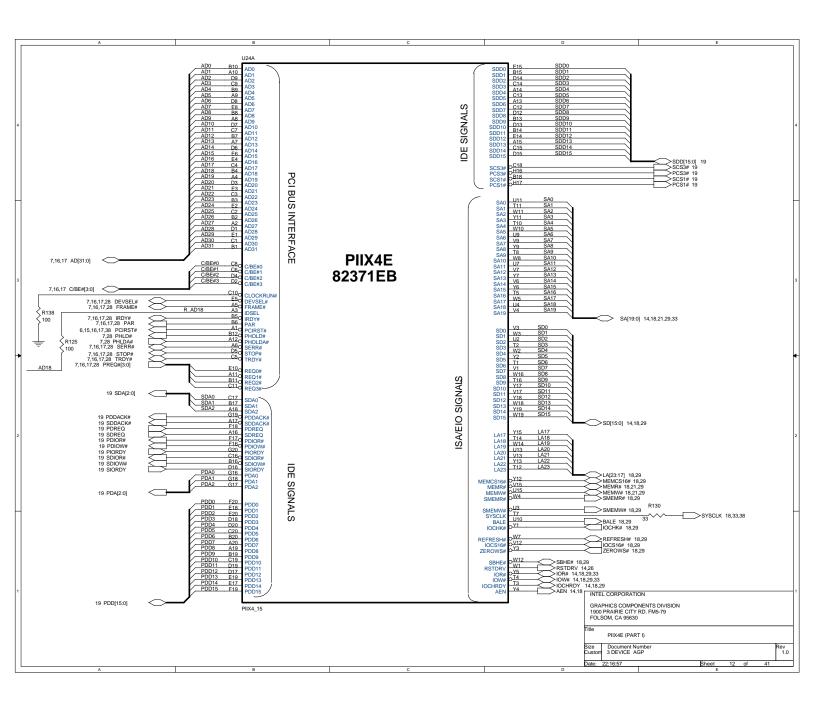

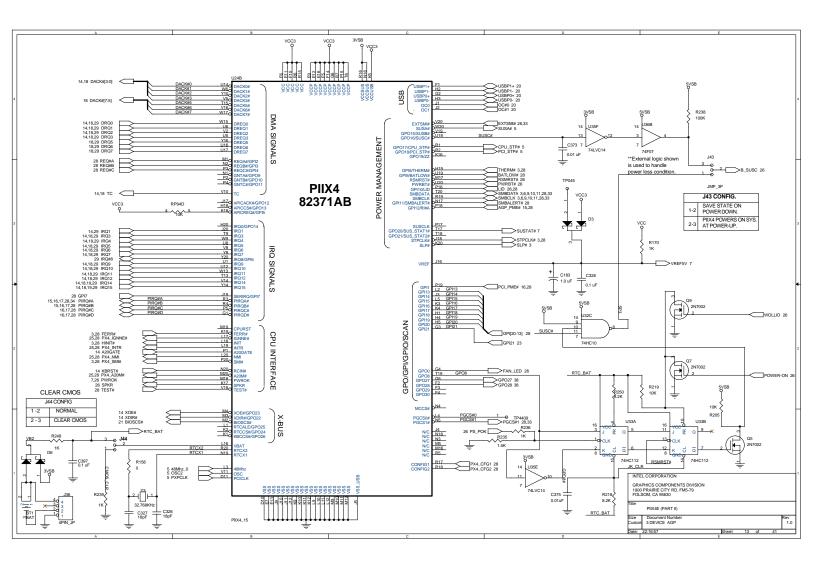

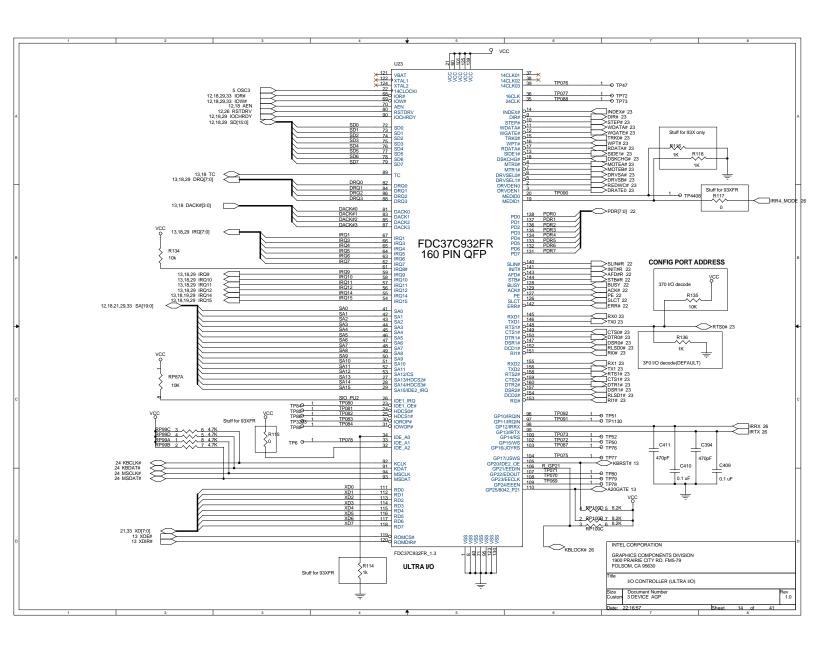

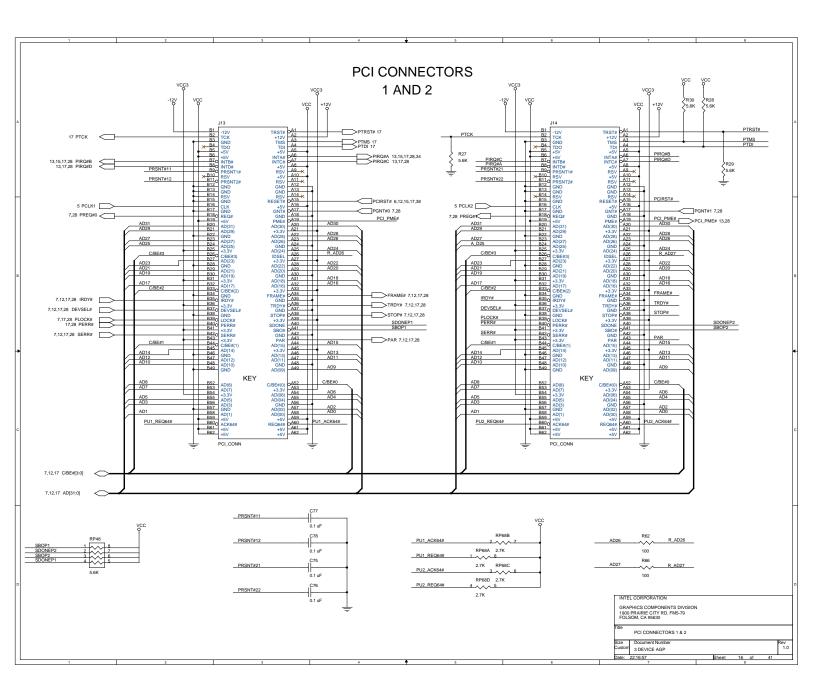

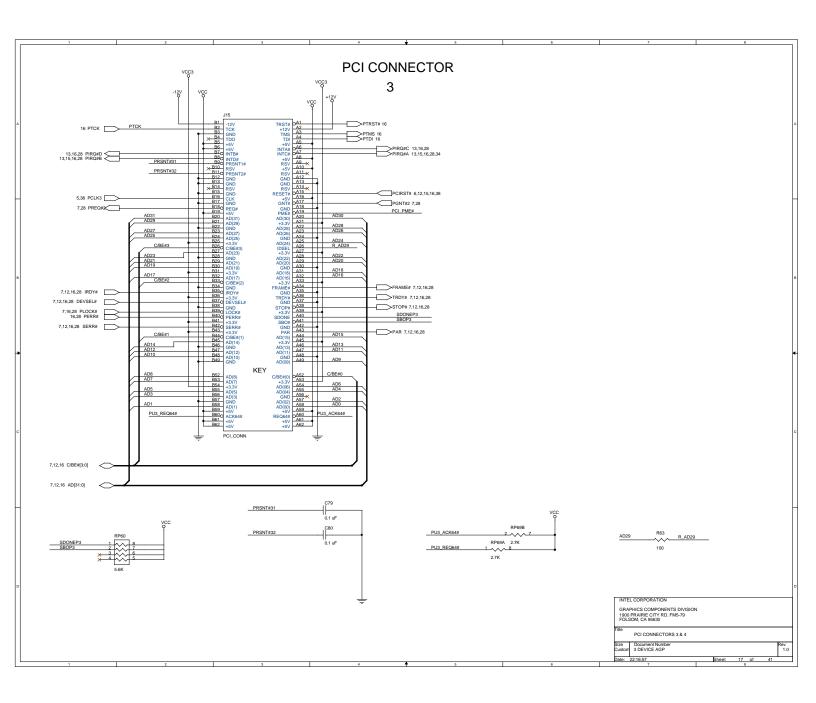

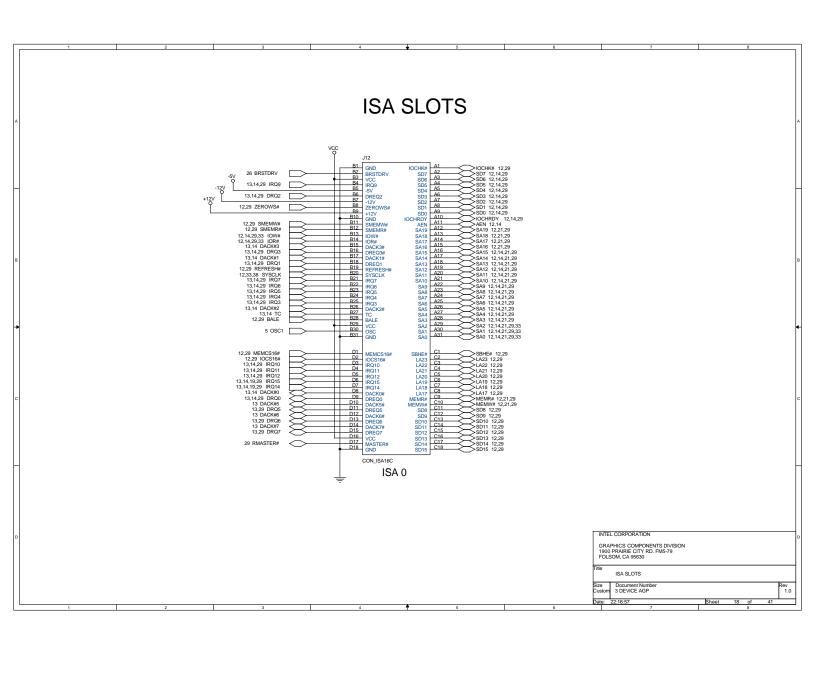

| 3 | 3 Devi                      | ce AGP    | MotherBoa          | ard Design                                  | 3-1  |  |

|---|-----------------------------|-----------|--------------------|---------------------------------------------|------|--|

|   | 3.1                         | Introdu   | iction             |                                             |      |  |

|   |                             | 3.1.1     |                    | V                                           |      |  |

|   |                             | 3.1.2     | About Th           | nis Chapter                                 | 3-2  |  |

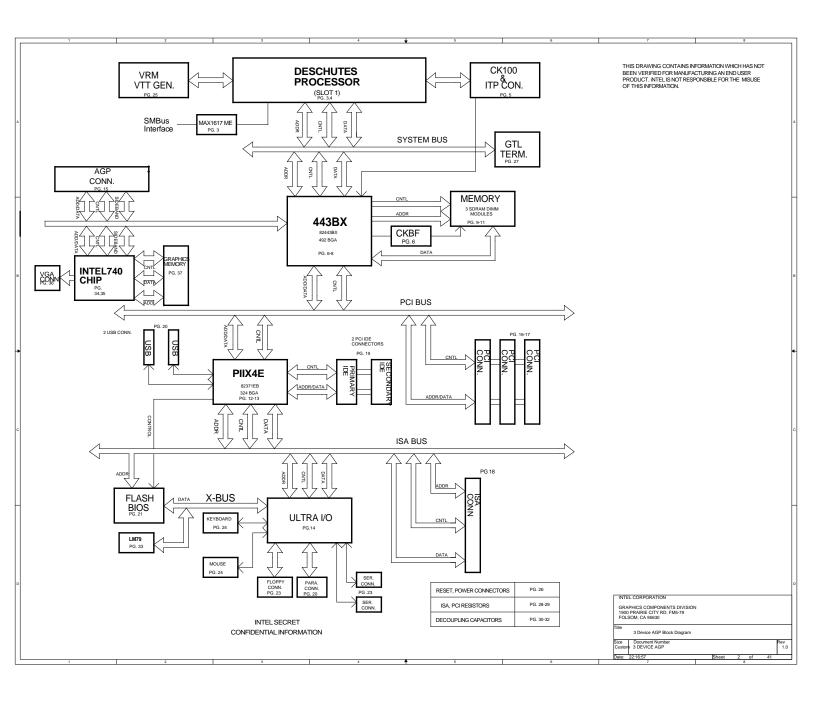

|   |                             | 3.1.3     |                    | agram                                       |      |  |

|   |                             | 3.1.4     |                    | ntation Issues                              |      |  |

|   |                             |           | 3.1.4.1            | Disabling A Master Device                   |      |  |

|   |                             |           | 3.1.4.2            | Low Power Logic Implementation              |      |  |

|   |                             |           | 3.1.4.3            | GPO27# and GPO28# Signal Duration           | 3-5  |  |

|   |                             | 3.1.5     | State Dia          | agrams                                      | 3-5  |  |

|   |                             |           | 3.1.5.1            | Signal Quality and Timing Issues            | 3-6  |  |

|   |                             |           | 3.1.5.2            | Strobe Edge Quality Issues                  | 3-7  |  |

|   |                             |           | 3.1.5.3            | Clock Issues                                |      |  |

|   |                             | 3.1.6     |                    | Recommendations                             | 3-9  |  |

|   |                             |           | 3.1.6.1            | Voltage Definitions                         | 3-9  |  |

|   |                             |           | 3.1.6.2            | General Design Recommendation               |      |  |

|   | 3.2                         |           |                    | otherboard Layout and Routing Guidelines    |      |  |

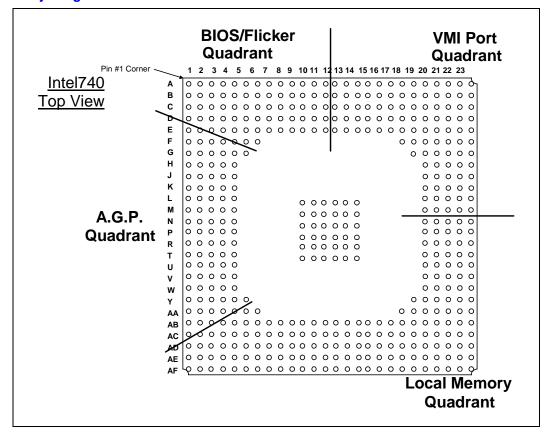

|   |                             | 3.2.1     |                    | adrant Assignment                           |      |  |

|   |                             | 3.2.2     |                    | escription                                  |      |  |

|   |                             | 3.2.3     |                    | GP Design Guidelines                        |      |  |

|   |                             |           | 3.2.3.1            | Layout and Routing                          | 3-12 |  |

|   |                             |           | 3.2.3.2            | Data and strobe definitions                 |      |  |

|   |                             |           | 3.2.3.3            | Assumptions for Board Design Guidelines     | 3-14 |  |

|   |                             |           | 3.2.3.4            | Add-in Card guideline assumptions:          | 3-14 |  |

|   |                             |           | 3.2.3.5            | Motherboard Guideline Assumptions           | 3-14 |  |

|   |                             |           | 3.2.3.6<br>3.2.3.7 | 3-Load AGP Topology Overall Solution Space  | 3-10 |  |

|   |                             | 2 2 4     |                    | ™ Graphics Accelerator Memory Layout and    | 3-10 |  |

|   |                             | 3.2.4     | Pouting (          | Guidelines                                  | 2 10 |  |

|   |                             |           | 3.2.4.1            | 3 Device AGP Intel740™ Graphics Accelerator | 3-10 |  |

|   |                             |           | 3.2.4.1            | Memory Configurations                       | 3-21 |  |

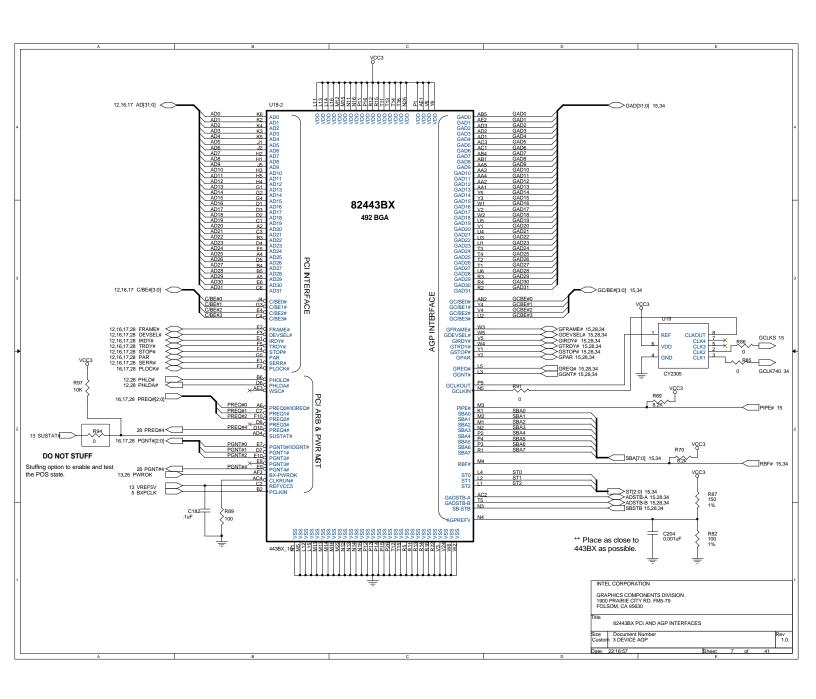

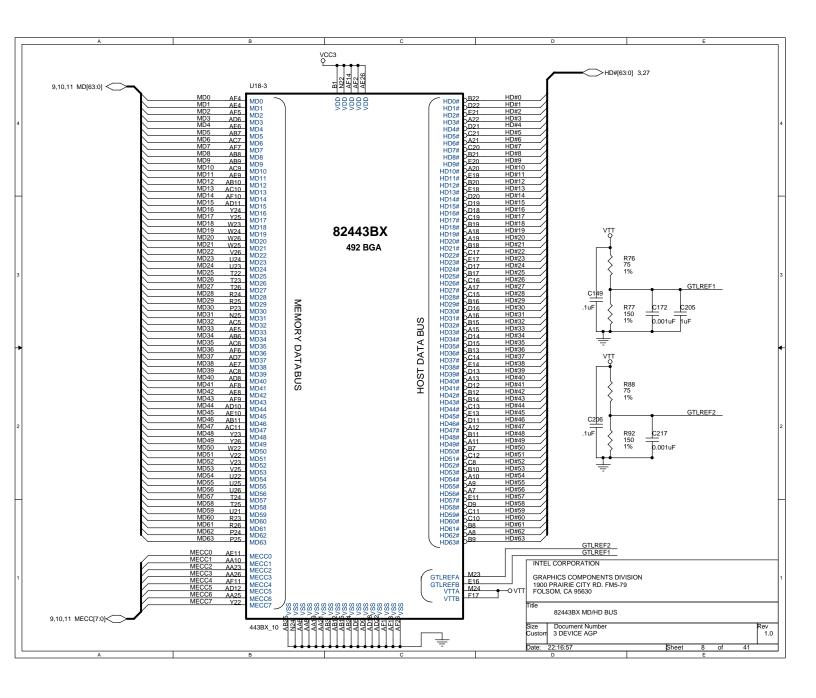

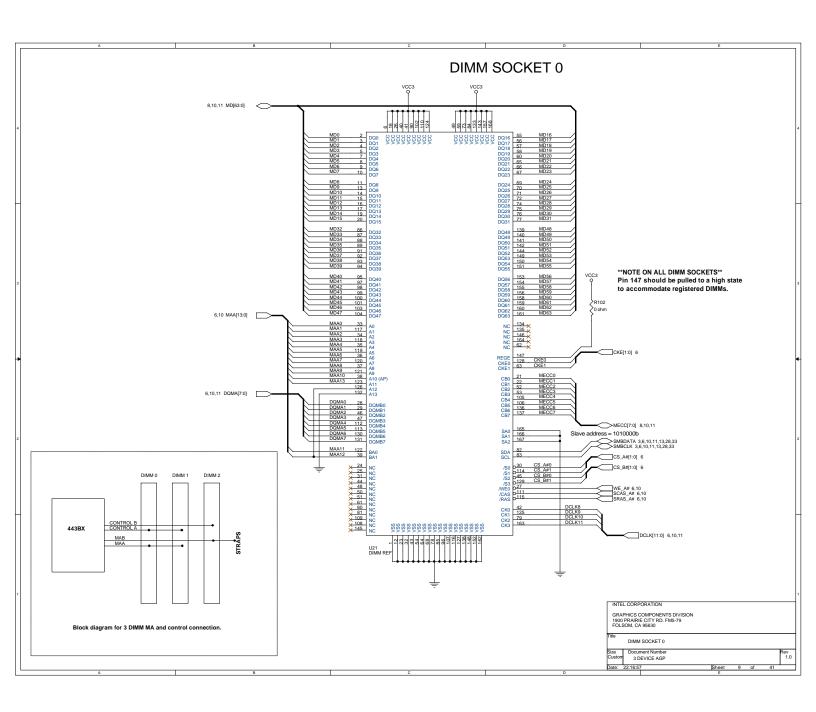

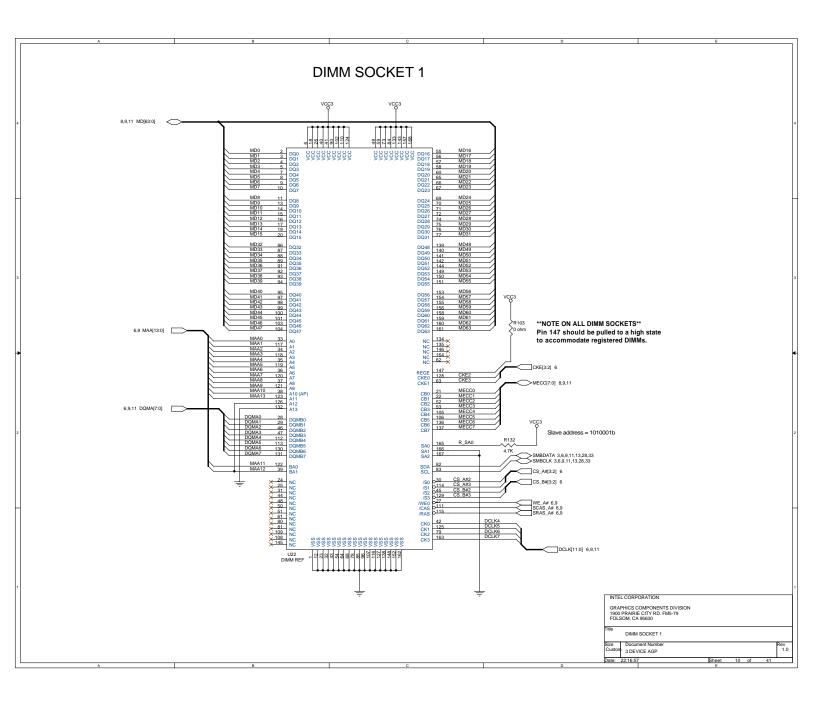

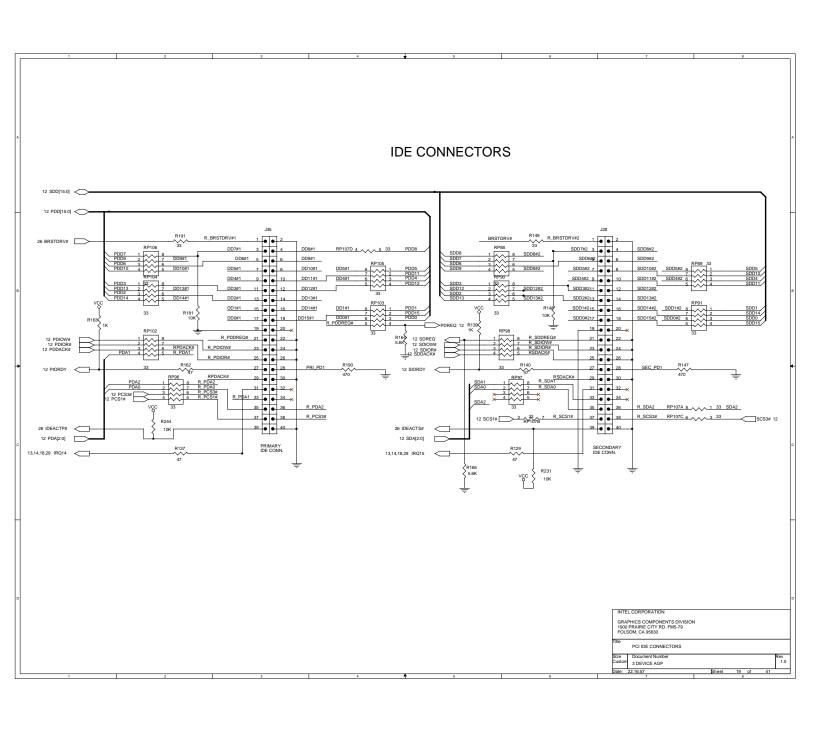

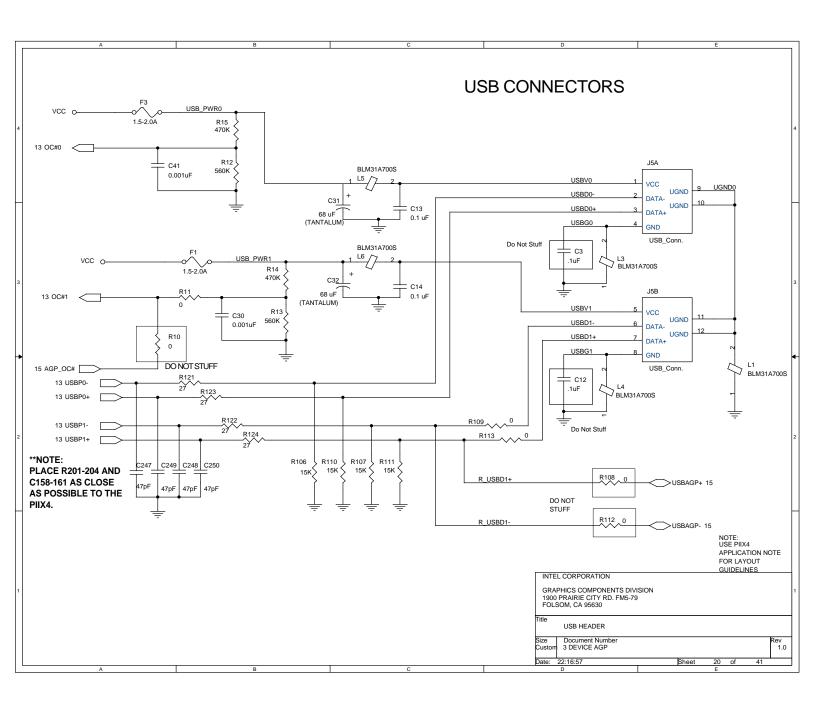

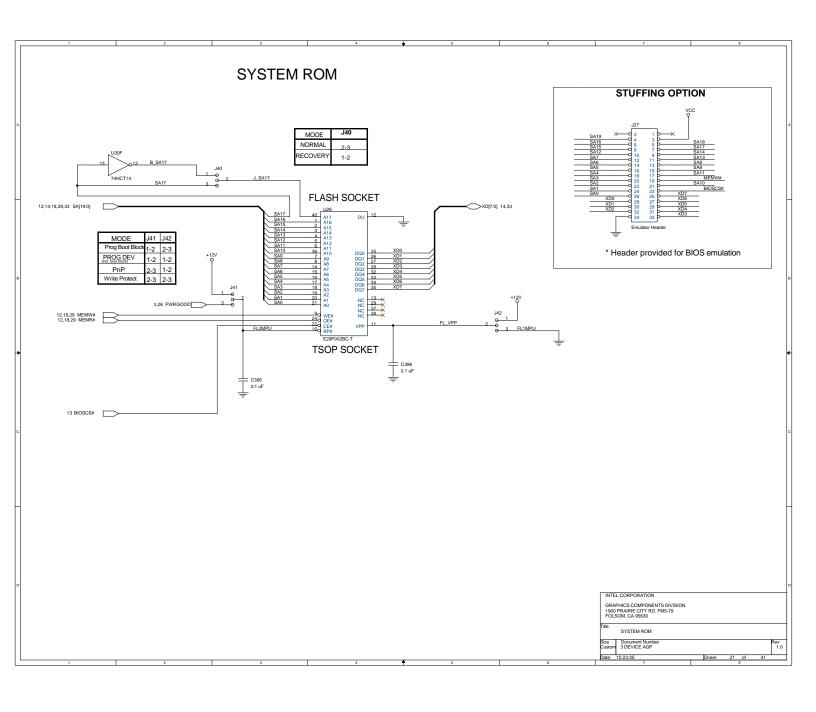

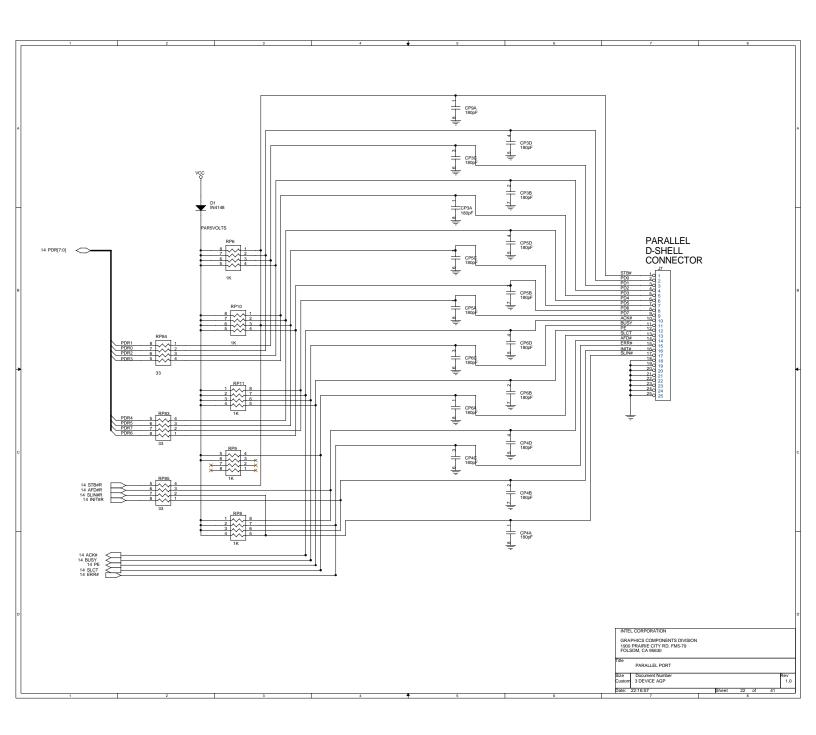

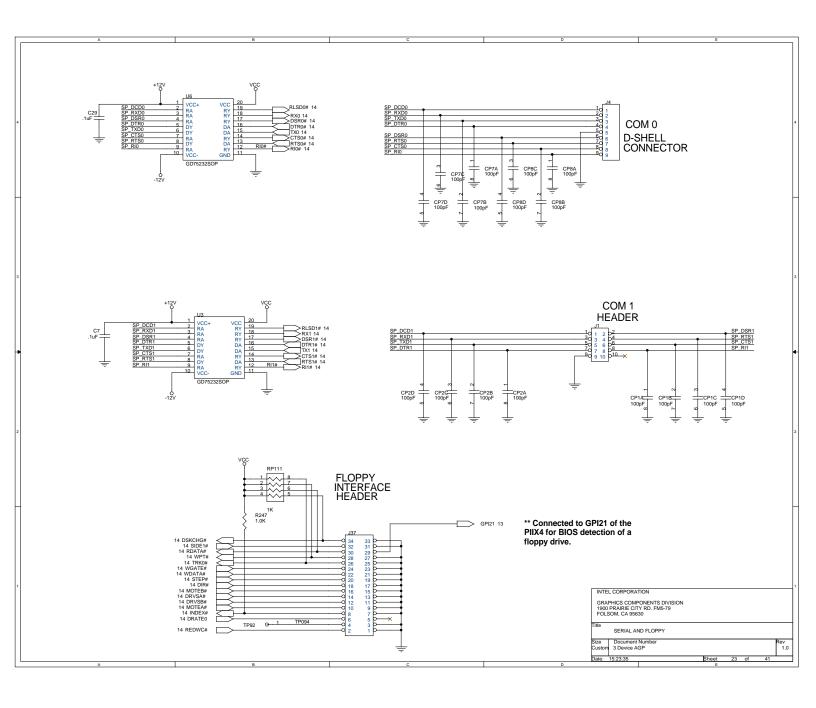

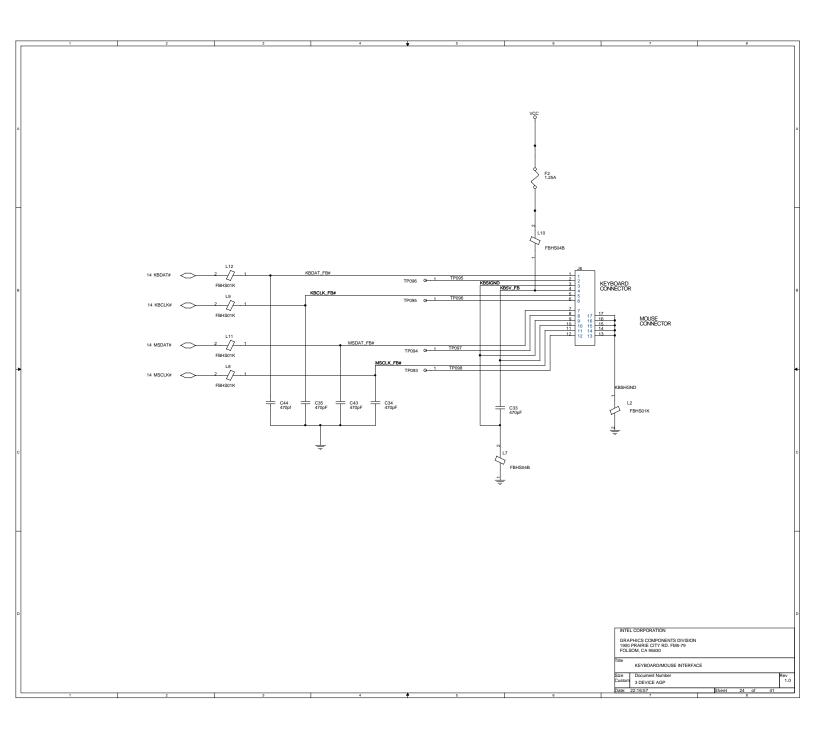

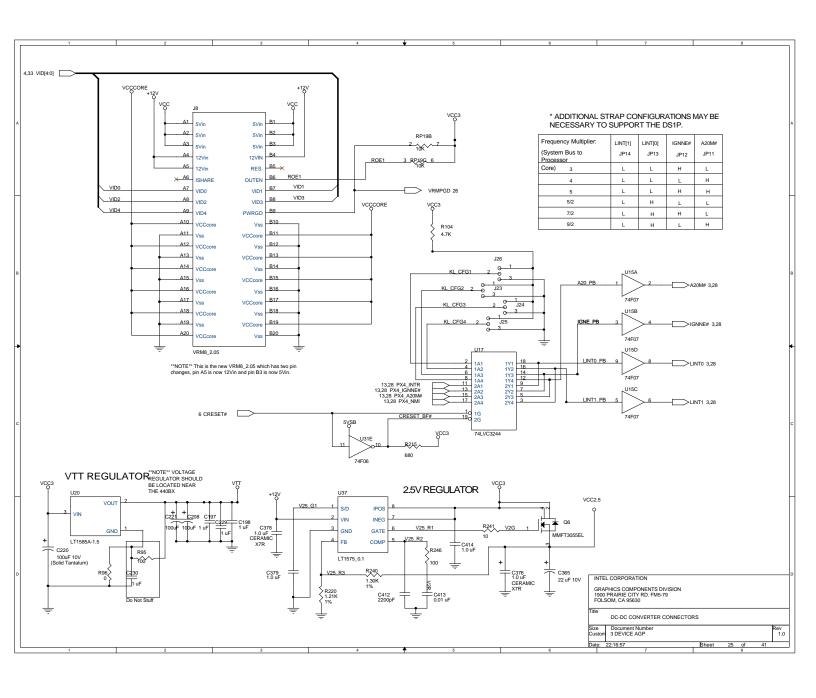

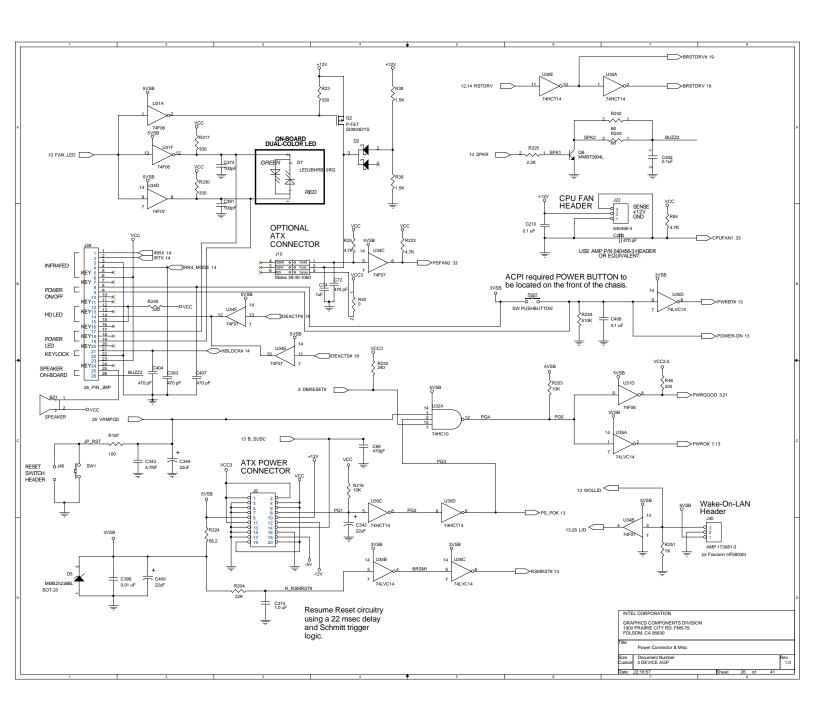

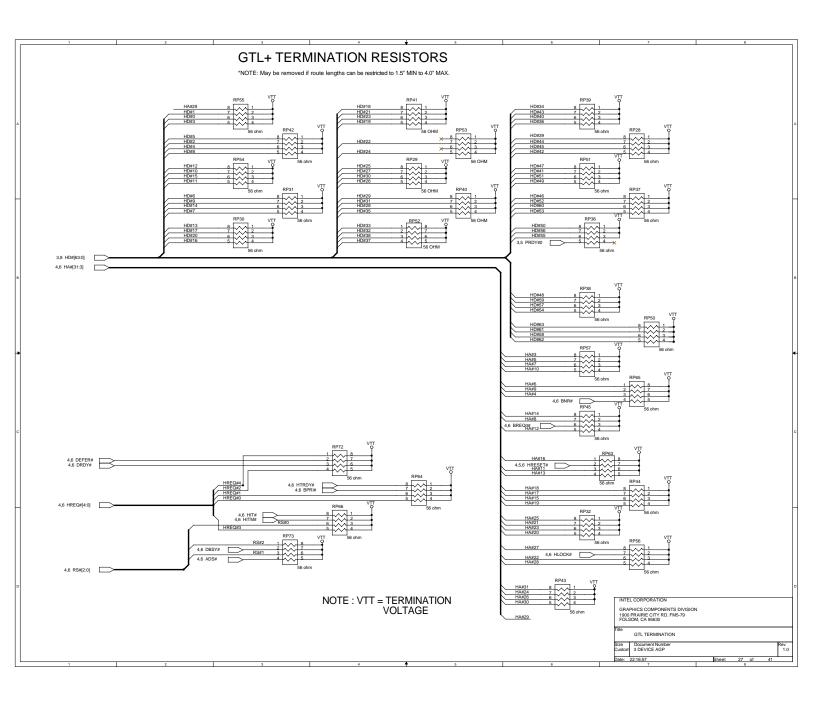

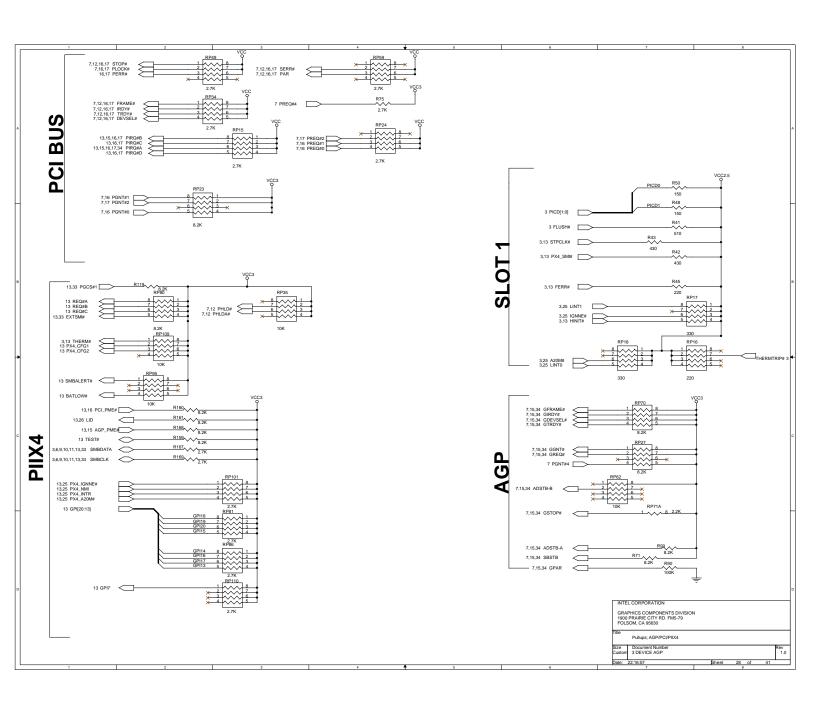

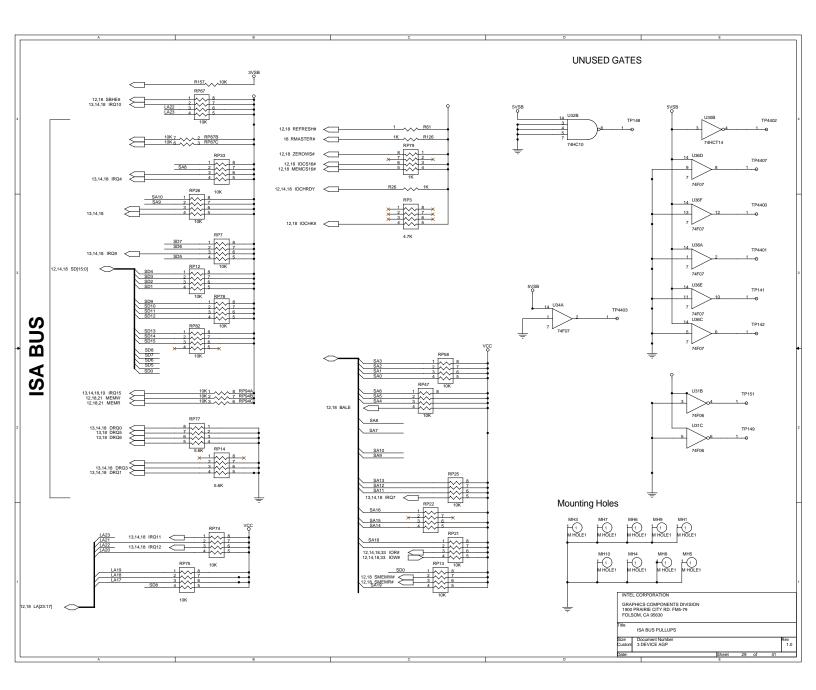

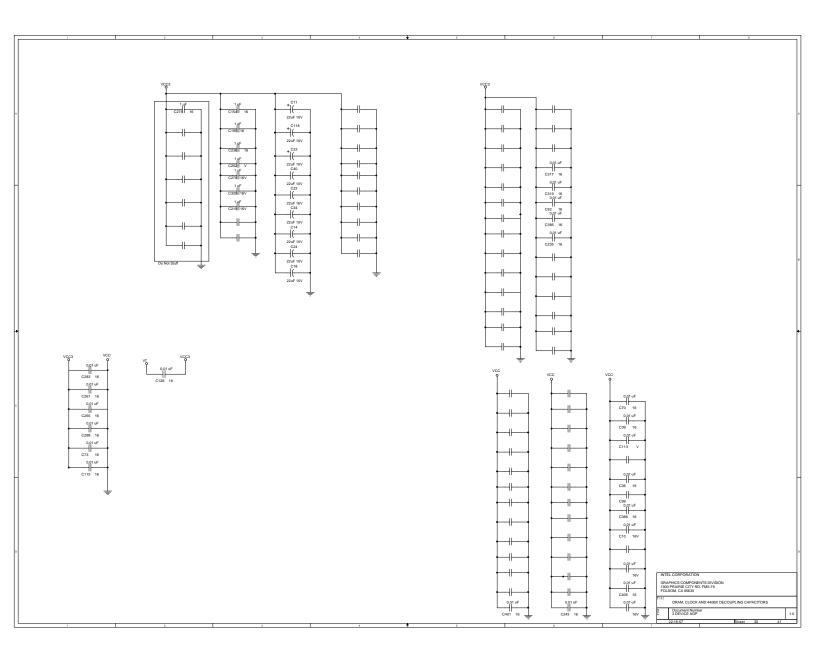

|   | 3.3                         | 3 Devi    | CO AGP M           | otherboard Reference Design Schematics      |      |  |

|   |                             |           |                    | -                                           |      |  |

| 4 | Therma                      | al Consi  | derations          |                                             | 4-1  |  |

| 5 | Mecha                       | nical Inf | ormation           |                                             | 5-1  |  |

|   | 5.1                         | Board     | Dimension          | ns                                          | 5-1  |  |

|   | 5.2                         |           |                    | le Pattern                                  |      |  |

|   | 5.3                         |           |                    | ement                                       |      |  |

|   | 5.4                         |           |                    | nnector                                     |      |  |

|   | 5.5                         |           |                    | illector                                    |      |  |

|   | 5.6                         |           |                    | ons                                         |      |  |

| 0 |                             |           |                    |                                             |      |  |

| 6 |                             | •         |                    |                                             |      |  |

|   | 6.1                         | -         | -                  | or                                          |      |  |

|   | 6.2                         |           |                    | r                                           |      |  |

|   | 6.3                         |           |                    |                                             |      |  |

|   | 6.4                         |           |                    | ts                                          |      |  |

|   | 6.5 Video Encoders/Decoders |           |                    |                                             |      |  |

|   | 6.6                         |           | •                  | ards                                        |      |  |

|   | 6.7                         |           |                    |                                             | 6-2  |  |

| Α | Applica                     | ation No  | tes                |                                             |      |  |

| В | Refere                      | nce Info  | rmation            |                                             |      |  |

# intط

# **Figures**

| 2-1  | Example of Power Plane Separation ("fencing")                                                                              | 2-4  |

|------|----------------------------------------------------------------------------------------------------------------------------|------|

| 2-2  | Example of Power Plane Stitching                                                                                           | 2-4  |

| 2-3  | Major Signal Sections                                                                                                      | 2-5  |

| 2-4  | Example ATX Layout                                                                                                         | 2-6  |

| 2-5  | Four Layer Board Stack-up                                                                                                  |      |

| 2-6  | Metal Defined land dimensions                                                                                              | 2-8  |

| 2-7  | BGA Trace                                                                                                                  | 2-8  |

| 2-8  | Dogbone Via Pattern                                                                                                        |      |

| 2-9  | Suggested VCC Planes for the Intel740™ Graphics Accelerator                                                                | 2-10 |

| 2-10 | Intel740™ Graphics Accelerator Decoupling                                                                                  |      |

| 2-11 | Intel740™ Graphics Accelerator BGA Routing Example                                                                         |      |

| 2-12 | Layout Dimensions (MA[11:0])                                                                                               |      |

| 2-13 | Layout Dimensions (MD[63:0], DQM[7:0])                                                                                     |      |

| 2-14 | Layout Dimensions (WEA#, SRASA#, SCASA#, CSA1#, CSB0#)                                                                     | 2-15 |

| 2-15 | Layout Dimensions (WEB#, SRASB#, SCASB#, CSA0#)                                                                            |      |

| 2-16 | Memory Layout Dimensions (TCLK0)                                                                                           | 2-16 |

| 2-17 | Memory Layout Dimensions (TCLK1)                                                                                           |      |

| 2-18 | Memory Layout Dimensions (RCLK and OCLK to RCLK)                                                                           | 2-17 |

| 2-19 | 2/4 MB Local Memory Connection (64-bit data path)                                                                          |      |

| 2-20 | 4/8 MB Local Memory Connection (64-bit data path)                                                                          | 2-18 |

| 2-21 | 8 MB Local Memory Connection (64-bit data path)                                                                            | 2-19 |

| 2-22 | Layout Dimensions, Digital TV Bus                                                                                          |      |

| 2-23 | 512Kx32 and 256Kx32 Pinout Compatibility                                                                                   |      |

| 2-24 | 1M X 16 Pinout Compatibility                                                                                               | 2-24 |

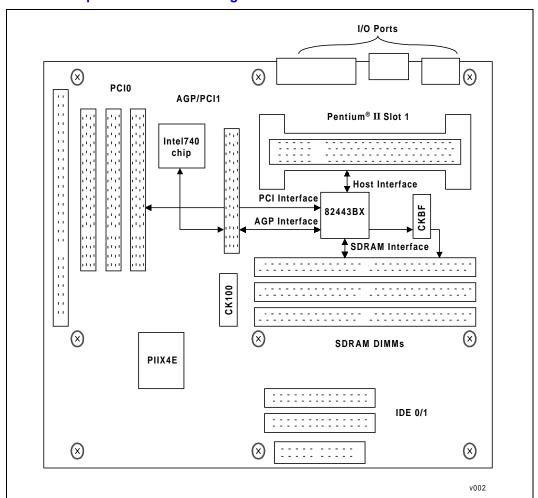

| 3-1  | Pentium <sup>®</sup> II Processor / Intel <sup>®</sup> 440BX AGPset/Intel 740 Graphics<br>Accelerator System Block Diagram | 3-3  |

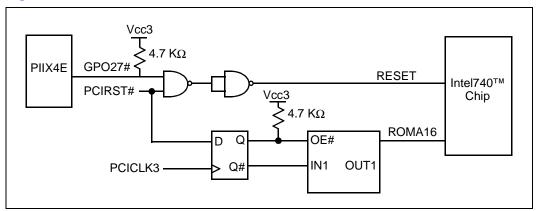

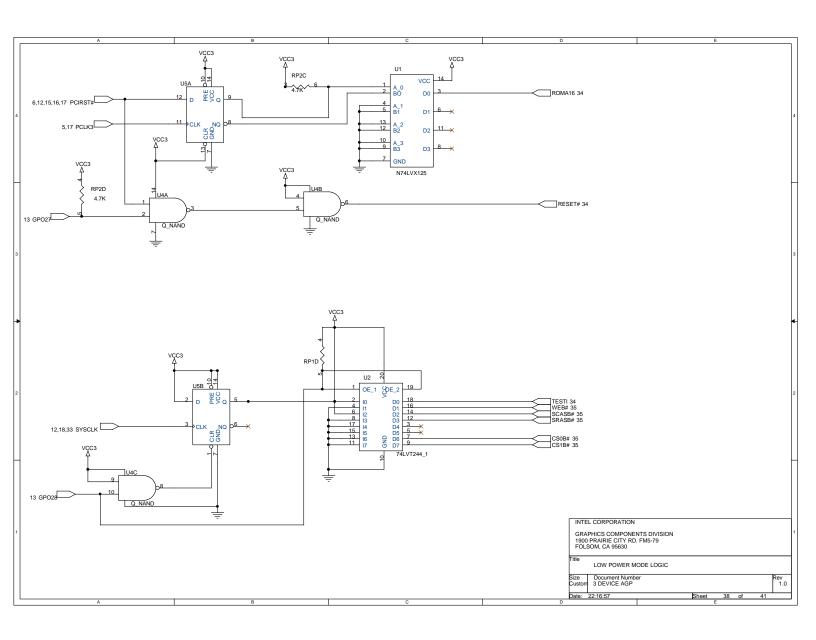

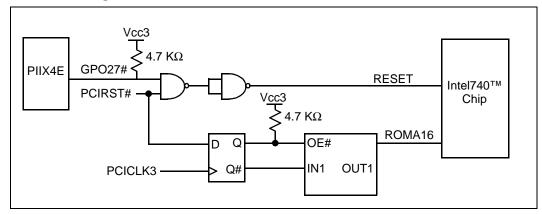

| 3-2  | The Schematic Diagram for GPO27#, PCIRST# (System Reset), RESET#, ROMA16 Signals                                           | 3-4  |

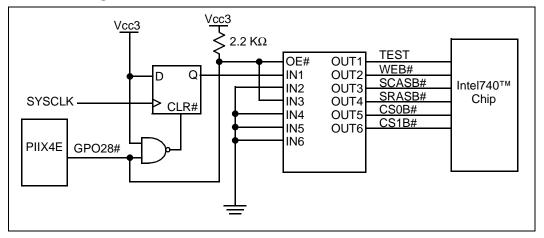

| 3-3  | The Schematic Diagram for the WEB#, SCASB#, SRASB#, CS0B#, CS1B# and TEST                                                  |      |

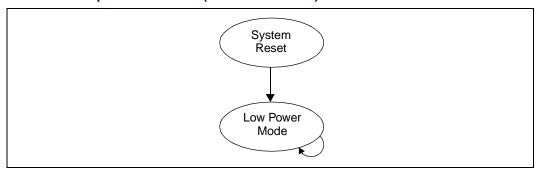

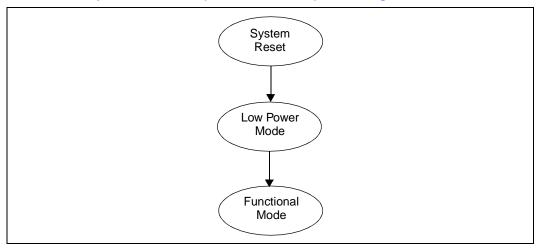

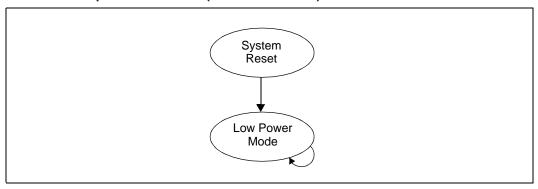

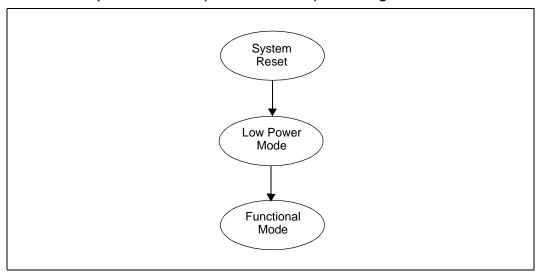

| 3-4  | Intel740 <sup>™</sup> Graphics Controller (On Board Device) Remains in Low Power Mode                                      |      |

| 3-5  | Intel740™ Graphics Controller (On Board Device) State Diagram                                                              |      |

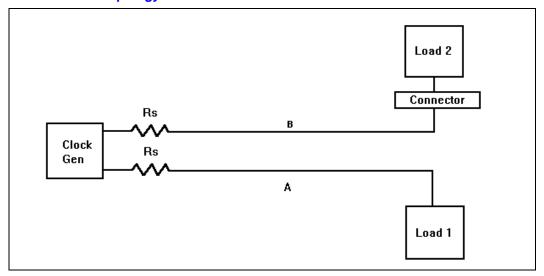

| 3-6  | Point-to-Point Topology                                                                                                    |      |

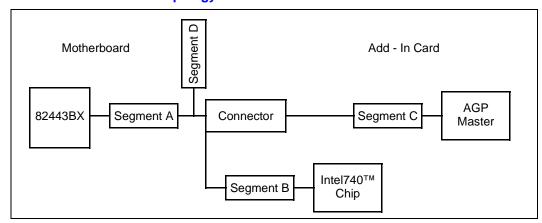

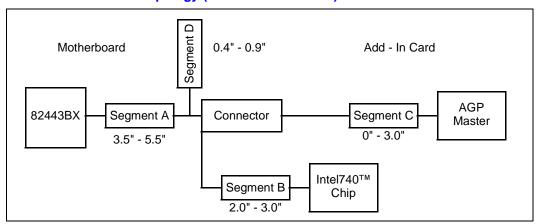

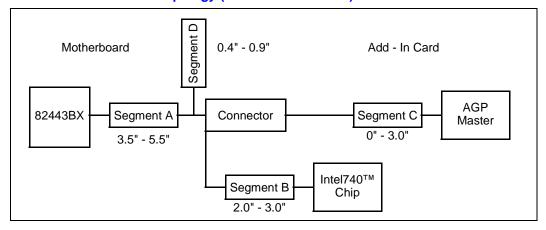

| 3-7  | Major Signal Sections                                                                                                      |      |

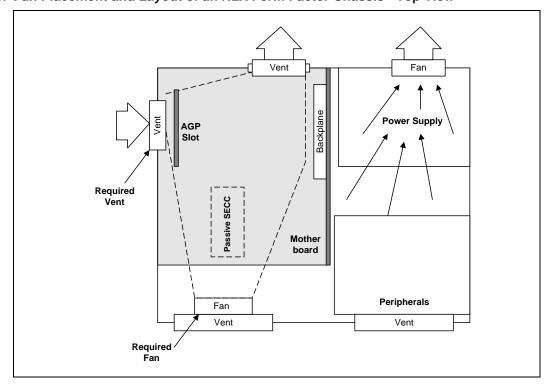

| 3-8  | Example ATX Placement for a UP Pentium® II Processor /                                                                     |      |

|      | Intel® 440BX AGPset / Intel 740 Graphics Accelerator Design                                                                | 3-11 |

| 3-9  | Four Layer Board Stack-up                                                                                                  |      |

| 3-10 | Point-to-Point Topology                                                                                                    |      |

| 3-11 | 3 Device Data Load Topology                                                                                                |      |

| 3-12 | 3 Device Strobe Load Topology                                                                                              |      |

| 3-13 | 3 Device Data Load Topology (Solution 1 is Shown)                                                                          |      |

| 3-14 | 3 Device Strobe Load Topology (Solution 1 is shown)                                                                        |      |

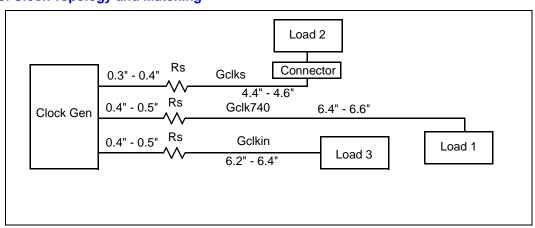

| 3-15 | Clock Topology and Matching                                                                                                |      |

| 3-16 | Layout Dimensions (MA[11:0])                                                                                               |      |

| 3-17 | Layout Dimensions (MD[63:0], DQM[7:0])                                                                                     |      |

| 3-18 | Layout Dimensions (WEA#, SRASA#, SCASA#, CSA0#)                                                                            |      |

| 3-19 | Memory Layout Dimensions (TCLK1)                                                                                           | 3-20 |

| 3-20 | Memory Layout Dimensions (RCLK and OCLK to RCLK)                                                                           | 3-21 |

# اntط

| 3-21 | 2/4 MB Local Memory Connection (64-bit data path)   | 3-21 |

|------|-----------------------------------------------------|------|

| 3-22 | 512Kx32 and 256Kx32 Pinout Compatibility            | 3-26 |

| 3-23 | 1M X 16 Pinout Compatibility                        | 3-26 |

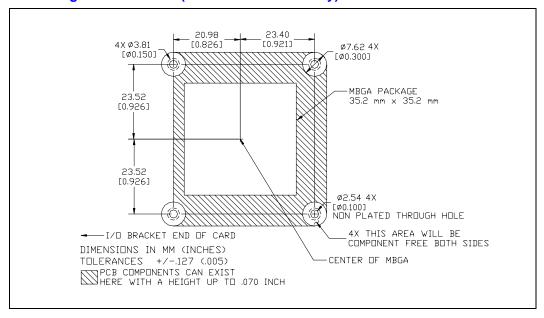

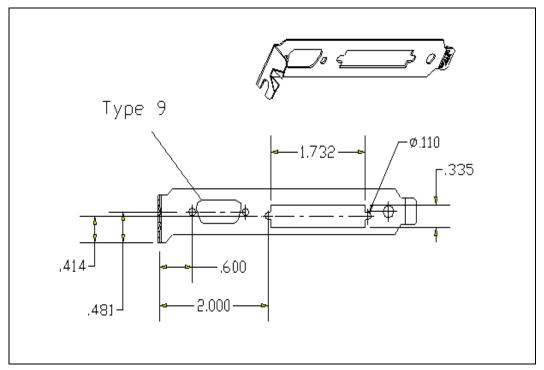

| 5-1  | Mounting Hole Locations (Fan/Heatsink Assembly)     | 5-1  |

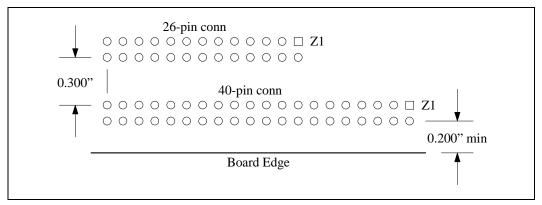

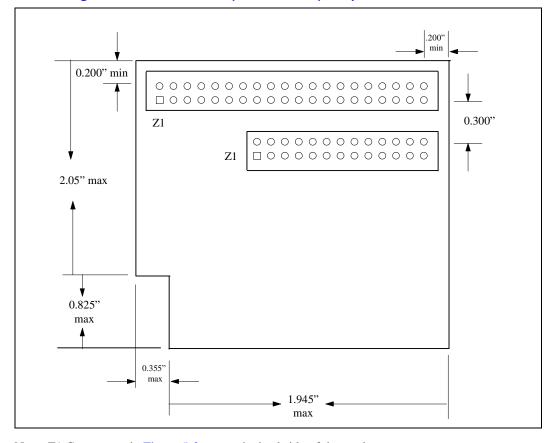

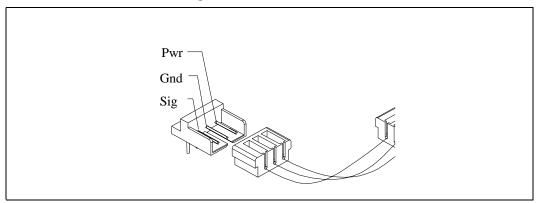

| 5-2  | VMI Header Placement                                | 5-2  |

| 5-3  | DVD Daughter Card Dimensions (ATX and NLX)—Top Side | 5-2  |

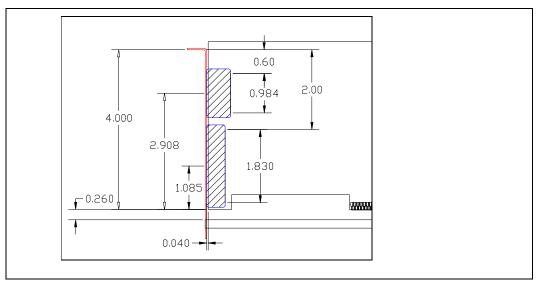

| 5-4  | 50 Pin Video Connector Schematic                    | 5-3  |

| 5-5  | Recommended Bracket Placement                       | 5-4  |

| 5-6  | Recommended Bracket Cutout                          | 5-4  |

|      |                                                     |      |

# intel®

# **Tables**

| 2-1  | Mix and Match Options For Intel740™ Graphics Accelerator Card | 2-2  |

|------|---------------------------------------------------------------|------|

| 2-2  | Intel740™ Graphics Accelerator Power Supplies                 | 2-3  |

| 2-3  | Bt829B GND and AGND Pins                                      | 2-12 |

| 2-4  | Bt829B VCC and AVCC Pins                                      | 2-12 |

| 2-5  | Bt869 Digital and Analog Power Pins                           | 2-13 |

| 2-6  | AGP Signal Lengths                                            |      |

| 2-7  | Strobes and Corresponding Signal Groups                       | 2-13 |

| 2-8  | Supported Memory Options (Other Memory Options Are            |      |

|      | Not Supported)                                                | 2-14 |

| 2-9  | Memory Layout Restrictions (See Figure 2-12 and Figure 2-13)  | 2-14 |

| 2-10 | Memory Layout Restrictions (See Figure 2-14 and Figure 2-15)  | 2-15 |

| 2-11 | Memory Layout Restrictions (See Figure 2-16 and Figure 2-17)  | 2-16 |

| 2-12 | TV Out/ROMA Trace Lengths (See Figure 2-22)                   | 2-20 |

| 2-13 | GPIO Functions                                                | 2-21 |

| 3-1  | State of Signals to be Driven After System Reset but at Least |      |

|      | One Clock Prior to Asserting TEST                             |      |

| 3-2  | Signal Duration of the GPO Signals from PIIX4                 | 3-5  |

| 3-3  | Data and Associated Strobe                                    |      |

| 3-4  | Data Signal and Strobe Guideline Assumptions                  | 3-14 |

| 3-5  | Control and Clock Signal Guideline Assumptions                | 3-14 |

| 3-6  | Data signal and strobe requirements                           | 3-14 |

| 3-7  | Control Signal Line Length Requirements                       | 3-15 |

| 3-8  | Strobe and Data Segment Solution Space                        | 3-16 |

| 3-9  | Clock Segment Solution Space                                  | 3-18 |

| 3-10 | Supported Memory Options (Other Memory Options Are            |      |

|      | Not Supported)                                                |      |

| 3-11 | Memory Layout Restrictions (See Figure 3-16 and Figure 3-17)  | 3-19 |

| 3-12 | Memory Layout Restrictions (See Table 3-16 and Table 3-17)    | 3-19 |

| 3-14 | Memory Layout Restrictions (See Figure 3-19)                  | 3-20 |

| 3-13 | Memory Layout Restrictions (See Figure 3-19)                  | 3-20 |

| 4-1  | Thermal Design Considerations Chart                           | 4-1  |

|      |                                                               |      |

# **Revision History**

| Date | Revision | Description                                                                                                                                                                                                                                                  |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2/98 | -001     | Initial Release.                                                                                                                                                                                                                                             |

| 4/98 | -002     | Part 2: Added Figure 2-2; added "Note" verbiage in 2.14. Part 3: Added verbiage to 3.3.5; Modified Figures 3-14, 3-15, 3-16, 3-19; Modified Table 3-10. Part 5: Modified Figure 5-6.                                                                         |

| 7/98 | -003     | Restructured document and added a motherboard design: Chapter 2 contains the Addin Card design. This chapter combines revision 2 Chapters 1, 2, 3, and Appendix A. Only re-organizaiton; the information is the same. Chapter 2 adds the motherboard design. |

intel®

1

# Introduction

# Introduction

1

This document provides a complete package of design information for the Intel740<sup>TM</sup> Graphics Accelerator. There are two design discussed:

- ATX Addin Card Design (Chapter 2 provides design considerations, layout and routing guidelines, and schematic diagrams)

- Motherboard Design (Chapter 3 provides design considerations, layout and routing guidelines, and schematic diagrams)

The purpose of the reference design is to provide a comprehensive design encompassing every Intel740<sup>TM</sup> graphics accelerator interface. The designer of another board may then modify this design as needed since the basic hook-up will remain the same.

For the latest Intel740<sup>TM</sup> graphics accelerator information, please visit Intel's website at:

http://developer.intel.com/design/graphics/740.htm

# 1.1 About This Design Guide

This design guide is intended for hardware designers who are experienced with PC architectures and board design. The design guide assumes that the designer has a working knowledge of the vocabulary and practices of PC hardware design.

- This chapter introduces the designer to the organization and purpose of this design guide and provides a list of references and related documents.

- Chapter 2, "Addin Card Design"—This chapter provides a detailed set of Intel740<sup>TM</sup> graphics accelerator design information for ATX and NLX graphics cards. The basis of the design information is a reference ATX card design. Schematics for the reference design are provided at the end of the chapter.

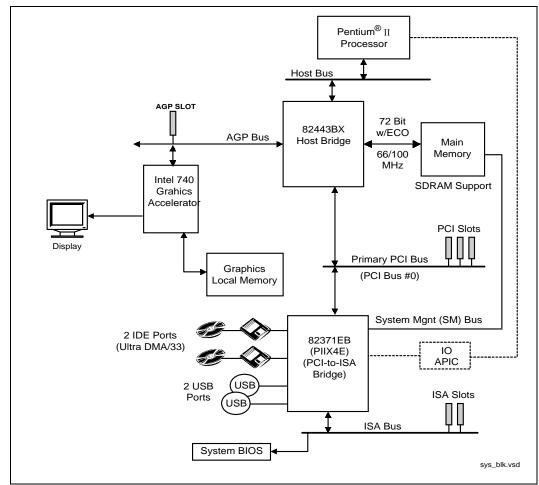

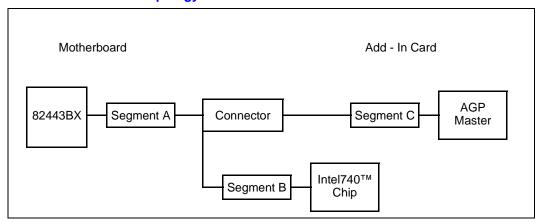

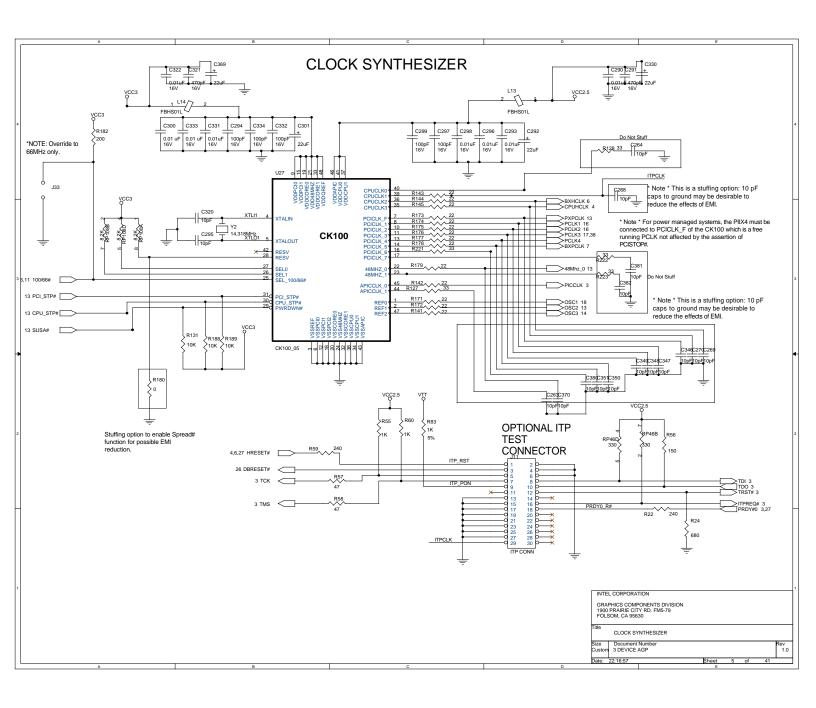

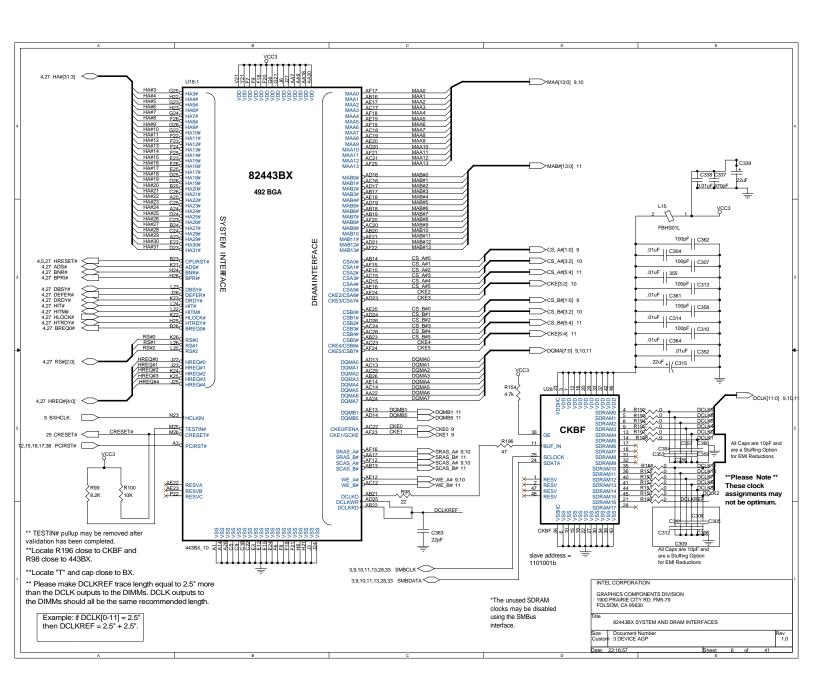

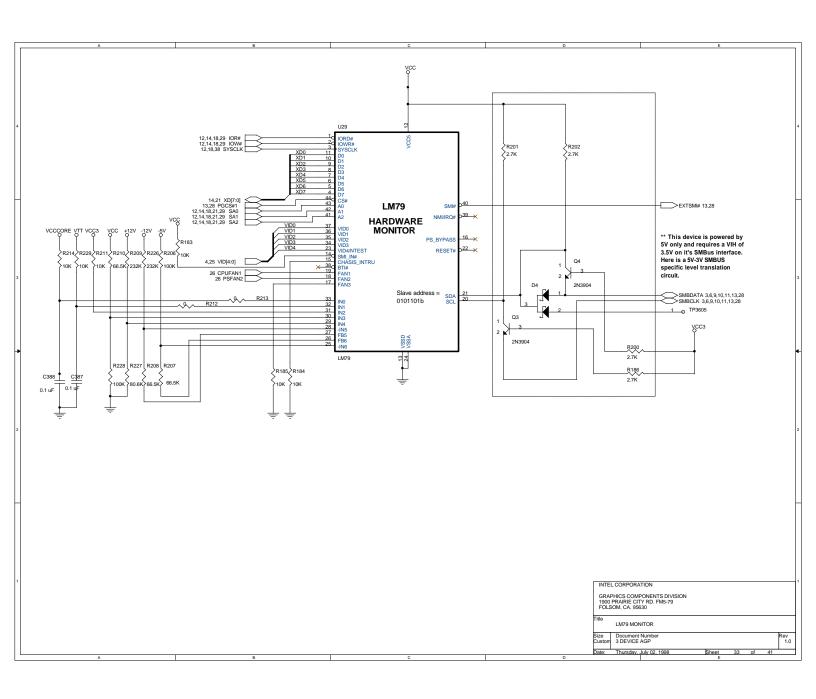

- Chapter 3, "3 Device AGP Motherboard Design"—This chapter provides design guidelines for developing a motherboard based on the Pentium II® processor, Intel® 440BX AGPset, and the Intel740<sup>TM</sup> graphics accelerator. The main focus of this chapter is the guidelines for developing a 3-point AGP solution with the Intel740 graphics accelerator and provides a detailed set of design information for a 3-point AGP reference design (DS1P/440BX/I740). Schematics for the reference design are provided at the end of the chapter.

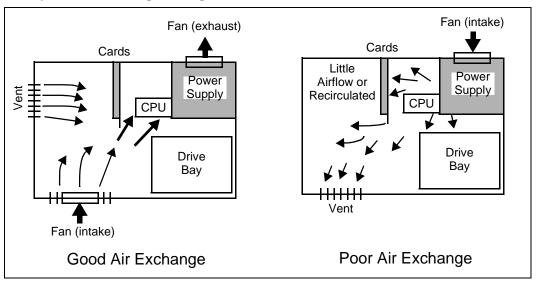

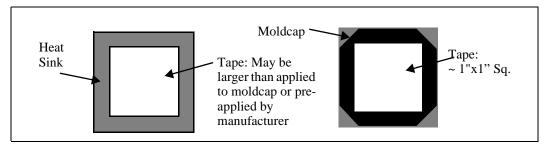

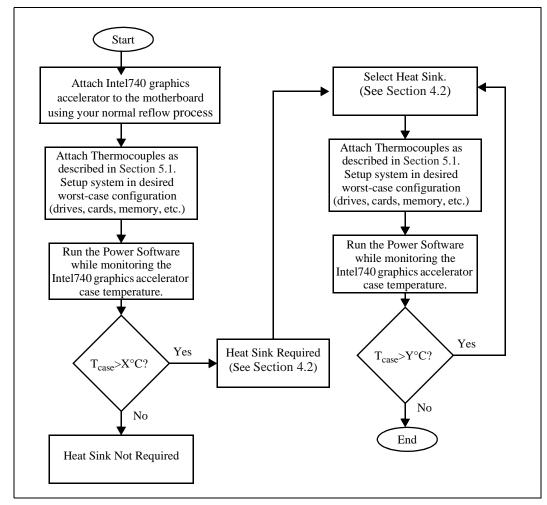

- Chapter 4, "Thermal Considerations"—This chapter introduces the topic of thermal considerations. See *Application Note 653* in Appendix A for a comprehensive description of thermal considerations.

- Chapter 5, "Mechanical Information"— This chapter provides mechanical information on Fan/Heatsink, VMI Header Placement, Video Connector, brackets, and NLX considerations.

- Chapter 6, "Third Party Vendor Information"— This section includes information regarding various third-party vendors who provide products to support the Intel 440BX AGPset and the Intel740 graphics accelerator.

- Appendix A, "Application Notes"—This appendix contains Application Note 653, Thermal Design Considerations. The application note provides a comprehensive guide to thermal design

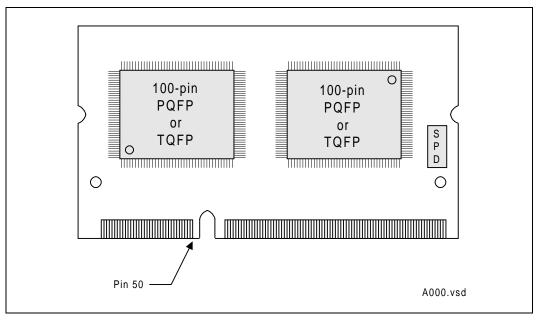

- Appendix B, "Reference Information"—This appendix provides reference information for designing with the Intel740 graphics accelerator. The appendix contains information on

SDRAM/SGRAM Graphics SO-DIMM Modules. The appendix also contains information on PC SGRAM specifications.

# 1.2 References

- Intel740<sup>TM</sup> Graphics Accelerator Datasheet: Contact your field sales representative (Literature order #290618) or visit the Intel740<sup>TM</sup> Graphics Accelerator WEB page at: http://developer.intel.com/design/graphics/740.htm

- Accelerated Graphics Port Interface Specification Rev 1.0: Contact www.agpforum.com

- Bt829A/Bt827A/Bt825A VideoStreamII Decoders Oct. 1996: Contact Rockwell\* Semiconductor

- Bt868/869 Flicker-Free Video Encoder with Ultrascale<sup>TM</sup> Technology: Contact Rockwell\* Semiconductor

- VMI 1.4 Interface Specification: Contact SGS Thompson Microelectronics

- PC '98: Contact www.microsoft.com/hwdev

- PC SGRAM Specification: See Appendix B

- SO-DIMM Module Specification: See Appendix B

- Intel740<sup>TM</sup> Graphics Accelerator Application Note 653 Thermal Design Considerations: See Appendix A

- Intel 440BX AGPset Design Guide. Contact your field sales representative (Literature order #290634). or visit the 440BX AGPSet WEB page at: http://developer.intel.com/design/pcisets/designex/290634.htm

intel<sub>®</sub>

2

Intel740<sup>TM</sup> Graphics Accelerator Addin Card Design

# Addin Card Design

2

This chapter provides a complete package of design information for the Intel740<sup>TM</sup> graphics accelerator. Usage of the Intel740<sup>TM</sup> graphics accelerator on an ATX and NLX graphics card is discussed. The basis of this document is a reference ATX card.

# 2.1 Introduction

The reference design card described in this document contains the following features.

- ATX Form Factor

- Memory

- 100 MHz SDRAM or SGRAM

- SO-DIMM Memory Upgrade Socket

- 2,4 MB Solder-Down Option

- BIOS

- Support for Flash or ROM

- Capable of Supporting up to 256KB

- Monitor

- Hardware Support for DDC 2B

- Video

- Capture

- Bi-Directional VMI Video Port for DVD Hardware

- CCIR 601 8/16-bit Video Capture Port

- NTSC, PAL, and SECAM Inputs Accepted

- Intercast Capable

- Video-Conferencing Capable

- Output

- NTSC or PAL TV Output

- Flicker Free TV Output

- Overscan Compensation

- 50-Pin Video Connector

- S-Video In/Out

- Composite In/Out

- TV Tuner

- I<sup>2</sup>C Programmability

Table 2-1 lists the various functions capable of being supported by the reference card design. This table describes which component is necessary for a specific feature. For hookup information, the corresponding schematic page should be referenced.

Table 2-1. Mix and Match Options For Intel740™ Graphics Accelerator Card

| Component/<br>Functionality | Intel740™<br>Graphics<br>Accelerator<br>Page 3 | BT829<br>Page 5 | BT869<br>Page 6 | DVD Chip/<br>Daughter<br>Card<br>Page 7 | SO-DIMM<br>Module<br>Page 11         | Memory<br>Components<br>Page 12      |

|-----------------------------|------------------------------------------------|-----------------|-----------------|-----------------------------------------|--------------------------------------|--------------------------------------|

| 2D/3D                       | Х                                              |                 |                 |                                         |                                      |                                      |

| Video Capture               | Х                                              | Х               |                 |                                         |                                      |                                      |

| TV Out                      | Х                                              |                 | Х               |                                         |                                      |                                      |

| DVD (HW)                    | Х                                              |                 |                 | Х                                       |                                      |                                      |

| 2 MB                        | Х                                              |                 |                 |                                         | (1) 256K x 64                        | (2) 256K x 32                        |

| 4 MB                        | х                                              |                 |                 |                                         | (1) 512K x 64<br>or<br>(2) 256K x 64 | (2) 512K x 64<br>or<br>(4) 256K x 32 |

| 8 MB                        | Х                                              |                 |                 |                                         | (1) 1M x 64                          | (4) 1M x 16                          |

# 2.1.1 Design Features

# 2.1.1.1 Intel740™ Graphics Accelerator

The Intel740<sup>TM</sup> graphics accelerator is the main component of the graphics reference design. This component delivers high performance 3D/2D graphics and video capabilities. Each of the interfaces are described below.

- Accelerated Graphics Port (AGP) Interface. The AGP interface is a new interface designed for 3D graphics. This interface provides increased bandwidth over PCI, side band addressing, and AGP memory 3D texture storage. For a more complete description of the AGP interface refer to the Intel740<sup>TM</sup> Graphics Accelerator Datasheet and AGP Specification.

- Local Memory Interface. The memory interface on the Intel740<sup>TM</sup> graphics accelerator can

operate at speeds up to 100 MHz. An SDRAM interface supports SGRAM and SDRAM to be

used for different memory densities.

- VMI Interface. A bi-directional VMI like port is incorporated into the Intel740<sup>TM</sup> graphics accelerator providing a mechanism for affordable DVD. Video capture is also supported using the video port pins.

- TV Out Interface. Intel has worked with Rockwell\* (Brooktree\*) to design an interface capable of supporting a high quality TV out chip. This interface allows the Intel740<sup>TM</sup> graphics accelerator to output on a monitor, TV, or both.

- **BIOS Interface.** The Intel740<sup>TM</sup> graphics accelerator supports a FLASH or ROM BIOS. Up to 256Kx8 can be supported.

- **GPIO Interface.** Nine GPIO signals exist on the Intel740<sup>TM</sup> graphics accelerator. GPIO[8:0] allow for power management, DDC, I<sup>2</sup>C, thermal fault sensing, and other general features.

- **DAC Interface.** An integrated DAC provides display resolutions up to 1600x1200.

# 2.1.2 BT829B - Video Decoder

The Bt829B is a video capture processor used to convert analog video data into CCIR 601 digital video data. This chip contains the following capabilities.

- Analog Inputs. The Bt829B contains four composite video inputs along with one chroma and one luma input for s-video.

- I<sup>2</sup>C Interface. Control of the Bt829B is accomplished though the use of an I<sup>2</sup>C interface. All of the chip's registers are programmed using this interface as is the selection of the analog input source to use in generating digital video data.

- Video Port. The Bt829B contains a video port capable of outputting 8 or 16 bit data. The data format is YUV 4:2:2 with HSYNC, VSYNC, and PIXEL CLOCK as control signals.

# 2.1.2.1 BT869 - TV Encoder

The Bt869 provides high quality TV out. This component contains the following interfaces:

- **Input Port.** The Bt869 is capable of receiving data in two formats. The format used by this reference design for receiving data is through the 24 bit digital port accepting data on both edges of the reference clock. This mode of operation is documented in the *Intel740*<sup>TM</sup> *Graphics Accelerator Datasheet*. The second method for capturing data is through the use of the VMI protocol. This interface is documented in the *VMI 1.4 Interface Specification*.

- Flicker Filter Output. The output of the Bt869 is a very high quality flicker filtered output. This is due to a 5 tap internal filter. Output can be displayed in interlaced, non-interlaced, PAL, or NTSC formats. Macrovision7 output is also supported in the Bt869 component. The Bt869 is capable of displaying composite or S-Video data.

- I<sup>2</sup>C Interface. Control of the Bt869 is achieved through the I<sup>2</sup>C port.

# 2.1.3 Terminology

# 2.1.3.1 Power Sources

The card is supplied with four voltages through the edge connector. Other voltages are derived on-board. Thus, the Power Layer of the board must be divided into several distinct planes. Table 2-2 lists the various power elements on the Intel740<sup>TM</sup> graphics accelerator reference design. Each of the voltage sources are supplied by a plane except for 12 volts, which is supplied by a 25 mil trace.

**Table 2-2. Intel740™ Graphics Accelerator Power Supplies**

| Schematic<br>Symbol | Description        | Voltage | Max<br>Current | Source                      |

|---------------------|--------------------|---------|----------------|-----------------------------|

| VDDQ3               | 3.3V AGP Supply    | +3.3V   | 8.0A           | Edge connector              |

| VCC3                | 3.3V Logic Supply  | +3.3V   | 6.0A           | Edge connector              |

| VCC                 | 5V Logic Supply    | +5.0V   | 2.0A           | Edge connector              |

| +12V                | 12V Supply         | +12V    | 1.0A           | Edge connector              |

| VCC2                | 2.7V Core Supply   | +2.7V   | 3.0A           | VCC3, via Voltage Regulator |

| 3VAA_BT869          | 3.3V Analog Supply | +3.3V   | < 1.0A         | VCC3, via Ferrite Bead      |

| AVCC                | 5V Analog Supply   | +5.0V   | < 1.0A         | VCC, via "fence"            |

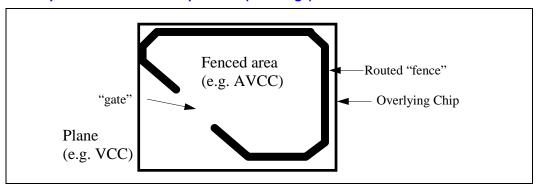

### 2.1.3.2 Fences

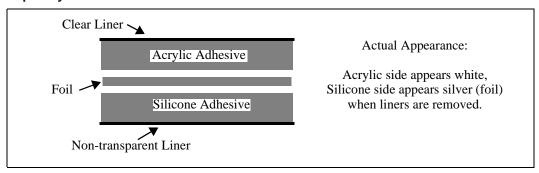

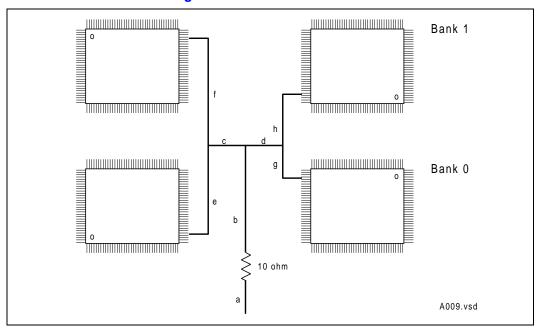

A "fence" is a line routed out of the plane such that a given area is isolated from the rest of the plane except at a single point of contact, conceptually the "gate" in the fence. A fence will minimize noise originating from digital signaling onto the analog signals. This provides higher quality video for both the Bt829B and Bt869. An example of a fenced power plane is shown in Figure 2-1. The heavy black line is the routed area. The width of the gate or opening can be up to 75% of the length of the IC in question. The width of the routed fence should conform to the separation routing between power planes (i.e., 25 mils minimum).

Figure 2-1. Example of Power Plane Separation ("fencing")

# 2.1.3.3 Stitching

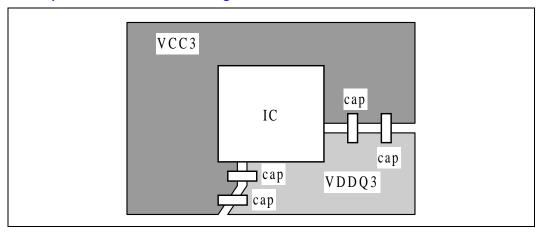

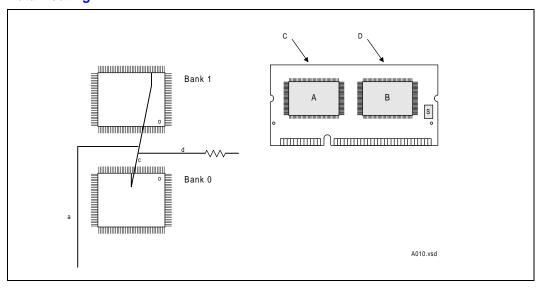

Power plane "stitching" is required between the VCC3 and VDDQ3 planes. Stitching two isolated planes together with capacitors allows a current return path for high frequency signals which pass over split power planes. This helps to eliminate EMI. The six  $0.1~\mu F$  capacitors coupling VCC3 to VDDQ3 should be spaced evenly if possible. Note the VDDQ3 plane is only near the AGP connector. An example of stitching is shown in Figure 2-2. This figure illustrates the power planes and, therefore, does not show signal traces between capacitors. The general rule for power plane stitching is to have a capacitor placed between every four signals crossing the two planes. As an example, there should be a capacitor, four signals, a capacitor, another four signals, and so forth ending with a capacitor.

Figure 2-2. Example of Power Plane Stitching

# 2.2 Layout and Routing Guidelines

This chapter describes layout and routing recommendations to insure a robust design. These guidelines should be followed as closely as possible. Any deviations from the guidelines listed here should be simulated to insure adequate margin is still maintained in the design.

# 2.2.1 Placement

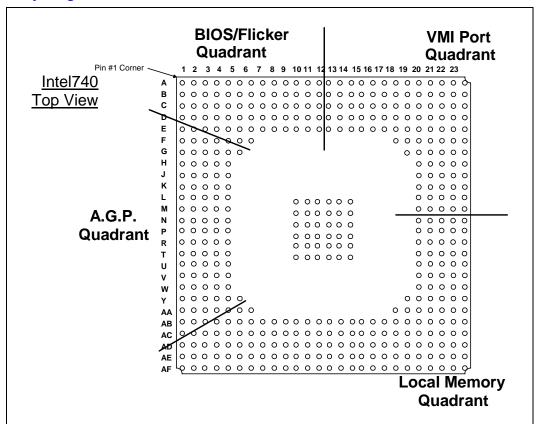

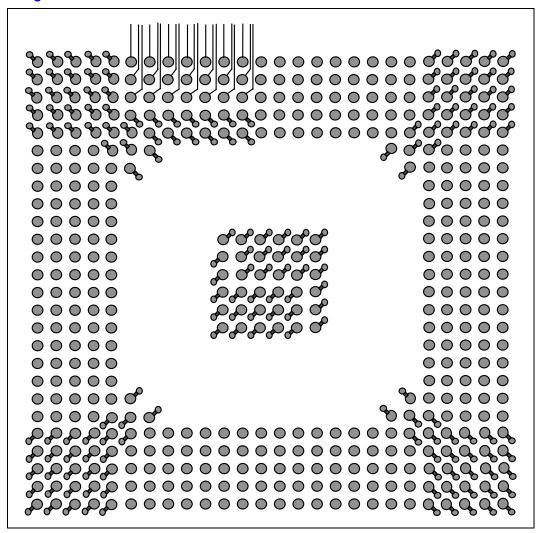

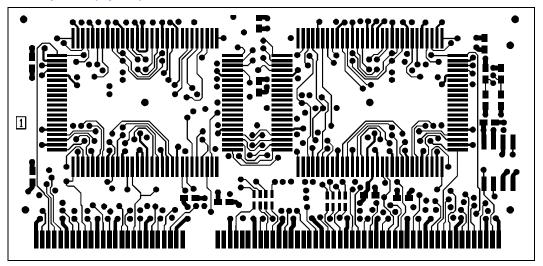

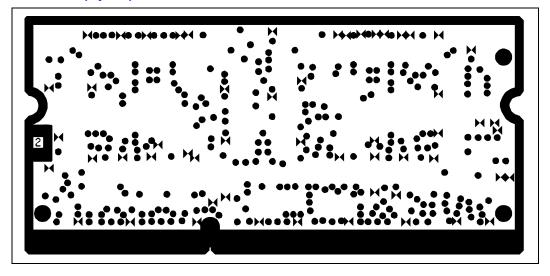

The ball connections on the Intel740<sup>TM</sup> graphics accelerator have been assigned to simplify routing and keep board fabrication costs down by enabling a 4-layer design. Figure 2-3 shows the four signal quadrants of the Intel740 graphics accelerator. Component placement should be done with this general flow in mind. This will simplify routing and minimize the number of signals which must cross. The individual signals within the respective groups have also been optimized to be routed using only 2 PCB layers.

A complete list of signals and ball assignments can be found in the Intel $740^{\rm TM}$  Graphics Accelerator Datasheet.

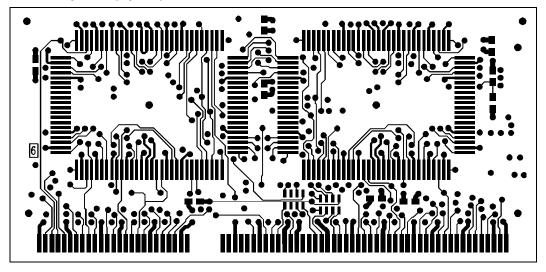

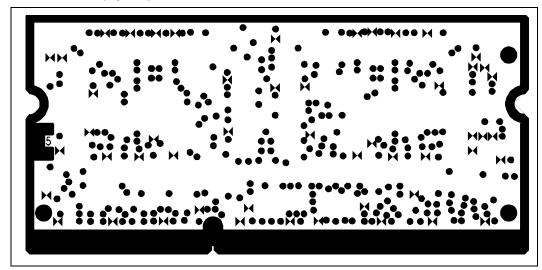

Figure 2-3. Major Signal Sections

An example of the proposed component placement for an ATX form factor design is shown in Figure 2-4. This is the placement used on the reference card. For NLX placement issues, refer to Section 5.6, "NLX Considerations" on page 5-5.

### ATX Form Factor:

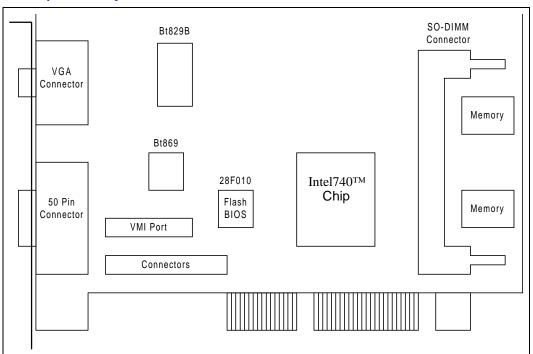

- The example placement (Figure 2-4) shows the Bt829B, Bt869, SO-DIMM Module, Intel740 graphics accelerator, VMI Port connections along with a 50 pin video connector.

- The trace length limitation between critical connections will be addressed later in this

document.

- Figure 2-4 is for *reference only*. The choice of size of memory, whether to have an SO-DIMM connector, what video components to place on the board, and which video connectors to have on the bracket will have to be evaluated by the board designer.

Figure 2-4. Example ATX Layout

# 2.2.2 Board Description

Even with the following recommendations, it is important to simulate your design.

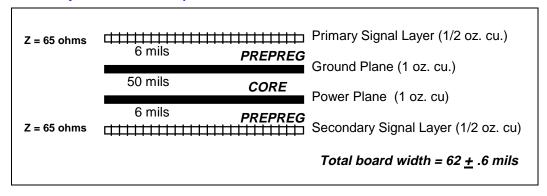

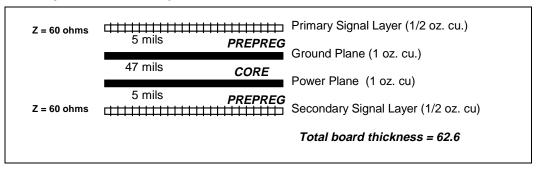

A 4-layer stack-up arrangement is recommended. The stack-up of the board is shown in Figure 2-5. The impedance of all the signal layers are to be between 50 and 80 ohms. Lower trace impedance will slow signal edge rates, over & undershoot, and have less cross-talk than higher trace impedance. Higher trace impedance will create faster edge rates and decrease signal flight times. Prepreg is FR-4 material.

Figure 2-5. Four Layer Board Stack-up

**Note:** Top and bottom routing layers specify 1/2 oz. cu. However, by the time the board is plated, the traces will end up with about 1 oz. cu. Please check with your fabrication vendor on the exact value and insure that any signal simulation accounts for this.

*Note:* Thicker core helps reduce board warpage issues, while thinner prepreg reduces trace impedance.

Additional guidelines on board buildup, placement and layout include:

- All layers should be cut back from the substrate outer edge by 0.050". A 0.025"-wide strip

should be added to all signal and power layers around the outer edge and tied to the ground

plane.

- All power and ground traces between vias and pads for all components should be at least as wide as the component power or ground pad itself.

- Through-hole vias, unless otherwise noted, are 10 mil drill, 25 mil diameter pad. Via capping

is required. All vias on the secondary side should be covered with solder mask. All vias on the

primary side are to be encroached with solder mask and anti-pad unless board dryness has

been guaranteed.

- To minimize solder wicking with the BGA, the component side solder mask should be applied prior to tinning the copper. There should be no surface mount over bare copper (S.M.O.B.C.).

- The solder mask must cover the trace between the via and pad.

- The board impedance (Z) should be between 50 and 80 ohms (65 ohms  $\pm 20\%$ ).

- FR-4 material should be used for the board fabrication.

- The ground plane should not be split on the ground plane layer. If a signal must be routed for a short distance on a power plane, then it should be routed on a VCC plane, not the ground plane.

- Keep vias for decoupling capacitors as close to the capacitor pads as possible.

- Keep isolated power planes as close as possible to each other. This will minimize impedance mismatch at the split.

- All decoupling capacitors should be tied to the ground plane by a trace at least as wide as the

via ring to the plane.

# 2.2.3 BGA Component

# 2.2.3.1 Layout Requirements

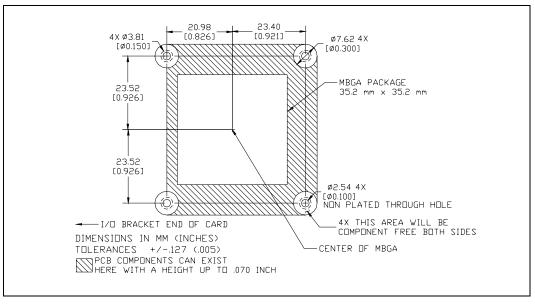

The following layout requirements should be followed when routing the 468 MBGA package.

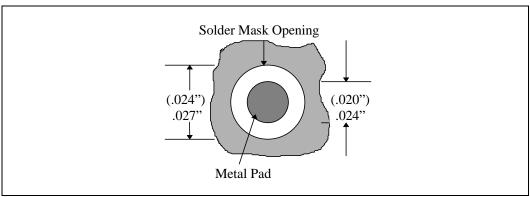

- All non-ground BGA lands should be Metal Defined (MD) lands with the following nominal dimensions (see Figure 2-6).

- Metal pad: 20 (6/6 routing) / 24 mils (5/5 routing)

Solder mask opening: 24 mil (20 mil pad) / 27 mils (24 mil pad)

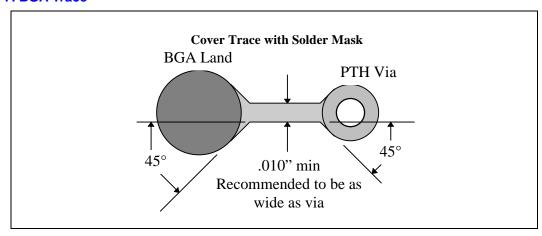

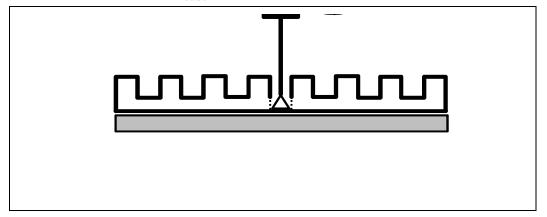

- Any trace connected to a MBGA land or PTH via in the MBGA land grid array should be teardropped. The teardrop should leave the trace at a 45° angle and intersect the via tangentially (see Figure 2-7).

- The minimum distance between the gold finger edge of the card and the center of the first row of MBGA lands should be 525 mils, and 480 mils from the end of the start of the bevel.

- All BGA ground vias should use 16 mil drill with **no thermal reliefs**.

Figure 2-6. Metal Defined land dimensions

Figure 2-7. BGA Trace

# 2.2.3.2 Ground Connections

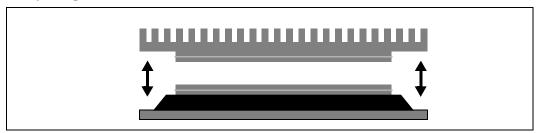

All lands in the four corners and center are  $V_{ss}$  (GND). Thermal analysis requires that each  $V_{ss}$  ball connect to an adjacent via which passes through to the solder side of the board, one via per ball, with a trace as wide as the via. Heat will dissipate through these vias to the GND plane as well as to the air on the solder side.

Figure 2-8. Dogbone Via Pattern

# 2.2.3.3 Power Connections

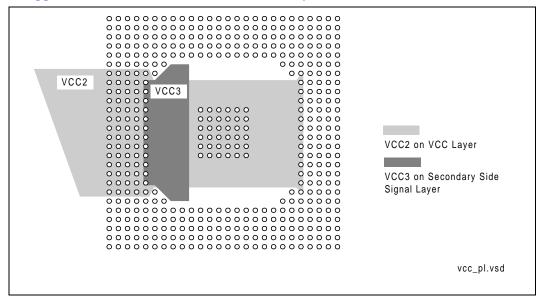

The VCC2 plane should be as wide as practical for high current-carrying capacity. Because of the interspersing of VCC2 and VCC3 pins on the Intel740<sup>TM</sup> graphics accelerator, a polygon will be needed on one of the signal layers to extend the VCC3 plane to the isolated VCC3 pins (Figure 2-9). The VCC2 polygon is a separate plane on the VCC Layer; the darker VCC3 polygon is a power flood on the solder side and connects to the VCC3 plane on the VCC Layer through vias.

Figure 2-9. Suggested VCC Planes for the Intel740™ Graphics Accelerator

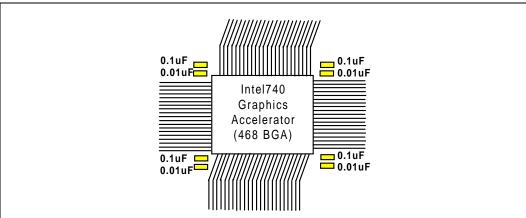

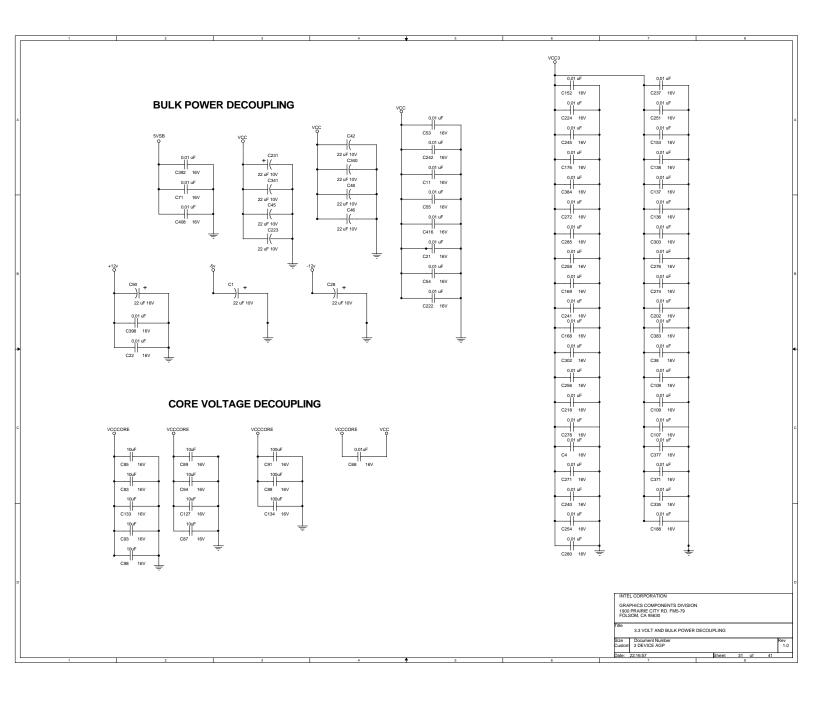

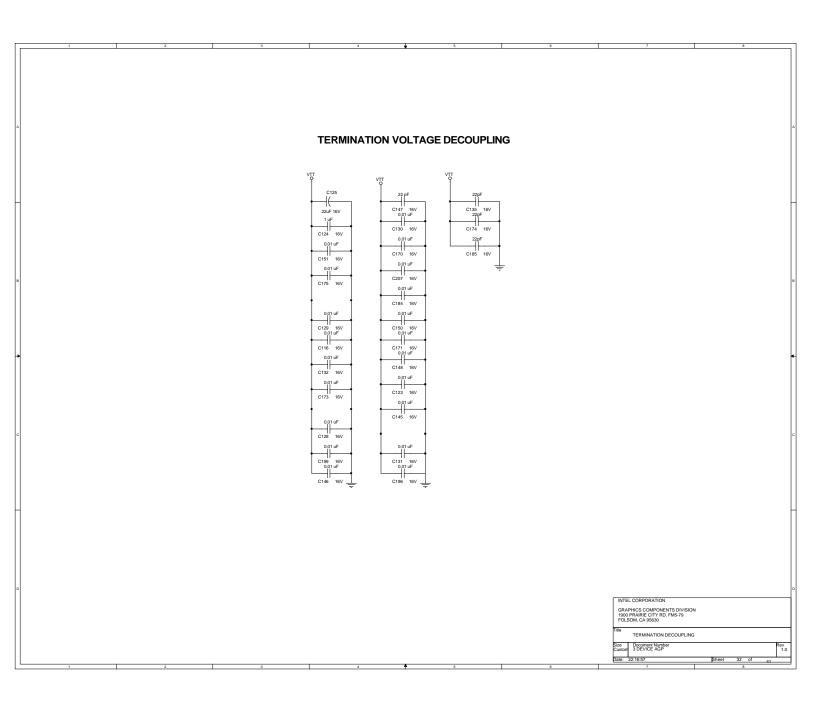

#### 2.2.3.4 Decoupling

Decoupling capacitors should ideally be placed as close as possible to the Intel740 graphics accelerator. This means that the best decoupling will occur if the capacitors are placed directly underneath the component. If a single sided board is required and capacitors cannot be placed underneath the component then decoupling is recommended at the corners of the Intel740 graphics accelerator package. At least a 0.1  $\mu$ F and 0.01  $\mu$ F are recommended for each corner. By placing the capacitors in this location all of the traces can "break-out" from the BGA package on all four sides.

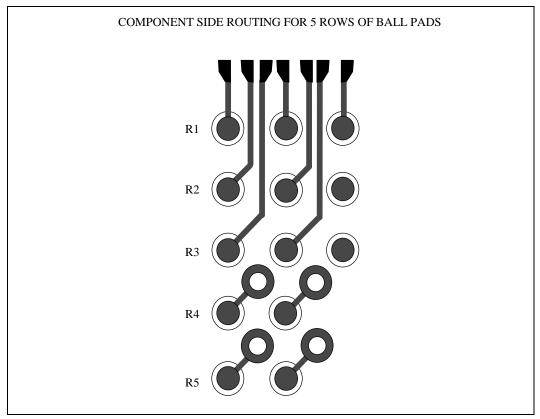

# 2.2.3.5 General Signal Routing

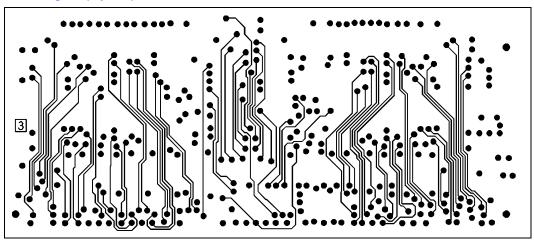

Figure 2-11 depicts general escape of traces from the five rows of BGA ball pads. The first three ball rows can be routed on the primary layer. The last two must be routed through vias to the secondary layer. Underneath the BGA, trace routing should be 5 on 5 or 6 on 6. Once the traces have left the BGA, however, routing should expand to 5 on 10 or 6 on 12. The ratio should be kept as 1:2.

The signals AD\_STB\_A, AD\_STB\_B and SB\_STB should have a spacing of 1:4 to other signals. Using this extra spacing between these specific signals will help to keep crosstalk to a minimum.

Figure 2-11. Intel740™ Graphics Accelerator BGA Routing Example

# 2.2.4 Voltage Regulator

The physical tab (used as a built in heatsink) on the MOSFET package is the drain pin, and will need a tab-shaped pad to solder to.

*Note:* The resistor/capacitor network between the COMP pin (pin 5) and the GND pin (pin 3) of the LT1575 should be connected directly to the GND pin of the device rather than tied to the ground plane.

# 2.2.5 Bt829 Video Decoder

Note: Rockwell\* Semiconductor should be contacted for up to date layout recommendations.

# 2.2.5.1 Ground Planes

The Bt829B and associated circuitry have two ground planes, GND and ANALOG\_GND (AGND). These are electrically the same plane but should be separated by a fence, as described in Section 2.1.3.2, "Fences" on page 2-4. The schematic illustrates which pins attach to which plane as does Table 2-3. The opening in the fence should be under the Bt829B and be up to 75% of the IC's width. The AGND plane is the isolated or subset plane, hence GND is the return path for current. The AGND plane should be as small as possible.

### Table 2-3. Bt829B GND and AGND Pins

| Bt829 Ground Pins |                                             |  |  |  |

|-------------------|---------------------------------------------|--|--|--|

| GND               | 11, 21, 31, 33, 39, 77, 81, 90, 93, 95, 100 |  |  |  |

| AGND              | 42, 47, 54, 56, 58, 61, 66, 71, 75          |  |  |  |

### 2.2.5.2 Power Planes

The Bt829 and associated circuitry have three power planes, VCC3, VCC and AVCC. The latter two are digital and analog +5V, respectively. As above, these are electrically the same plane but separated by a fence. This fence and the AVCC plane should parallel the AGND fence and plane closely, with the opening in about the same location.

### Table 2-4, Bt829B VCC and AVCC Pins

| Bt829B 5V Pins |                        |  |  |

|----------------|------------------------|--|--|

| VCC            | 10, 38, 76, 88, 96     |  |  |

| AVCC           | 40, 44, 48, 60, 65, 72 |  |  |

# 2.2.5.3 Passive Components and Signal Routing

All passive components should be placed as near to the Bt829B as possible. These parts include: the  $0.1\mu F$  and  $0.01\mu F$  bypass capacitors, the  $10\mu F$  capacitors, the 75 ohm terminating resistors, and the crystal oscillator circuitry.

**Note:** There must be NO digital signals routed under or above the analog power and ground planes (AVCC and AGND).

The filter circuits on the four video input signals (TUNER, SV\_LUM, SV\_CHR, CV\_IN) need to be located near the 50-pin connector. Note that other designs not using a 50 pin video connector should have the filter circuits placed as close as possible to the input connectors. The analog traces should not be routed such that they parallel other analog signals at a close spacing for a long length. Wherever analog signals run in parallel, separated by less than 15 mils for longer than 250 mils, run a ground line between them of approximately 12 mils width.

# 2.2.6 Bt869 Video Encoder

**Note:** Rockwell Semiconductor should be contacted for up to date layout recommendations.

# 2.2.6.1 Ground Planes

Only one ground plane is recommended for the Bt869. This ground plane should be formed as a fence underneath the Bt869.

# 2.2.6.2 Power Planes

The Bt869 and associated circuitry have two power planes, VCC3 and 3VAA\_BT869. The 3VAA\_BT869 plane is a separate cutout, joined to VCC3 by a ferrite bead. The device should reside entirely above the 3VAA\_BT869 plane, as there are no VCC3 connections to the device. So long as the 3VAA\_BT869 plane underlies all the analog components, it should be as small as possible.

Table 2-5. Bt869 Digital and Analog Power Pins

| Bt869 3V Pins                      |                                    |  |  |

|------------------------------------|------------------------------------|--|--|

| 3VAA_BT869 (Analog) 69, 71, 73, 80 |                                    |  |  |

| 3VAA_BT869 (Digital)               | 19, 20, 30, 40, 46, 47, 57, 60, 61 |  |  |

# 2.2.6.3 Passive Components and Signal Routing

All passive components should be placed as close to the Bt869 device as possible. These devices consist of: the  $0.1\mu F$  and  $0.01\mu F$  bypass capacitors, the  $10\mu F$  capacitors, the crystal oscillator circuitry, and the  $0.1\mu F$  capacitors and 75 ohm resistors at the VREF, VBIAS and FSADJUST pins as well as the protection diodes.

**Note:** There must be NO digital signals routed under or above the analog power and ground planes (3VAA BT869 and AGND).

The filter circuits on the three video output signals (TVOUT\_Y, TVOUT\_C, TVOUT\_CVBS) must be very near the 50-pin connector or other output connectors. Long lengths of closely spaced parallel analog signals should be avoided. Wherever analog signals run in parallel, separated by less than 15 mils for longer than 250 mils, run a ground line between the video input traces of approximately 12 mils width.

# 2.2.6.4 AGP Layout and Routing Guidelines

This section describes the group of signals that runs between the Intel740 graphics accelerator AGP Interface and the AGP edge connector. For the definition of AGP functionality (protocols, rules and signaling mechanisms, as well as the platform level aspects of AGP functionality), refer to the latest *AGP Interface Specification*. This document focuses only on specific Intel740 graphics accelerator recommendations for the AGP interface. The general length requirements are shown in Table 2-6.

**Table 2-6. AGP Signal Lengths**

| Group | Recommendation |

|-------|----------------|

| All   | ≤ 3.0"         |

| CLK   | 2.6" ± 0.4"    |

Mismatch between strobe and data traces must be less than 0.5". Thus the trace length for signals within a group must be within  $\pm 0.5$ " of the corresponding strobe's trace length, as indicated in Table 2-7.

**Table 2-7. Strobes and Corresponding Signal Groups**

| Group                 | Strobe   | Recommendation               |

|-----------------------|----------|------------------------------|

| AD[31:16], C/BE[3:2]# | AD_STB_B | L <sub>AD_STB_B</sub> ± 0.5" |

| AD[15:0], C/BE[1:0]#  | AD_STB_A | L <sub>AD_STB_A</sub> ± 0.5" |

| SBA[7:0]              | SB_STB   | L <sub>SB_STB</sub> ± 0.5"   |

For example, AD29 and AD\_STB\_B must not be mismatched by more than 0.5". No such comparison, however, should be enforced between AD29 and AD30, or AD29 and C/BE2#, etc.

*Note:* AGP strobes must be separated by 2X normal signal spacing (i.e., if normal spacing is 5/10 or 6/12, the strobe signals must be separated from other traces by 20 or 24 mils, respectively).

# 2.2.6.5 Intel740™ Graphics Accelerator Memory Layout and Routing Guidelines

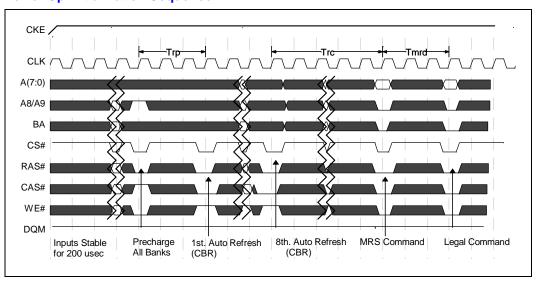

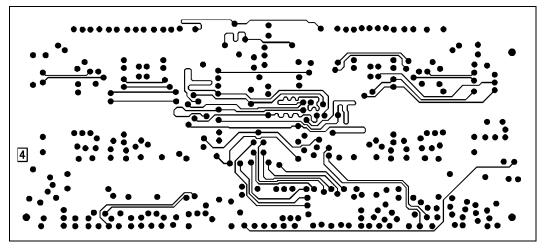

The Intel740 graphics accelerator integrates a memory controller which supports a 64-bit memory data interface. SGRAM can be used in addition to SDRAM if it is configured to perform as an SDRAM. The Intel740 graphics accelerator generates the Row Address Strobe (SRAS[A:B]#), Chip Selects (CS0[A:B]#, CS1[A:B]#), Column Address Strobe (SCAS[A:B]#), Byte Enables (DQM[0:7]#), Write Enables (WE[A:B]#), and Memory Addresses (MA). The memory controller interface is fully configurable through a set of control registers.

Eleven memory address signals (MAx[10:0]) allow the Intel740<sup>TM</sup> graphics accelerator to support a variety of commercially available SO-DIMMs and components. Two SRAS# lines permit two 64-bit wide rows of SDRAM. All write operations must be one Quadword (QWord). The Intel740 graphics accelerator supports memory up to 100 MHz.

Rules for populating a Intel740 graphics accelerator Memory:

- Memory can be populated using either an SO-DIMM or components.

- SDRAM and SGRAM components and/or SO-DIMMs can be mixed.

- The DRAM Timing register, which provides the DRAM speed grade control for the entire memory array, must be programmed to use the timings of the slowest memories installed.

Possible DRAM and system options supported by the Intel740 graphics accelerator are shown in Table 2-8.

Table 2-8. Supported Memory Options (Other Memory Options Are Not Supported)

| SDRAM/<br>SGRAM<br>Technology | SDRAM/<br>SGRAM<br>Density | SDRAM/<br>SGRAM<br>Width | Addressing | Address Size |        |     | ocal Memory<br>Size |  |

|-------------------------------|----------------------------|--------------------------|------------|--------------|--------|-----|---------------------|--|

|                               |                            |                          |            | Row          | Column | Min | Max                 |  |

| 8 Mbit                        | 256K                       | 32                       | Asymmetric | 10           | 8      | 2MB | 4MB                 |  |

| 16Mbit                        | 512K                       | 32                       | Asymmetric | 11           | 8      | 4MB | 8MB                 |  |

| 16Mbit                        | 1M                         | 16                       | Asymmetric | 12           | 8      | 8MB | 8MB                 |  |

There are several groups of signals within the memory bus with layout restrictions.

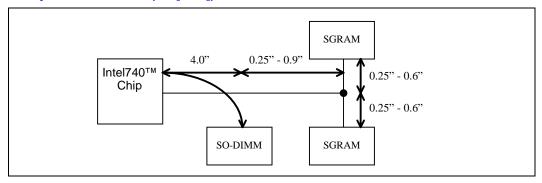

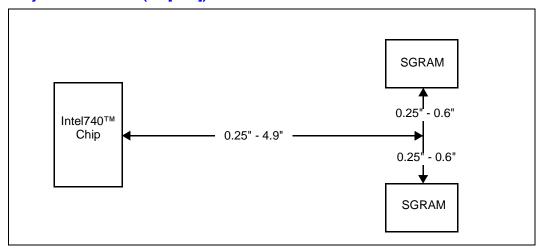

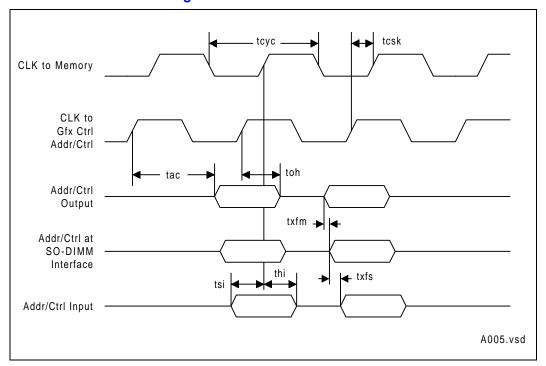

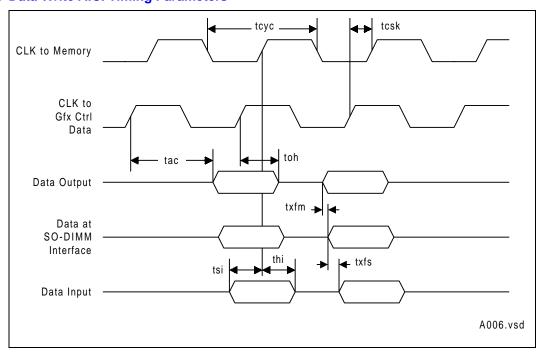

Table 2-9. Memory Layout Restrictions (See Figure 2-12 and Figure 2-13)

| Signal             | Intel740™ to SO-DIMM |      | SO-DIMM SGRAM Stub |      | SGRAM Stub |      |

|--------------------|----------------------|------|--------------------|------|------------|------|

|                    | Min                  | Max  | Min                | Max  | Min        | Max  |

| MA[11:0]           | n/a                  | 4.0" | 0.25"              | 0.9" | 0.25"      | 0.6" |

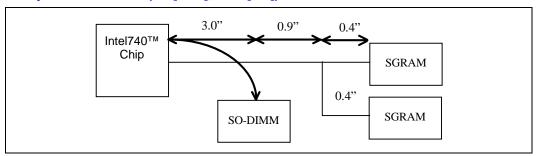

| MD[63:0], DQM[7:0] | n/a                  | 3.0" | 0.25"              | 0.9" | 0.25"      | 0.4" |

Figure 2-12. Layout Dimensions (MA[11:0])

Figure 2-13. Layout Dimensions (MD[63:0], DQM[7:0])

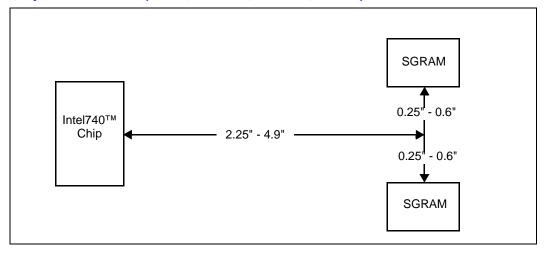

Table 2-10. Memory Layout Restrictions (See Figure 2-14 and Figure 2-15)

| Signal                                | Intel740™ to<br>SO-DIMM |      | SO-DIMM to SGRAM<br>Stub |      | SGRAM Stub |      |

|---------------------------------------|-------------------------|------|--------------------------|------|------------|------|

|                                       | Min                     | Max  | Min                      | Max  | Min        | Max  |

| WEA#, SRASA#, SCASA#,<br>CSA1#, CSB0# | n/a                     | 4.0" | n/a                      |      | n/a        |      |

| WEB#, SRASB#, SCASB#,<br>CSA0#        | n/a                     | 4.0" | 0.25"                    | 0.9" | 0.25"      | 0.6" |

Figure 2-14. Layout Dimensions (WEA#, SRASA#, SCASA#, CSA1#, CSB0#)

Figure 2-15. Layout Dimensions (WEB#, SRASB#, SCASB#, CSA0#)

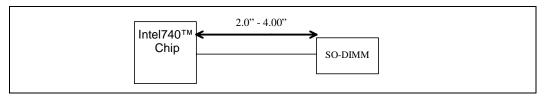

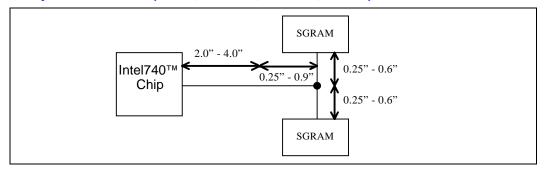

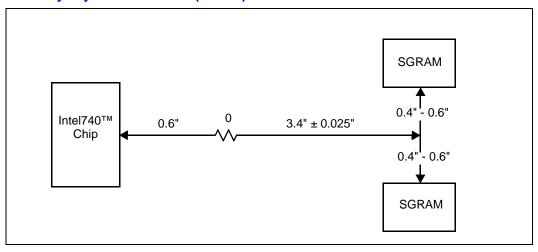

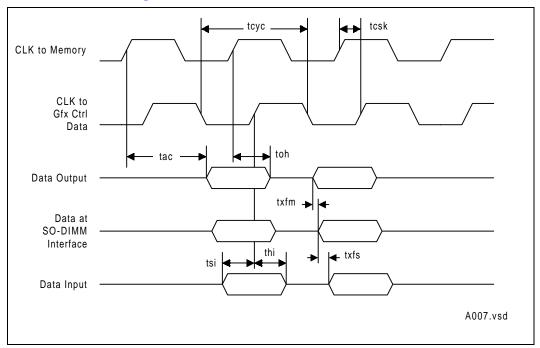

Table 2-11. Memory Layout Restrictions (See Figure 2-16 and Figure 2-17)

| Signal | Intel740™ to<br>Resistor | Resistor to SO-DIMM | SO-DIMM to<br>SGRAM Stub | SGRAM Stub |      |

|--------|--------------------------|---------------------|--------------------------|------------|------|

|        |                          |                     |                          | Min        | Max  |

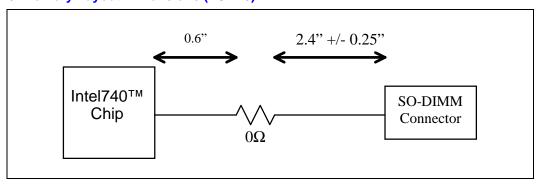

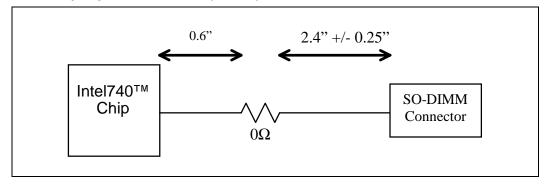

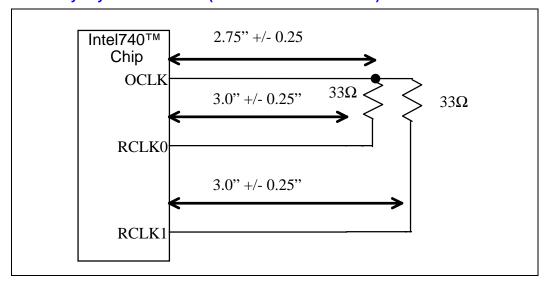

| TCLK0  | 0.6"                     | 2.4" ±0.25"         | n/a                      | n/a        | n/a  |

| TCLK1  | 0.6"                     | 2.4" ±0.25"         | 1.0"                     | 0.4"       | 0.6" |

Figure 2-16. Memory Layout Dimensions (TCLK0)

Figure 2-17. Memory Layout Dimensions (TCLK1)

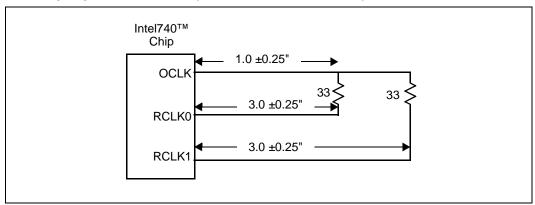

| Signal           | Intel740™ to Resistor |

|------------------|-----------------------|

| OCLK to Resistor | 2.75" ±0.25           |

| RCLK0, RCLK1     | 3.0" ±0.25"           |

**Note:** It is important to match clock lengths. For example, if the length from OCLK to Resistor is 1.03, then the length from Resistor to RCLK should be 3.03.

Figure 2-18. Memory Layout Dimensions (RCLK and OCLK to RCLK)

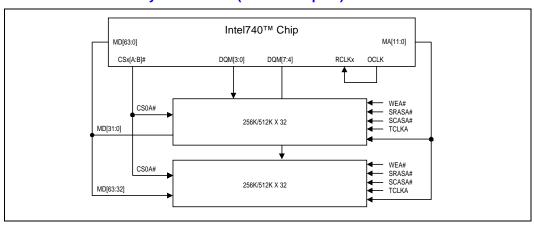

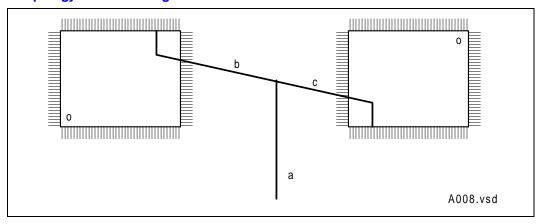

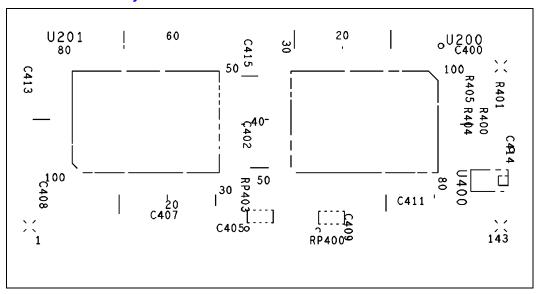

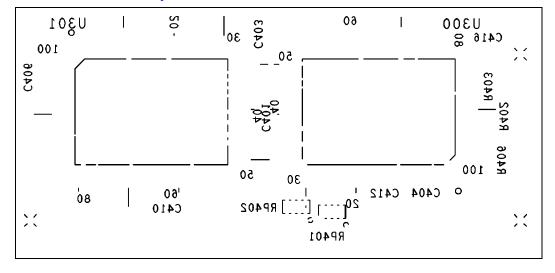

# 2.2.6.6 Intel740™ Graphics Accelerator Memory Configurations

In the following discussion the term *row* refers to a set of memory devices that are simultaneously selected by an SRAS and the CS# signal.

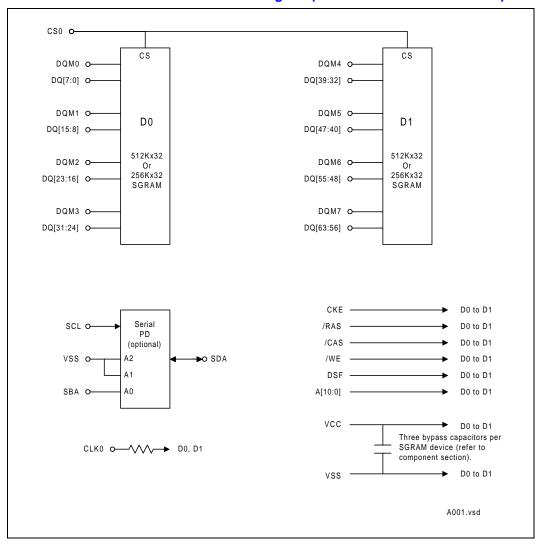

**Configuration #1:** In this configuration, the minimum amount of memory (2MB) is supported. Note that, the same copy of all control signals goes to each component.

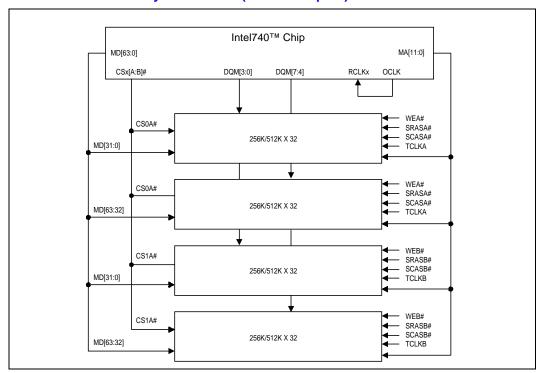

Figure 2-19. 2/4 MB Local Memory Connection (64-bit data path)

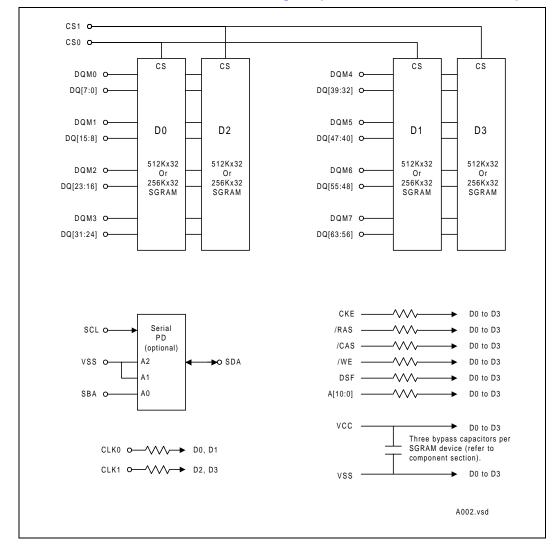

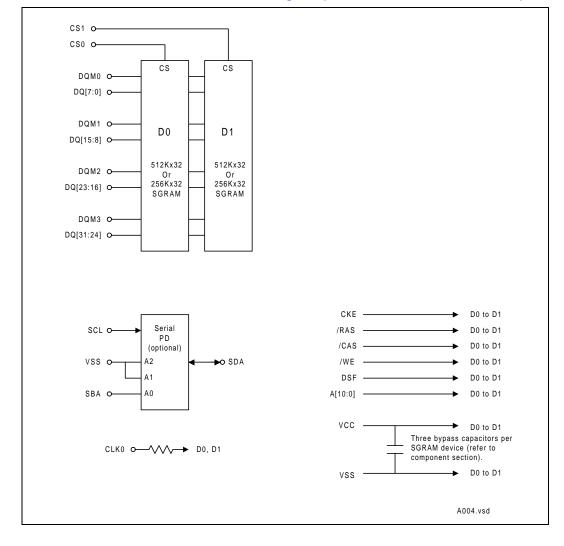

**Configuration #2:** Two rows of memory are supported in this configuration. If 256Kx32 components are used 4MB of memory is obtainable, if 512Kx32 is used, then 8MB is supported. Note that both rows of memory receive different copies of each control signal, for loading reasons.

Figure 2-20. 4/8 MB Local Memory Connection (64-bit data path)

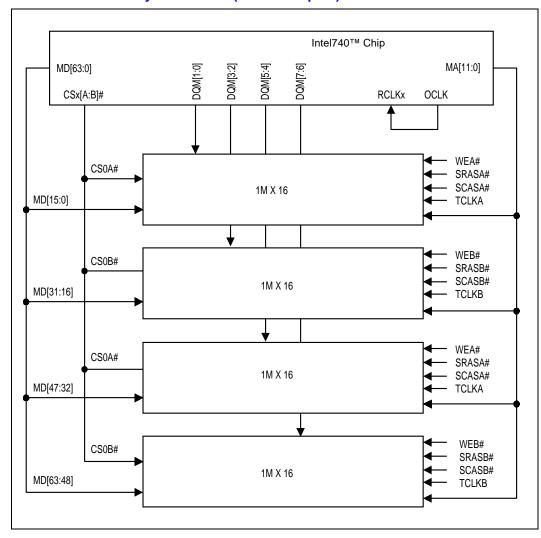

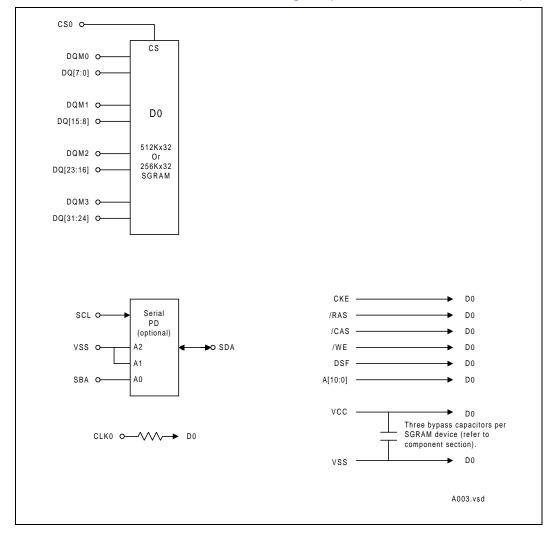

**Configuration #3:** One row of memory is supported in this configuration using 1Mx16 SDRAMs. Only the maximum allowable amount of memory (8MB) is supported in this configuration. Note that each copied signal is sent to only two components.

Figure 2-21. 8 MB Local Memory Connection (64-bit data path)

# 2.2.6.7 TV Out Interface

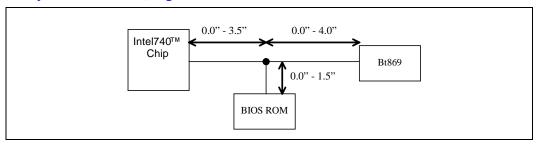

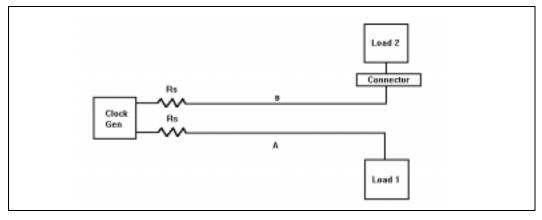

The TV out bus is the group of signals that carry digitized display data from the Intel740 graphics accelerator to the Bt869 flicker filter TV-out component. This interface is shared with the BIOS interface. Table 2-12 gives the maximum trace lengths between components.

Table 2-12. TV Out/ROMA Trace Lengths (See Figure 2-22)

| Signal     | Intel740™ to BIOS<br>Stub |      | RIOS Stub |      | BIOS to Bt869 |      |

|------------|---------------------------|------|-----------|------|---------------|------|

|            | Min                       | Max  | Min       | Max  | Min           | Max  |

| ROMA[17:0] | 0.0"                      | 3.5" | 0.0"      | 1.5" | 0.0"          | 4.0" |

Figure 2-22. Layout Dimensions, Digital TV Bus

# 2.2.6.8 Analog Signals

It is recommended that all analog signal traces be  $75\Omega \pm 5\%$ . It is important that these traces not violate the 5x10 mil spacing for the  $65\Omega$  traces. Analog traces include the DAC R, G, B traces, all of the inputs to the Bt829B component and outputs from the Bt869 component.

# 2.2.7 UL and FCC Considerations

Certain precautions should be taken in the design of the of a graphics card to ensure passing safety and EMI tests. These precautions are listed below.

- When a signal can be hot plugged, clamping diodes should be used to limit voltage spikes.

- When a voltage leaves the card, a fuse should be placed in the path to protect from a short circuit.

- Sockets, Fans and Brackets should be grounded.

- Separate Power Planes of the same voltage should be stitched together.

# 2.3 Addin Card Schematics

This section describes the Intel740<sup>TM</sup> Graphics Accelerator Reference Design Schematics. Please read this section carefully to observe all design recommendations and requirements.

The description of each schematic page is named by the logic block shown on that page.

### **Cover Sheet (Schematic Page 1)**

The Cover Sheet shows the schematic page titles, page numbers, disclaimers and power pins.

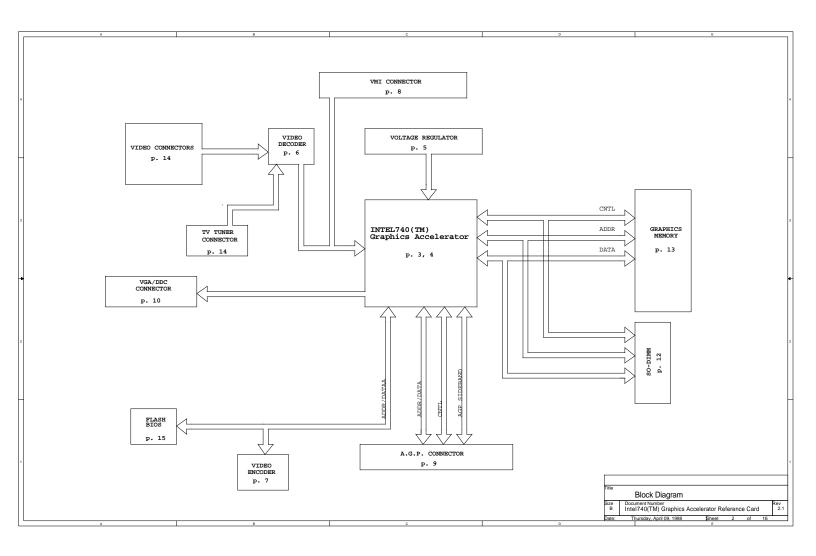

### **Block Diagram (Schematic Page 2)**

This page shows a block diagram overview of the Intel740 AGP card design. Schematic page numbers for each of the major schematic components are shown.

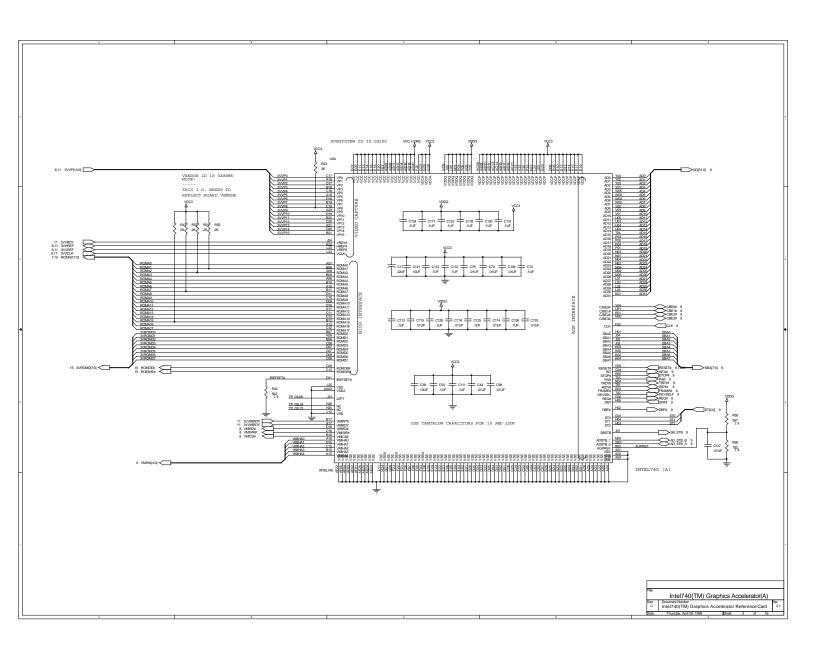

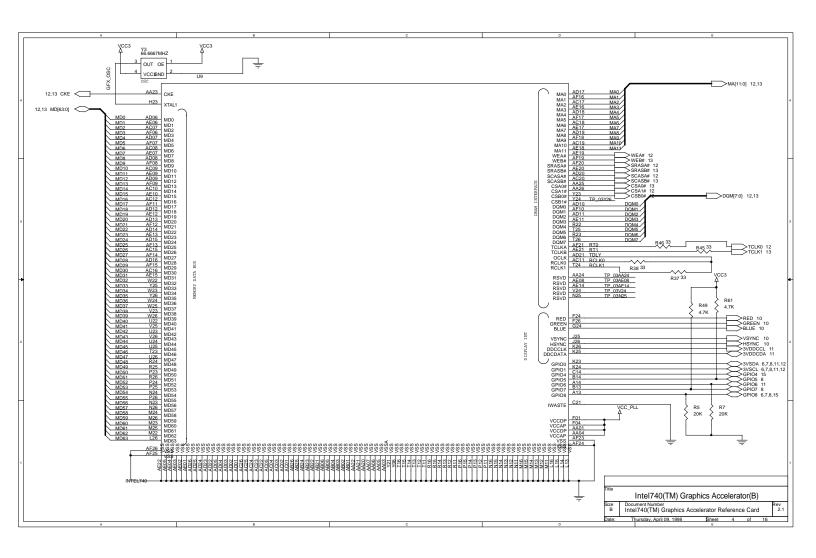

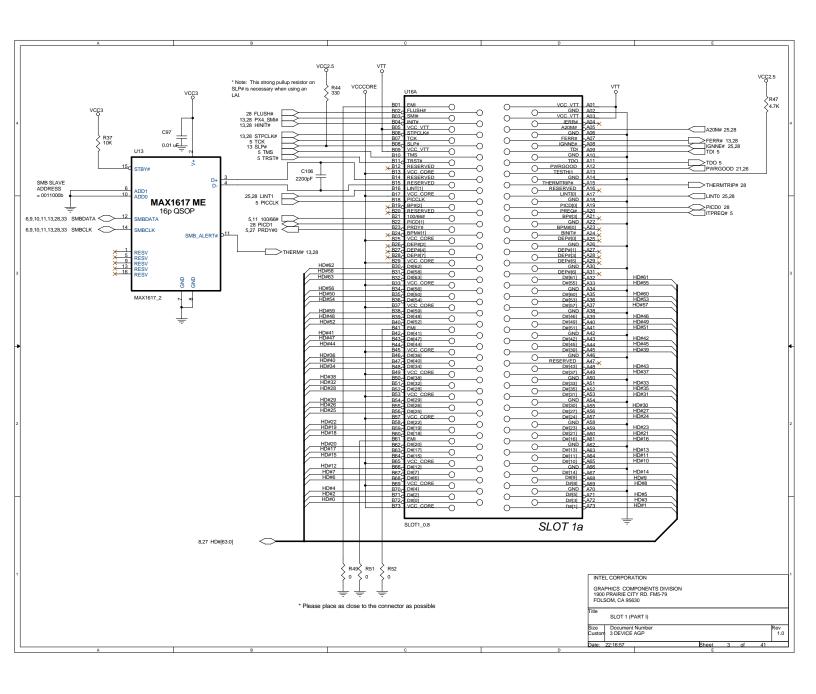

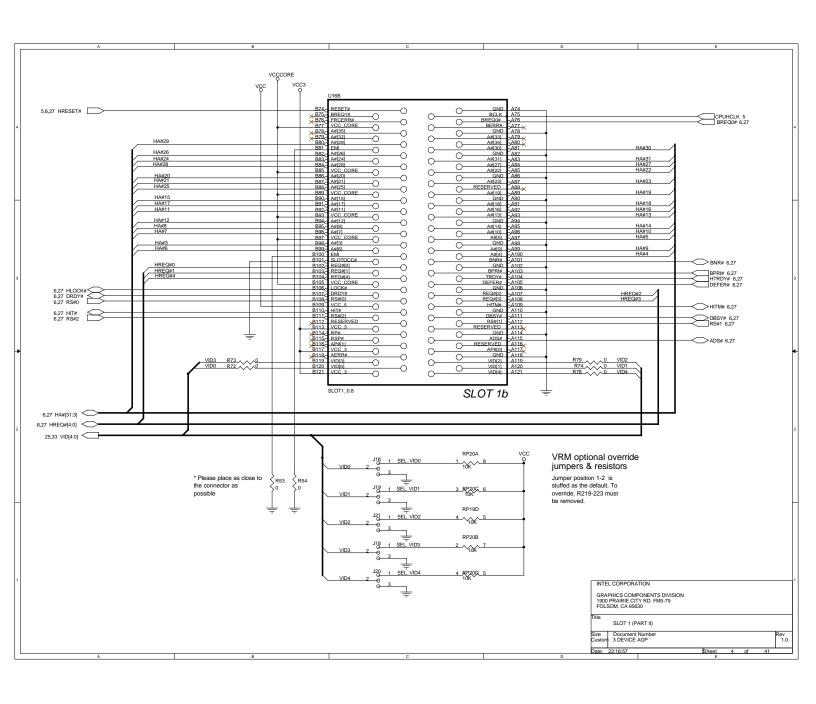

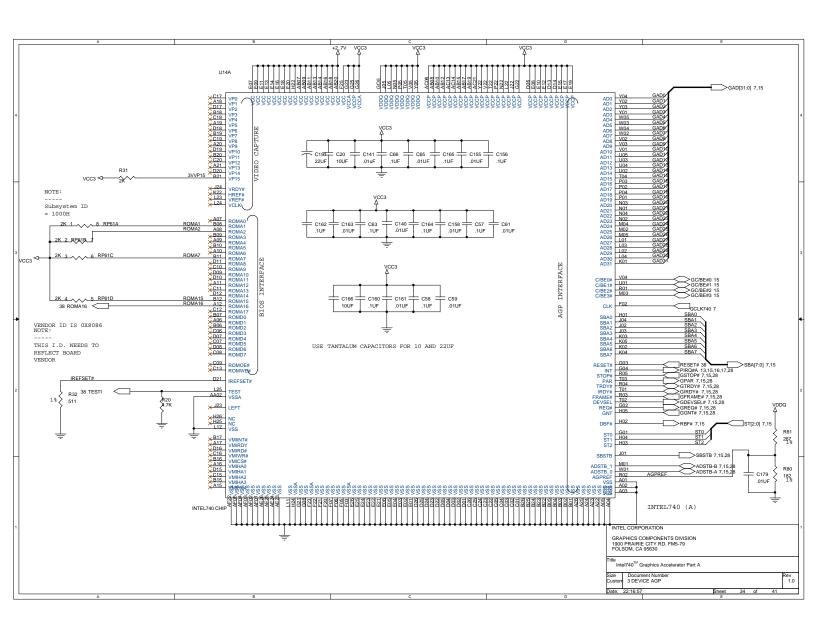

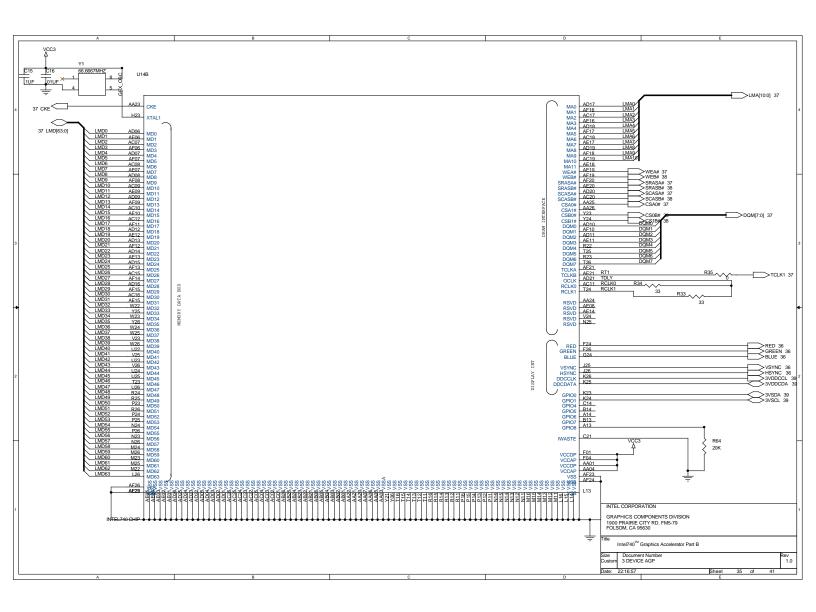

### Intel740<sup>TM</sup> Graphics Accelerator (Schematic Pages 3,4)

This page shows all of the connections to the Intel740 graphics accelerator. Each Intel740 graphics accelerator interface is hooked up in this reference design. Beginning in the upper left hand corner of the page, the video capture port is shown. Internally, the input pins are pulled down. These pins contain a strapping option for subsystem ID. In this case the reference design has an ID of 0100h. Bits that should be a "1" may be pulled up using a 2K pull-up resistor. If the graphics design will not have video, the only concern is pulling the bus up to the correct value for the subsystem ID. The video control signals may be left unconnected. The BIOS interface multiplexes the BIOS, vendor ID, and flicker filter TV encoder. The ROMA lines are internally pulled down and may be pulled up using a 2K pull-up resistor. The video host port connects directly to the VMI header. The section labeled AGP interface connects directly to the AGP connector. The memory interfaces connect to an SO-DIMM connector and memory components. Each of the 9 GPIOs serve a different function in the reference design. Table 2-13 lists the function assigned to the GPIOs.

**Table 2-13. GPIO Functions**

| GPIO  | FUNCTION                       |

|-------|--------------------------------|

| GPIO0 | I <sup>2</sup> C Data          |

| GPIO1 | I <sup>2</sup> C Clock         |

| GPIO2 | DDC Data                       |

| GPIO3 | DDC Clock                      |

| GPIO4 | Fan Fail                       |

| GPIO5 | Extra For DVD Control          |

| GPIO6 | VP[15:0] Bus Isolation Control |

| GPIO7 | Extra For DVD Control          |

| GPIO8 | Power Down                     |

Decoupling for the Intel740 graphics accelerator is shown along the bottom of the schematic page.

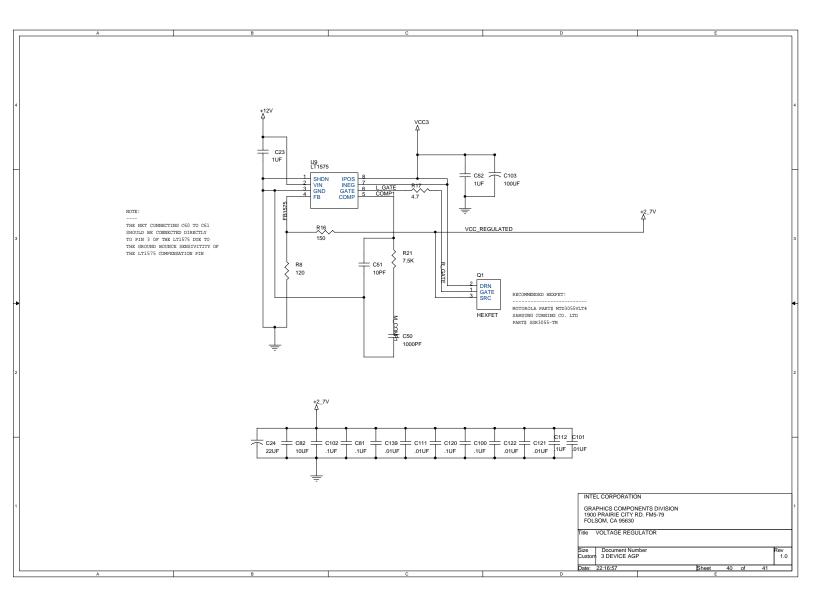

### **Voltage Regulator (Schematic Page 5)**

This page shows the circuitry to convert from 3.3 Volts to 2.7 Volts. The regulator used in the reference design does not need any heat sink for the FET. As shown, the FET will be dissipating slightly over 1 watt. If a different voltage regulator solution will be used, calculations will be needed to determine the need for a heatsink. Resistors R50, R44, R42, and R43 are only for the reference card design. These resistors allow different voltage combinations for core and internal Intel740 graphics accelerator PLLs. The table at the top of the page describes the voltage configurations. Core decoupling is shown at the bottom of the page and should be placed close to the Intel740 graphics accelerator.

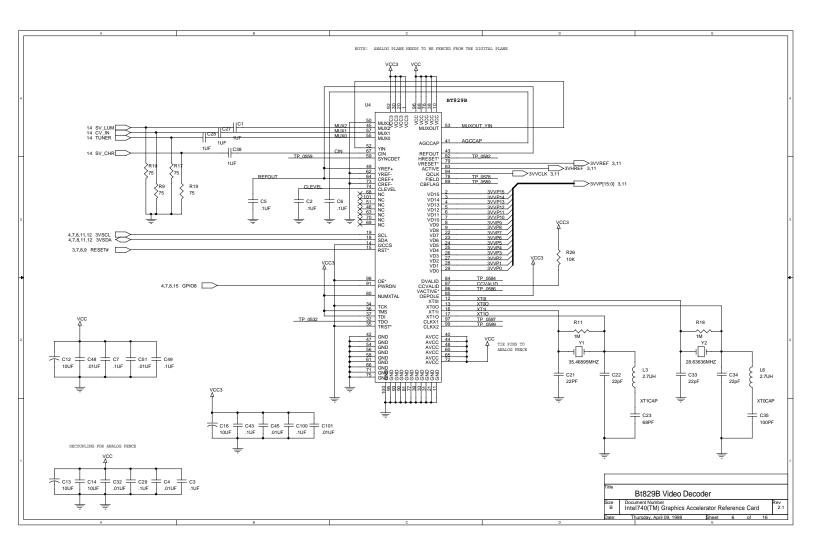

# Bt829B (Schematic Page 6)

The Bt829B component contains analog inputs which require special routing requirements detailed in Section 2.2.5, "Bt829 Video Decoder" on page 2-11. If these analog inputs are not used, then they should be tied to ground as is MUX3 in the reference design. The I2CCS pin is pulled low in the reference design to select an I<sup>2</sup>C address of 88h and 89h. This selection becomes important if connecting other I<sup>2</sup>C devices like the Bt869.

*Note:* Care must be taken to ensure that no two devices use the same address.

The QCLK output of the Bt829B obviates the need for connection to the VRDY input on the Intel740 graphics accelerator as this clock "ANDs" the ACTIVE and CLK outputs of the Bt829B together. The reference design is designed to support NTSC, PAL and SECAM. If only NTSC is desired, the circuitry including Y1 can be removed and XT1I should be tied high or low with XT10 left floating. If only PAL mode of operation is desired, XT1I should be tied high or low with XT10 floating and Y2 should be replaced with Y1. Decoupling for the component is shown at the bottom of the page.

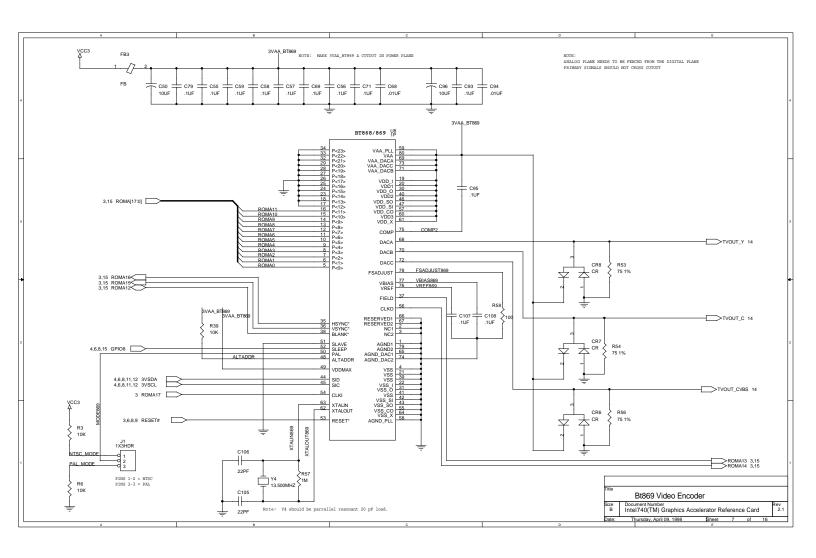

### Bt869 (Schematic Page 7)

The Bt869 power supply is generated from the VCC3 supply. Decoupling for this supply is shown at the top of the page. The component contains a 24-bit data port. The Intel740 graphics accelerator connects only to 12 of these bits. The functionality of this interface is described in the Intel740 Graphics Accelerator Datasheet. The slave input is tied to ground to place this chip in master mode. If the digital port were to be used as a VMI port, the component should be placed in slave mode. This page contains the only jumper in the design. This jumper selects which mode (PAL or NTSC) the Bt869 will operate in. The *PC* '98 specification recommends this jumper for designs where a TV may be the only output display. The ALTADDR pin is pulled high so that the device responds to an address of 8Ah. This address keeps this device from conflicting with the Bt829B's I<sup>2</sup>C address. Note that ROMA17 is wired to the CLKI pin while ROMA14 is connected to the CLKO pin. ROMA17 is also called CLKOUT and ROMA14 is called CLKIN. The Intel740's graphics accelerator CLKOUT pin corresponds to the Bt869's CLKI pin while the CLKIN pin corresponds to the CLKO pin on the Bt869. The DAC lines have special routing requirements detailed in section. These DAC lines allow the component to output S-Video and composite video.

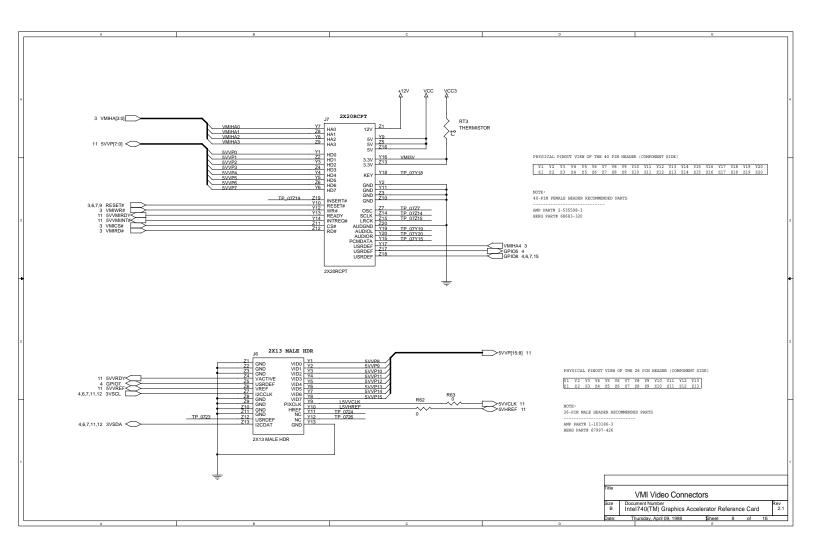

# VMI Video Connectors (Schematic Page 8)

The VMI video connectors are used for the attachment of a DVD daughter card or video capture card. The capture port is connected to the 26 pin header while the bi-directional host port is connected to the 40 pin header. The reference design uses a 2A fuse for the 3.3 volt supply to the 40 pin header. The 2A fuse is allowed for the 5 volt supply and 1A is allowed for the 12 volt supply. GPIO5 and GPIO7 come to the header for added DVD daughter card functionality control. GPIO8 is used for power down operation on the card. The I<sup>2</sup>C connections on the 26 pin header are 3.3 volt signals. Mechanical dimensions for the placement of the connectors is shown in Section 5.3, "VMI Header Placement" on page 5-2.

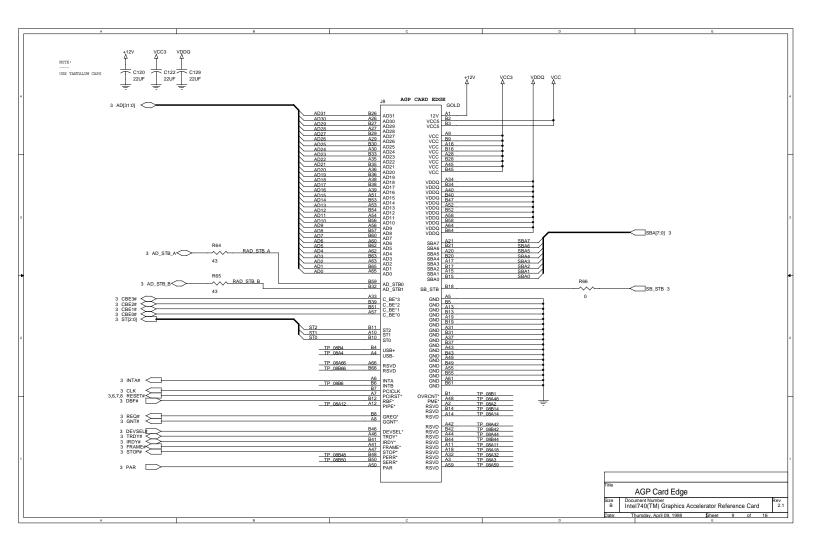

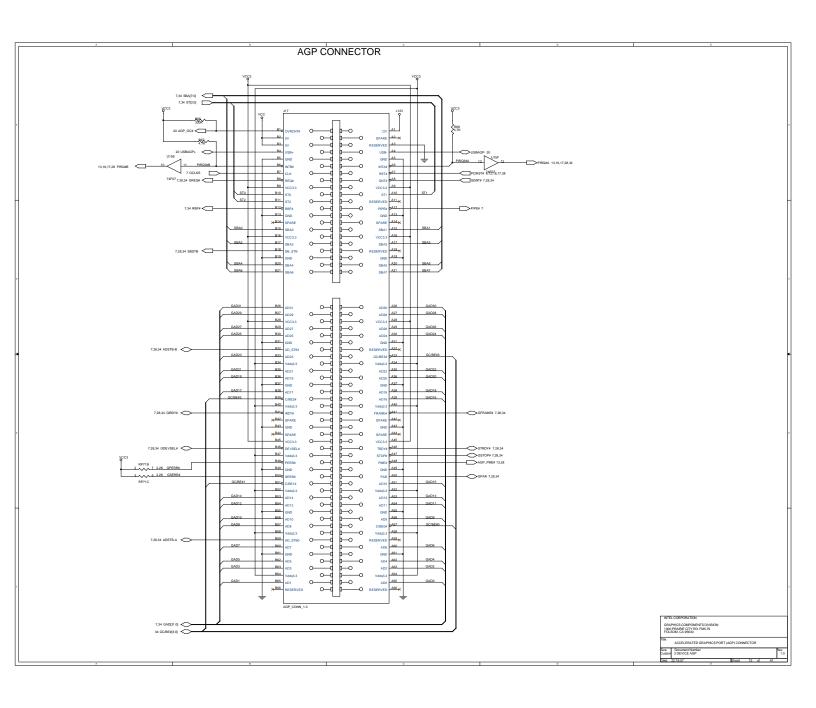

#### AGP Card Edge (Schematic Page 9)

This page details the connections of AGP. All power is derived from this connector. Using the rule of 1A per pin, the 12 volt supply is capable of supplying 1A, the 5 Volt supply is capable of supplying 2A and the 3.3 Volt supply is capable of supplying 8A.

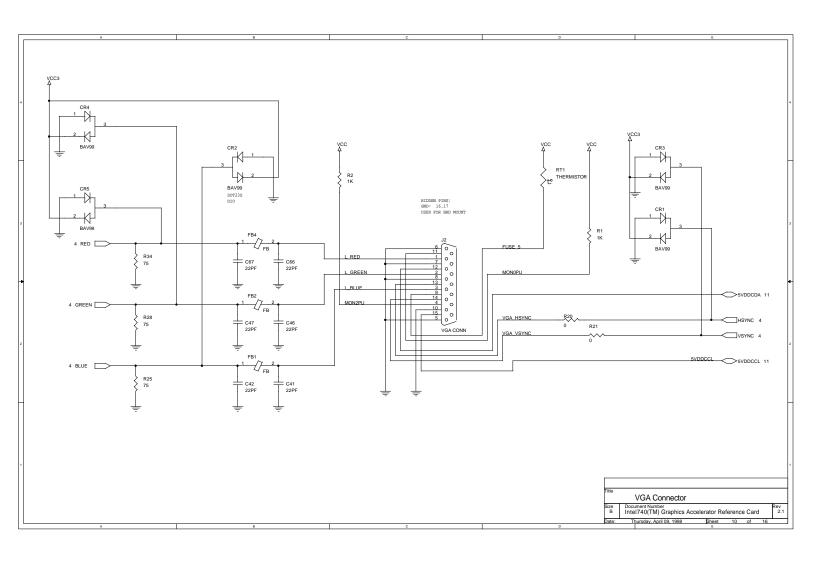

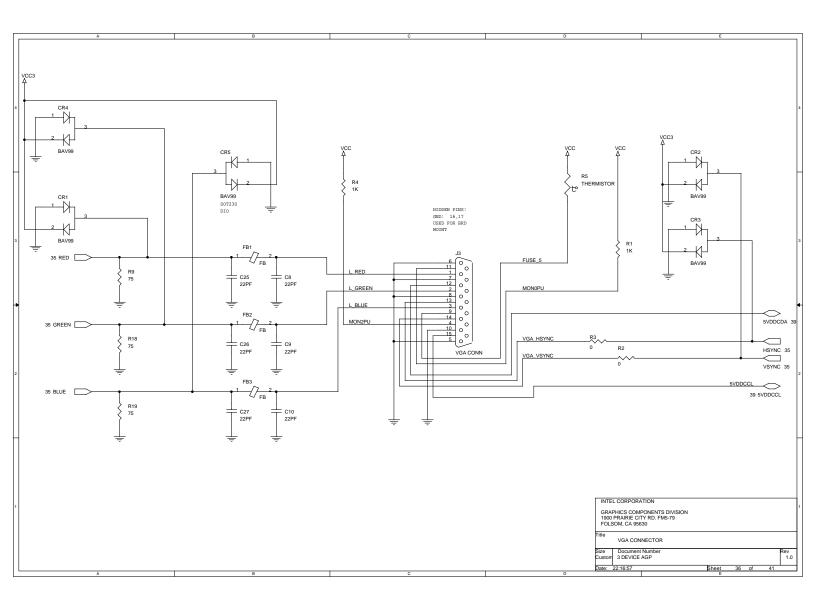

#### **VGA Connector (Schematic Page 10)**

The VGA connector provides the RGB output to a monitor. BIOS and hardware provide support for plug-and-play capability.

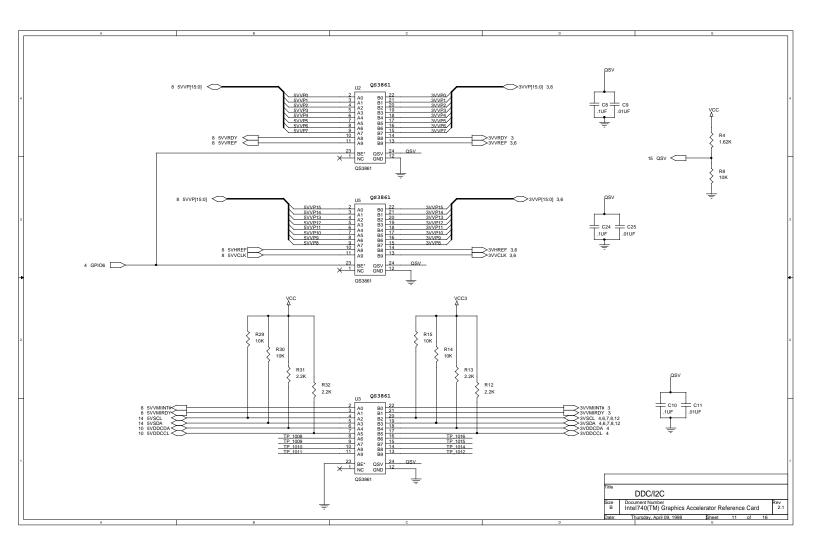

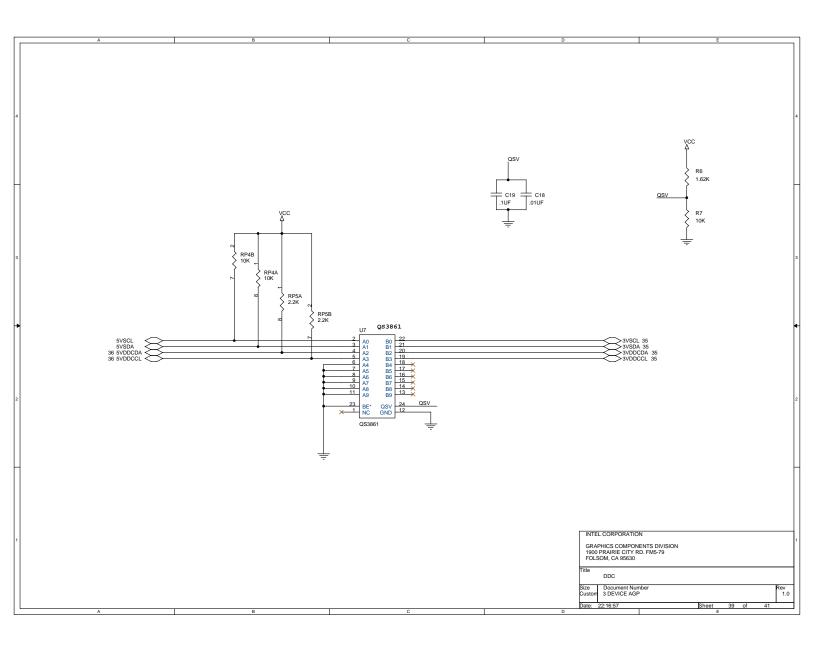

#### DDC/I<sup>2</sup>C (Schematic Page 11)

This page details the 3.3 volt/5 volt signal conversion as well as the DDC/I<sup>2</sup>C connections. To perform the voltage translation, quick switches are used. The quick switches at the top of the page serve a second function of isolating the VMI port from the Intel740 graphics accelerator. GPIO6 can tri-state this bus to preclude the possibility of contention between something connected to the VMI header and the Bt829B.

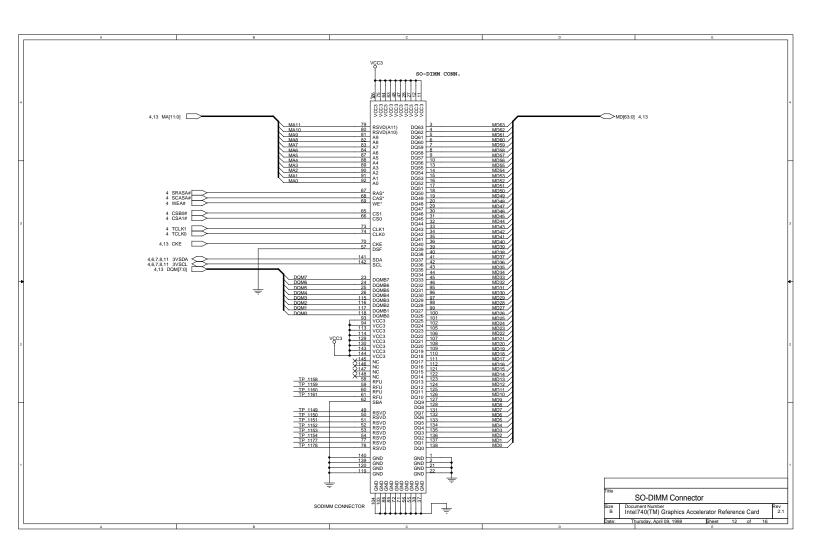

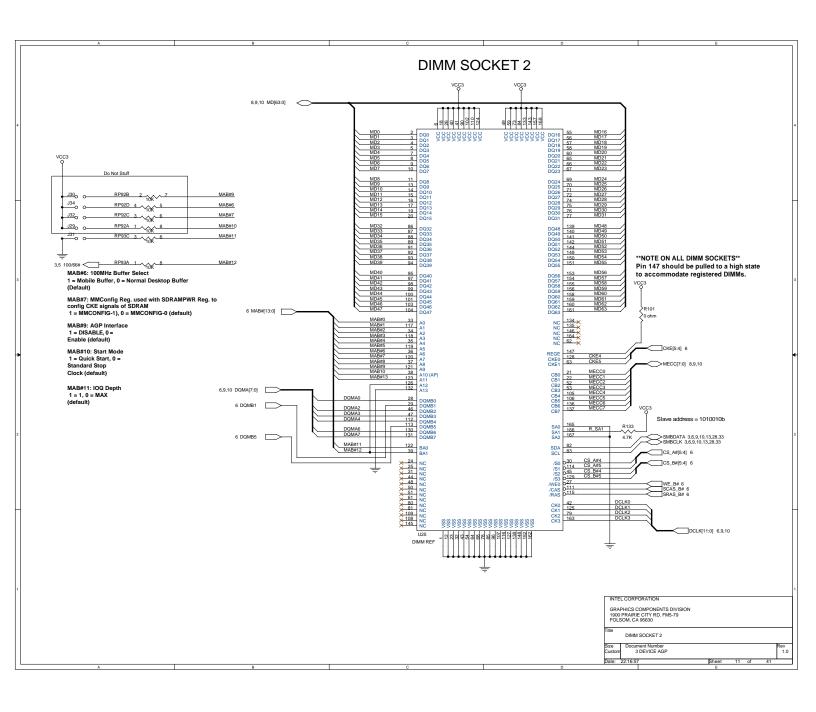

#### **SO-DIMM Connector (Schematic Page 12)**

The SO-DIMM connector shows a fairly straight forward connection to the Intel740 graphics accelerator memory signals. Note that the primary CS0 connection is tied to the Intel740 graphics accelerator CSA1# signal. The CSB0# signal is connected to CS1 on the connector. The reference design has the first row of memory down on the graphics card. The second row of memory is assumed to be placed in the SO-DIMM connector.

**Note:** It is important not to have the memory on the graphics card and memory on the SO-DIMM connector connected to the same row.

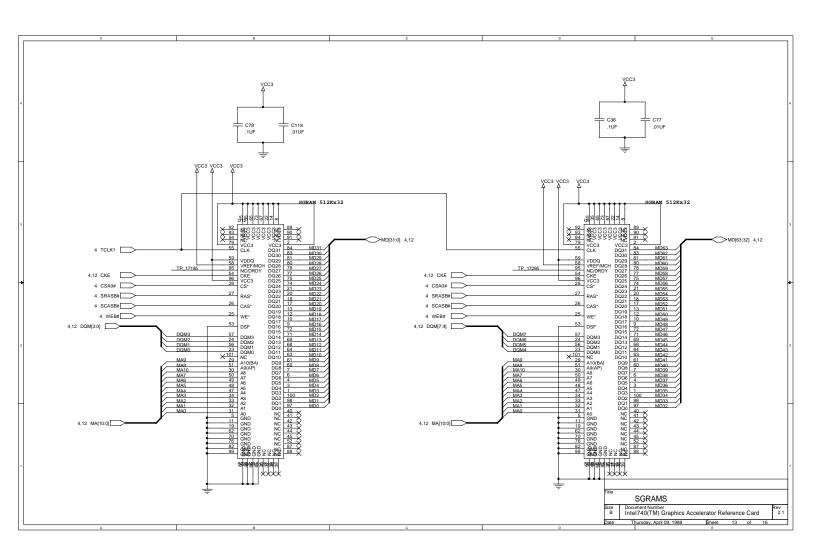

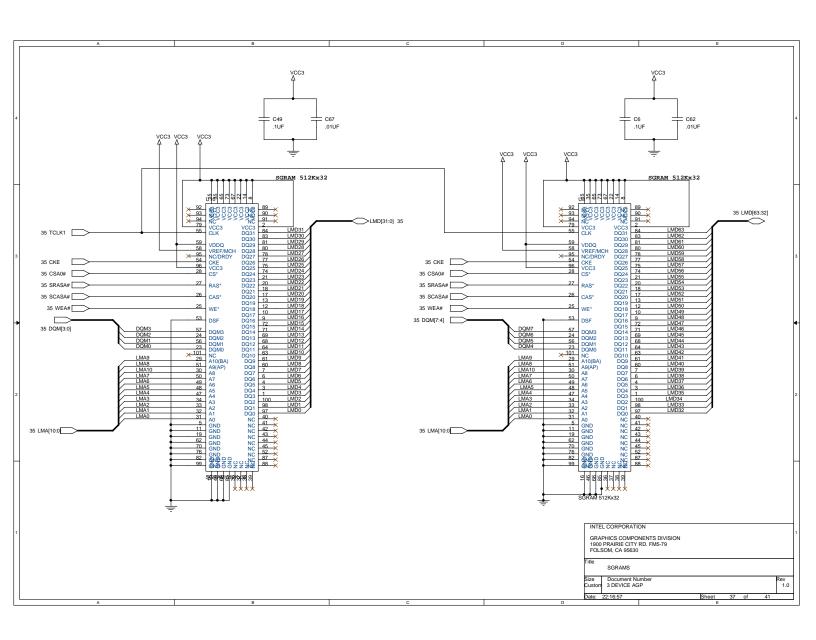

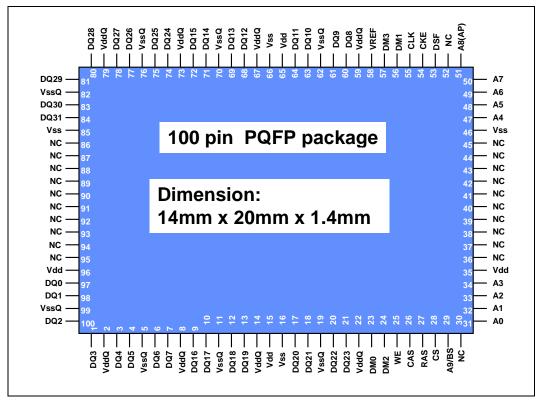

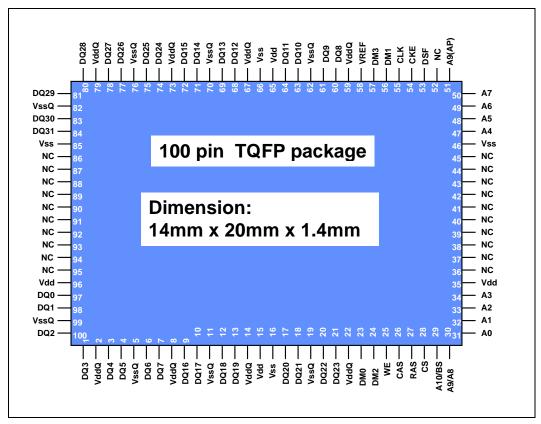

#### **SGRAMS (Schematic Page 13)**

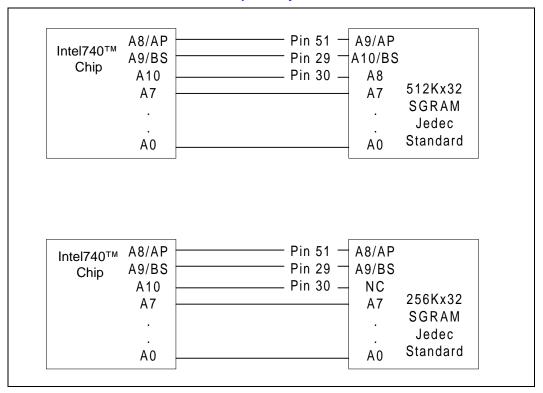

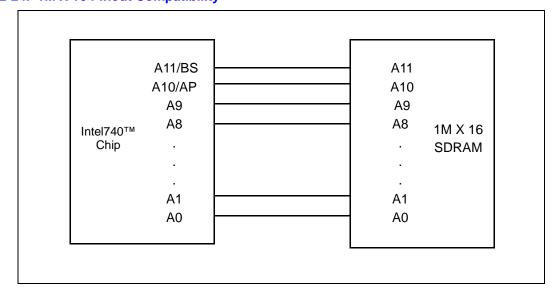

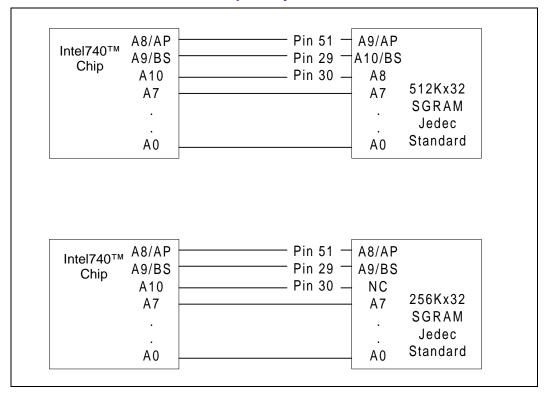

The SGRAMs shown on this page are labeled as 512Kx32. The schematic pinout is actually capable of supporting either the 512Kx32 or 256Kx32 SGRAMs. This dual-support connection is achieved through the following method. The 512Kx32 Jedec standard defines AP on pin 51 which is address 9. BS is on pin 29 and is also labeled as address 10. Address 8 is on pin 30. The Intel740 contains the AP on its address 8 pin and BS on address 9 pin. Since the 256Kx32 has AP with graphics accelerator address 8 and on pin 51 along with BS with address 9 on pin 29 and a no connect on pin 30, either the 512K or the 256K SGRAMs are capable of being supported in the same design (see Figure 2-23).

*Note:* It is important to disable the special features of SGRAM. This will make the SGRAM operate as an SDRAM, thus making it compatible with the Intel740 graphics accelerator.

Figure 2-23. 512Kx32 and 256Kx32 Pinout Compatibility

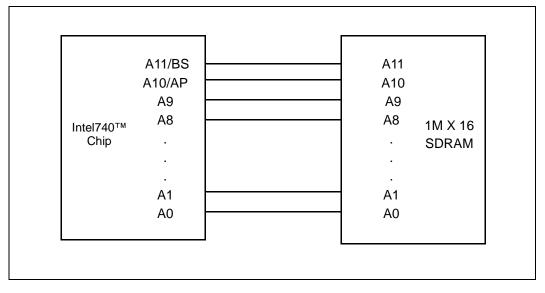

Figure 2-24. 1M X 16 Pinout Compatibility

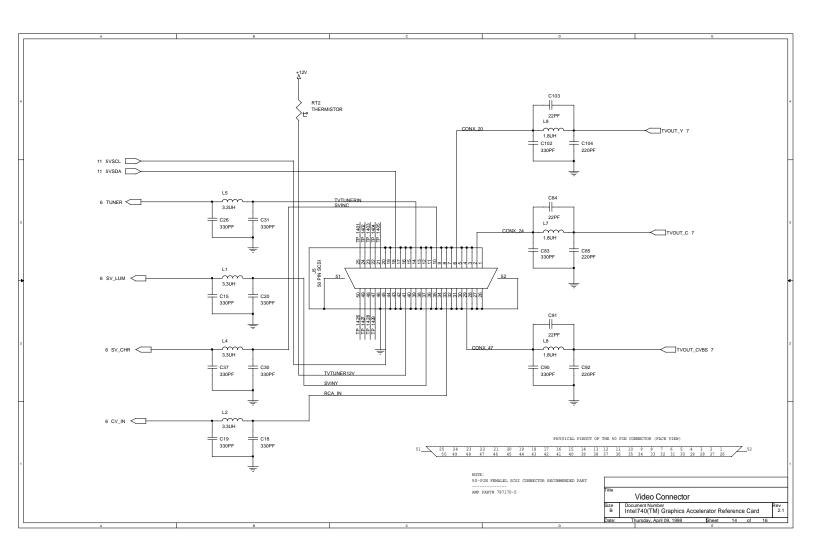

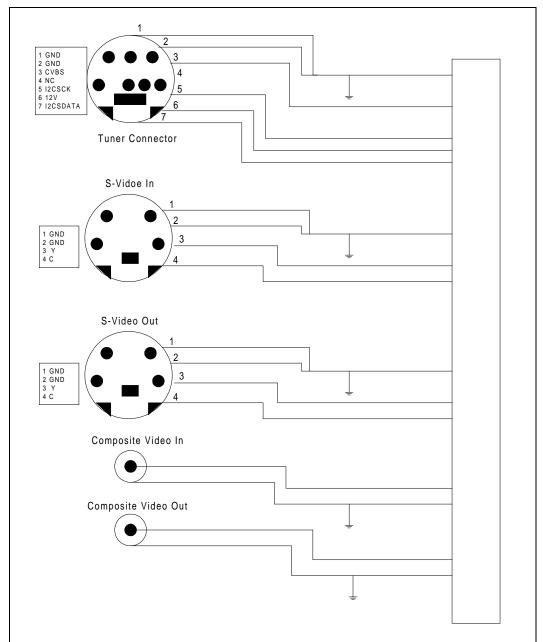

#### **Video Connector (Schematic Page 14)**

This page shows a specially designed solution to the problem of too many connectors and not enough board space. This 50 pin connector allows external hookup for a tuner, S-Video in, S-Video Out, composite video in, and composite video out. The input connections feed to the Bt829B component while the out connections come from the Bt869. Individual designs may or may not have all possible connectors and, therefore, may not need this type of solution.

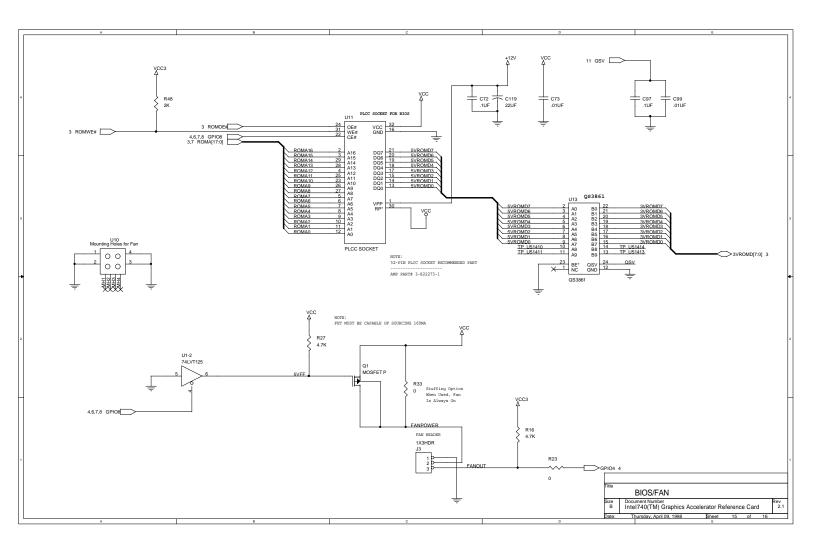

#### **BIOS/FAN** (Schematic Page 15)

This page shows the connections to the flash BIOS and fan power. The BIOS used in this design is a PLCC socket for early debug capabilities. To use less board space a TSOP package may be the preferred component. Since the selected part is a 5 volt part, the data lines are isolated from the Intel740 graphics accelerator by a level shifter.

**Note:** The Intel740 graphics accelerator does not require a fan for AGP compliant systems. These design features have been added for ease of use if the customer determines a fan is required. Refer to the Thermal Application Note and software to determine the correct thermal solution.

The fan powerdown control is done through the use of a FET. Normal operation of the fan is allowed by the 4.7 K $\Omega$  pull-up resistor (R26). If powerdown is desired, the GPIO8 pin will turn the FET off. Pin 3 of the fan header allows the fan to signal the Intel740 graphics accelerator that it has failed.

#### INTEL740(TM) GRAPHICS ACCELERATOR FULL FEATURED REFERENCE CARD

| TITLE                             |     | PAGE |

|-----------------------------------|-----|------|

| COVER SHEET                       |     | P.1  |

| BLOCK DIAGRAM                     |     | P.2  |

| INTEL740(TM) GRAPHICS ACCELERATOR | (A) | P.3  |

| INTEL740(TM) GRAPHICS ACCELERATOR | (B) | P.4  |

| VOLTAGE REGULATOR                 |     | P.5  |

| BT829B VIDEO DECODER              |     | P.6  |

| BT869 VIDEO ENCODER               |     | P.7  |

| VMI VIDEO CONNECTOR               |     | P.8  |

| AGP CONNECTOR                     |     | P.9  |

| VGA CONNECTOR                     |     | P.10 |

| VMI/DDC/I2C/FANFAIL LEVEL SHIFTER |     | P.11 |

| SO-DIMM                           |     | P.12 |

| SGRAM                             |     | P.13 |

| VIDEO CONNECTORS                  |     | P.14 |

| BIOS/FAN CONNECTOR                |     | P.15 |

| REVISION HISTORY                  |     | P.16 |

|                                   |     | P.17 |

$\stackrel{+12V}{\longleftarrow}$  +12V = 12V ANALOG UNLESS OTHERWISE SPECIFIED

$\stackrel{\text{\tiny VCC}}{\longleftarrow} \quad \text{\tiny VCC} \ = \ \text{\tiny 5V} \ \text{\tiny DIGITAL UNLESS} \ \text{\tiny OTHERWISE} \ \text{\tiny SPECIFIED}$

$\stackrel{\text{VCC3}}{\longleftarrow}$  VCC3 = 3.3V DIGITAL UNLESS OTHERWISE SPECIFIED

VCC\_CORE = VOLTAGE SUPPLIED TO THE INTEL740 CHIP CORE

GND = DIGITAL GND

THIS SPECIFICATION IS PROVEDED AS IS WITH NO WARRANTIES WHATSOURE, INCLUDING MAY WARRANTY OF MERCHANTABILITY, FITNESS FOR MAY PARTICULAR PURPOSE, OR MAY WARRANTY OTHERWISE ARISING OUT OF PROPOSAL, SPECIFICATION OR SAMPLE.

NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PRPERTY RIGHTS IS GRANED HEREIN.

INTEL DISCLAIMS ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OF INFORMATION IN THIS SPECIFICATION. INTEL DOSS NOT WARRANT OR REPRESENT THAT SUCH USE WILL NOT INFRINGE SUCH RIGHTS.

I2C IS A TWO-WIFE COMMUNICATIONS BUS/PROTOCOL DEVELOPED BY PHILIPS. SMRUS IS A SUBSET OF THE I2C BUS/PROTOCOL AND WAS DEVELOPED BY INTREL IMPLEMENTATIONS OF THE I2C BUS/PROTOCOL OR THE SMBUS BUS/PROTOCOL MAY REQUIRE LICENSES FROM VARIOUS ENTITIES, INCLUDE PHILIPS ELECTRONICS N.V. AND NORTH AMERICAN PHILIPS CORPORATION.

\*THIRD-PARTY BRANDS AND NAMES ARE THE PROPERTY OF THEIR RESPECTIVE OWNERS.

COPYRIGHT \* INTEL CORPORATION 1997

```

1.5 REVISIONS

C39, C41, C42, & C44 CHANGED TO 15PF ON P.5, NO PACKAGE SIZE CHANGE NEEDED

SIGNALS XITLDA AND XITCAP RELOCATED SINCE XIAL FILTRES CHANGED ON P.5

L3 AND L4 ON P.5 CHANGED TO 4.70H NAD LOCATION IN NITAL FILTRE CIRCUIT CHANGED

PIN 36, 37, 80, & BS CONNECTED TO VCCI SINTERIO OF VCC ON THE BETSAULT ON P.5

R2D ON P.5 NOW COMMINICATE TO VCCI SINTERIO OF VCC ON THE BETSAULT ON P.5

R2D ON P.5 NOW COMMINICATE TO VCCI SINTERIO OF VCC ON THE BETSAULT ON P.5

THIS REQUIRED A PACKAGE SIZE CHANGED FROM 905 TO 1206.

VCC CONNECTION TO PIN 59 OF BETSSUE (P.5) DELETED. WIRE LEFT OFEN AND RENAMED TH_0559.

REMOVED NOTE NEAR PIN 59 OF BETSSUE (P.5) WHICH STATED THE TO ANNOL OF ENCE

DELETED R13, R18 & R19 FROM P.5 OF SCHEWATICS.

SIGNAL NAME SEGMENT REMOVED FROM P.14

SIGNAL NAME SEGMENT REMOVED FROM P.14

SIGNAL NAME SEGMENT REMOVED FROM P.14 AND CONNECTED TO PIN 25 OF THE ZXI3 HER ON P.7

ROWNER SIGNAL NOL LONGER USES 74LVT125 ON P.14 BUT CONNECTED DIRECTLY TO BIOS FIN 31

PULL-UP RESISTOR TO VCC3, R13, ADDED ON P.14 AND CHANGED TO GPOIT

SIGNAL NAME TO,0709 EMBOVED FROM P.16

SIGNAL NAME TO,0709 EMBOVED FROM P.16

SIGNAL NAME CHANGED TO DIFSSE ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESS, RESEARCH FOR P.2 CHANGED TO VIDEO EMBODED

SIGNAL NAME (CHANGED TO DIFSSE ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESS, RESEARCH FOR P.6

BRESSALV NAME CHANGED TO DIFSSE ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESS, RESEARCH FOR P.6

BRESSALV NAME CHANGED TO DRESS ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESS, RESEARCH FOR P.6

BRESSALV NAME CHANGED TO DRESS ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESS, RESEARCH FOR P.6

BRESSALV NAME CHANGED TO DRESS ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESSALV NAME CHANGED TO DRESS ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESSALV NAME CHANGED TO DRESS ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESSALV NAME CHANGED TO DRESS ON P.1 AT 2 PLACES AND P.5 AT 2 PLACES

BRESSALV NAME CHANGED TO DRESSAULT TO DRESSAULT TO DRESSAULT TO DRESSAULT TO THE TO THE TOTAL THE TOTAL TO THE TOTAL TO TH

PULL-DOWN REISITOR ON GPIO4 REMOVED

SIGNAL GFIO8 ADDED TO VMI 2220 HEADER ON PIN 218

SIGNAL GFIO8 ADDED TO VMI 2220 HEADER ON PIN 218

OF VMI INTELLY OF THE SECOND OF THE

MEMORY ADDRESSES 8,9 AND 10 FROM INTEL740(TM) GRAPHICS ACCELERATOR CONNECTED TO 8,9 AND 10 OF SODIME CONNECTOR, RESPECTIVELY POWER SUPPLY VIDOJS CHANGED TO VID 1.7 REVELSION.

REMOVED 1UF CAP BETWEEN PIN 1 AND GND OF LT1575 ON P.4

ADDED 1UF CAP TO VCC3 NEAR PIN 1 OF HEXFET ON P.4

REPLACED 220UF CAP WITH 100UF CAP ON P.4

LAYOUT NOTE ADDED TO P.4

1.4 REVISIONS

SIGNAL NAMES L RED, L GREEN L BLUE CHANGED TO L RED, L GREEN AND L BLUE, RESPECTIVELY, ON P.9 SIGNAL NAMES AND STREET, AND VOA VERNEZ ON P.9 SIGNAL NAMES AND STREET, AND VOA VERNEZ ON P.9 SIGNAL NAMES AND VOA VERNEZ ON VERNEZ ON VERNEZ ON P.9 SIGNAL NAMES AND VOA VERNEZ ON VERNEZ

AVCC CHANGED TO VCC GLOBALLY

ON HIDDEN PINS OF BTS29ALV REMOVED FROM P.5

PROPERTY OF BT829ALV ADDED, HIDDEN PINS DESIGNATED AS ANALOG_GND CONNECT TO GND

POWER NOTES CHANGED ON P.1 TO REFLECT AGND AND AVCC REMOVAL

THE 4 GND RINGS OF FAN MOUNTING HOLES BROUGHT OUT EXTERNALLY P.14 THE 4 NC MOUNTING HOLES ARE STILL LEFT AS HIDDEN

1.6 REVISIONS

1.42

1.42M RESISTOR ABUSE TO GRIGA SINE ON P.14

INSTITUTED ON MERISTOR ADDED RETWEST BASH AND SOURCE OF PROSPET ON P.14

PINOUT CHANGED ON LITTLE 140 (TM) GRAPHICS ACCELERATOR ON PINS SPARE2, SPARE1, LEFT, VSYNC,

RENYC, VEEP, AND VCLK.

NO OTHER PIN'S ARE H25, H26, J23, J25, J26, L23, & L24 RESPECTIVELY ON P.3.

NO OTHER PINS AFFECTS.