# **Table of Contents**

| 1. SiS5513 PCI System I/O (PSIO)                      | 1    |

|-------------------------------------------------------|------|

| 1.1. SiS5513 Overview                                 | 1    |

| 1.1.1. Features                                       | 1    |

| 1.1.2. Functional Block Diagram                       | 3    |

| 1.2. Functional Description                           | 4    |

| 1.2.1. PCI Bridge                                     | 4    |

| 1.2.2. ISA Bus Controller                             | 5    |

| 1.2.3. DMA Controller                                 | 6    |

| 1.2.4. Interrupt Controller                           | 7    |

| 1.2.5. Timer/Counter                                  | 8    |

| 1.2.6. Built-in RTC                                   | 8    |

| 1.2.7. Built-in PCI Master/Slave IDE                  | 8    |

| 1.2.8. Built-in Keyboard Controller                   | . 14 |

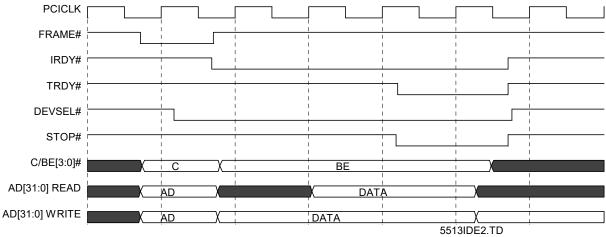

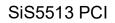

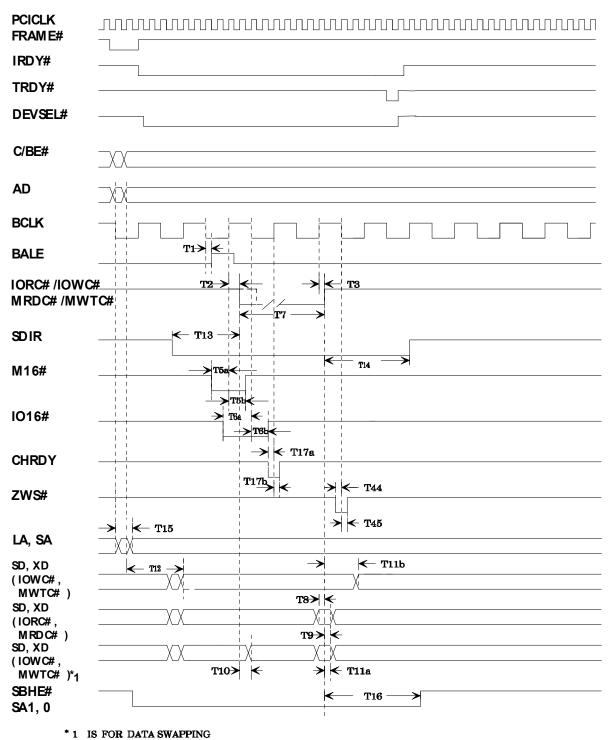

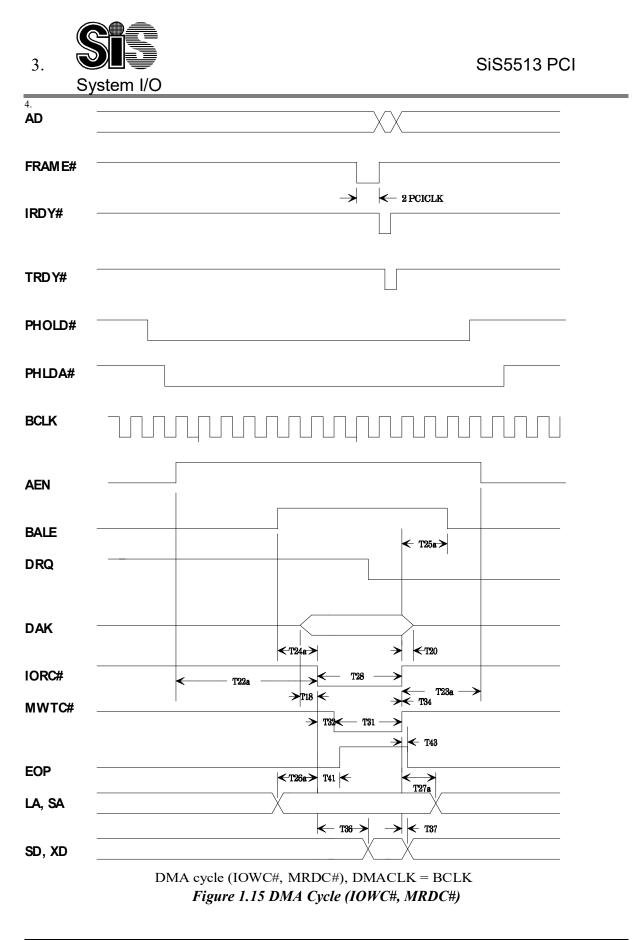

| 1.2.9. Timing Diagram                                 | 17   |

| 1.3. Register Description                             | 21   |

| 1.3.1. PCI Configuration Register (PCI to ISA Bridge) |      |

| 1.3.2. Non-Configuration Registers                    | . 36 |

| 1.3.3. ISA Internal Register                          | . 39 |

| 1.3.4. PCI IDE Configuration Registers                | . 44 |

| 1.3.5. PCI Bus Master IDE Registers                   | 50   |

| 1.4. Pin Assignment and Description                   | 52   |

| 1.4.1. Hardware Trap                                  | . 52 |

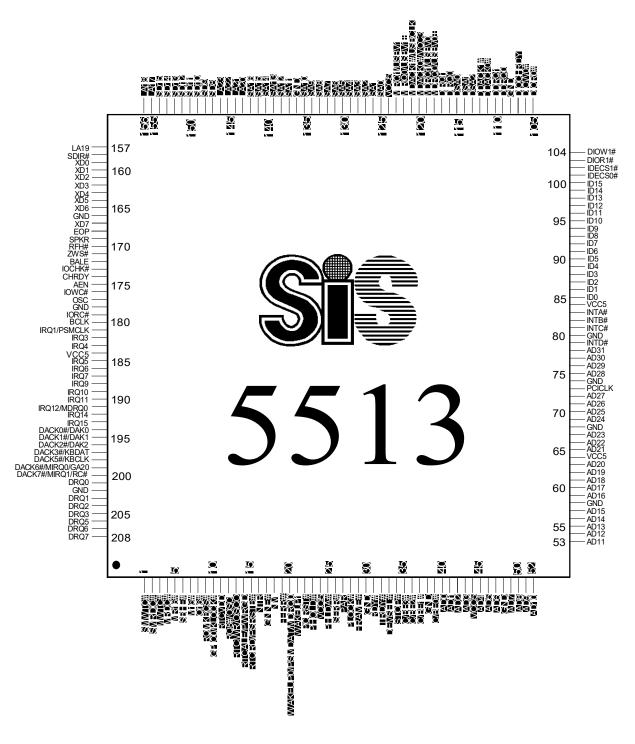

| 1.4.2. Pin Assignment                                 | . 54 |

| 1.4.3. Pin Listing ( # means active low)              | . 55 |

| 1.4.4. Pin Description                                | . 56 |

| 1.5. Electrical Characteristics                       | . 65 |

| 1.5.1. Absolute Maximum Ratings                       | 65   |

| 1.5.2. DC Characteristics                             | 65   |

| 1.5.3. AC Characteristics                             | 66   |

| 1.5.4. AC Timing Diagram                              | 70   |

| 2. Mechanical Dimension                               | 77   |

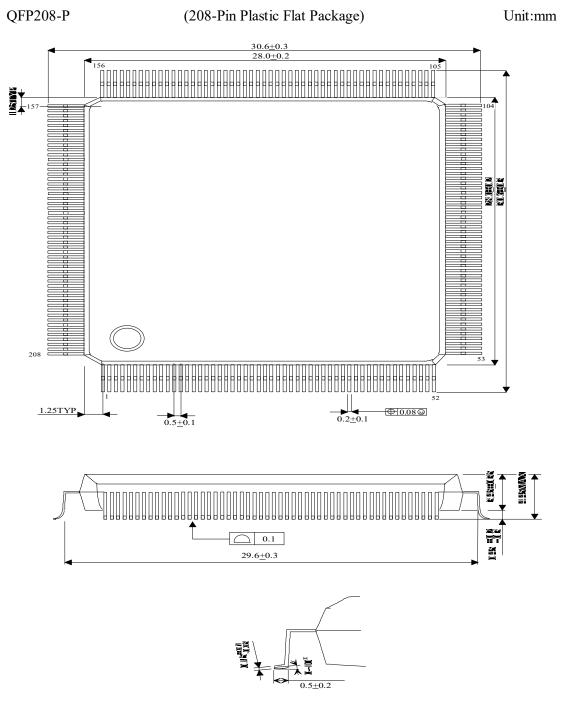

| 2.1. SiS5513 (208 pins)                               | , 77 |

| 3. COPYRIGHT NOTICE                                   | 78   |

Ι

# 1. SiS5513 PCI System I/O (PSIO)

# 1.1. SiS5513 Overview

1.1.1. Features

# • Integrated Bridge Between PCI Bus and ISA Bus

- Translates PCI Bus Cycles into ISA Bus Cycles

- Translates ISA Master or DMA Cycles into PCI Bus Cycles

- Provides a Dword Post Buffer for PCI to ISA Memory cycles

- Two 32 bit Prefetch/Post Buffers Enhance the DMA and ISA Master Performance

- Fully Compliant to PCI 2.1 (5513C)

# • Enhanced DMA Functions

- 8-, 16- bit DMA Data Transfer

- ISA compatible, and Fast Type F DMA Cycles

- Two 8237A Compatible DMA Controllers with Seven Independent Programmable Channels

- Provides the Readability of the two 8237 Associated Registers

# • Built-in Two 8259A Interrupt Controllers

- 14 Independently Programmable Channels for Level- or Edge-triggered Interrupts

- Provides the Readability of the two 8259A Associated Registers

# • Three Programmable 16-bit Counters compatible with 8254

- System Timer Interrupt

- Generates Refresh Request

- Speaker Tone Output

- Provides the Readability of the 8254 Associated Registers

- Built-in Keyboard Controller

- Hardwired Logic Provides Instant Response

- Supports PS/2 Mouse

- Support Hot Key "Sleep" Function

- Built-in Real Time Clock(RTC) with 256B CMOS SRAM

- Fast PCI IDE Master/Slave Controller

- PCI Local Bus Specification V2.1 Compliance

- Supports PCI Bus Mastering

- Plug and Play Compatible

- Supports Scatter and Gather

- Supports Dual Mode Operation Native Mode and Compatibility Mode

- Supports IDE PIO Timing Mode 0, 1, 2 of ANSI ATA Specification

- Supports Mode 3 and Mode 4 Timing Proposal on Enhanced IDE Specification

1

- Supports Multiword DMA Mode 0, 1, 2

- Separate IDE Bus

- Two 8x32-bit FIFO for PCI Burst Read/Write Transfers.

- Universal Serial Bus Controller(5513C)

- Host/Hub Controller

- Two USB ports

- On-Board Plug and Play Support

- Two Steerable DMA Channels

- Two Steerable Interrupts

Preliminary V2.0 November 22, 1995

- One Programmable Chip Select

- Supports the Reroutibility of the four PCI Interrupts

- Supports Flash ROM

- 208-Pin PQFP

- 0.5 µm CMOS Technology

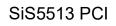

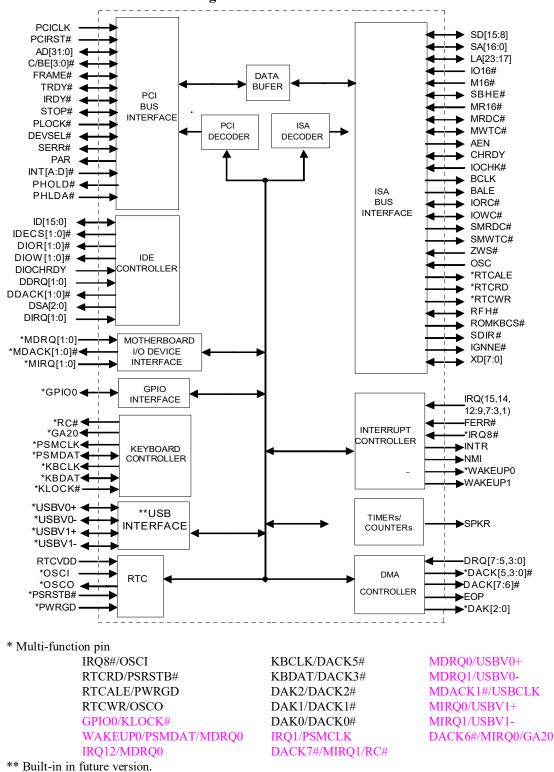

#### 1.1.2. Functional Block Diagram

| Figure | 1.1 | SiS5513 | Functional | Block | Diagram |

|--------|-----|---------|------------|-------|---------|

|--------|-----|---------|------------|-------|---------|

| Preliminary V2.0 | November 22, 1995 | 3 | Silicon Integrated Systems Corporation |

|------------------|-------------------|---|----------------------------------------|

# 1.2. Functional Description

The SiS5513 is a highly integrated PCI/ISA system I/O (PSIO) device that integrates all the necessary system control logic used in PCI/ISA specific applications.

The SiS5513 consists of

- 1. A PCI bridge that translates PCI cycles onto ISA bus

- 2. ISA master/DMA device cycles onto PCI bus

- 3. A seven-channel programmable DMA Controller

- 4. Sixteen-level programmable interrupt controller

- 5. A programmable timer with three counters

- 6. A built-in RTC with 256 bytes CMOS SRAM

- 7. A on-board Plug and Play port

- 8. A built-in PCI master/slave IDE interface.

In 5513B, the ISA compatible keyboard controller is also implemented with the enhancement of hotkey and PS/2 mouse support. Besides, two Dword buffers are employed to enhance the performance of the DMA/ISA master cycles. Also with the aid of the two Dword buffer, the fast type F DMA cycle is also supported.

The USB function will be supported in 5513C.

Since 5513 includes a PCI to ISA bridge and a PCI IDE, it naturally becomes a multi-function device. The PCI/ISA bridge is defined as a function 0 device while PCI IDE is a function 1 device. The following two examples describe how to write register XX in PCI to ISA bridge configuration space and register YY in PCI IDE configuration space.

# Example 1: MOV EAX, 800010XXh OUT 0CF8h, EAX MOV AL, data

| OUT | 0CFDh, AL |

|-----|-----------|

|     |           |

| EAX, 800011YYh |

|----------------|

| 0CF8h, EAX     |

| AL, data       |

| 0CFDh, AL      |

|                |

# 1.2.1. PCI Bridge

The SiS5513 PCI bus interface provides the interface between PSIO and the PCI bus. It contains both PCI master and slave bridges to the PCI bus. When PHLDA# is asserted, the master bridge translates the ISA master, DMA cycles or PCI IDE Master cycles onto the PCI bus based on the decoding status from ISA address decoder. When PHLDA# is negated, the slave bridge accepts these cycles initiated on the PCI bus targeted to the PSIO internal registers or ISA bus , and then

Preliminary V2.0 November 22, 1995 4 Silicon Integrated Systems Corporation

forwards the cycles to the ISA Bus Interface that further translates them onto the ISA Bus. The PCI address decoder provides the information on which the slave bridge depends to respond and process the cycle initiated by PCI Masters.

# PCI Slave Bridge

As a PCI slave, PSIO responds to both I/O and memory transfers. PSIO always target-terminates after the first data phase for any bursting cycle.

SiS5513 always converts the single interrupt acknowledge cycle (from 5511) into two cycles that the internal 8259 pair can respond to.

The PSIO is assigned as the subtractive decoder in the Bus 0 of the SiS PCI/ISA system by accepting all accesses not positively decoded by some other agent. In reality, the PSIO only subtractively responds to low 64K I/O or low 16M memory accesses. PSIO also positively decodes I/O addresses for internal registers, and BIOS memory space by asserting DEVSEL# on the medium timing.

# PCI Master Bridge

As long as PHLDA# is asserted, the PCI master bridge on behalf of DMA devices or ISA Masters starts to drive the AD bus, C/BE[3:0]# and PAR signals. When MRDC# or MWTC# is asserted, the PSIO will generate FRAME#, and IRDY# to PCI bus if the targeted memory is not on the ISA side. The valid address and command are driven during the address phase, and PAR is asserted one clock after that phase. PSIO always activated FRAME# for 2 PCLKs because it does not conduct any bursting cycle.

The ISA address decoder is used to determine the destination of ISA master or DMA devices. This decoder provides the following options as they are defined in configuration registers 48 to 4B.

- a. Memory: 0-512K

- b. Memory: 512K-640K

- c. Memory: 640K-768K(video buffer)

- d. Memory: 768K-896K in eight 16K sections(Expansion ROM)

- e. Memory: 896K-960K(lower BIOS area)

- f. Memory: 1M-XM-16M within which a hole can be opened. Access to the hole is not forwarded to PCI bus.

- g. Memory:>16Mb automatically forwards to PCI.

# **1.2.2. ISA Bus Controller**

The SiS5513 ISA Bus Interface accepts those cycles from PCI bus interface and then translates them onto the ISA bus. It also requests the PCI master bridge to generate PCI cycle on behalf of DMA or ISA master. The ISA bus interface thus contains a standard ISA Bus Controller and a Data Buffering logic. IBC provides all the ISA control, such as ISA command generation, I/O recovery control, wait-state insertion, and data buffer steering. The PCI to/from ISA address and data bus bufferings

Preliminary V2.0 November 22, 1995 5 Silicon Integrated Systems Corporation

are also all integrated in SiS5513. The SiS5513 can directly support six ISA slots without external data or address buffering.

Standard ISA bus refresh is requested by Counter 1, and then performed via the IBC. IBC generates the pertinent command and refreshes address to the ISA bus. Since the ISA refresh is transparent to the PCI bus and the DMA cycle, an arbiter is employed to resolve the possible conflicts among PCI cycles, refresh cycles, and DMA cycles.

# 1.2.3. DMA Controller

The SiS5513 contains a seven-channel DMA controller. The channel 0 to 3 is for 8-bit DMA devices while channel 5 to 7 is for 16-bit devices. The channels can also be programmed for any of the four transfer modes, which include single, demand, block, and cascade. Except in cascade mode, each of the three active transfer modes can perform three different types of transfers, which include read, write, and verify. The address generation circuitry in SiS5513 can only support 24-bit address for DMA devices.

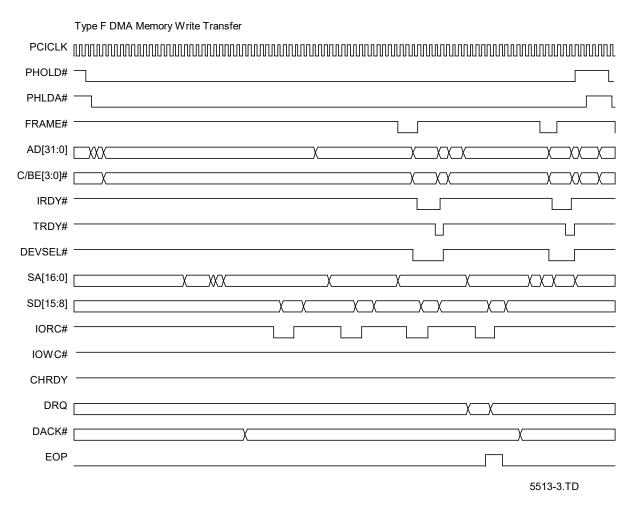

Besides, there is another function: Type F DMA. The type F DMA is composed by two parts, one is the prefetch\postwrite buffer from the ISA bus to the PCI bus and the type F DMA timing controller. We will explain these two parts separately.

# **Prefetch/postwrite buffer**

This prefetch/postwrite buffer is used for the memory cycles of the DMA controllers and the ISA bus masters and is of two double word width. Those memory cycles that are forwarded to the PCI bus are processed by this buffer. The two-double word is further divided into two parts, each is of one double word width. These two parts act as a ring buffer and each can communicate with the PCI bus and the ISA bus independently.

The buffer is triggered by the memory commands on the ISA bus regardless of the sources of the commands. When a memory read command comes, the buffer begins to prefatch a double word from the PCI bus and then disassembles the data onto the ISA bus. At the same time, the buffer begins to prefatch anther double word from the PCI bus. Whenever one of the two double word has disassembles all its data to the ISA bus, then the buffer will prefatch another double word from the PCI bus, at the same time the buffer switch the data of the other double word to the ISA bus.

When one of the following conditions occurs, the data in the buffer is all invalidated; the address goes beyond the double word range, the following command is memory write cycle, and the bus ownership of the ISA bus changes.

When a memory write command comes, the buffer latches the data and the address, and at the same time, sets the byte enable. That is to say, the buffer performs byte\word merge during the memory write cycles. Whenever the data has filled a double word then the buffer begins to flush the double word to the PCI bus and at the same time, switches the other double of the buffer to latch the data of the following memory write cycle from the ISA bus.

Preliminary V2.0 November 22, 1995 6 Silicon Integrated Systems Corporation

When one of the following conditions occurs, the data in the buffer must be flushed onto the PCI bus; the buffer is full, the address comparison fails, the following command is a memory read command, and the bus ownership of the ISA bus changes.

# Type F DMA Timing Controller

The type F DMA timing controller controls the timings of the DMA commands, the DMA wait states and the DMA clock. This controller must cooperate with the prefatch/postwrite buffer described above. When the DACK of the DMA channel that is programmed to perform type F DMA transfers is active, the timing controller first switch the DMA clock from the half of the system clock to the system clock. During the transfer, the timing controller will disable the default wait state of the DMA controller, only active all the I/O commands and shorten the pulse width of the I/O commands to one system clock. The wait states are controlled by the prefetch\postwrite buffer.

# 1.2.4. Interrupt Controller

The SiS5513 provides an ISA compatible interrupt controller that incorporates the functionality of two 82C59 interrupt controllers. The two controllers are cascaded so that 14 external and two internal interrupts are supported. The master interrupt controller provides IRQ<7:0> and the slave one provides IRQ<15:8>. The two internal interrupt are used for internal functions only and are not available externally. IRQ2 is used to cascade the two controllers together and IRQ0 is used as a system timer interrupt and is tied to interval Counter 0. The remaining 14 interrupt lines are available for external system interrupts.

| Priority | Label | Controller | Typical Interrupt Source                          |

|----------|-------|------------|---------------------------------------------------|

| 1        | IRQ0  | 1          | Timer/Counter 0 Out                               |

| 2        | IRQ1  | 1          | Keyboard                                          |

| 3-10     | IRQ2  | 1          | Interrupt from Controller 2                       |

| 3        | IRQ8# | 2          | Real Time Clock                                   |

| 4        | IRQ9  | 2          | Expansion bus pin B04                             |

| 5        | IRQ10 | 2          | Expansion bus pin D03                             |

| 6        | IRQ11 | 2          | Expansion bus pin D04                             |

| 7        | IRQ12 | 2          | Expansion bus pin D05                             |

| 8        | IRQ13 | 2          | Coprocessor Error Ferr#                           |

| 9        | IRQ14 | 2          | Fixed Disk Drive Controller Expansion bus pin D07 |

| 10       | IRQ15 | 2          | Expansion bus pin D06                             |

| 11       | IRQ3  | 1          | Serial port 2, Expansion Bus B25                  |

| 12       | IRQ4  | 1          | Serial port 1, Expansion Bus B24                  |

| 13       | IRQ5  | 1          | Parallel Port 2, Expansion Bus B23                |

| 14       | IRQ6  | 1          | Diskette Controller, Expansion Bus B22            |

| 15       | IRQ7  | 1          | Parallel Port, Expansion Bus B21                  |

#### Table 1-1

In addition to the ISA features, the ability to do interrupt sharing is included. Two registers(ECLR) located at 4D0h and 4D1h are defined to allow edge or level sense selection to be made on an

Preliminary V2.0 November 22, 1995 7 Sili

Silicon Integrated Systems Corporation

SiS5513 PCI

individual channel by channel basis instead of on a complete bank of channels. Note that the default of IRQ0, IRQ1, IRQ2, IRQ8# and IRQ13 is edge sensitive, and can not be programmed. Also, each PCI Interrupt(INTx#) can be programmed independently to route to one of the eleven ISA compatible interrupts(IRQ<7:3>, IRQ<15:14>, and IRQ<12:9>) through configuration registers 41h to 44h.

# 1.2.5. Timer/Counter

The SiS5513 contains 3 channel counter/timer that is equivalent to those found in the 82C54 programmable interval timer. The counters use a division of 14.31818MHz OSC input as the clock source. The outputs of the timers are directed to key system functions. Counter 0 is connected to the interrupt controller IRQ0 and provides a system timer interrupt for a time-of-day, diskette time-out, or the other system timing function. Counter 1 generates a refresh-request signal and Counter 2 generates the tone for the speaker.

# 1.2.6. Built-in RTC

The 5513 incorporates a real-time clock and system configuration memory. The RTC combines:

- A complete time-of-day clock with alarm

- 100 year calendar

- Programmable periodic interrupt

- 14 bytes of clock and control registers and 242 bytes of lower power general purpose SRAM

The method of accessing the upper 128 bytes of CMOS SRAM is to write 50h to I/O port 22h and then setting bit 3 of I/O port 23h.

# 1.2.7. Built-in PCI Master/Slave IDE

Design of the built-in PCI IDE follows the PCI Local Bus Specification and PCI IDE Controller Specification.

Both primary and secondary channel may be programmed as Native mode or Compatibility mode via the Class Code Field in the controller's Configuration Space register.

In Compatibility mode, the interrupt requests for channel 0 and channel 1 are rerouted to IRQ 14 and IRQ 15 of the built-in Interrupt Controller.

Following tables illustrate the accessing methods to the I/O ports in compatibility mode:

**Table 1-2 Primary Channel**

|      |                |         | READ   |        | WRITE  |        |

|------|----------------|---------|--------|--------|--------|--------|

| PORT | <b>IDECS1#</b> | IDECS0# | DIOR0# | DIOR1# | DIOW0# | DIOW1# |

| 1F0  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F1  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F2  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F3  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F4  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F5  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F6  | 1              | 0       | 0      | 1      | 0      | 1      |

| 1F7  | 1              | 0       | 0      | 1      | 0      | 1      |

| 3F6  | 0              | 1       | 0      | 1      | 0      | 1      |

# **Table 1-3 Secondary Channel**

|      |                |                | READ   |        | WRITE  |        |

|------|----------------|----------------|--------|--------|--------|--------|

| PORT | <b>IDECS1#</b> | <b>IDECS0#</b> | DIOR0# | DIOR1# | DIOW0# | DIOW1# |

| 170  | 1              | 0              | 1      | 0      | 1      | 0      |

| 171  | 1              | 0              | 1      | 0      | 1      | 0      |

| 172  | 1              | 0              | 1      | 0      | 1      | 0      |

| 173  | 1              | 0              | 1      | 0      | 1      | 0      |

| 174  | 1              | 0              | 1      | 0      | 1      | 0      |

| 175  | 1              | 0              | 1      | 0      | 1      | 0      |

| 176  | 1              | 0              | 1      | 0      | 1      | 0      |

| 177  | 1              | 0              | 1      | 0      | 1      | 0      |

| 376  | 0              | 1              | 1      | 0      | 1      | 0      |

In Native mode, the interrupt requests of both channels share the same PCI interrupt pin. The interrupt pin may be rerouted to any one of eleven ISA compatible interrupts (IRQ[15:14], IRQ[12:9], and IRQ[7:3]) via programming 5513 Configuration Register 63h.

Meanwhile, accessing of the I/O ports are via the addresses programmed in Base Address Registers 10h, 14h, 18h and 1Ch in IDE configuration space.

While serving as a bus master device, the IDE controller may transfer data between IDE devices and main memory directly. By performing the DMA transfer, IDE offloads the CPU and improves system performance. Bus master DMA programming is according to the information specification "Programming Interface for Bus Master IDE Controller".

Master PIO mode, which means that PCI site is running in Master mode, while the IDE site is running in PIO mode, is also supported here. Master PIO mode for Primary Channel and Secondary Channel may be enabled via IDE configuration register 4A, bit 4 and bit 3.

Under master mode, IDE controller shares the same request (PHOLD#) and acknowledge (PHLDA#) signals with PSIO via a high performance hidden arbitration scheme.

The built-in IDE controller contains PCI configuration header and registers to meet PCI specifications. The internal PCI IDE supports PCI type 0 configuration cycles of configuration mechanism #1.

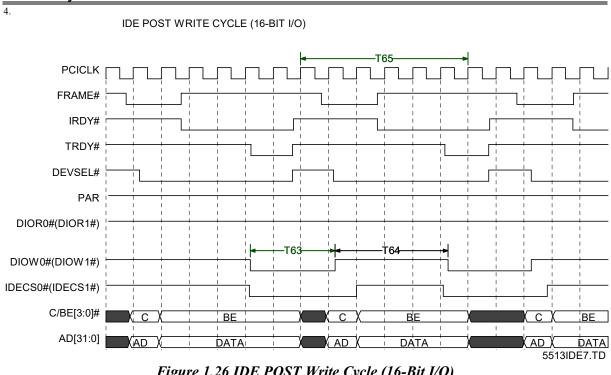

Proper cycle timing is generated to fit PCI Bus speed and different modes of IDE drive. All cycle timing can be controlled by software programming.

As a slave device, IDE decodes and interprets PCI cycles and generate signals to start and terminate IDE cycles. This block responds only to cycles that belong to IDE I/O address space. It supports both 16-bit and 32-bit I/O data transfer at address 1F0/170. All other IDE registers read or write operations are 8-bit only.

There are four  $8 \times 32$  bits FIFOs, which support post write and pre-fetch operations, in the internal PCI IDE. Prefetch and post write operations for each channel may be activated via Register 4B in IDE Configuration Space. The two FIFOs may operate independently.

The posted write operations can enhance the transfer rate of the PCI Bus interface to IDE interface write operation by decoupling the wait-states effect from the slower IDE side to the faster PCI Bus side.

The prefetch operations can eliminate the idle cycle of the PCI Bus side to improve read operation. IDE CONFIGURATION CYCLE

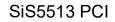

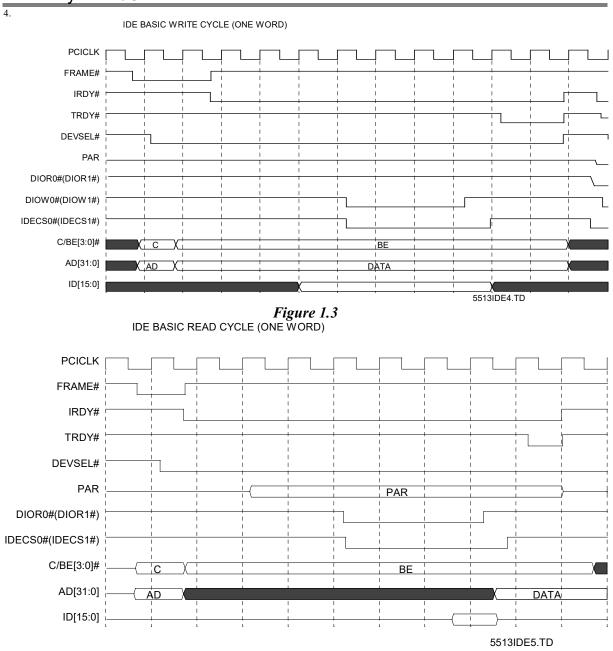

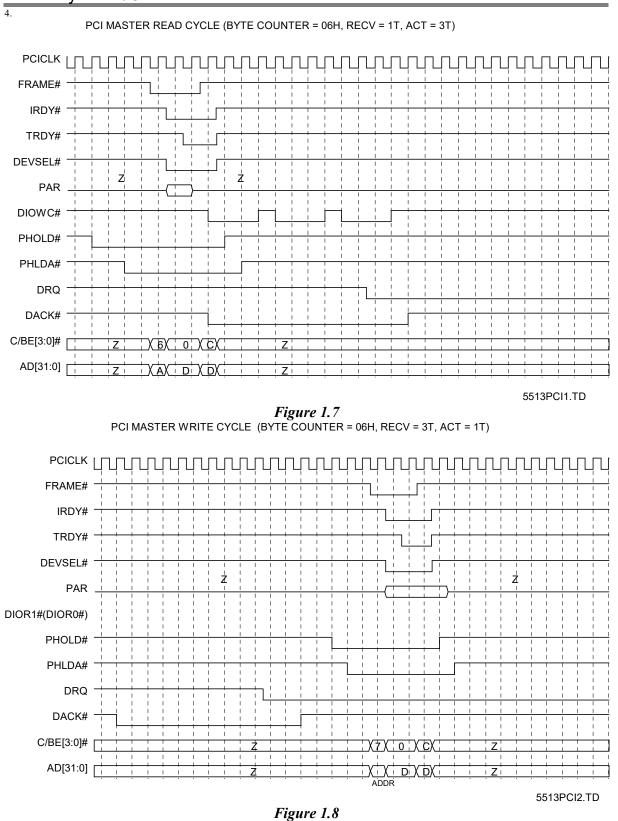

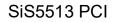

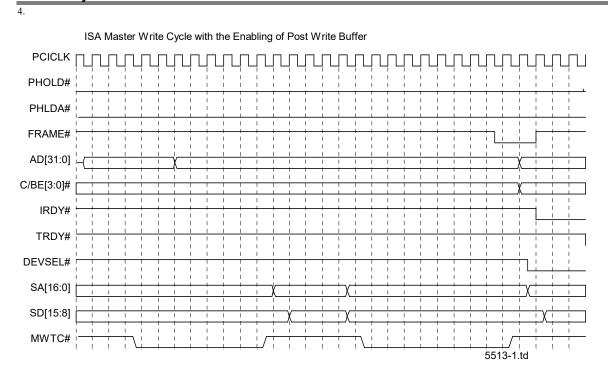

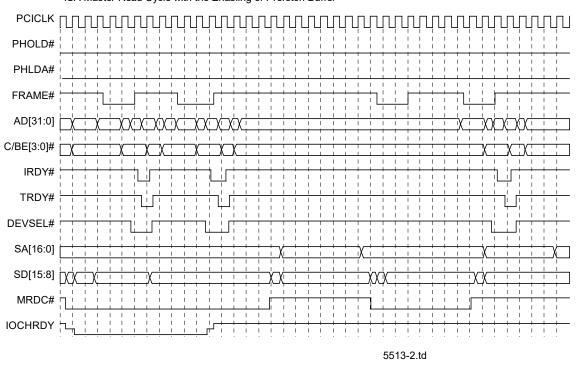

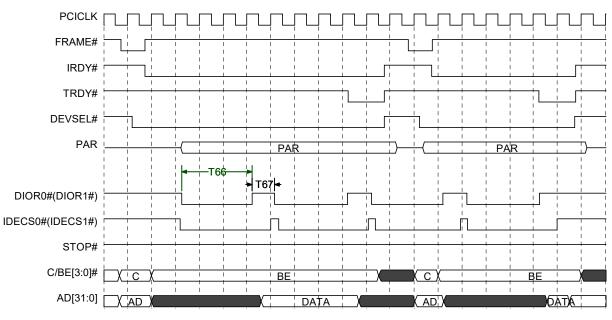

Figure 1.2

# SiS5513 PCI

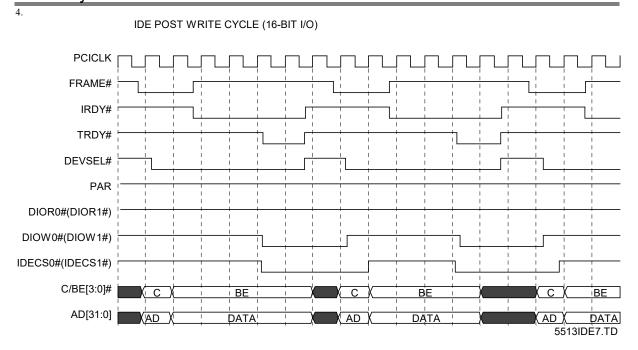

Figure 1.4

# SiS5513 PCI

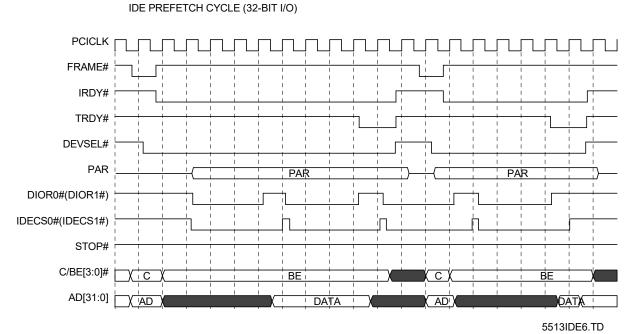

Figure 1.5

Figure 1.6

| Preliminary V2.0 | November 22, 1995 | 13 | Silicon Integrated Systems Corporation |

|------------------|-------------------|----|----------------------------------------|

|------------------|-------------------|----|----------------------------------------|

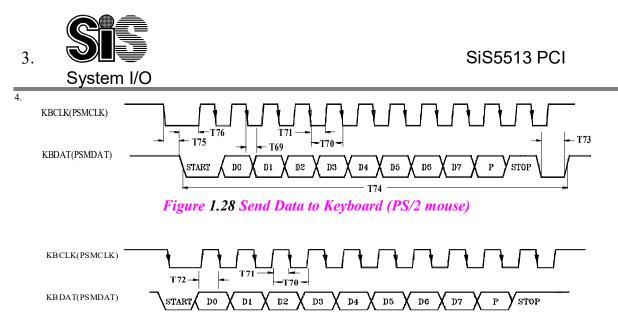

# 1.2.8. Built-in Keyboard Controller

The built-in KBC uses hardwired methodology instead of software implementation as the traditional 8042 keyboard BIOS. In this way, keyboard controller can have instant response to all the commands. It also has Fast Gate-20 and Fast Reset Features. Besides, the built-in KBC has a power control feature. After the [Ctrl]+[Alt]+[Backspace] hot keys are pressed, the system will enter the power saving mode. Moreover, the built-in KBC supports the industrial standard PS/2 mouse optionally.

# Status Register

The status register is an 8 bits read only register located at I/O address hex 64. It has information about the state of the keyboard controller and interface. It may be read at any time.

| Bit 7 | Parity Error                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

|       | 0 : Odd Parity (No Parity Error)                                                                                                             |

|       | 1 : Even Parity (Parity Error)                                                                                                               |

| Bit 6 | Time-out Error                                                                                                                               |

|       | 0 : No Transmission Time-out Error                                                                                                           |

|       | 1 : Transmission Time-out Error                                                                                                              |

| Bit 5 | Auxiliary Output Buffer Full                                                                                                                 |

|       | 0 : Keyboard Data                                                                                                                            |

|       | 1 : Mouse Data                                                                                                                               |

| Bit 4 | Inhibit Switch                                                                                                                               |

|       | 0 : Keyboard is Inhibited                                                                                                                    |

|       | 1 : Keyboard is not Inhibited                                                                                                                |

| Bit 3 | Command/Data                                                                                                                                 |

|       | 0 : Data Byte. Writing to I/O 60h                                                                                                            |

|       | 1 : Command Byte. Writing to I/O 64h                                                                                                         |

| Bit 2 | System Flag                                                                                                                                  |

|       | This bit may be set to 0 or 1 by writing to system flag bit in the keyboard controller's command byte. It is set to 0 after a power on reset |

| Bit 1 | Input Buffer Full                                                                                                                            |

|       | 0 : Input Buffer Empty                                                                                                                       |

|       | 1 : Input Buffer Full. Data has been written into the buffer but the controller has not read the data                                        |

Preliminary V2.0November 22, 199514Silicon Integrated Systems Corporation

# Bit 0 Output Buffer Full

- 0 : Output Buffer Empty

- 1 : Output Buffer Full. The controller has placed data into its output buffer but the system has not yet read data

# Input/Output Buffer

#### **Input Buffer**

The input buffer is an 8 bits write only register located at I/O address hex 60 or 64. Writing to address hex 60 sets a flag, that indicates a data write; writing to address hex 64 sets a flag, indicating a command write. Data written to I/O address hex 60 is sent to the keyboard, unless the keyboard controller is expecting a data byte following a controller command. Data should be written to the controller's input buffer only if the input buffer's full bit in the status register equal 0. The next command are valid keyboard controller commands.

#### **Output Buffer**

The output buffer is an 8 bits read only register at I/O address hex 60. The keyboard controller uses the output buffer to send scan codes received from the keyboard, and data bytes requested by command to the system. The output buffer should be read only when output buffer's full bit in the status register set to 1.

# Commands (I/O Address 64H)

# Write I/O Address 64h that is Keyboard BIOS Command:

| Command         Keyboard Mode         Keyboard PS/2 Mode           00-1F         Read Internal RAM – The controller sends value of RAM to output buffer.           20         Read Keyboard Controller's Command Byte The controller sends its current Command byte to its output buffer.           21-3F         Read Internal RAM – The controller sends value of RAM to output buffer.           40-5F         Write Internal RAM – The next byte of data written to 1/O 60h is placed into Internal RAM.           60         Write Keyboard Controller's Command Byte – The next byte of data written to 1/O 60h is placed in to controller's command byte.           8it         Bit Definitions           0         Enable Keyboard Output-Buffer-Full Interrupt.           Generates an interrupt when it places keyboard data into its output buffer.           1         In Keyboard PS/2 Mode:           1         - The controller generates an System Flag.           The value written to this bit is placed in the system flat bit of the controller's status register.           3         1           1         Disable Keyboard Lock Switch "KBLOCK".           4         1         Disable Keyboard Computer Compatibility Mode.           5         1         - Disable Mouse.           1         - Disable Mouse.         Disable the recived.           6         1         - IBM Personal Computer Compatibility Mode                                                                                                                                                                  | 10<br>10 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 20       Read Keyboard Controller's Command Byte The controller sends its current Command byte to its output buffer.         21-3F       Read Internal RAM The controller sends value of RAM to output buffer.         40-5F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         60       Write Keyboard Controller's Command Byte The next byte of data written to I/O 60h is placed into Internal RAM.         60       Bit Definitions         0       Enable Keyboard Output-Buffer-Full Interrupt.         Generates an interrupt when it places keyboard data into its output buffer.         1       In Keyboard PS/2 Mode:         1 - The controller generates an System Flag.         The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard.         Disable Keyboard.       Disable Keyboard.         Disable Keyboard.       Disable Keyboard.         Disable Keyboard.       Disable Keyboard.         0       Enable Mouse.         1 - Disable Keyboard.       Disable Keyboard.         Disable Keyboard.       Disable Keyboard.         1 - Disable Mouse.       Disable Keyboard to IBM PC.         1 - Disable Mouse.       Disable Keyboard to Base of the one-byte IBM Personal Computer format.         1 - Disable Mouse.       Disable the m                                                                                                                                                                                                   | 1e       |

| output buffer.           21-3F         Read Internal RAM – The controller sends value of RAM to output buffer.           40-5F         Write Internal RAM – The next byte of data written to I/O 60h is placed into Internal RAM.           60         Write Keyboard Controller's Command Byte – The next byte of data written to I/O 60h is placed in t controller's command byte.           Bit         Bit Definitions         0           0         Enable Keyboard Output-Buffer-Full Interrupt.<br>Generates an interrupt when it places keyboard data into its output buffer.           1         In Keyboard Mode: Reserved to 0.<br>In Keyboard PS/2 Mode:         1           1         Enable Keyboard Controller Full Interrupt.<br>Generates an interrupt when it places mouse data into its output buffer.           2         1         The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.           3         1         Disable Keyboard.           Disable Keyboard.         Disable the Keyboard Compatibuting the 'clock' line low.<br>Disable the Keyboard Computer Compatibility Mode.           6         1         I BM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.           7         0         Reserved.           61-7F         Write Internal RAM – The next byte of data written to I/O 60h is placed into Inter             | 1e       |

| 21-3F       Read Internal RAM – The controller sends value of RAM to output buffer.         40-5F       Write Internal RAM – The next byte of data written to I/O 60h is placed into Internal RAM.         60       Write Keyboard Controller's Command Byte – The next byte of data written to I/O 60h is placed in t controller's command byte.         Bit       Bit Definitions       0         0       Enable Keyboard Output-Buffer-Full Interrupt.         Generates an interrupt when it places keyboard data into its output buffer.       1         1       In Keyboard PS2 Mode:       1         1       - Enable Mouse-Buffer-Full Interrupt.       Generates an interrupt when it places mouse data into its output buffer.         2       1       - The controller generates an System Flag.         The value written to this bit is placed in the system flat bit of the controller's status register.       3         3       1       Disable Keyboard Lock Switch "KBLOCK".         4       1       Disable Keyboard.       Disable Keyboard.         Data is not sent or received.       5       1       Disable Keyboard Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.       This includes converting a two-byte sequence to the one-byte IBM Personal Computer format.         7       0       - Reserved.       1       The spasword Installed - The controller.                                                                                                                                                                        | 1e       |

| 60       Write Keyboard Controller's Command Byte – The next byte of data written to I/O 60h is placed in t controller's command byte.         Bit       Bit Definitions         0       Enable Keyboard Output-Buffer-Full Interrupt.<br>Generates an interrupt when it places keyboard data into its output buffer.         1       In Keyboard Mode: Reserved to 0.<br>In Keyboard PS/2 Mode:         1       - Enable Mouse-Buffer-Full Interrupt.<br>Generates an interrupt when it places mouse data into its output buffer.         2       1 - The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.<br>Disable the Keyboard.<br>Disable the Keyboard.<br>Disable the Keyboard.<br>Disable the Keyboard.         5       1 - Disable Keyboard.<br>Disable Mouse.         Data is not sent or received.       5         3       1 - Disable Keyboard to the virving the 'clock' line low.<br>Data is not sent or received.         6       1 - IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM - The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM - The controller sends value to its output buffer that end with a "0". | 1e       |

| 60       Write Keyboard Controller's Command Byte – The next byte of data written to I/O 60h is placed in t controller's command byte.         Bit       Bit Definitions         0       Enable Keyboard Output-Buffer-Full Interrupt.<br>Generates an interrupt when it places keyboard data into its output buffer.         1       In Keyboard Mode: Reserved to 0.<br>In Keyboard PS/2 Mode:         1       - Enable Mouse-Buffer-Full Interrupt.<br>Generates an interrupt when it places mouse data into its output buffer.         2       1 - The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.<br>Disable the Keyboard.<br>Disable the Keyboard.<br>Disable the Keyboard.<br>Disable the Keyboard.         5       1 - Disable Keyboard.<br>Disable Mouse.         Data is not sent or received.       5         3       1 - Disable Keyboard to the virving the 'clock' line low.<br>Data is not sent or received.         6       1 - IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM - The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM - The controller sends value to its output buffer that end with a "0". |          |

| controller's command byte.           Bit         Bit Definitions           0         Enable Keyboard Output-Buffer-Full Interrupt.<br>Generates an interrupt when it places keyboard data into its output buffer.           1         In Keyboard PS/2 Mode:<br>1 - Enable Mouse-Buffer-Full Interrupt.<br>Generates an interrupt when it places mouse data into its output buffer.           2         1 - The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.           3         1 - Disable Keyboard Lock Switch "KBLOCK".           4         1 - Disable Keyboard.           Disable the Keyboard interface by driving the 'clock' line low.<br>Data is not sent or received.           5         1 - Disable Mouse.<br>Disable the mouse interface by driving the 'clock' line low.<br>Data is not sent or received.           6         1 - IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.           7         0 - Reserved.           61-7F         Write Internal RAM - The next byte of data written to 1/O 60h is placed into Internal RAM.           A0         Read Internal ROM The controller sends value to its output buffer that end with a "0".           A1         Read Internal ROM The controller sends value to its output buffer:<br>FAh Password Installed - The controller sends<br>value to its output buffer:                |          |

| 0       Enable Keyboard Output-Buffer-Full Interrupt.<br>Generates an interrupt when it places keyboard data into its output buffer.         1       In Keyboard Mode: Reserved to 0.<br>In Keyboard PS/2 Mode:         1       - Enable Mouse-Buffer-Full Interrupt.<br>Generates an interrupt when it places mouse data into its output buffer.         2       1       - The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.         3       1       - Disable Keyboard Lock Switch "KBLOCK".         4       1       - Disable Keyboard interface by driving the 'clock' line low.<br>Data is not sent or received.         5       1       - Disable Mouse.<br>Disable the mouse interface by driving the 'clock' line low.<br>Data is not sent or received.         6       1       - IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0       - Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Reset Internal Register B to 0.       Test Password Installed                                                                                                                                                                         |          |

| Generates an interrupt when it places keyboard data into its output buffer.         1       In Keyboard Mode: Reserved to 0.         In Keyboard PS/2 Mode:       1         1       - Enable Mouse-Buffer-Full Interrupt.         Generates an interrupt when it places mouse data into its output buffer.         2       1         3       1         1       - The controller generates an System Flag.         The value written to this bit is placed in the system flat bit of the controller's status register.         3       1         4       1         Disable Keyboard         Data is not sent or received.         5       1         1       - Bisable Mouse.         Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1         6       1         7       0         8       - Reserved.         6       1         9       - Reserved.         6       1         1       - Beast byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal RAM - The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends val                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 1       In Keyboard Mode: Reserved to 0.         In Keyboard PS/2 Mode:       1         1       - Enable Mouse-Buffer-Full Interrupt.         Generates an interrupt when it places mouse data into its output buffer.         2       1         -       The controller generates an System Flag.         The value written to this bit is placed in the system flat bit of the controller's status register.         3       1         1       Disable Keyboard Lock Switch "KBLOCK".         4       1         1       Disable Keyboard.         Disable the Keyboard interface by driving the 'clock' line low.         Data is not sent or received.         5       1         6       1         1       Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.       6         6       1         1       Bersonal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0         0       Reserved.         61-7F       Write Internal RAM - The next byte of data written to I/O 60h is placed into Internal RAM.         A0 </td <td></td>                                                                                                                                                                                                                                                                                                                                               |          |

| In Keyboard PS/2 Mode:         1 Enable Mouse-Buffer-Full Interrupt.         Generates an interrupt when it places mouse data into its output buffer.         2       1 Enable Mouse-Buffer-Full Interrupt.         Generates an interrupt when it places mouse data into its output buffer.         2       1 Disable Controller generates an System Flag.         The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.         Disable the Keyboard interface by driving the 'clock' line low.         Data is not sent or received.         5       1 Disable Mouse.         Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 BM Personal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result wi                                                                                                                                                                                                    |          |

| 1 - Énable Mouse-Buffer-Full Interrupt.         Generates an interrupt when it places mouse data into its output buffer.         2       1 - The controller generates an System Flag.         The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.         Disable the Keyboard interface by driving the 'clock' line low.         Data is not sent or received.         5       1 - Disable Mouse.         Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 - IBM Personal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password installed The controller sends value to its output buffer: FAh Password installed </td <td></td>                                                                                                                                                           |          |

| Generates an interrupt when it places mouse data into its output buffer.         1       - The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.         3       1       - Disable Keyboard Lock Switch "KBLOCK".         4       1       - Disable Keyboard.         Disable the Keyboard interface by driving the 'clock' line low.<br>Data is not sent or received.       -         5       1       Disable Mouse.<br>Disable the mouse interface by driving the 'clock' line low.<br>Data is not sent or received.         6       1       IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0       - Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                          |          |

| 2       1 The controller generates an System Flag.<br>The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.         Disable Keyboard.       Disable the Keyboard interface by driving the 'clock' line low.         Data is not sent or received.       5         1 - Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                 |          |

| The value written to this bit is placed in the system flat bit of the controller's status register.         3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.         Disable the Keyboard interface by driving the 'clock' line low.         Data is not sent or received.         5       1 - Disable Mouse.         Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 - IBM Personal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM - The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password installed The controller sends value to its output buffer: FAh Password installed                                                                                                                                                                                                                                                                                                                                                                      |          |

| 3       1 - Disable Keyboard Lock Switch "KBLOCK".         4       1 - Disable Keyboard.         Disable the Keyboard interface by driving the 'clock' line low.         Data is not sent or received.         5       1 - Disable Mouse.         Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 - IBM Personal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM - The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed - The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Disable the Keyboard interface by driving the 'clock' line low.<br>Data is not sent or received.         5       1 - Disable Mouse.<br>Disable the mouse interface by driving the 'clock' line low.<br>Data is not sent or received.         6       1 - IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| Data is not sent or received.         5       1 Disable Mouse.         Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 IBM Personal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer: FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 5       1 Disable Mouse.<br>Disable the mouse interface by driving the 'clock' line low.<br>Data is not sent or received.         6       1 IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| Disable the mouse interface by driving the 'clock' line low.         Data is not sent or received.         6       1 IBM Personal Computer Compatibility Mode.         Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer: FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| Data is not sent or received.         6       1 IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 6       1 IBM Personal Computer Compatibility Mode.<br>Convert the scan codes received from keyboard to IBM PC.<br>This includes converting a two-byte sequence to the one-byte IBM Personal<br>Computer format.         7       0 Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| Convert the scan codes received from keyboard to IBM PC.         This includes converting a two-byte sequence to the one-byte IBM Personal         Computer format.         7       0 - Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer: FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| Computer format.     Computer format.       7     0 Reserved.       61-7F     Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.       A0     Read Internal ROM The controller sends value to its output buffer that end with a "0".       A1     Read Keyboard Controller's Version - The version code result will be placed to its output buffer.       A4     Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 7       0 - Reserved.         61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer: FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 61-7F       Write Internal RAM The next byte of data written to I/O 60h is placed into Internal RAM.         A0       Read Internal ROM The controller sends value to its output buffer that end with a "0".         A1       Read Keyboard Controller's Version - The version code result will be placed to its output buffer.         A4       Reset Internal Register B to 0.       Test Password Installed The controller sends value to its output buffer: FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| A0         Read Internal ROM The controller sends value to its output buffer that end with a "0".           A1         Read Keyboard Controller's Version - The version code result will be placed to its output buffer.           A4         Reset Internal Register B to 0.         Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| A1         Read Keyboard Controller's Version - The version code result will be placed to its output buffer.           A4         Reset Internal Register B to 0.         Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| A4 Reset Internal Register B to 0. Test Password Installed The controller sends value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| value to its output buffer:<br>FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| FAh Password installed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |