# Content

| Figure     |                                             | vi  |

|------------|---------------------------------------------|-----|

| Table      |                                             | vii |

| Revision H | History                                     | ix  |

| 1 SiS54    | 40 Overview                                 | 1   |

| 1.1        | Function Block Reference                    | 3   |

| 2 Featu    | ıres                                        | 4   |

| 3 Pin A    | ssignment                                   | 13  |

| 3.1        | Pin Assignment (Top View)                   | 13  |

| 3.1.1      | SiS540 Pin Assignment (Top View-Left Side)  | 13  |

| 3.1.2      | SiS540 Pin Assignment (Top View-Right Side) | 14  |

| 3.2        | SiS540 Alphabetical Pin List                | 15  |

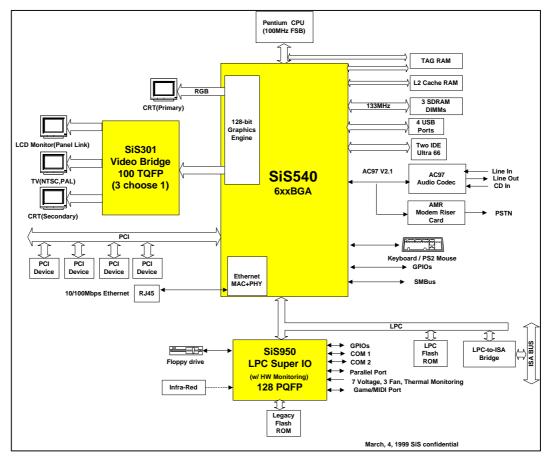

| 3.3        | Power Plane                                 | 23  |

| 4 Pin D    | escription (Preliminary)                    | 24  |

| 4.1        | Host interface Interface Signals            | 24  |

| 4.2        | L2 Cache Interface Signals                  | 27  |

| 4.3        | DRAM Controller                             | 28  |

| 4.4        | PCI Interface                               | 29  |

| 4.5        | PCI IDE Interface                           | 32  |

| 4.6        | VGA Interface                               | 33  |

| 4.7        | Power management Interface                  | 35  |

| 4.8        | SMBus Interface                             | 36  |

| 4.9        | Keyboard controller Interface               | 37  |

| 4.10       | LPC Interface                               | 38  |

| 4.11       | RTC Interface                               | 38  |

| 4.12       | AC' 97 interface                            | 39  |

| 4.13       | Fast Ethernet and Home Networking interface | 40  |

| 4.14       | USB interface                               | 41  |

| 4.15       | Legacy I/O and Miscellaneous Signals        | 42  |

| 4.16       | Power and Ground Signals                    | 43  |

| 5 Hardy    | ware Trap                                   | 44  |

| 6 Funct    | tion Description                            | 47  |

| 6.1        | MA mapping table                            | 47  |

| 6.1.1      | SDRAM/System Memory                         | 47  |

| 6.1.2      | SDRAM/FBC                                   | 48  |

| 6.1.3      | VCM/System Memory                           | 49  |

| 6.1.4      | VCM/FBC                                     | 52  |

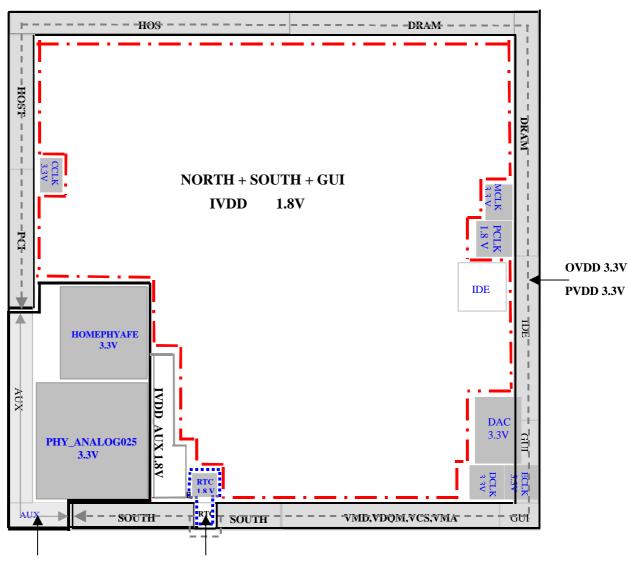

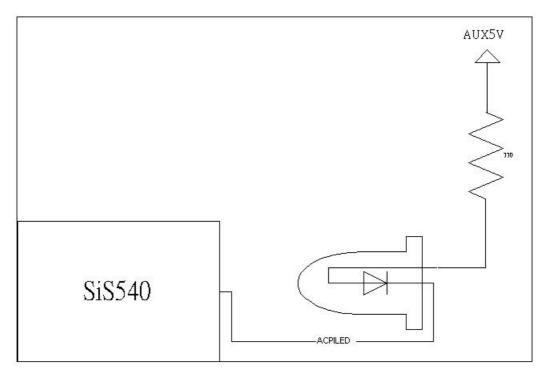

| 6.2        | PSON# and ACPILED Description:              | 53  |

|   | 6.3      | ACPILED Control                                               | 54  |

|---|----------|---------------------------------------------------------------|-----|

|   | 6.4      | Power States for 540 Signals                                  | 55  |

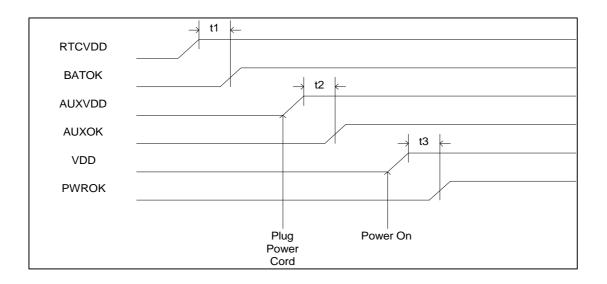

|   | 6.5      | Power Sequence in SiS540                                      | 59  |

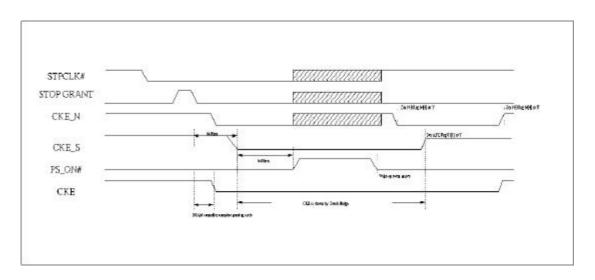

|   | 6.6      | S3 Timing Table                                               | 60  |

|   | 6.7      | Multi-function Pins Relational Data Table                     | 60  |

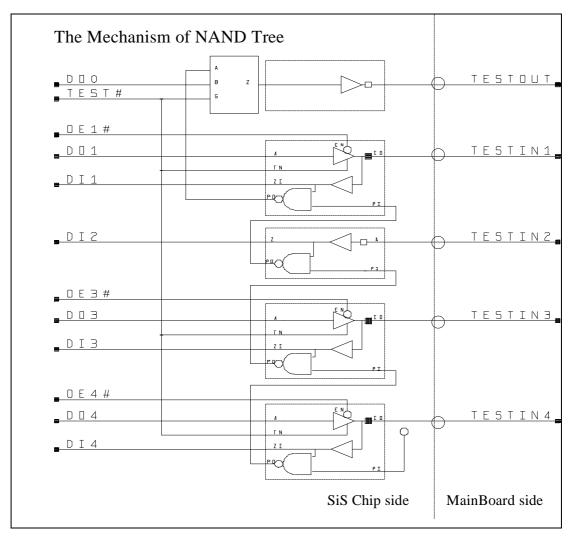

|   | 6.8      | Ball Connectivity Testing                                     | 62  |

|   | 6.8.1    | Test Scheme                                                   | 62  |

|   | 6.8.2    | Measurements                                                  | 64  |

| 7 | Register | Summary / Description – Core Logic                            | 67  |

|   | 7.1      | Host-to-PCI Bridge Configuration Space (Device 0, Function 0) | 67  |

|   | 7.1.1    | Host-to-PCI Bridge Configuration Space Header                 | 67  |

|   | 7.1.2    | Host/L2 Cache/DRAM                                            | 67  |

|   | 7.1.3    | Power Management                                              | 68  |

|   | 7.1.4    | Shadow RAM & Non-cacheable Area                               | 68  |

|   | 7.1.5    | Hardware Trapping Control                                     | 68  |

|   | 7.1.6    | Host Bridge & PCI Arbiter                                     | 69  |

|   | 7.1.7    | Clock Control                                                 | 69  |

|   | 7.1.8    | GART and Page Table Cache                                     | 69  |

|   | 7.1.9    | DRAM Priority Timer                                           | 70  |

|   | 7.1.10   | A.G.P. and Host Bridge                                        | 70  |

|   | 7.1.11   | Device 2 (Virtual PCI-to-PCI Bridge)                          | 70  |

|   | 7.2      | Register Description Core logic                               | 71  |

|   | 7.2.1    | Host Bridge Registers (Device 0, Function 0)                  | 71  |

|   | 7.2.1.   | Host-to-PCI Bridge Configuration Space Header                 | 71  |

|   | 7.2.1.2  | 2 Host/L2 Cache/DRAM Control Register                         | 75  |

|   | 7.2.2    | Power Management Control Register                             | 92  |

|   | 7.2.2.   | Shadow Ram & Non-Cacheable Area Control Register              | 95  |

|   | 7.2.2.2  | 2 HOST Bridge and PCI Arbiter Control Register                | 101 |

|   | 7.2.2.3  | Clock Control Register                                        | 107 |

|   | 7.2.2.4  | GART and Page Table Cache Control Register                    | 110 |

|   | 7.2.2.   | DRAM Priority Timer Control Register                          | 113 |

|   | 7.2.2.6  | A.G.P. and Host Bridge Control Registers                      | 115 |

|   | 7.2.3    | Virtual PCI-to-PCI Bridge Registers (Device 2)                | 117 |

| 8 | PCI IDE  | Configuration Space Register                                  | 125 |

|   | 8.1      | Offset Registers for PCI Bus Master IDE Control Registers     | 139 |

| 9 | Register | Summary / Description – Graphics                              |     |

|   | 9.1      | General Registers                                             | 143 |

|   | 9.2      | CRT Controller Registers                                      | 146 |

|   | 9.3      | Sequencer Registers                                           | 155 |

| 9.4      | Graphics Controller Registers                                        | 159 |

|----------|----------------------------------------------------------------------|-----|

| 9.5      | Attribute Controller and Video DAC Registers                         | 164 |

| 9.6      | Color Registers                                                      | 168 |

| 9.7      | Extended Registers                                                   | 170 |

| 9.8      | Video/TV Extended Registers                                          | 172 |

| 9.9      | Video Playback Index Registers                                       | 172 |

| 9.10     | Digital Video Interface Registers                                    | 176 |

| 9.11     | PCI Configuration Registers                                          | 178 |

| 9.12     | AGP Configuration Registers                                          | 181 |

| 10 Regi  | ster Summary / Description Legacy                                    | 183 |

| 10.1     | Legacy ISA Registers                                                 | 183 |

| 10.1.1   | DMA Registers                                                        | 183 |

| 10.1.2   | Interrupt Controller Registers                                       | 185 |

| 10.1.3   | Timer Registers                                                      | 185 |

| 10.1.4   | Other Registers                                                      | 185 |

| 11 Regis | ster Summary / Description – LPC Summary                             | 187 |

| 11.1     | LPC Bridge Configuration Registers                                   | 187 |

| 11.2     | LPC Bridge Configuration Registers                                   | 188 |

| 12 Regis | ster Summary / Description –USB Summary                              | 208 |

| 12.1     | USB OpenHCI Host Controller Configuration Space                      | 208 |

| 12.1.1   | USB Configuration Space                                              | 208 |

| 12.2     | USB OpenHCI Host Controller Operational Registers                    | 208 |

| 12.2.1   | Host Controller Operational Registers                                | 209 |

| 12.2.    | 1.1 Control and Status Partition                                     | 210 |

| 12.2.    | 1.2 Memory Pointer Partition                                         | 218 |

| 12.2.    | 1.3 Frame Counter Partition                                          | 221 |

| 12.2.    | 1.4 Root Hub Partition                                               | 224 |

| 12.3     | Legacy Support Registers                                             | 232 |

| 13 Regis | ster Summary / Description – Fast Ethernet / Home Networking Summary | 237 |

| 13.1     | MAC and PHY Registers                                                | 237 |

| 13.1.1   | MAC Configuration Space (Function 1)                                 | 237 |

| 13.1.2   | MAC Operational Registers                                            | 238 |

| 13.1.3   | PHY Configuration Registers                                          | 238 |

| 13.2.    | 10M/100M Ethernet Controller Registers                               | 239 |

| 13.2     | PCI Configuration Registers                                          | 240 |

| 13.3     | MAC Operational Registers                                            | 251 |

| 13.3.1   | Wake-up Sample Frame Byte Mask Register                              | 276 |

| 13.4     | MII PHY Registers                                                    | 277 |

| 13.5     | Home SPI Registers                                                   | 285 |

| 14 Reg  | gister Summary / Description – AC' 97 / S/W Modem Summary      | 294 |

|---------|----------------------------------------------------------------|-----|

| 14.1    | Audio Configuration Space (Function 4)                         | 294 |

| 14.1.1  | Audio Operational Registers                                    | 295 |

| 14.2    | Audio Processor Register Map:                                  | 298 |

| 14.2.1  | Wave Engine Register:                                          | 319 |

| 15 Reg  | gister Summary / Description – ACPI/SMBus Summaries            | 344 |

| 15.1    | ACPI Configuration Registers                                   | 344 |

| 15.2    | Register Summary / Description – SMBus                         | 345 |

| 15.2.1  | SMBus Control Registers                                        | 345 |

| 15.3    | ACPI Register                                                  | 346 |

| 16 Reg  | gister Summary / Description – Automatic Power Control Summary | 378 |

| 16.1    | Automatic Power Control (APC) Registers                        | 378 |

| 16.1.1  | RTC Registers                                                  | 378 |

| 16.2    | APC Register                                                   | 379 |

| 17 Elec | ctrical Characteristics                                        | 386 |

| 17.1    | Absolute maximum Ratings                                       | 386 |

| 17.2    | DC Characteristics                                             | 386 |

| 17.2.1  | Ta=0-70°C, Gnd=0V, VCC3=3.3V±5%,VCC18=1.8V±5%,,                | 386 |

| 17.2.2  | DC Characteristics for DAC (Analog Output Characteristics)     | 386 |

| 17.2.3  | Integrated RTC POWER CONSUMPTION                               | 387 |

| 17.3    | AC Characteristics                                             | 387 |

| 17.3.1  | Host AC Timing                                                 | 387 |

| 17.3.2  | CACHE and TAG Signals AC Timing                                | 388 |

| 17.3.3  | B DRAM AC Timing                                               | 389 |

| 17.3    | 3.3.1 Light Loading of SDRAM                                   | 389 |

| 17.3    | 3.3.2 Heavy Loading of SDRAM                                   | 391 |

| 17.3    | 3.3.3 Light Loading of FBC                                     | 392 |

| 17.3    | 3.3.4 Heavy Loading of FBC                                     | 394 |

| 17.3.4  | PCI Signals AC Timing                                          | 397 |

| 17.3    | 3.4.1 Light Loading                                            | 397 |

| 17.3    | 3.4.2 Heavy Loading                                            | 397 |

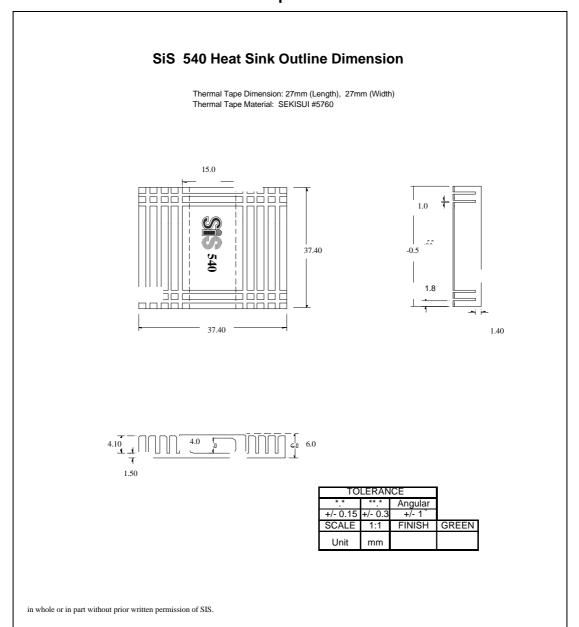

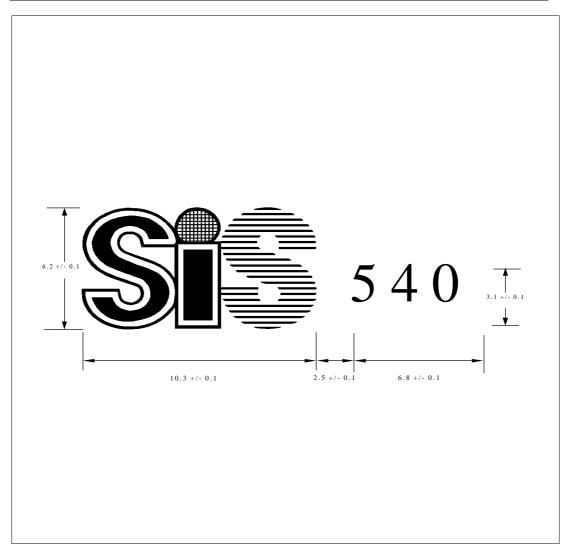

| 18 Hea  | at Sink Dimension and Topside Mark                             | 399 |

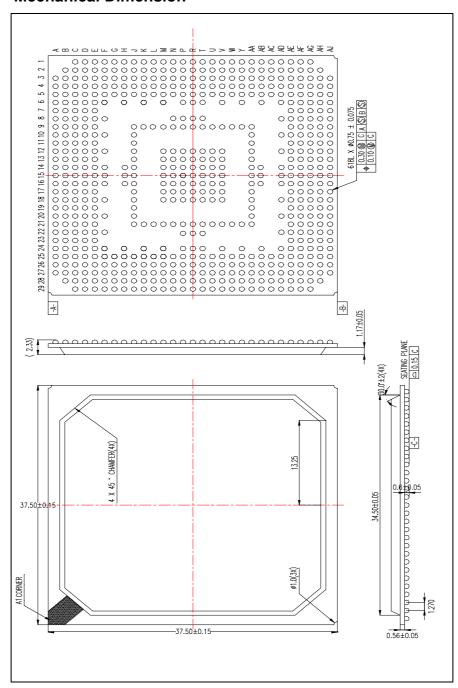

| 19 Med  | chanical Dimension                                             | 401 |

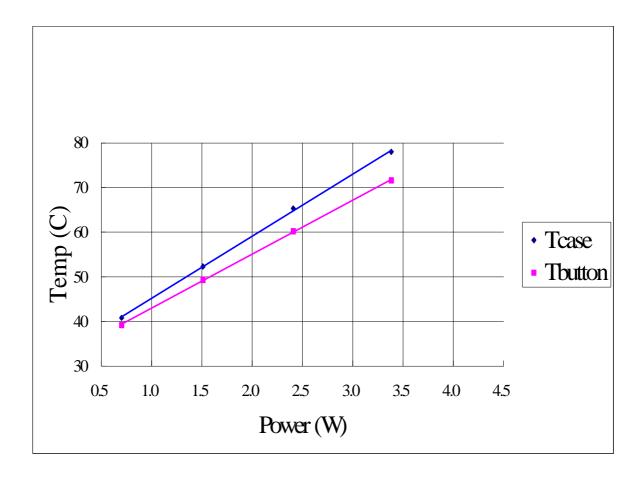

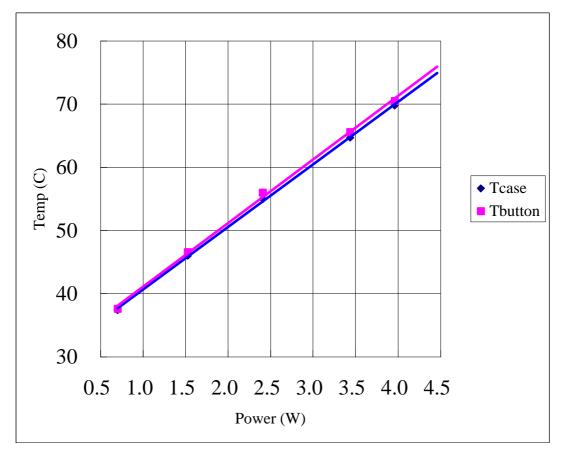

| 20 THE  | ERMAL ANALYSIS                                                 | 402 |

| 20.1    | CHIP THERMAL ANALYSIS WITHOUT HEATSINK                         | 402 |

| 20.2    | CHIP THERMAL ANALYSIS WITH HEATSINK                            | 403 |

| 21 App  | pendix:                                                        | 404 |

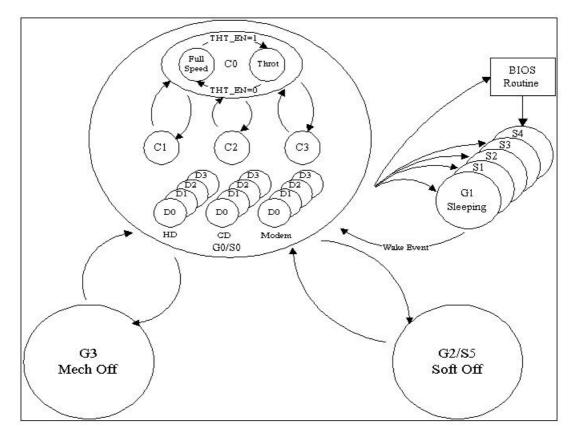

| 21.1    | ACPI Power State                                               | 404 |

| 21.1.1  | Global System State Definitions                                | 404 |

| 21.1.2  | Device Power State Definitions                         | 404 |

|---------|--------------------------------------------------------|-----|

| 21.1.3  | Sleeping State Definitions                             | 405 |

| 21.1.4  | Processor Power State Definitions                      | 406 |

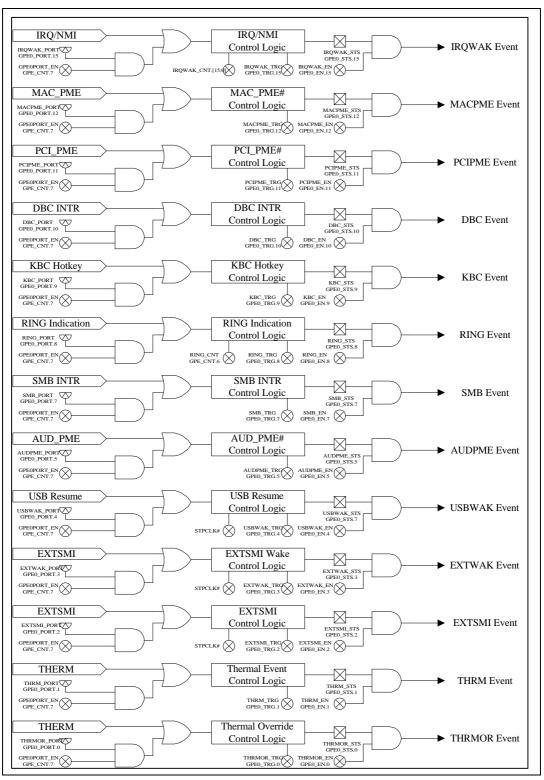

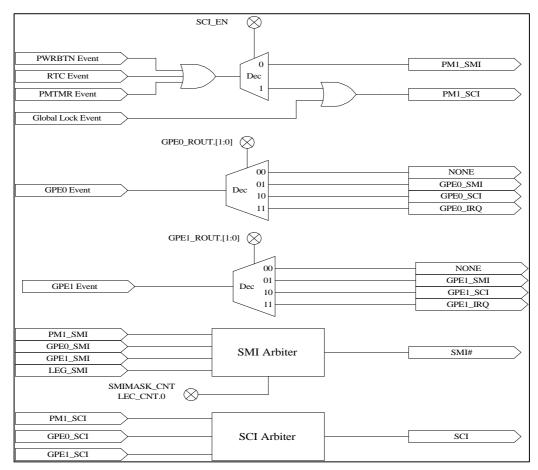

| 21.2    | The Hardware Event of ACPI                             | 407 |

| 21.3    | The Interrupt Event of ACPI                            | 410 |

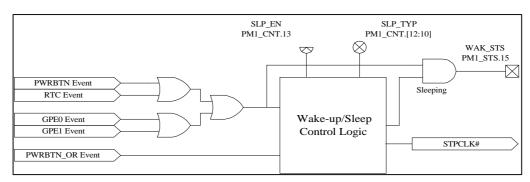

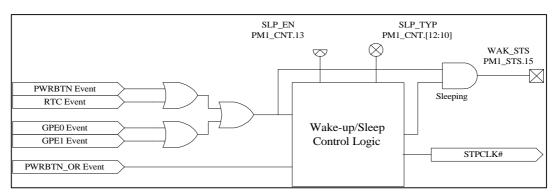

| 21.4    | The Sleeping/Wake Event of ACPI                        | 411 |

| 21.5    | Types of ACPI Events                                   | 412 |

| 21.5.1  | Fixed ACPI Events Handling                             | 412 |

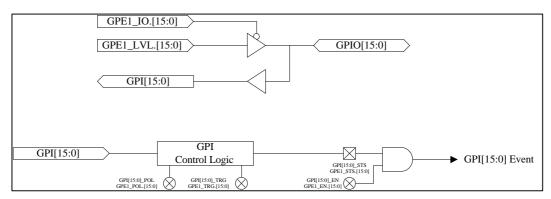

| 21.5.2  | General-purpose Events Handling                        | 412 |

| 21.6    | Examples                                               | 413 |

| 21.6.1  | Hardware Model of Integrate Modem and PCI Network Card | 414 |

| 21.6.2  | The System Enter S1 Sleeping State                     | 414 |

| 21.6.3  | The System Exit S1 Sleeping State                      | 415 |

| 21.6.4  | The Integrate Modem enters D3/S0 State                 | 415 |

| 21.6.5  | The PCI LAN Card enters D3/S0 State                    | 416 |

| 21.6.6  | When The Modem Detects Phone Call                      | 416 |

| 21.6.7  | When The PCI LAN Card Detects a Wakeup Event           | 416 |

| 22 Сору | right Notice                                           | 417 |

# **Figure**

| Figure 1-1 SiS540 System Block Diagram                    | 2   |

|-----------------------------------------------------------|-----|

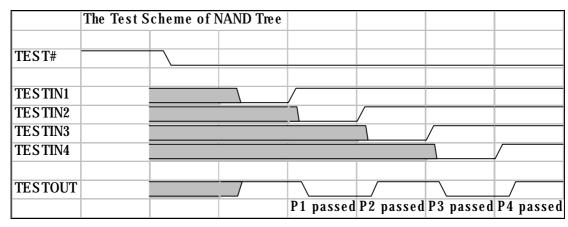

| Figure 6.8-1 The Mechanism of NAND Tree                   | 63  |

| Figure 6.8-2 The Test Scheme of NAND Tree                 | 64  |

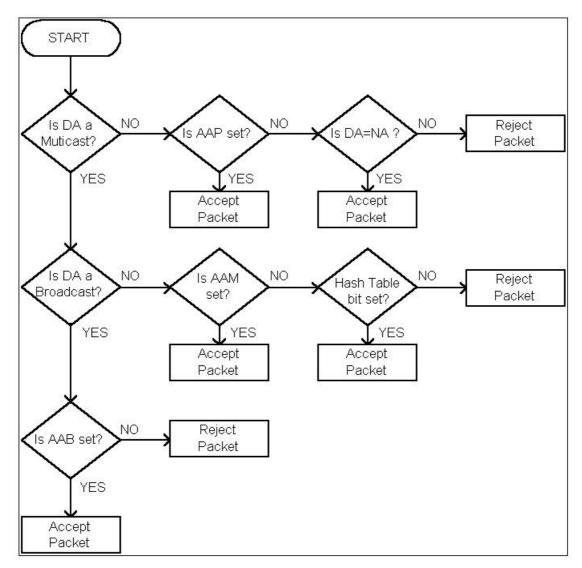

| Figure 13.3-1 Receive Filter Algorithm                    | 272 |

| Figure 21.1-1 ACPI Model                                  | 407 |

| Figure 21.2-1 Hardware Model for Fix Feature              | 408 |

| Figure 21.2-2 Hardware Model for Generic Fixture 0 (GPE0) | 409 |

| Figure 21.2-3 Hardware Model for Generic Feature 1 (GPE1) | 410 |

| Figure 21.3-1 Interrupt Model for ACPI                    | 411 |

| Figure 21.4-1 Sleeping/Wake model for ACPI                | 412 |

| Figure 21.6-1 Hardware Model for PME#                     | 414 |

# Table

| Table 9.1-1 Sync Polarity vs. Vertical Screen Resolution             | 143 |

|----------------------------------------------------------------------|-----|

| Table 9.1-2 Table for Video Clock Selection                          | 143 |

| Table 9.1-3 Table for Video Read-back Through Diagnostic Bit (I)     | 145 |

| Table 9.1-4 Table for Video Read-back Through Diagnostic Bit (II)    | 145 |

| Table 9.2-1 Table of CRT Controller Registers                        | 146 |

| Table 9.3-1 Table of Sequencer Registers                             | 156 |

| Table 9.3-2 Table of Selecting Active Character Generator            | 158 |

| Table 9.4-1 Table of Graphics Controller Registers                   | 159 |

| Table 9.4-2 Table of Function Select                                 | 160 |

| Table 9.4-3 Table of Rotate Count                                    | 161 |

| Table 9.4-4 Table for Write Mode                                     | 162 |

| Table 9.4-5 Table of Memory Address Select                           | 163 |

| Table 9.5-1 Table of Attribute Controller Registers                  | 164 |

| Table 9.5-2 Table for Video Read-back Through Diagnostic Bit (I)     | 166 |

| Table 9.5-3 Table for Video Read-back Through Diagnostic Bit (II)    | 167 |

| Table 9.5-4 Table of Pixel Panning                                   | 167 |

| Table 9.7-1 Table of Extended Registers                              | 170 |

| Table 9.9-1 Table of Video Playback Registers                        | 173 |

| Table 9.10-1 Table of digital video interface registers              | 177 |

| Table 11.2-1 Interrupt Pin Reroute Table                             | 192 |

| Table 12.3-1 Legacy Support Registers                                | 232 |

| Table 12.3-2 Emulated Registers                                      | 233 |

| Table 14.2-1 Audio Processor Register Map                            | 298 |

| Table 17.1-1 Absolute Maximum Ratings                                | 386 |

| Table 17.2-1 DC Characteristics of Host, DRAM, PCI and IDE Interface | 386 |

| Table 17.2-1 Table of DC Characteristics for DAC                     | 386 |

| Table 17.2-2 RTC Power Consumption Table                             | 387 |

| Table 17.3-1 CPU AC Timing Measurement                               | 387 |

| Table 17.3-2 Clock Skew                                              |     |

| Table 17.3-3 CACHE and TAG AC Timing Measurement                     | 388 |

| Table 17.3-4 Clock Skew                                              |     |

| Table 17.3-5 Signal Valid/Invalid Delay of SDRAM from SDRAM Clock    | 389 |

| Table 17.3-6 Peak Voltage of SDRAM                                   | 390 |

| Table 17.3-7 Signal Valid/Invalid Delay of SDRAM from SDRAM Clock    | 391 |

| Table 17.3-8 Peak Voltage of SDRAM                                   | 392 |

| Table 17.3-9 Signal Valid/Invalid Delay of FBC from SDRAM Clock      | 393 |

| Table 17.3-10 Peak Voltage of FBC                                    | 393 |

|                                                                      |     |

| Table 17.3-11 Signal Valid/Invalid Delay of FBC from SDRAM Clock | 394 |

|------------------------------------------------------------------|-----|

| Table 17.3-12 Peak Voltage of FBC                                | 395 |

| Table 17.3-13 PCI Signals AC Timing                              |     |

| Table 17.3-14 PCI Signals AC Timing                              |     |

| Table 17.3-15 Clock Skew                                         |     |

# **Revision History**

| Date        | Rev. | Description                                                    |

|-------------|------|----------------------------------------------------------------|

|             |      | 1.Revision to the Pin Assignment for USB (UV[4:0]) .           |

|             |      | 2.GUI Device ID from 5400 to 5300.                             |

|             |      | 3.Add S3 and Ring Timing table to Chap 6, Function Description |

|             |      | 4.Revisions to Chap.7, Register 7D, Bit 4:1. The original      |

|             |      | description [43:40] is revisied to [44:41]                     |

|             | 0.95 | 5.Revisions to Chap.10_Register Summary-Legacy.doc             |

|             |      | 6.Chap.15_Register Summary-SMBUS                               |

| Aug.19,1999 |      | Revision to Register 1Ah~1Bh ACPI Fix Feature Control          |

|             |      | 7.Chap.15_Register Summary-SMBus                               |

|             |      | Reverse Register 4Ah and 4Bh.                                  |

|             |      | 8.Chap.15_Register Summary-SMBUS                               |

|             |      | Revisions Register 5E, Bit 8 and 9. (I <sup>2</sup> C)         |

|             |      | 9.Chap.15 Register 20~28h have been changed for USB            |

|             |      | wake-up function.                                              |

|             |      | 10.Add Chap.22                                                 |

| Nov.30,1999 | 1.0  | Formal Release                                                 |

#### 1 SiS540 Overview

The single chipset, SiS540, provides a high performance/low cost Desktop solution for the Super Socket 7 series CPUs based system by integrating a high performance North Bridge, advanced hardware 2D/3D GUI engine and Super-South bridge. In addition, SiS540 provides system-on-chip solution that complies with Easy PC Initiative which supports Instantly Available/OnNow PC technology, USB, Legacy Removal and Slotless Design and FlexATX form factor.

By integrating the Ultra-AGP<sup>™</sup> technology and advanced 128-bit graphic display interface, SiS540 delivers high performance and up to 2 GB/s memory bandwidth. Furthermore, SiS540 provides powerful slice layer decoding DVD accelerator to improve the DVD playback performance. In addition to providing the standard interface for CRT monitors, SiS540 also provides the Digital Flat Panel Port (DFP) for a standard interface between a personal computer and a digital flat panel monitor. To extend functionality and flexibility, SiS also provides the "Video Bridge" (SiS301) to support the NTSC/PAL Video Output, Digital LCD Monitor and Secondary CRT Monitor, which reduces the external Panel Link transmitter and TV-Out encoder for cost effected solution. SiS540 also adopts Share System Memory Architecture which can flexibly utilize the frame buffer size up to 64MB.

The "Super-South Bridge" in SiS540 integrates all peripheral controllers /accelerators /interfaces. SiS540 provides a total communication solution including 10/100Mb Fast Ethernet for Office requirement. SiS540 offers AC 97 compliant interface that comprises digital audio engine with 3D-hardware accelerator, on-chip sample rate converter, and professional wavetable along with separate modem DMA controller. SiS540 also provides interface to Low Pin Count (LPC) operating at 33 MHz clock which is the same as PCI clock on the host, and dual USB host controller with four USB ports that deliver better connectivity and 2 x 12Mb bandwidth.

The built-in fast PCI IDE controller supports the ATA PIO/DMA, and the Ultra DMA33/66 function that supports the data transfer rate up to 66 MB/s. It provides a separate data path for two IDE channels that can eminently improve the performance under the multi-tasking environment.

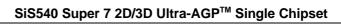

The following illustrates the system block diagram.

Figure 1-1 SiS540 System Block Diagram

# 1.1 Function Block Reference

| TableBus # | Device # | Function # | Device ID | IDSEL | Device Function              |

|------------|----------|------------|-----------|-------|------------------------------|

| Bus 0      | Device 0 | Function 0 | 0540h     | AD11  | North Bridge                 |

| Bus 0      | Device 0 | Function 1 | 5513h     | AD11  | PCI IDE                      |

| Bus 1      | Device 0 | Function 0 | 5300h     | AD11  | GUI                          |

| Bus 0      | Device 1 | Function 0 | 0008h     | AD12  | LPC                          |

| Bus 0      | Device 1 | Function 1 | 0900h     | AD12  | LAN                          |

| Bus 0      | Device 1 | Function 2 | 7001h     | AD12  | USB 0                        |

| Bus 0      | Device 1 | Function 3 | 7001h     | AD12  | USB 1                        |

| Bus 0      | Device 1 | Function 4 | 7018h     | AD12  | H/W Audio                    |

| Bus 0      | Device 1 | Function 6 | 7013h     | AD12  | S/W Modem                    |

| Bus 0      | Device 2 | Function 0 | 0001h     | AD13  | Virtual PCI-to-PCI<br>Bridge |

### 2 Features

# Supports Intel/AMD/Cyrix/IDT Pentium CPU Host Bus at 66/83/90/95/100 MHz with 3.3V Bus Interface

- Supports the Pipelined Address of Pentium Compatible CPU

- 100/100, 95/95, 90/90 and 83/83 MHz Synchronous Host/DRAM Clocking Configuration

- 100/133, 100/66 and 66/100 MHz Asynchronous Host/DRAM Clocking Configuration

- Supports Host Bus Direct Access GUI Engine for Integrated 3D VGA Controller

## **Integrated Level 2 Cache Controller**

- Write Back And Write through Cache Mode

- Direct Mapped Cache Organization

- Supports Pipelined Burst SRAM

- Supports 256K/512K/1M/2M Bytes Cache Sizes

- Cache Hit Read/Write Cycle of 3-1-1-1

- Cache Back-To-Back Read Cycle of 3-1-1-1-1-1

- Supports Single Read Allocation for L2 Cache

- Supports Concurrency of CPU to L2 Cache and Integrated A.G.P. VGA Master to DRAM Accesses

#### **Integrated DRAM Controller**

- Supports up to 3 Double Sided DIMMs (6 Rows Memory)

- Supports PC100/PC133 SDRAM Technology

- Supports NEC Virtual Channel Memory (VC-SDRAM) Technology

- System Memory Size up to 1.5 GB

- Supports Cacheable DRAM Sizes up to 512 Mbytes

- Supports 16Mb, 64Mb, 128Mb, 256Mb, 512Mb SDRAM Technology

- Suspend-To-RAM (STR)

- Relocatable System Management Memory Region

- Programmable Buffer Strength for CS#, DQM[7:0], WE#, RAS#, CAS#, CKE, MA[14:0] and MD[63:0]

- Shadow RAM Size from 640KB to 1MB In 16KB Increments

- Two Programmable PCI Hole Areas

#### Integrated A.G.P. Compliant Target Host-To-PCI Bridge

■ AGP V2.0 Compliant

- Supports Graphic Window Size from 4Mbytes To 256Mbytes

- Supports Pipelined Process in CPU-To-Integrated 3D A.G.P. VGA Access

- Supports 8 Way, 16 Entries Page Table Cache for GART to Enhance Integrated A.G.P. VGA Controller Read/Write Performance

- Supports PCI-To-PCI Bridge Function for Memory Write from 33Mhz PCI Bus to Integrated A.G.P. VGA

### **Meets PC99 Requirements**

## **PCI 2.2 Specification Compliant**

### **High Performance PCI Arbiter**

- Supports up to 4 PCI Masters

- Rotating Priority Arbitration Scheme

- Advanced Arbitration Scheme Minimizing Arbitration Overhead

- Guaranteed Minimum Access Time for CPU And PCI Masters

## **Integrated Host-To-PCI Bridge**

- Zero Wait State Burst Cycles

- CPU-To-PCI Pipeline Access

- 256B to 4KB PCI Burst Length for PCI Masters

- PCI Master Initiated Graphical Texture Write Cycles Re-Mapping

- Reassembles PCI Burst Data Size into Optimized Block Size

#### **Fast PCI IDE Master/Slave Controller**

- Supports PCI Bus Mastering

- Native Mode and Compatibility Mode

- PIO Mode 0, 1, 2, 3, 4

- Multiword DMA Mode 0, 1, 2

- Ultra DMA 33/66

- Two Independent IDE Channels Each with 16 DW FIFO

## Virtual PCI-To-PCI Bridge

## Integrated Ultra-AGP™ VGA for Hardware 2D/3D Video/Graphics Accelerators

- Supports Tightly Coupled 64 Bits 100Mhz Host Interface to VGA to Speed Up GUI

Performance and the Video Playback Frame Rate

- AGP Rev. 2.0 Compliant

- Zero-Wait-State 128x4 Post-Write Buffer with Write Combine Capability

- Zero-Wait-State 128x4 2-Way Read Ahead Cache Capability

- Re-Locatable Memory-Mapped and I/O Address Decoding

- Flexible Design Shared Frame Buffer Architecture for Display Memory

- Shared System Memory Area up to 64MB

- Built-In 8K Bytes Texture Cache

- 32-Bit VLIW Floating-Point Primitive Setup Engine

- Peak Polygon Rate: 4M Polygon/Sec @ 1 Pixel/Polygon with 16bpp, Bilinear Textured,

Z Buffered and Alpha Blended

- Supports Flat and Gouraud Shading

- Supports High Quality Dithering

- Supports Z-Test, Stencil Test, Alpha Test and Scissors Clipping Test

- Supports Z Pre-Test for Reducing Texture Read DRAM Bandwidth

- Supports 256 Rops

- Supports Individual Z-Buffer and Render Buffer at the same time

- Supports 16/24/32 BPP Z Buffer Integer/Floating Formats

- Supports 16/32 BPP Render Buffer Format

- Supports 1/2/4/8 Stencil Format

- Supports Per-Pixel Texture/Fog Perspective Correction

- Supports MIPMAP with Point-Sampled, Linear, Bi-Linear and Tri-Linear Texture

Filtering

- Supports Single Pass Two MIPMAP Texture, One Texture On Clock

- Supports up to 2048x2048 Texture Size

- Supports 2'S Power of Width and Height Structure Rectangular Texture

- Supports 1/2/4/8 BPP Palletize Texture with 32 Bit ARGB Format

- Supports Palette for High Performance Palette Look Up

- Supports 1/2/4/8 BPP Luminance Texture

- Supports 1/2/4/8 BPP Intensity Texture

- Supports 8/16/24/32 BPP RGB/ARGB Texture Format

- Supports Video YUV Texture in all Supported Texture Formats

- Supports MIP-Mapped Texture Transparency, Blending, Wrapping, Mirror and Clamping

- Supports Fogging and Alpha Blending

- Supports Vertex Fogging, Linear Fogging Table and Non-Linear Fogging Table

- Supports Specula Lighting

- Supports Sort Dependent Edge Anti-Aliasing

- Supports Full Scene Anti-Aliasing

- Supports Hardware Back Face Culling

- Internal Full 32 Bits ARGB Format Ultra Pipelined Architecture for Ultra High Performance and High Rendering Quality

- 128-Bit 2D Engine with a Full Instruction Set

- Built-In 64x64x2 Bit-Mapped Hardware Cursor

- Built-In 32x32x16, 32x32x32 Bit-Mapped Color Hardware Cursor

- Maximum 64 MB Frame Buffer with Linear Addressing

- MPEG-2 ISO/IEC 13818-2 MP@ML and MPEG-1 ISO/IEC 11172-2 Standards Compliant

- Supports Advanced H/W DVD Accelerator

- Direct DVD to TV Playback

- Supports Single Frame Buffer Architecture

- Supports Two Independent Video Windows with Overlay Function and Scaling Factors

- Supports YUV-To-RGB Color Space Conversion

- Supports Bi-Linear Video Interpolation with Integer Increments of Pixel Accuracy

- Supports Graphic and Video Overlay Function

- Supports VCD/DVD to TV Playback Mode

- Simultaneous Graphic and TV Video Playback Overlay

- Supports Current Scan Line Of Refresh Red-Back and Interrupt

- Supports Tearing Free Double/Triple Buffer Flipping

- Supports Input Video Vertical Blank or Line Interrupt

- Supports RGB555, RGB565, YUV422 and YUV420 Video Playback Format

- Supports Filtered Horizontal up and down Scaling Playback

- Supports DVD Sub-Picture Playback Overlay

- Supports DVD Playback Auto-Flipping

- Built-In Two Video Playback Line Buffers

- Supports DCI Drivers

- Supports Direct Draw Drivers

- Built-In Programmable 24-Bit True-Color RAMDAC up to 270 Mhz Pixel Clock RAMDAC

Snoop Function

- Built-In Reference Voltage Generator and Monitor Sense Circuit

- Supports Down-Loadable RAMDAC for Gamma Correction In High Color and True Color Modes

- Built-In Dual-Clock Generator

- Supports Multiple Adapters and Multiple Monitors

- Built-In PCI Multimedia Interface

- Built-In VESA Plug and Display for Digital TV-Out Encoder, Panellink<sup>™</sup> (TMDS) and LVDS Digital Interface

- Supports Digital Flat Panel Port for Digital Monitor (LCD Panel)

- Built-In Secondary CRT Controller for Independent Secondary CRT, LCD or TV Digital

Output

- Supports VESA Standard Super High Resolution Graphic Modes

| 640x480   | 16/256/32K/64K/16M Colors 120 Hz NI |

|-----------|-------------------------------------|

| 800x600   | 16/256/32K/64K/16M Colors 120 Hz NI |

| 1024x768  | 256/32K/64K/16M Colors 120 Hz NI    |

| 1280x1024 | 256/32K/64K/16M Colors 120 Hz NI    |

| 1600x1200 | 256/32K/64K/16M Colors 100 Hz NI    |

| 1920x1200 | 256/32K/64K/16M Colors 80 Hz NI     |

Low Resolution Modes

- Supports Virtual Screen up to 4096x4096

- Fully DirectX 6.0 Compliant

- Efficient and Flexible Power Management with ACPI Compliance

- Supports DDC1, DDC2B and DDC 3.0 Specifications

- Cooperate with "SiS301 Video Bridge" to Support

NTSC/PAL Video Output

Digital LCD Monitor

Secondary CRT Monitor

## **Low Pin Count Interface**

- Forwards PCI I/O and Memory Cycles into LPC Bus

- Translates 8-/16-Bit DMA Cycles into PCI Bus Cycles

### Advanced PCI H/W Audio & S/W Modem

■ Advanced Wavetable Synthesizer

64-Voices Polyphony Wavetable Synthesizer Supports All Combinations of

Stereo/Mono, 8-/16-Bits, and Signed/Unsigned Samples

Per Channel Volume and Envelop Control, Pitch Shift, Left/Right Pan, Tremolo, and Vibrato

Global Effect Process for Reverb, Chorus and Echo

DirectMusic<sup>™</sup> Support with Unlimited Downloadable Samples in System Memory

DLS-1-Compatible Downloadable Samples Support

■ DirectSound<sup>™</sup>3D

64-Voice DirectSound™ Channels

32-Voice DirectSound<sup>™</sup> 3D Accelerator with IID, IAD and Doppler Effects on 3D Positional Audio Buffer

DirectSound Accelerator for Volume, Pan and Pitch Shift Control on Streaming or Static Buffers

VirtualHRTF Interactive 3D Positional Audio Accelerator for DirectX<sup>™</sup> 5/6

Advanced Streaming Architecture

Microsoft WDM Streaming Architecture Compliant and Re-Routable Endpoint Support Three Stereo Capture Channels

AC' 97/98 Stereo Recording Channel through AC-Link

■ High Quality Audio and AC 97/98 Support

CD Quality Audio with 90db+ SNR Using External High Quality AC 97/98 CODEC AC 97/98 Support with Full Duplex, Independent Sample Rate Converter for Audio Recording and Playback

On-Chip Sample Rate Converter Ensures All Internal Operation At 48khz High Precision Internal 26-Bit Digital Mixer with 20-Bit Digital Audio Output

■ Full Legacy Compatibility

SoundBlaster Pro/16

VirtualFM<sup>™</sup> Enhances Audio Experience through Realtime FM-To-Wavetable Conversion

MPU-401 Compatible UART for External Or Internal Synthesis

■ Telephony & Modem

Full Duplex VirtualPhone Speaker Phone With Modem Capable AC 97/98 HSP V.90 Modem

■ Software Support

Complete DirectX Driver Suite (DirectSound3D, DirectSound, DirectMusic, DirectInput) for Windows 98/Windows 2000

Configuration Installation and Diagnostics Under Real Mode DOS, Windows 98 DOS Box

Windows 98/ Windows 2000 Configuration, Installation and Mixer Program

■ Extras

2-To-6 Speakers Output with Optional VirtaulFX, VirtualAC3

DirectX Timer for Video/Audio Synchronization I<sup>2</sup>S and SPDIF Interface

### **Advanced Power Management**

- Meets ACPI 1.0 Requirements

- Meets APM 1.2 Requirements

- ACPI Sleep States Include S1, S2, S3, S4, S5

- CPU Power States Include C0, C1, C2, C3

- Power Button with Override

- RTC Day-Of-Month, Month-Of-Year Alarm

- 24-Bit Power Management Timer

- LED Blinking In S0,S1,S2 and S3 States

- System Power-Up Events Include: Power Button, Hot-Key, Keyboard Password/ Hot-Key, RTC Alarm, Modem Ring-In, SMBALT#, LAN, PME#, AC 97 Wake-Up and USB Wake-Up

- Software Watchdog Timer

- PCI Bus Power Management Interface Spec. 1.0

#### **Integrated DMA Controller**

- Two 8237A Compatible DMA Controllers

- 8/16- Bit DMA Data Transfer

- Distributed DMA Support

## **Integrated Interrupt Controller**

- Two 8259A Compatible Interrupt Controllers

- Level- Or Edge-Triggered Programmable Serial IRQ

- Interrupt Sources Re-Routable to Any IRQ Channel

### Three 8254 Compatible Programmable 16-Bit Counters

- System Timer Interrupt

- Generate Refresh Request

- Speaker Tone Output

## **Integrated Keyboard Controller**

- Hardwired Logic Provides Instant Response

- Supports PS/2 Mouse Interface

- Password Security and Password Power-Up

- System Sleep and Power-Up By Hot-Key

- KBC and PS/2 Mouse Can Be Individually Disabled

## Integrated Real Time Clock (RTC) with 256B CMOS SRAM

- Supports ACPI Day-Of-Month and Month-Of-Year Alarm

- 256 Bytes Of CMOS SRAM

- Provides RTC H/W Year 2000 Solution

### **Universal Serial Bus Host Controller**

- OpenHCI Host Controller with Root Hub

- Two USB Host Controllers

- Four USB Ports

- Supports Legacy Devices

- Over Current Detection

## I<sup>2</sup>C Bus/SMBUS Series Interface

# Integrated Fast Ethernet Controller and 10/100 Megabit Per Second (Mbps) Physical Layer Transceivers for the PCI Local Bus

- Plug and Play Compatible

- High-Performance 32-Bit PCI Bus Master Architecture with Integrated Direct Memory Access (DMA ) Controller for Low CPU and Bus Utilization

- Supports An Unlimited PCI Burst Length

- Supports Big Endian and Little Endian Byte Alignments

- Supports PCI Device ID, Vendor ID/Subsystem ID, Subsystem Vendor ID

Programming through the EEPROM Interface

- Implements Optional PCI 3.3V Auxiliary Power Source 3.3Vaux Pin and Optional PCI

- IEEE 802.3 and 802.3u Standard Compatible

- IEEE 802.3u Auto Negotiation and Parallel Detection for Automatic Speed Selection

- Full Duplex and Half Duplex Mode for Both 10 and 100 Mbps.

- Fully Compliant ANSI X3.263 TP-PMD Physical Sub-Layer Which Includes Adaptive Equalization and Baseline Wander Correction.

- Automatic Jam and IEEE 802.3x Auto-Negotiation for Flow Control

- Single Access to Complete PHY Register Set

- Built-In Waveform Shaping Requires No External Filters

- Single 25Mhz Clock for 10 and 100 Mbps Operation.

- Power Down Of 10Base-T/100Base-TX Sections When Not In Use

- Jabber Control and Auto-Polarity Correction for 10Base-T.

- User Programmable LED Function Mapping

- Supports Software, Enhanced Software, and Automatic Polling Schemes to Internal

PHY Status Monitor and Interrupt

■ Supports 10BASE-T, 100BASE-TX

NAND Tree for Ball Connectivity Testing

618-Balls BGA Package

1.8V Core with Mixed 3.3V and 5V I/O CMOS Technology

- 3 Pin Assignment

- 3.1 Pin Assignment (Top View)

- 3.1.1 SiS540 Pin Assignment (Top View-Left Side)

|    | 1        | 2         | 3        | 4          | 5        | 6       | 7        | 8      | 9         | 10       | 11       | 12     | 13      | 14        | 15      |

|----|----------|-----------|----------|------------|----------|---------|----------|--------|-----------|----------|----------|--------|---------|-----------|---------|

| A  |          |           | EESK     | TXAVDD     | REXT     | HRTXRXN | AD7      | AD12   | C/BE1#    | IRDY#    | AD19     | C/BE3# | AD28    | PGNT1#    | PGNT0#  |

| В  |          | AC_RESET# | EEDI     | RXAVDD     | OSC25MHI | HRTXRXP | AD5      | AD11   | AD15      | TRDY#    | AD17     | AD23   | AD26    | PGNT2#    | PREQ1#  |

| С  | PMCLK    | AC_SDIN1  | AC_SDIN0 | EEDO       | RXAVSS   | ADI     | AD4      | AD10   | AD14      | DEVSEL#  | AD16     | AD21   | AD25    | AD30      | PREQ0#  |

| D  | ACPILED  | KBDAT     | KBCLK    | PMDAT      | PLED0#   | EECS    | AD3      | AD8    | AD13      | STOP#    | C/BE2#   | AD20   | AD24    | AD29      | SMI#    |

| Е  | USBVDD   | UV3-      | PME#     | SMBALT#    | PSON#    | PCIRST# | AD2      | C/BE0# | AD6       | PAR      | PLOCK#   | AD18   | AD22    | AD31      | PREQ2#  |

| F  | UV3+     | USBVDD    | UV2+     | PWRBTN#    | CKE      | RING    |          | AD0    |           | AD9      |          | FRAME# |         | AD27      | INIT#   |

| G  | RTCVDD   | AUXOK     | UV0+     | UV1+       | UV2-     |         |          |        |           |          |          |        |         |           |         |

| Н  | OSC32KHO | OSC32KHI  | PWROK    | RTCVSS     | UV0-     | UVI-    |          |        |           |          |          |        |         | VCC3      | VCC3    |

| J  | CLK48M   | SMCLK     | INTD#    | INTC#      | INTB#    |         |          |        | TPI-      | TPI+     | TPO-     | TPO+   | VCC3    | VCC3      | VCC3    |

| K  | EXTSMI#  | AC_SYNC   | AC_SDOUT | SMBDAT     | INTA#    | BATOK   |          |        | OVDD(AUX) |          |          |        |         |           |         |

| L  | VMD63    | GPIO7     | GPIO1    | AC_BIT_CLK | SERR#    |         |          |        | IVDD(AUX) |          |          |        |         |           |         |

| М  | VMD58    | VMD60     | VMD61    | VMD62      | GPIO2    | GPIO0   |          |        | VCC3      |          |          | RXAVSS | TXAVSS  | OSC25AVSS | VSS     |

| N  | VDQM6    | VDQM7     | VMD56    | VMD57      | VMD59    |         |          | VCC3   | VCC3      |          |          | VSS    | VSS     | VSS       | VSS     |

| P  | VMD53    | VMD55     | VDQM4    | VDQM5      | VMD54    | VCS#    |          | VCC3   | VCC3      |          |          | VSS    | VSS     | VSS       | VSS     |

| R  | VMD49    | VMD50     | VMD51    | VMD52      | VMD44    | VMD48   |          | VCC3   | VCC3      |          |          | VSS    | VSS     | VSS       | VSS     |

| T  | VMD47    | VMD46     | VMD45    | VMD43      | VMD40    | VMD32   |          | VCC3   | VCC3      |          |          | VSS    | VSS     | VSS       | VSS     |

| U  | VMD42    | VMD41     | VMD39    | VMD38      | VMD31    |         |          |        | VCC3      |          |          | VSS    | VSS     | VSS       | VSS     |

| v  | VMD37    | VMD36     | VMD35    | VMD34      | VMD27    | VDQM3   |          |        | VCC3      |          |          | VSS    | VSS     | VSS       | VSS     |

| W  | VMD33    | VMA10     | VMA11    | VBA1       | VMD23    |         | l .      |        | IVDD      |          |          |        |         |           |         |

| Y  | VMD30    | VMD29     | VMD28    | VMD26      | VMD25    | VMD15   |          |        | IVDD      |          |          |        |         |           |         |

| AA | VMD24    | VDQM2     | VDQM1    | VDQM0      | VMD7     |         |          |        | IVDD      | IVDD     | IVDD     | VCC3   | VCC3    | VCC3      | VCC3    |

| AB | VMD22    | VMD21     | VMD20    | VMD19      | VMD18    | SSYNC   |          |        |           |          |          |        |         | VCC3      | VCC3    |

| AC | VMD17    | VMD16     | VMD14    | VMD13      | VMD12    |         | <u> </u> |        | <u> </u>  |          |          |        |         |           |         |

| AD | VMD11    | VMD10     | VMD9     | VMD8       | VMD6     | LAD0    |          | IDA8   |           | IDA10    |          | IDA14  |         | CBLIDA    | IDB10   |

| AE | VMD5     | VMD4      | VMD3     | VMD2       | SPK      | LDRQ#   | LAD3     | IDA3   | IDA9      | IDACKA#  | IDA12    | IDREQA | IIRQA   | IDB8      | IDB12   |

| AF | VMD1     | VMD0      | VSYNC    | COMP       | LAD2     | SIRQ    | LFRAME#  | IDA2   | IDA15     | IDSAA1   | IDECSA1# | IDB5   | IDB2    | IDB14     | IDREQB  |

| AG | OSCI     | HSYNC     | DDCDATA  | RSET       | LADI     | IDA7    | IDA5     | IDA13  | IIOWA#    | IDSAA0   | IDB7     | IDB4   | IDB13   | IDB15     | IDSAB2  |

| АН |          | DDCCLK    | DCLKAVDD | VREF       | ROUT     | DACAVDD | IDA4     | IDA1   | ICHRDYA   | IDSAA2   | IDB6     | IDB11  | IDB1    | IIOWB#    | IDACKB# |

| AJ |          |           | ECLKAVDD | BOUT       | GOUT     | IDA6    | IDA11    | IDA0   | IIORA#    | IDECSA0# | IDB9     | IDB3   | IDEAVDD | ICHRDYB   | IDSAB1  |

|    | 1        | 2         | 3        | 4          | 5        | 6       | 7        | 8      | 9         | 10       | 11       | 12     | 13      | 14        | 15      |

# 3.1.2 SiS540 Pin Assignment (Top View-Right Side)

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | 1      |      | ı    |      |      |       | ı    |        | ı      |          |       |         |         |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|------|------|------|-------|------|--------|--------|----------|-------|---------|---------|----|

| STECLAR   NET   1801                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16       | 17     | 18   | 19   | 20   | 21   | 22    | 23   | 24     | 25     | 26       | 27    | 28      | 29      |    |

| CHISST   102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A20M#    | NMI    | HD11 | HD12 | HD14 | HD22 | HD26  | HD42 | HD46   | HD44   | HD48     | HD51  |         |         | Α  |

| Model   Hor   Ho | STPCLK#  | INTR   | HD3  | HD7  | HD13 | HD21 | HD28  | HD31 | HD40   | HD45   | HD49     | HD53  | HD55    |         | В  |

| February   High   Hig | CPURST   | HD2    | HD5  | HD9  | HD18 | HD19 | HD27  | HD32 | HD37   | HD41   | HD50     | HD54  | HD56    | HD57    | С  |

| HIDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IGNE#    | HD1    | HD6  | HD10 | HD16 | HD23 | HD30  | HD35 | HD39   | HD43   | HD52     | HD58  | HD59    | HD60    | D  |

| VCC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FERR#    | HD4    | HD8  | HD20 | HD17 | HD25 | HD29  | HD34 | HD36   | HD47   | HD61     | HD62  | HD63    | SMIACT# | E  |

| VCC3         VCD         IVDD         IVDD         IVDD         INAP         IHA19         IHA17         IHA16         IHA15         IHA13         K           I         I         I         IVDD         I         IMBE##         IHA19         IHA17         IHA16         IHA15         IHA13         K           I         I         I         IVDD         I         IMBE##         IHA18         IHA1         IHA10         IHA5         I         I         IIA17         IHA1         IHA10         IHA5         IIA17         IHA1         IHA10         IHA5         IIA17         IHA1         IHA11         IHA10         IHA5         IHA1         IHA11         IHA10         IHA14         IHA21         IHA4         IHA21         IHA4         IHA22         IHA4         IHA22         IHA4         IHA22         IHA4         IHA22         IHA4         IHA22         IHA4         IHA23         IHA44         IHA23         IHA44         IHA23         IHA44         IHA23         IH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | HD0      |        | HD15 |      | HD24 |      | HD33  |      | HD38   | M/IO#  | KEN#/INV | AHOLD | BRDY#   | BOFF#   | F  |

| VCC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |        |      |      |      |      |       |      |        | D/C#   | ADS#     | HITM# | CPUAVDD | CPUCLK  | G  |

| NA#   HA19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VCC3     |        |      |      |      |      |       |      | CACHE# | W/R#   | EADS#    | HBE0# | HBE2#   | HBE3#   | Н  |

| VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VCC3     | VCC3   | VCC3 | IVDD | IVDD | IVDD |       |      |        | HLOCK# | HBE5#    | HBE6# | HBE7#   | HA20    | J  |

| VSS         VSS         VSS         VSS         VCC3         HBE##         HAIB         HAS         HA31         HA25         HA27         M           VSS         VSS         VSS         VSS         VCC3         VCC3         HAIL         HA7         HA3         HA25         HA4         N           VSS         VSS         VSS         VSS         VCC3         VCC3         HAIL         HA7         HA3         HA29         KOE#         HA30         P           VSS         VSS         VSS         VCC3         VCC3         HA26         HA23         BWE#         ADV#         ADSC#         HA6         R           VSS         VSS         VSS         VCC3         VCC3         CCSI#         HA28         TA2         TAI         TA0         GWE#         T           VSS         VSS         VSS         VSS         VCC3         VCC3         MB60         TAGWE#         MB06         MB30         MB63         MB31         V           VCC3         VCC3         VCC3         VCC3         MB56         MB27         MB25         MB38         MB26         MB39         Y           VCC3         VCC3         VCC3         MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |        |      |      |      | IVDD |       |      | NA#    | HA19   | HA17     | HA16  | HA15    | HA13    | K  |

| VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |        |      |      |      | IVDD |       |      |        | HBE1#  | HA9      | HA11  | HA10    | HA5     | L  |

| VSS         VSS         VSS         VCC3         VCC3         VCC3         HA12         HA7         HA3         HA29         KOE#         HA30         P           VSS         VSS         VSS         VCC3         VCC3         CCS1#         HA26         HA28         BWE#         ADV#         ADSC#         HA6         R           VSS         VSS         VSS         VCC3         VCC3         CCS1#         HA28         TA2         TA1         TA0         GWE#         T           VSS         VSS         VSS         VCC3         CCS1#         MD60         TAGWE#         MD62         MD30         MD63         MD31         V           VSS         VSS         VSS         VSS         VCC3         VCC3         MD60         TAGWE#         MD62         MD30         MD63         MD31         V           VSS         VSS         VSS         VSS         VCC3         VCC3         MD60         TAGWE#         MD62         MD30         MD63         MD31         V           VCC3         VCC3         IVDD         IVDD         MD54         MD57         MD28         MD58         MD64         MD59         Y           VCC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VSS      | VSS    | VSS  |      |      | VCC3 |       |      | HBE4#  | HA18   | HA8      | HA31  | HA25    | HA27    | M  |

| VSS         VSS         VSS         VCC3         VCC3         VCC3         HA26         HA25         BWE#         ADV#         ADSC#         HA6         R           VSS         VSS         VSS         VCC3         VCC3         CCS1#         HA28         TA2         TA1         TA0         GWE#         T           VSS         VSS         VSS         VCC3         WCC3         MD60         TAGWE#         MD62         MD30         MD63         MD31         V           VSS         VSS         VSS         VCC3         WCC3         MD60         TAGWE#         MD62         MD63         MD31         V           WCS         VSS         VSS         VSS         WCC3         WCC3         MD60         TAGWE#         MD62         MD63         MD31         V           WCC3         VSS         VSS         VCC3         WCC3         WCC3         MD60         MD54         MD57         MD25         MD68         MD60         MD69         W           VCC3         VCC3         IVDD         IVDD         IVDD         MD70         MD70         MD70         MD73         MD21         AA           VCC3         VCC3         IVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VSS      | VSS    | VSS  |      |      | VCC3 |       |      |        | HA14   | HA21     | HA24  | HA22    | HA4     | N  |

| VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VSS      | VSS    | VSS  |      |      | VCC3 | VCC3  |      | HA12   | HA7    | HA3      | HA29  | KOE#    | HA30    | P  |