# intel

### Intel<sup>®</sup> 815 Chipset: Graphics Controller

**Programmer's Reference Manual (PRM)**

July 2000

Order Number: 298237-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 815 chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2C$  is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert On LAN\* is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

www.intel.com

or call 1-800-548-4725

\*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 2000

# Contents

| 1. | Introd             | uction                                                                                                               | 15 |

|----|--------------------|----------------------------------------------------------------------------------------------------------------------|----|

|    | 1.1.               | Terminology                                                                                                          | 15 |

|    | 1.2.               | Reference Documents                                                                                                  |    |

| 2. | Intel <sup>®</sup> | 815 Chipset Overview                                                                                                 | 17 |

|    | 2.1.               | I/O Controller Hub                                                                                                   |    |

|    | 2.2.               | Intel <sup>®</sup> 82815 Chipset GMCH Overview                                                                       |    |

|    |                    | 2.2.1. Host Interface                                                                                                |    |

|    |                    | 2.2.2. System Memory Interface                                                                                       |    |

|    |                    | 2.2.3. Multiplexed AGP and Display Cache Interface                                                                   |    |

|    |                    | 2.2.4. Hub Interface                                                                                                 |    |

|    |                    | 2.2.5. Intel <sup>®</sup> 82815 Chipset GMCH Integrated Graphics Support                                             |    |

|    |                    | 2.2.6. System Clocking                                                                                               |    |

|    |                    | 2.2.7. GMCH Power Delivery                                                                                           |    |

|    | 2.3.               | Three PCI Devices on GMCH                                                                                            |    |

|    |                    | 2.3.1. Multi-Mode Capability Requirements                                                                            |    |

|    |                    | <ul><li>2.3.1.1. Supported Single Monitor and Multi-monitor Configurations</li><li>2.3.1.2. System Startup</li></ul> |    |

|    |                    | 2.3.1.2. System Startup<br>2.3.1.3. Software Start-Up Sequence                                                       |    |

|    |                    | 2.3.1.4. Switching Device modes                                                                                      |    |

| 3. | Suctor             | m Address Map                                                                                                        |    |

| 3. | 3.1.               | Memory and I/O Space Registers                                                                                       |    |

|    | 3.1.<br>3.2.       |                                                                                                                      |    |

|    |                    | GC Register Memory Address Map                                                                                       |    |

|    | 3.3.               | VGA and Extended VGA Register Map                                                                                    |    |

|    | 2.4                | 3.3.1. VGA and Extended VGA I/O and Memory Register Map                                                              |    |

|    | 3.4.               | Indirect VGA and Extended VGA Register Indices                                                                       |    |

|    |                    | <ul><li>3.4.1. Graphics Address Translation</li><li>3.4.2. Memory Buffers for GC's Instruction Interface</li></ul>   |    |

|    | <b>.</b> .         | -                                                                                                                    |    |

| 4. | Graph              | nics Translation Table (GTT) Range Definition                                                                        | 43 |

| 5. | Basic              | Initialization Procedures                                                                                            | 45 |

|    | 5.1.               | Initialization Sequence                                                                                              | 45 |

|    | 5.2.               | Hardware Detection (Probe)                                                                                           | 45 |

|    | 5.3.               | Frame Buffer Initialization                                                                                          | 46 |

|    | 5.4.               | Hardware Register Initialization                                                                                     | 47 |

|    |                    | 5.4.1. Color vs. Monochrome Monitors                                                                                 |    |

|    |                    | 5.4.2. Protect Registers: Locking and Unlocking                                                                      |    |

|    |                    | 5.4.3. Checking Memory Frequency                                                                                     | 47 |

|    | 5.5.               | Hardware State                                                                                                       |    |

|    | 5.6.               | Saving the Hardware State                                                                                            | 48 |

|    | 5.7.               | Restoring the Hardware State                                                                                         | 49 |

| 6. | Blt En             | gine Programming                                                                                                     | 53 |

|    | 6.1.               | BLT Engine Programming Considerations                                                                                |    |

|    |                    | 6.1.1. When the Source and Destination Locations Overlap                                                             |    |

|    | 6.2.               | Basic Graphics Data Considerations                                                                                   |    |

|    |                    | 6.2.1. Contiguous vs. Discontinuous Graphics Data                                                                    | 57 |

|    |                    |                                                                                                                      |    |

|    |            | 6.2.2.<br>6.2.3. | Source Data                                                                               | 59  |

|----|------------|------------------|-------------------------------------------------------------------------------------------|-----|

|    |            | 6.2.4.           | Pattern Data                                                                              |     |

|    | 6.0        | 6.2.5.           | Destination Data                                                                          |     |

|    | 6.3.       |                  | gramming Examples                                                                         |     |

|    |            | 6.3.1.<br>6.3.2. | Pattern Fill A Very Simple BLT<br>Drawing Characters Using a Font Stored in System Memory |     |

| 7. | Initiali   |                  |                                                                                           |     |

| 1. |            |                  | isters                                                                                    |     |

|    | 7.1.       |                  | I VGA Registers                                                                           |     |

|    | 7.2.       |                  | Registers                                                                                 |     |

|    |            | 7.2.1.           | SMRAM—System Management RAM Control Register (Device 0)                                   |     |

|    | 7.3.       |                  | I/O, GPIO, Clock, LCD, and Pixel Pipeline Registers                                       |     |

|    | 7.4.       |                  | hics Controller Registers (3CEh / 3CFh)                                                   |     |

|    | 7.5.       | 2D CRT           | Controller Registers (3B4h/3D4h/3B5h/3D5h)                                                | 73  |

|    | 7.6.       | Initializat      | ion Values for VGA Registers                                                              | 74  |

| 8. | Frame      | e Buffer Ac      | cess                                                                                      | 77  |

| 9. | VGA ;      | and Extend       | ed VGA Registers                                                                          | 79  |

| 0. | 9.1.       |                  | Control & Status Registers                                                                |     |

|    | 9.1.       | 9.1.1.           | ST00—Input Status 0                                                                       |     |

|    |            | 9.1.1.<br>9.1.2. | ST00—Input Status 0<br>ST01—Input Status 1                                                |     |

|    |            | 9.1.2.           | FCR—Feature Control                                                                       |     |

|    |            | 9.1.4.           | MSR—Miscellaneous Output                                                                  |     |

|    | 9.2.       |                  | er Registers                                                                              |     |

|    | 0.2.       | 9.2.1.           | SRX—Sequencer Index                                                                       |     |

|    |            | 9.2.2.           | SR00—Sequencer Reset                                                                      |     |

|    |            | 9.2.3.           | SR01—Clocking Mode                                                                        |     |

|    |            | 9.2.4.           | SR02—Plane/Map Mask                                                                       |     |

|    |            | 9.2.5.           | SR03—Character Font                                                                       |     |

|    |            | 9.2.6.           | SR04—Memory Mode Register                                                                 |     |

|    |            | 9.2.7.           | SR07—Horizontal Character Counter Reset                                                   | 90  |

|    | 9.3.       | Graphics         | Controller Registers                                                                      |     |

|    |            | 9.3.1.           | GRX—GRX Graphics Controller Index Register                                                |     |

|    |            | 9.3.2.           | GR00—Set/Reset Register                                                                   |     |

|    |            | 9.3.3.           | GR01—Enable Set/Reset Register                                                            |     |

|    |            | 9.3.4.           | GR02—Color Compare Register                                                               |     |

|    |            | 9.3.5.           | GR03—Data Rotate Register                                                                 |     |

|    |            | 9.3.6.           | GR04—Read Plane Select Register                                                           | 93  |

|    |            | 9.3.7.           | GR05—Graphics Mode Register                                                               | 93  |

|    |            | 9.3.8.           | GR06—Miscellaneous Register                                                               | 96  |

|    |            | 9.3.9.           | GR07—Color Don't Care Register                                                            |     |

|    |            | 9.3.10.          | GR08—Bit Mask Register                                                                    |     |

|    |            | 9.3.11.          | GR10—Address Mapping                                                                      |     |

|    |            | 9.3.12.          | GR11—Page Selector                                                                        |     |

|    | <b>-</b> . | 9.3.13.          | GR[14:1F]—Software Flags                                                                  |     |

|    | 9.4.       |                  | Controller Registers                                                                      |     |

|    |            | 9.4.1.           | ARX—Attribute Controller Index Register                                                   |     |

|    |            | 9.4.2.           | AR[00:0F]—Palette Registers [0:F]                                                         |     |

|    |            | 9.4.3.           | AR10—Mode Control Register                                                                |     |

|    |            | 9.4.4.           | AR11—Overscan Color Register                                                              | 104 |

|      | 9.4.5.    | AR12—Memory Plane Enable Register                                    | 1 | 04 |

|------|-----------|----------------------------------------------------------------------|---|----|

|      | 9.4.6.    | AR13—Horizontal Pixel Panning Register                               | 1 | 05 |

|      | 9.4.7.    | AR14—Color Select Register                                           | 1 | 06 |

| 9.5. | VGA Color | Palette Registers                                                    | 1 | 06 |

|      | 9.5.1.    | DACMASK—Pixel Data Mask Register                                     | 1 | 07 |

|      | 9.5.2.    | DACSTATE—DAC State Register                                          |   |    |

|      | 9.5.3.    | DACRX—Palette Read Index Register                                    |   |    |

|      | 9.5.4.    | DACWX—Palette Write Index Register                                   |   |    |

|      | 9.5.5.    | DACDATA—Palette Data Register                                        |   |    |

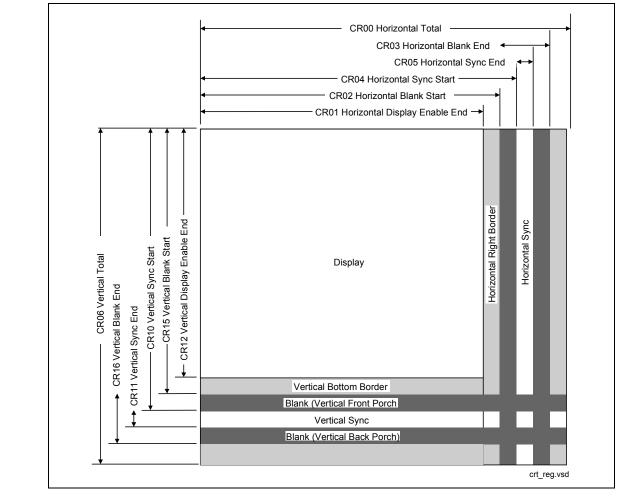

| 9.6. | CRT Contr | oller Register                                                       |   |    |

|      | 9.6.1.    | CRX—CRT Controller Index Register                                    |   |    |

|      | 9.6.2.    | CR00—Horizontal Total Register                                       |   |    |

|      | 9.6.3.    | CR01—Horizontal Display Enable End Register                          |   |    |

|      | 9.6.4.    | CR02—Horizontal Blanking Start Register                              |   |    |

|      | 9.6.5.    | CR03—Horizontal Blanking End Register                                |   |    |

|      | 9.6.6.    | CR04—Horizontal Sync Start Register                                  |   |    |

|      | 9.6.7.    | CR05—Horizontal Sync End Register                                    |   |    |

|      | 9.6.8.    | CR06—Vertical Total Register                                         |   |    |

|      | 9.6.9.    | CR07—Overflow Register                                               |   |    |

|      | 9.6.10.   | CR08—Preset Row Scan Register                                        |   |    |

|      | 9.6.11.   | CR09—Maximum Scan Line Register                                      |   |    |

|      | 9.6.12.   | CR0A—Text Cursor Start Register                                      |   |    |

|      | 9.6.13.   | CR0B—Text Cursor End Register                                        |   |    |

|      | 9.6.14.   | CR0C—Start Address High Register                                     | 1 | 20 |

|      | 9.6.15.   | CR0D—Start Address Low Register                                      |   |    |

|      | 9.6.16.   | CR0E—Text Cursor Location High Register                              |   |    |

|      | 9.6.17.   | CR0F—Text Cursor Location Low Register                               |   |    |

|      | 9.6.18.   | CR10—Vertical Sync Start Register                                    |   |    |

|      | 9.6.19.   | CR11—Vertical Sync End Register                                      |   |    |

|      | 9.6.20.   | CR12—Vertical Display Enable End Register                            | 1 | 24 |

|      | 9.6.21.   | CR13—Offset Register                                                 |   |    |

|      | 9.6.22.   | CR14—Underline Location Register                                     |   |    |

|      | 9.6.23.   | CR15—Vertical Blanking Start Register                                |   |    |

|      | 9.6.24.   | CR16—Vertical Blanking End Register                                  |   |    |

|      | 9.6.25.   | CR17—CRT Mode Control                                                | 1 | 27 |

|      | 9.6.26.   | CR18—Line Compare Register                                           | 1 | 31 |

|      | 9.6.27.   | CR22—Memory Read Latch Data Register                                 | 1 | 31 |

|      | 9.6.28.   | CR24—Test Register for Toggle State of Attribute Controller Register |   |    |

|      | 9.6.29.   | CR30—Extended Vertical Total Register                                | 1 | 32 |

|      | 9.6.30.   | CR31—Extended Vertical Display End Register                          |   |    |

|      | 9.6.31.   | CR32—Extended Vertical Sync Start Register                           | 1 | 34 |

|      | 9.6.32.   | CR33—Extended Vertical Blanking Start Register                       | 1 | 35 |

|      | 9.6.33.   | CR35— Extended Horizontal Total Time Register                        | 1 | 36 |

|      | 9.6.34.   | CR39—Extended Horizontal Blank Time Register                         |   |    |

|      | 9.6.35.   | CR40—Extended Start Address Register                                 |   |    |

|      | 9.6.36.   | CR41—Extended Offset Register                                        |   |    |

|      | 9.6.37.   | CR42—Extended Start Address High Register                            |   |    |

|      | 9.6.38.   | CR70—Interlace Control Register                                      |   |    |

|      | 9.6.39.   | CR80—I/O Control                                                     |   |    |

|      | 9.6.40.   | CR81—Reserved                                                        | 1 | 40 |

|      | 9.6.41.   | CR82—Blink Rate Control                                              | 1 | 40 |

|      |           |                                                                      |   |    |

| 10. | Progra | amming Inte        | erface               |                                                              | 141 |

|-----|--------|--------------------|----------------------|--------------------------------------------------------------|-----|

|     | 10.1.  | Reserved           | Bits and             | d Software Compatibility                                     |     |

|     | 10.2.  |                    |                      |                                                              |     |

|     | 10.3.  |                    |                      | ramming                                                      |     |

|     | 10.4.  | -                  | -                    | eams                                                         |     |

|     | 10.1.  | 10.4.1.            |                      | tion Use                                                     |     |

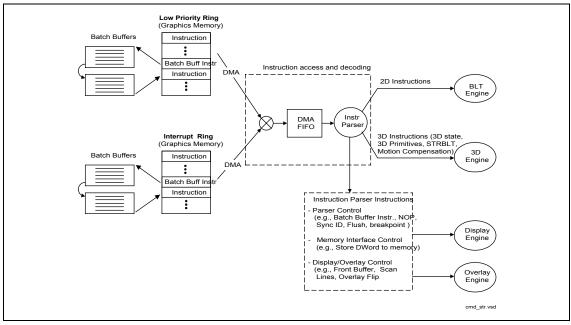

|     |        | 10.4.2.            |                      | tion Transport Overview                                      |     |

|     |        | 10.4.3.            |                      | tion Parser                                                  |     |

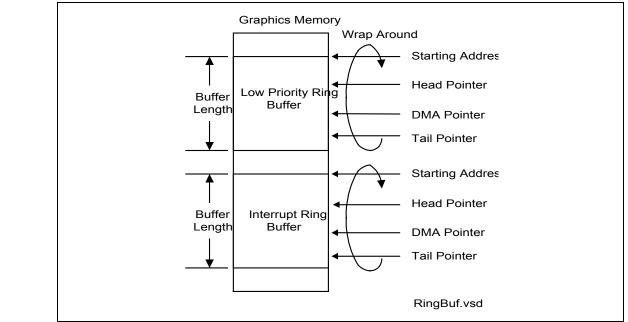

|     |        | 10.4.4.            |                      | Buffers (RB)                                                 |     |

|     |        | 10                 | 0.4.4.1.             |                                                              |     |

|     |        | 10                 | 0.4.4.2.             | Ring Buffer Initialization                                   |     |

|     |        |                    | 0.4.4.3.             | <b>J</b>                                                     |     |

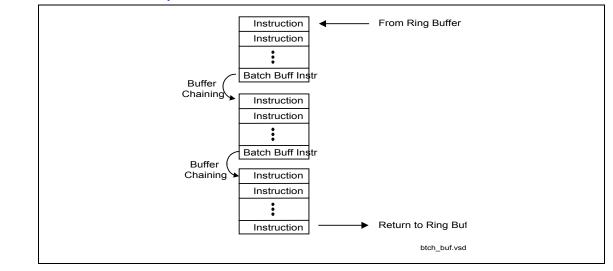

|     |        | 10.4.5.            |                      | Buffers                                                      |     |

|     |        | 10.4.6.            |                      | tion Arbitration                                             |     |

|     |        |                    | 0.4.6.1.             |                                                              |     |

|     |        |                    | 0.4.6.2.             | Wait Instructions                                            |     |

|     |        |                    | 0.4.6.3.             | Instruction Arbitration Points                               | -   |

|     |        |                    | ).4.6.4.<br>).4.6.5. | Instruction Arbitration Rules<br>Batch Buffer Protected Mode |     |

|     | 10.5.  |                    |                      | t                                                            |     |

|     | 10.5.  |                    |                      | tion Parser Instructions                                     |     |

|     |        | 10.5.1.<br>10.5.2. |                      | tructions                                                    |     |

|     |        | 10.5.2.            |                      | tructions                                                    |     |

|     |        |                    |                      | ions                                                         |     |

| 11. |        |                    |                      |                                                              |     |

|     | 11.1.  |                    |                      |                                                              |     |

|     | 11.2.  |                    |                      | ptions                                                       |     |

|     |        | 11.2.1.            |                      | MDPARSER_NOP_IDENTIFICATION                                  |     |

|     |        | 11.2.2.            | GFXC                 | MDPARSER_BREAKPOINT_INTERRUPT                                |     |

|     |        | 11.2.3.            |                      | MDPARSER_USER_INTERRUPT                                      |     |

|     |        | 11.2.4.            |                      | MDPARSER_WAIT_FOR_EVENT                                      |     |

|     |        | 11.2.5.            |                      | MDPARSER_FLUSH                                               |     |

|     |        | 11.2.6.            |                      | MDPARSER_CONTEXT_SEL                                         |     |

|     |        | 11.2.7.<br>11.2.8. | GEXC                 | MDPARSER _DEST_BUFFER_INFO<br>MDPARSER _FRONT_BUFFER_INFO    |     |

|     |        | 11.2.9.            |                      | MDPARSER _ FRONT_BOFFER_INFO                                 |     |

|     |        | 11.2.10.           |                      | MDPARSER _2_BOTT ER_INTO                                     |     |

|     |        | 11.2.11.           |                      | MDPARSER_ARB_ON_OFF                                          |     |

|     |        | 11.2.12.           | GFXC                 | MDPARSER_OVERLAY_FLIP                                        |     |

|     |        | 11.2.13.           | GFXC                 | MDPARSER LOAD SCAN LINES INCL                                |     |

|     |        | 11.2.14.           |                      | MDPARSER LOAD SCAN LINES EXCL                                |     |

|     |        | 11.2.15.           |                      | MDPARSER STORE DWORD IMM                                     |     |

|     |        | 11.2.16.           |                      | MDPARSER_STORE_DWORD_INDEX                                   |     |

|     |        | 11.2.17.           | GFXC                 | MDPARSER_BATCH_BUFFER                                        |     |

| 12. | 2D Ins | structions         |                      |                                                              |     |

|     | 12.1.  | BLTs To a          | and Fron             | n Cacheable Memory                                           |     |

|     | 12.2.  |                    |                      | ictions                                                      |     |

|     |        | 12.2.1.            |                      | P BLT                                                        |     |

|     |        | 12.2.2.            |                      | P_MONO_PATTERN_SL_BLT                                        |     |

|     |        | 12.2.3.            | PIXEL                | BLT                                                          |     |

|     |        | 12.2.4.            |                      | LINE_BLT                                                     |     |

|     |        | 12.2.5.            | TEXT_                | _BLT                                                         |     |

13.

|       | 12.2.6.     | TEXT_Immediate_BLT                                            | 169 |

|-------|-------------|---------------------------------------------------------------|-----|

|       | 12.2.7.     | COLOR_BLT                                                     |     |

|       | 12.2.8.     | PAT_BLT                                                       | 171 |

|       | 12.2.9.     | MONO_PAT_BLT                                                  | 172 |

|       | 12.2.10.    | SRC_COPY_BLT                                                  | 173 |

|       | 12.2.11.    | MONO_SRC_COPY_BLT                                             |     |

|       | 12.2.12.    | MONO_SRC_COPY_IMMEDIATE_BLT                                   | 175 |

|       | 12.2.13.    | FULL_BLT                                                      | 177 |

|       | 12.2.14.    | FULL_MONO_SRC_BLT                                             | 178 |

|       | 12.2.15.    | FULL_MONO_PATTERN_BLT                                         |     |

|       | 12.2.16.    | FULL_MONO_PATTERN_MONO_SRC_BLT                                | 182 |

| 12.3. | BLT Engi    | ne Instruction Definitions                                    | 184 |

|       | 12.3.1.     | BR00—BLT Opcode and Control                                   |     |

|       | 12.3.2.     | BR01—Setup BLT Raster OP, Control, and Destination Offset     | 186 |

|       | 12.3.3.     | BR02—Clip Rectangle Y1 Address                                |     |

|       | 12.3.4.     | BR03—Clip Rectangle Y2 Address                                | 188 |

|       | 12.3.5.     | BR04—Clip Rectangle X1 and X2                                 | 189 |

|       | 12.3.6.     | BR05—Setup Expansion Background Color                         | 190 |

|       | 12.3.7.     | BR06—Setup Expansion Foreground Color                         | 190 |

|       | 12.3.8.     | BR07—Setup Color Pattern Address                              |     |

|       | 12.3.9.     | BR08—Destination X1 and X2                                    | 192 |

|       | 12.3.10.    | BR09—Destination Address and Destination Y1 Address           | 193 |

|       | 12.3.11.    | BR10—Destination Y2 Address                                   | 193 |

|       | 12.3.12.    | BR11—BLT Source Pitch (Offset) or Monochrome Source Quadwords | 194 |

|       | 12.3.13.    | BR12—Source Address                                           | 195 |

|       | 12.3.14.    | BR13—BLT Raster OP, Control, and Destination Pitch            | 196 |

|       | 12.3.15.    | BR14—Destination Width & Height                               | 198 |

|       | 12.3.16.    | BR15—Color Pattern Address                                    |     |

|       | 12.3.17.    | BR16—Pattern Expansion Background & Solid Pattern Color       | 200 |

|       | 12.3.18.    | BR17—Pattern Expansion Foreground Color                       |     |

|       | 12.3.19.    | BR18—Source Expansion Background, and Destination Color       |     |

|       | 12.3.20.    | BR19—Source Expansion Foreground Color                        |     |

|       | 12.3.21.    | S_SLADD—Source Scan Line Address                              |     |

|       | 12.3.22.    | D_SLH—Destination Scan Line Height                            |     |

|       | 12.3.23.    | D_SLRADD—Destination Scan Line Read Address                   | 203 |

| Rende | rina Enaine | Instructions                                                  | 205 |

|       |             |                                                               |     |

| 13.1. |             |                                                               |     |

|       | 13.1.1.     | Axis Aligned Rectangles                                       |     |

|       | 13.1.2.     | Primitive Winding Order                                       |     |

|       | 13.1.3.     | Position Mask                                                 |     |

|       | 13.1.4.     | Bias                                                          |     |

|       | 13.1.5.     | Primitive Rendering Instruction Format                        |     |

|       | 13.1.6.     | Variable Length Vertex Formats for Rendering Instructions     |     |

|       | 13.1.7.     | GFXVERTEX                                                     |     |

| 13.2. |             | DERSTATE_VERTEX_FORMAT                                        |     |

| 13.3. | GFXBLO      | CK                                                            |     |

|       | 13.3.1.     | Motion Vector Format                                          | 213 |

| 13.4. | Non-pipel   | ined State Variables                                          | 213 |

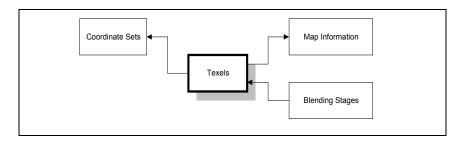

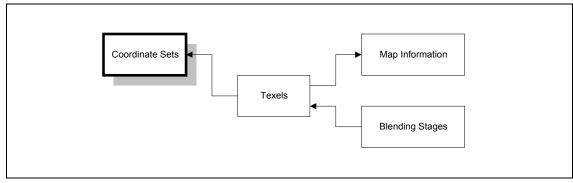

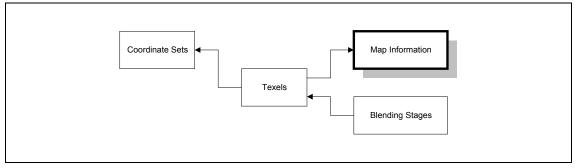

| 13.5. | GFXREN      | DERSTATE_MAP_TEXELS                                           | 214 |

| 13.6. |             | DERSTATE_MAP_COORD_SETS                                       |     |

| 13.7. |             | DERSTATE_MAP_INFO                                             |     |

| 13.8. |             | DERSTATE MAP FILTER                                           |     |

| 10.0. |             |                                                               | 222 |

| 13.9.   | GFXRENDERSTATE_MAP_LOD_LIMITS                                                                                  | 224 |

|---------|----------------------------------------------------------------------------------------------------------------|-----|

| 13.10.  | GFXRENDERSTATE_MAP_LOD_CONTROL                                                                                 |     |

| 3.11.   | GFXRENDERSTATE_MAP_PALETTE_LOAD                                                                                |     |

|         | GFXRENDERSTATE_MAP_COLOR_BLEND_STAGES                                                                          |     |

|         | GFXRENDERSTATE_MAP_ALPHA_BLEND_STAGES                                                                          |     |

|         | GFXRENDERSTATE_COLOR_FACTOR                                                                                    |     |

|         | GFXRENDERSTATE COLOR CHROMA KEY                                                                                |     |

|         | GFXRENDERSTATE_SRC_DST_BLEND_MONO                                                                              |     |

|         | GFXRENDERSTATE_Z_BIAS_ALPHA_FUNC_REF                                                                           |     |

|         | GFXRENDERSTATE_LINE_WIDTH_CULL_SHADE_MODE                                                                      |     |

|         | GFXRENDERSTATE_BOOLEAN_ENA_1                                                                                   |     |

|         | GFXRENDERSTATE_BOOLEAN_ENA_2                                                                                   |     |

|         | GFXRENDERSTATE_FOG_COLOR                                                                                       |     |

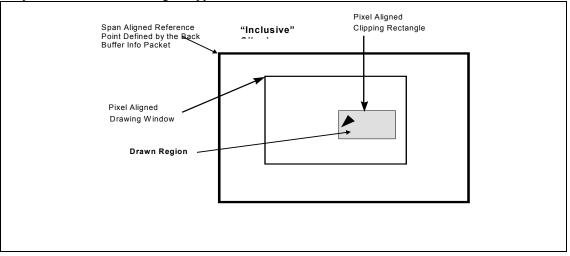

|         | GFXRENDERSTATE_DRAWING_RECTANGLE_INFO                                                                          |     |

|         | GFXRENDERSTATE_DRAWING_RECTANGLE_INFO                                                                          |     |

|         | GFXRENDERSTATE_SCISSOR_ENABLE                                                                                  |     |

|         |                                                                                                                |     |

|         | Stipple Pattern<br>GFXRENDERSTATE_ANTI_ALIASING                                                                |     |

|         |                                                                                                                |     |

|         | GFXRENDERSTATE_PROVOKING_VTX_PIXELIZATION_RULE                                                                 |     |

|         | GFXRENDERSTATE_DEST_BUFFER_VARIABLES                                                                           |     |

|         | Programming Hints/Rules                                                                                        |     |

| Clock ( | Control Registers                                                                                              | 257 |

| 14.1.   | Programming Notes                                                                                              | 257 |

| 14.2.   | DCLK_0D—Display Clock 0 Divisor Register                                                                       |     |

| 14.3.   | DCLK_1D—Display Clock 1 Divisor Register                                                                       |     |

| 4.4.    | DCLK_2D—Display Clock 2 Divisor Register                                                                       |     |

| 4.5.    | LCD_CLKD—LCD Clock Divisor Register                                                                            |     |

| 4.6.    | DCLK_0DS—Display & LCD Clock Divisor Select Register                                                           |     |

| 14.7.   | PWR_CLKC—Power Management and Miscellaneous Clock Control                                                      |     |

|         |                                                                                                                |     |

| -       | y Registers                                                                                                    |     |

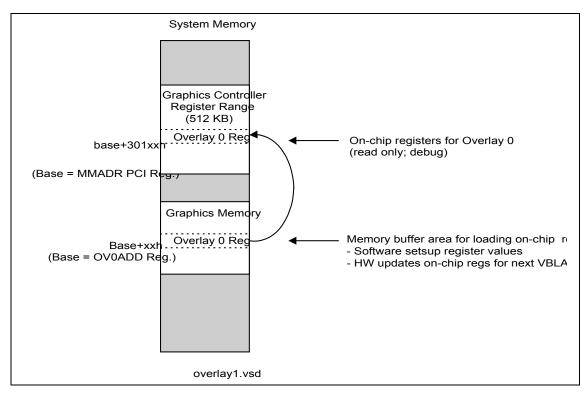

| 15.1.   | OV0ADD—Overlay 0 Register Update Address Register                                                              |     |

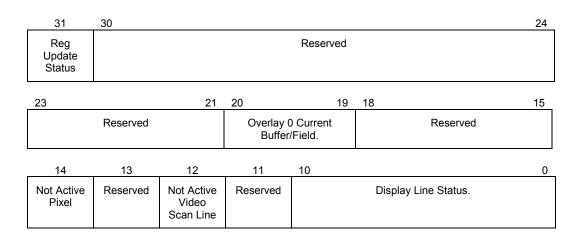

| 15.2.   | DOV0STA—Display/Overlay 0 Status Register                                                                      |     |

| 15.3.   | Gamma Correction                                                                                               |     |

|         | 15.3.1.1. GAMC[5:0]—Gamma Correction Registers                                                                 |     |

|         | 15.3.1.2. Mathematical Gamma Correction For Overlay                                                            |     |

| 5.4.    | Memory Offset Registers                                                                                        |     |

|         | 15.4.1. Overlay Buffer Pointer Registers                                                                       |     |

|         | 15.4.1.1. OBUF_0Y—Overlay Buffer 0 Y Pointer Register<br>15.4.1.2. OBUF_1Y—Overlay Buffer 1 Y Pointer Register |     |

|         | 15.4.1.3. OBUF_11—Overlay Buffer 0 U Pointer Register                                                          |     |

|         | 15.4.1.4. OBUF_0V—Overlay Buffer 0 V Pointer Register                                                          |     |

|         | 15.4.1.5. OBUF_1U—Overlay Buffer 1 U Pointer Register                                                          |     |

|         | 15.4.1.6. OBUF_1V—Overlay Buffer 1 V Pointer Register                                                          | 277 |

|         | 15.4.2. Overlay Stride Registers                                                                               |     |

|         | 15.4.2.1. OV0STRIDE—Overlay 0 Stride Register                                                                  |     |

|         | 15.4.3. Overlay Initial Phase Registers                                                                        |     |

|         | 15.4.3.1. YRGB_VPH—Y/RGB Vertical Phase Register<br>15.4.3.2. UV_VPH—UV Vertical Phase Register                |     |

|         |                                                                                                                |     |

14.

16.

|         |           | 15.4.2.2 HORZ DH. Harizantal Dhaga Degistar                    | 270 |

|---------|-----------|----------------------------------------------------------------|-----|

|         |           | 15.4.3.3. HORZ_PH—Horizontal Phase Register                    |     |

|         |           | 15.4.3.4. INIT_PH—Initial Phase Register                       |     |

|         | 15.4.4.   |                                                                |     |

|         |           | 15.4.4.1. DWINPOS—Destination Window Position Register         |     |

|         |           | 15.4.4.2. DWINSZ—Destination Window Size Register              |     |

|         | 15.4.5.   |                                                                |     |

|         |           | 15.4.5.1. SWID—Source Width Register                           | 282 |

|         |           | 15.4.5.2. SWIDQW—Source Width In QWords Register               | 283 |

|         |           | 15.4.5.3. SHEIGHT—Source Height Register                       | 284 |

|         | 15.4.6.   | 5 5                                                            |     |

|         |           | 15.4.6.1. YRGBSCALE—Y/RGB Scale Factor Register                | 285 |

|         |           | 15.4.6.2. UVSCALE—UV Scale Factor Register                     |     |

|         | 15.4.7.   |                                                                |     |

|         |           | 15.4.7.1. OV0CLRC0—Overlay 0 Color Correction 0 Register       |     |

|         |           |                                                                |     |

|         |           | 15.4.7.2. OV0CLRC1—Overlay 0 Color Correction 1 Register       |     |

|         | 15.4.8.   | , , , , , , , , , , , , , , , , , , , ,                        |     |

|         |           | 15.4.8.1. DCLRKV—Destination Color Key Value Register          |     |

|         |           | 15.4.8.2. DCLRKM—Destination Color Key Mask Register           |     |

|         | 15.4.9.   | , , , , , , , , , , , , , , , , , , , ,                        |     |

|         |           | 15.4.9.1. SCLRKVH—Source Color Key Value High Register         |     |

|         |           | 15.4.9.2. SCLRKVL—Source Color Key Value Low Register          | 291 |

|         |           | 15.4.9.3. SCLRKM—Source Color Key Mask Register                | 291 |

|         | 15.4.10.  |                                                                |     |

|         |           | 15.4.10.1. OV0CONF—Overlay Configuration Register              |     |

|         | 15.4.11.  |                                                                |     |

|         |           | Overlay Alpha Blend Window Position/Size Registers             |     |

|         |           | 15.4.12.1. AWINPOS—Alpha Blend Window Position Register        |     |

|         |           | 15.4.12.2. AWINSZ—Alpha Blend Window Size Register             |     |

| 455     |           |                                                                |     |

| 15.5.   | Overlay   | Flip Instruction                                               |     |

| Instruc | tion Mer  | nory, and Interrupt Control Registers                          | 301 |

|         |           |                                                                |     |

| 16.1.   | Instructi | on Control Registers                                           |     |

|         | 16.1.1.   | FENCE—Graphics Memory Fence Table Registers                    | 301 |

|         | 16.1.2.   | PGTBL_CTL—Page Table Control Register                          |     |

|         | 16.1.3.   | PGTBL ER—Page Table Error Register                             |     |

|         | 16.1.4.   | PGTBL_ERRMSK—Page Table Error Mask Register                    |     |

|         | 16.1.5.   | RINGBUF—Ring Buffer Registers                                  |     |

|         | 16.1.6.   | HWS_PGA—Hardware Status Page Address Register                  |     |

|         | 16.1.7.   | IPEIR—Instruction Parser Error Identification Register (debug) |     |

|         | 16.1.8.   | IPEHR—Instruction Parser Error Header Register (debug)         |     |

|         |           |                                                                |     |

|         | 16.1.9.   | INSTDONE—Instruction Stream Interface Done Register            |     |

|         | 16.1.10.  |                                                                |     |

|         | 16.1.11.  |                                                                |     |

|         | 16.1.12.  |                                                                |     |

|         | 16.1.13.  |                                                                |     |

|         | 16.1.14.  | ABB_STR—Active Batch Buffer Start Address Register (debug)     | 317 |

|         | 16.1.15.  | ABB_END—Active Batch Buffer End Address Register (debug)       | 318 |

|         | 16.1.16.  |                                                                |     |

|         | 16.1.17.  | _ 0                                                            |     |

| 16.2.   |           | t Control Registers                                            |     |

| 10.2.   | 16.2.1.   | HWSTAM—Hardware Status Mask Register                           |     |

|         |           |                                                                |     |

|         | 16.2.2.   | IER—Interrupt Enable Register                                  |     |

|         | 16.2.3.   | IIR—Interrupt Identity Register                                |     |

|         | 16.2.4.   | IMR—Interrupt Mask Register                                    | 325 |

|     |         | 16.2.5. ISR—Interrupt Status Register                                             |     |

|-----|---------|-----------------------------------------------------------------------------------|-----|

|     |         | 16.2.6. Error Identity, Mask and Status Registers                                 |     |

|     |         | 16.2.6.1. Page Table Error handling in Intel <sup>®</sup> 815 Chipset             |     |

|     |         | 16.2.6.2. Resetting the Page Table Error<br>16.2.6.3. EIR—Error Identity Register |     |

|     |         | 16.2.6.4. EMR—Error Mask Register                                                 |     |

|     |         | 16.2.6.5. ESR—Error Status Register                                               |     |

|     | 16.3.   | Display Interface Control                                                         |     |

|     | 10.01   | 16.3.1. FW_BLC—FIFO Watermark and Burst Length Control                            |     |

| 17. | LCD /   | TV-Out Register Description                                                       |     |

|     | 17.1.   | HTOTAL—Horizontal Total Register                                                  |     |

|     | 17.2.   | HBLANK—Horizontal Blank Register                                                  |     |

|     | 17.3.   | HSYNC—Horizontal Sync Register                                                    |     |

|     | 17.4.   | VTOTAL—Vertical Total Register                                                    |     |

|     | 17.5.   | VBLANK—Vertical Blank Register                                                    |     |

|     | 17.6.   | VSYNC—Vertical Sync Register                                                      |     |

|     | 17.7.   | LCDTV_C—LCD/TV-Out Control Register                                               |     |

|     | 17.8.   | OVRACT—Overlay Active Register                                                    |     |

|     | 17.9.   | BCLRPAT— Border Color Pattern Register                                            |     |

| 18. | Local I | Memory Interface                                                                  |     |

|     | 18.1.   | DRT—DRAM Row Type                                                                 | 343 |

|     | 18.2.   | DRAMCL—DRAM Control Low                                                           |     |

|     | 18.3.   | DRAMCH—DRAM Control High                                                          |     |

| 19. | I/O Co  | ontrol Registers                                                                  |     |

|     | 19.1.   | HVSYNC—HSYNC/VSYNC Control Register                                               |     |

|     | 19.2.   | GPIO Registers                                                                    |     |

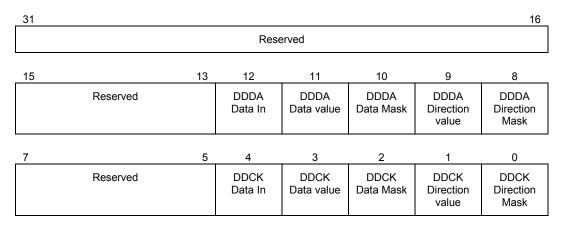

|     | 10.2.   | 19.2.1. GPIOA—General Purpose I/O Control Register A                              |     |

|     |         | 19.2.2. GPIOB—General Purpose I/O Control Register B                              |     |

| 20. | Displa  | y And Cursor Registers                                                            |     |

|     | 20.1.   | DISP_SL—Display Scan Line Count                                                   |     |

|     | 20.1.   | DISP SLC—Display Scan Line Count Range Compare                                    |     |

|     | 20.2.   | Pixel Pipeline Control                                                            |     |

|     | 20.3.   | 20.3.1. PIXCONF—Pixel Pipeline Configuration                                      |     |

|     |         | 20.3.2. BLTCNTL—BLT Control                                                       |     |

|     |         | 20.3.3. SWF[1:3]—Software Flag Registers                                          |     |

|     |         | 20.3.4. DPLYBASE—Display Base Address Register                                    |     |

|     |         | 20.3.5. DPLYSTAS—Display Status Select Register                                   |     |

|     | 20.4.   | Hardware Cursor                                                                   |     |

|     |         | 20.4.1. CURCNTR—Cursor Control Register                                           |     |

|     |         | 20.4.2. CURBASE—Cursor Base Address Register                                      |     |

|     |         | 20.4.3. CURPOS—Cursor Position Register                                           |     |

| 21. | Appen   | idix A: Mode Parameters                                                           |     |

### **Figures**

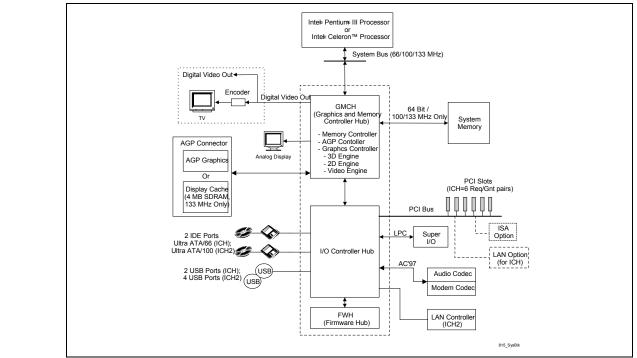

| Figure 1.   | Intel <sup>®</sup> 815 Chipset System Block Diagram                        | . 18 |

|-------------|----------------------------------------------------------------------------|------|

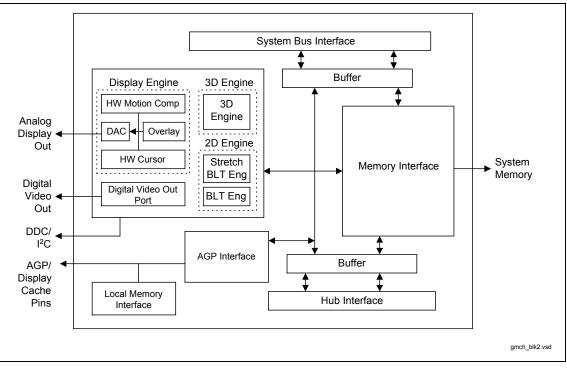

| Figure 2.   | Intel <sup>®</sup> 82815 Chipset GMCH Block Diagram                        | . 19 |

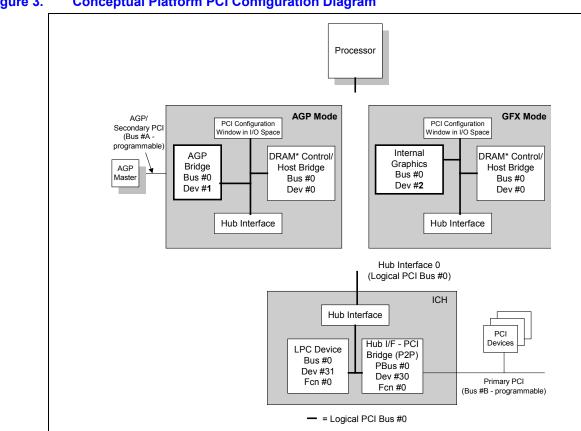

| Figure 3.   | Conceptual Platform PCI Configuration Diagram                              |      |

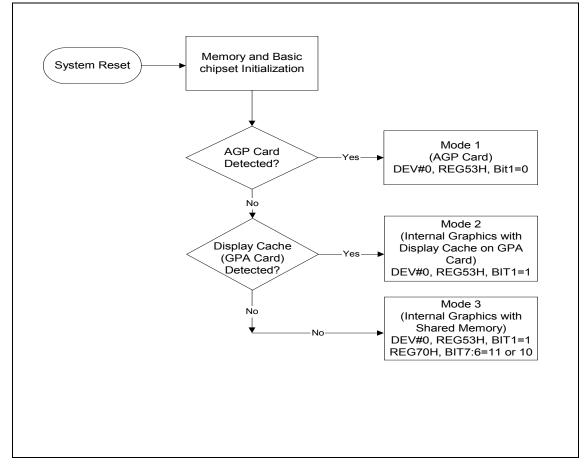

| Figure 4.   | Device Mode Auto-Detect Flowchart                                          |      |

| Figure 5.   | System Memory Address Map                                                  |      |

| Figure 6.   | Detailed Memory System Address Map                                         |      |

| Figure 7.   | Graphics Controller Register Memory and I/O Map                            |      |

| Figure 8.   | GTT Mapping                                                                |      |

| Figure 9.   | Source Corruption in BLT with Overlapping Source and Destination Locations |      |

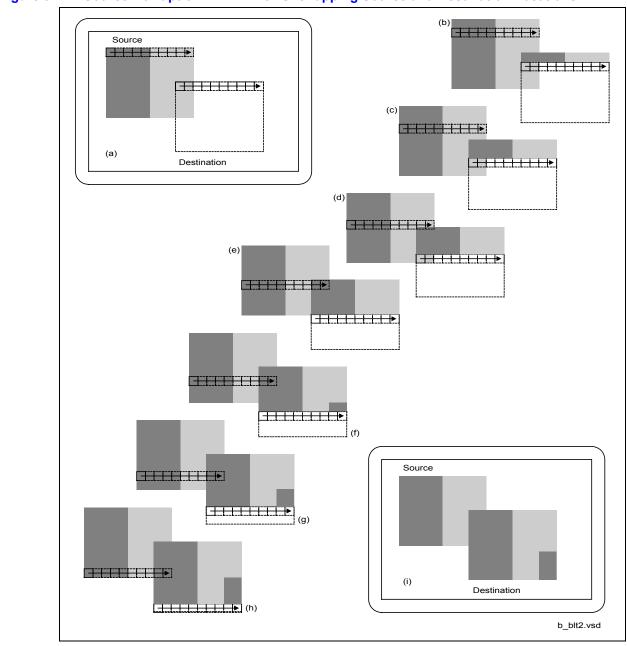

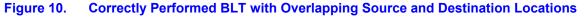

| Figure 10.  | Correctly Performed BLT with Overlapping Source and Destination Locations  |      |

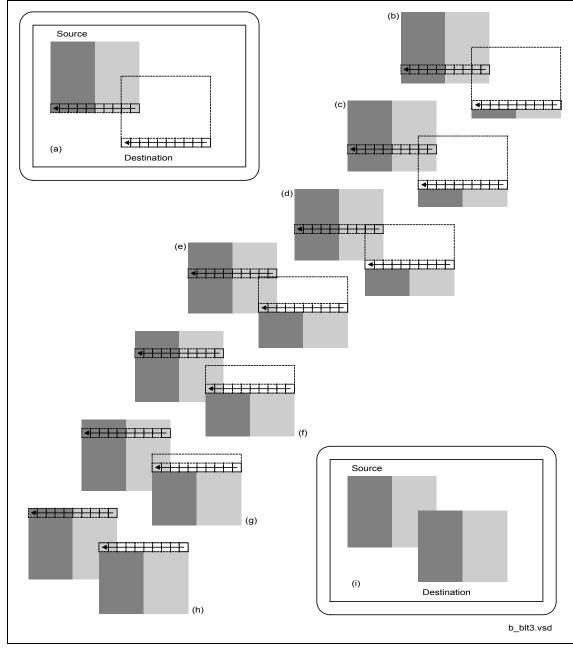

| Figure 11.  | Suggested Starting Points for Possible Source & Destination Overlap        |      |

| riguio i i. | Situations                                                                 | . 56 |

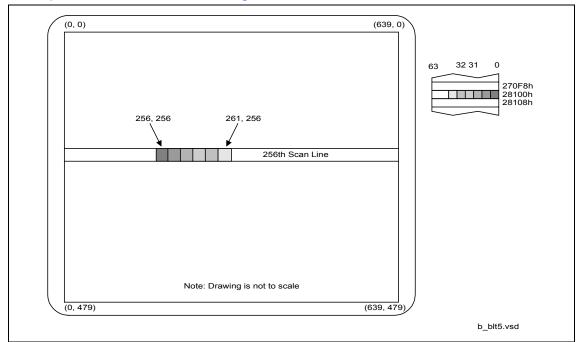

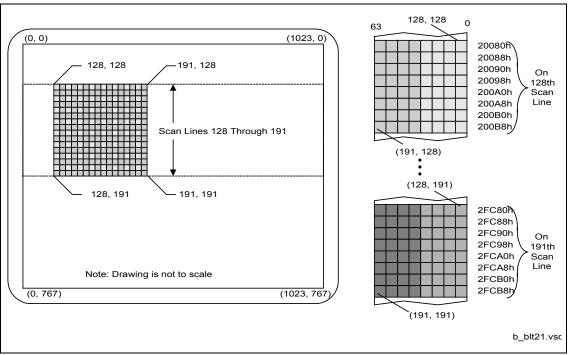

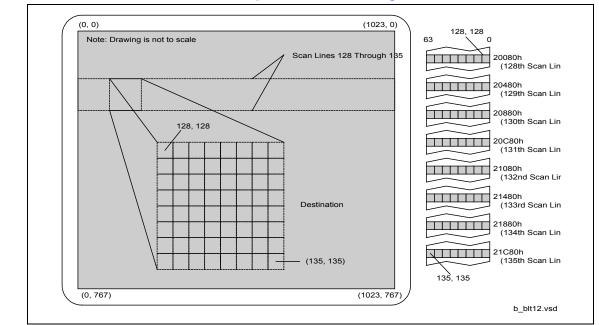

| Figure 12.  | Representation of On-Screen Single 6-Pixel Line in the Frame Buffer        |      |

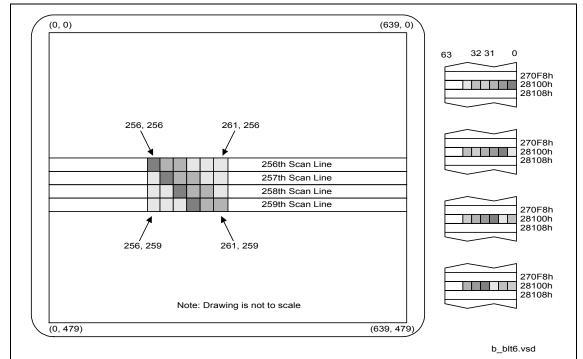

| Figure 13.  | Representation of On-Screen 6x4 Array of Pixels in the Frame Buffer        |      |

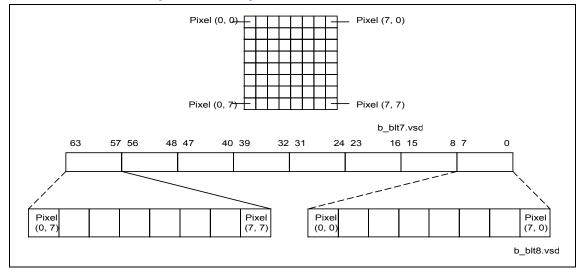

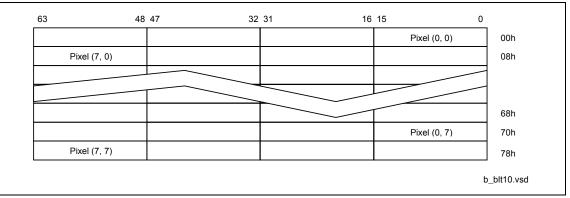

| Figure 14.  | Pattern Data Always an 8x8 Array of Pixels                                 |      |

| Figure 15.  | 8bpp Pattern Data Occupies 64 Bytes (8 quadwords)                          |      |

| Figure 16.  | 16bpp Pattern Data Occupies 128 Bytes (16 quadwords)                       | . 61 |

| Figure 17.  | 24bpp Pattern Data Occupies 256 Bytes (32 quadwords)                       |      |

| Figure 18.  | 2bpp Pattern Data Occupies 256 Bytes (32 quadwords)                        |      |

| Figure 19.  | On-Screen Destination for Example Pattern Fill BLT                         |      |

| Figure 20.  | Pattern Data for Example Pattern Fill BLT                                  |      |

| Figure 21.  | Results of Example Pattern Fill BLT                                        |      |

| Figure 22.  | On-Screen Destination for Example Character Drawing BLT                    | . 66 |

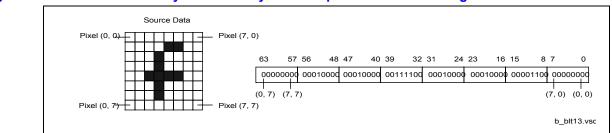

| Figure 23.  | Source Data in System Memory for Example Character Drawing BLT             | . 66 |

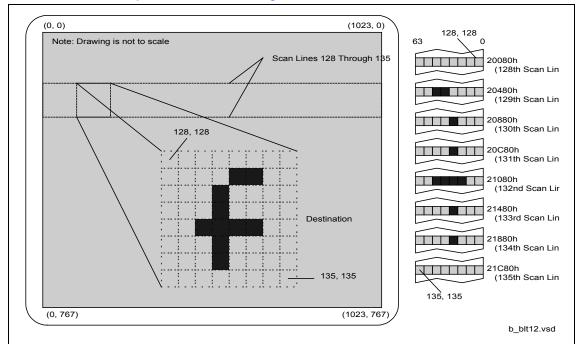

| Figure 24.  | Results of Example Character Drawing BLT                                   | . 68 |

| Figure 25   | Display Fields and Dimensions CRxx Control Registers                       | 110  |

| Figure 26.  | Graphics Controller Instruction Interface                                  |      |

| Figure 27.  | Ring Buffers                                                               | 144  |

| Figure 28.  | Batch Buffer Sequence                                                      |      |

| Figure 29.  | Instruction Format For First DWord                                         |      |

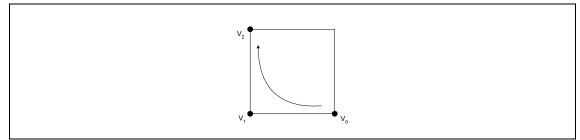

| Figure 30.  | Rectangle Vertices                                                         |      |

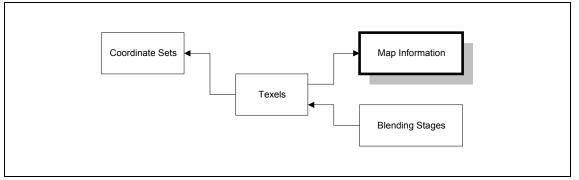

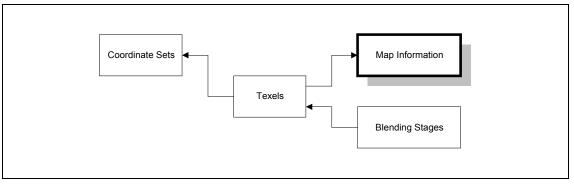

| Figure 31.  | State Variable Relationships                                               | 214  |

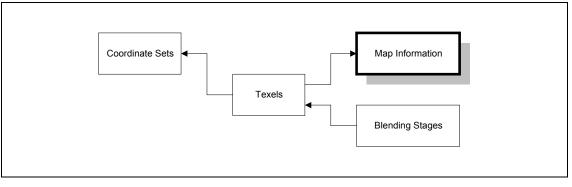

| Figure 32.  | State Variable Relationships                                               | 215  |

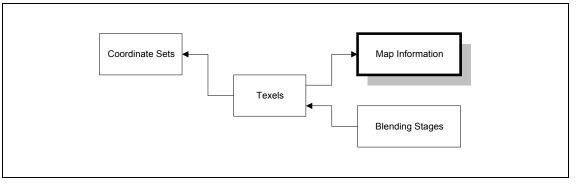

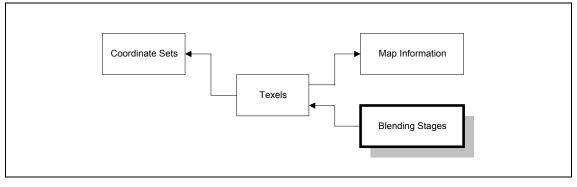

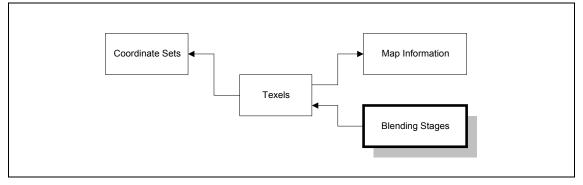

| Figure 33.  | State Variable Relationships                                               | 217  |

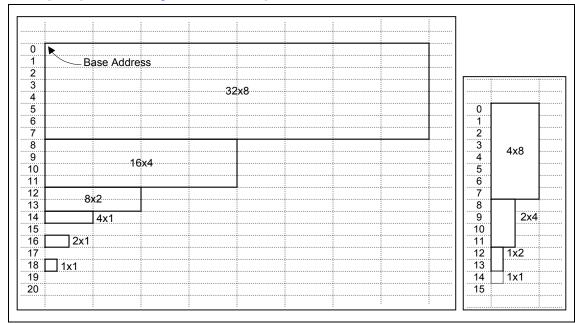

| Figure 34   | Mip-map Surface Organization Example                                       | 218  |

| Figure 35.  | State Variable Relationships                                               | 222  |

| Figure 36.  | State Variable Relationships                                               | 224  |

| Figure 37.  | State Variable Relationships                                               | 225  |

| Figure 38.  | State Variable Relationships                                               | 226  |

| Figure 39.  | State Variable Relationships                                               |      |

| Figure 40.  | State Variable Relationships                                               |      |

| Figure 41.  | Gamma Correction Unit Block Diagram                                        | 271  |

#### **Tables**

| Table 1.  | Supported System Dup and System Mamony Dup Fraguencias                 | 22  |

|-----------|------------------------------------------------------------------------|-----|

|           | Supported System Bus and System Memory Bus Frequencies                 |     |

| Table 2.  | Memory-Mapped Registers                                                | 32  |

| Table 3.  | I/O and Memory Register Map                                            | 37  |

| Table 4.  | 2D Sequence Registers (3C4h / 3C5h)                                    | 38  |

| Table 5.  | 2D Graphics Controller Registers (3CEh / 3CFh)                         | 38  |

| Table 6.  | 2D Attribute Controller Registers (3C0h / 3C1h)                        |     |

| Table 7.  | 2D CRT Controller Registers (3B4h / 3D4h / 3B5h / 3D5h)                |     |

| Table 8.  | CRT Display Sync Polarities                                            | 84  |

| Table 9.  | VGA Address Range                                                      |     |

| Table 10. | Memory Address Counter Address Bits [15:0]                             |     |

| Table 11. | Frame Buffer Address Decoder                                           |     |

| Table 12. | Ring Buffer Characteristics                                            |     |

| Table 13. | Graphics Controller Instructions                                       | 151 |

| Table 14. | Summary of Source Surface Formats with Filter Output Channel Mappings. | 217 |

| Table 15. | Selecting Specular Mode                                                | 235 |

| Table 16. | Overlay Register/Instruction Categories                                | 266 |

| Table 17. | Bit Definition For Interrupt Control Registers                         |     |

|           |                                                                        |     |

### **Revision History**

| Rev. | Description               | Date |

|------|---------------------------|------|

| 1.0  | Initial Release July 2000 |      |

This page is intentionally left blank.

### intel

### 1. Introduction

The Intel<sup>®</sup> 815 chipset is a highly flexible chipset designed to extend from the basic graphics/multimedia PC platform up to the mainstream performance desktop platform. The chipset consists of an Intel<sup>®</sup> 82815 chipset Graphics and Memory Controller Hub (GMCH), an I/O Controller Hub (ICH) for the I/O subsystem, and a Firmware\* Hub (FWH). For this chipset, the graphics capability resides in the Graphics and Memory Controller Hub (GMCH) chip.

The GMCH's Graphics Controller (GC) contains an extensive set of registers and instructions for configuration, 2D, 3D, and Video systems. This document describes the Intel<sup>®</sup> 815 chipset registers/instructions and provides detailed bit/field descriptions.

This Programmer's Reference Manual (PRM) is intended for hardware, software, and Firmware\* designers who seek to implement or utilize the graphic functions of the Intel<sup>®</sup> 815 chipset. Familiarity with 2D and 3D graphics programming is assumed.

#### 1.1. Terminology

| Term                          | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGP Mode                      | The GMCH is using its capability to interface with and AGP card. The internal graphics controller is disabled in this mode.                                                                                                                                                                                                                                                                       |

| GPA Card                      | Graphics Performance Accelerator Card. This is a new implementation which<br>allows local memory devices to be placed on a card that plugs into the AGP slot.<br>When an AGP card is not present, an GPA card can be added to improve<br>performance by acting as a display cache, for the Z-buffer only, of up to 4 MB.<br>The GPA card was previously known as the AIMM (Add-In Memory Module). |

| CSI                           | Command Stream Interface (same as instruction stream interface)                                                                                                                                                                                                                                                                                                                                   |

| GC                            | Graphics Controller                                                                                                                                                                                                                                                                                                                                                                               |

| GFX Mode                      | The GMCH is using its internal graphics capability. This means that the ability to interface with an AGP card is disabled.                                                                                                                                                                                                                                                                        |

| GMCH                          | The Graphics and Memory Controller Hub component that contains the functionality of an MCH plus an internal graphics controller.                                                                                                                                                                                                                                                                  |

| Group 0 Protection (register) | As per the original IBM VGA specification, CRT Controller registers CR[0:7] can be write-protected via CR11[bit 7]. In BIOS code, this write protection is set following each mode change. Note that other group protection levels have no current use and are not supported by the GC. Only Group 0 Protection is supported.                                                                     |

| Instruction                   | The GC has a set of graphics instructions. In some documents the term "command" is used for instruction.                                                                                                                                                                                                                                                                                          |

| IP                            | Instruction Parser                                                                                                                                                                                                                                                                                                                                                                                |

| MBZ                           | Must Be Zero                                                                                                                                                                                                                                                                                                                                                                                      |

| Term            | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCH             | The Memory Controller Hub component that contains the processor interface,<br>DRAM controller, and AGP interface. The MCH communicates with the ICH over<br>a proprietary interconnect called the hub interface (previously known as<br>HubLink). The MCH was called the North Bridge (NB) in previous chip sets.<br>MCH will be used to refer to non-graphics portion of the GMCH. |

| MM              | Memory Mapped address space.                                                                                                                                                                                                                                                                                                                                                        |

| MMIO            | Memory Mapped I/O space.                                                                                                                                                                                                                                                                                                                                                            |

| QW              | Quad Word = 64 bits = 8 Bytes.                                                                                                                                                                                                                                                                                                                                                      |

| R/W (register)  | Read/Write. A register with this attribute can be read and written.                                                                                                                                                                                                                                                                                                                 |

| R/WC (register) | Read/Write Clear. A register bit with this attribute can be read and written.<br>However, a write of 1 clears (sets to 0) the corresponding bit and a write of 0 has<br>no effect.                                                                                                                                                                                                  |

| R/WO (register) | Read/Write Once. A register bit with this attribute can be written to only once after power up. After the first write, the bit becomes read only.                                                                                                                                                                                                                                   |

| RO (register)   | Read Only. In some cases, if a register is read only, writes to this register location have no effect. However, in other cases, two separate registers are located at the same location where a read accesses one of the registers and a write accesses the other register. See the I/O and memory map tables for details.                                                          |

| WO (register)   | Write Only. In some cases, If a register is write only, reads to this register location have no effect. However, in other cases, two separate registers are located at the same location where a read accesses one of the registers and a write accesses the other register. See the I/O and memory map tables for details.                                                         |

#### 1.2. Reference Documents

The following documents should be available for reference when using this specification:

- Intel<sup>®</sup> 815 Chipset: Intel<sup>®</sup> 82815 chipset Graphics and Memory Controller Hub (GMCH) External Design Specification (EDS)

- Intel<sup>®</sup> 82801AA (ICH) and Intel<sup>®</sup> 82801AB (ICH0) I/O Controller Hub Datasheet

- Intel<sup>®</sup> 82801BA (ICH2) I/O Controller Hub External Design Specification (EDS)

- Intel<sup>®</sup> 82802AB/82802AC Firmware\* Hub (FWH) Datasheet

### 2. Intel<sup>®</sup> 815 Chipset Overview

The chipset consists of an Intel<sup>®</sup> 82815 chipset Graphics and Memory Controller Hub (GMCH), an I/O Controller Hub (ICH) for the I/O subsystem, and a Firmware\* Hub (FWH). The GMCH integrates a system memory SDRAM controller that supports a 64-bit 100/133 MHz SDRAM array. The Intel<sup>®</sup> 815 chipset family includes:

- Intel<sup>®</sup> 815 chipset: This chipset consists of the Intel<sup>®</sup> 82815 chipset GMCH, the 82801AA ICH, and the 82802AB/82802AC FWH.

- Intel<sup>®</sup> 815E chipset: This chipset consists of the Intel<sup>®</sup> 82815 chipset GMCH, the 82801BA ICH2, and the 82802AB/82802AC FWH.

The Intel<sup>®</sup> 82815 chipset GMCH integrates a Display Cache SDRAM controller that supports a 32-bit 133 MHz SDRAM array for enhanced integrated 2D and 3D graphics performance. Multiplexed with the display cache interface is an AGP controller interface to enable graphics configuration and upgrade flexibility with the Intel<sup>®</sup> 815 chipset. The AGP interface and the internal graphics device are mutually exclusive. When the AGP port is populated with an AGP graphics card, the integrated graphics is disabled; thus, the display cache interface is not needed.

The Intel<sup>®</sup> 815 chipset family uses a hub architecture with the Intel<sup>®</sup> 82815 chipset GMCH as the host bridge hub and the I/O Controller Hub (ICH) as the I/O hub. The Intel<sup>®</sup> 815 chipset supports the 82801AA ICH and the Intel<sup>®</sup> 815E chipset supports the 82801BA ICH2. The ICH is a highly integrated multifunctional I/O Controller Hub that provides the interface to the PCI Bus and integrates many of the functions needed in today's PC platforms. The GMCH and ICH communicate over a dedicated hub interface.

#### Figure 1. Intel<sup>®</sup> 815 Chipset System Block Diagram

#### 2.1. I/O Controller Hub

The 82801AA ICH/82801BA ICH2 functions and capabilites are listed below. Unless otherwise specified, the function/capability applies to both ICH and ICH2.

- PCI Rev 2.2 compliant with support for 33 MHz PCI operations

- ICH supports up to 6 Req/Gnt pairs

- Power Management Logic Support

- Enhanced DMA Controller, Interrupt Controller & Timer Functions

- Integrated IDE controller; ICH supports Ultra ATA/66 (ICH); Ultra ATA/100/66/33 (ICH2)

- Integrated LAN Controller (ICH2 only)

- USB host interface with support for two USB ports (ICH); Four ports (ICH2)

- System Management Bus (SMBus) compatible with most I<sup>2</sup>C devices

- AC'97 2.1 Compliant Link for Audio and Telephony CODECs

- Low Pin Count (LPC) interface

- Firmware\* Hub (FWH) interface support

- Alert On LAN\*

### 2.2. Intel<sup>®</sup> 82815 Chipset GMCH Overview

Figure 2 is a block diagram of the GMCH illustrating the various interfaces and integrated functions. The functions and capabilities include:

### intel

- Support for a single processor configuration

- 64-bit AGTL+ based System Bus Interface at 66/100/133 MHz

- 32-bit Host Address Support

- 64-bit System Memory Interface with optimized support for SDRAM at 100/133 MHz

- Integrated 2D & 3D Graphics Engines

- Integrated H/W Motion Compensation Engine

- Integrated 230 MHz DAC

- Integrated Digital Video Out Port

- 133 MHz Display Cache

- AGP 1X/2X/4X Controller

#### Figure 2. Intel<sup>®</sup> 82815 Chipset GMCH Block Diagram

#### 2.2.1. Host Interface

The host interface of the GMCH is optimized to support the Intel<sup>®</sup> Pentium<sup>®</sup> III processor and Intel<sup>®</sup> Celeron<sup>TM</sup> processor in the FC-PGA package. The GMCH implements the host address, control, and data bus interfaces within a single device. The GMCH supports a 4-deep in-order queue (i.e., supports pipelining of up to 4 outstanding transaction requests on the host bus). Host bus addresses are decoded by the GMCH for accesses to system memory, PCI memory and PCI I/O (via hub interface), PCI configuration space and Graphics memory. The GMCH takes advantage of the pipelined addressing capability of the processor to improve the overall system performance.

The Intel<sup>®</sup> 82815 chipset GMCH supports the 370-pin socket processor.

• **370-pin socket** (PGA370). The PGA370 is a zero insertion force (ZIF) socket that a processor in the FC-PGA package will use to interface with a system board.

#### 2.2.2. System Memory Interface

The GMCH integrates a system memory controller that supports a 64-bit 100/133 MHz SDRAM array. The only DRAM type supported is industry standard Synchronous DRAM (SDRAM). The SDRAM controller interface is fully configurable through a set of control registers.

The GMCH supports industry standard 64-bit wide DIMMs with SDRAM devices. The thirteen multiplexed address lines, SMAA[12:0], along with the two bank select lines, SBS[1:0], allow the GMCH to support 2M, 4M, 8M, 16M, and 32M x64 DIMMs. Only asymmetric addressing is supported. The GMCH has six SCS# lines (two copies of each for electrical loading), enabling the support of up to six 64-bit rows of SDRAM. The GMCH targets SDRAM with CL2 and CL3 and supports both single and double-sided DIMMs. Additionally, the GMCH also provides a 1024 entry deep refresh queue. The GMCH can be configured to keep up to 4 pages open within the memory array. Pages can be kept open in any one bank of memory.

SCKE[5:0] are used in configurations requiring powerdown mode for the SDRAM.

#### 2.2.3. Multiplexed AGP and Display Cache Interface

The Intel<sup>®</sup> 82815 chipset GMCH multiplexes an AGP interface with a display cache interface for internal 3D graphics performance improvement. The display cache is used only in the internal graphics. When an AGP card is installed in the system, the GMCH internal graphics will be disabled and the AGP controller will be enabled.

#### **AGP Interface**

A single AGP connector is supported by the GMCH AGP interface. The AGP buffers operate in one of two selectable modes in order to support the AGP Universal Connector:

- 3.3V drive, not 5 volt safe: This mode is compliant to the AGP 1.0 and 2.0 specifications.

- 1.5V drive, not 3.3 volt safe: This mode is compliant with the AGP 2.0 specification.

The following table shows the AGP Data Rate and the Signaling Levels supported by the GMCH.

| Data Rate | Signaling Level |      |

|-----------|-----------------|------|

|           | 1.5V            | 3.3V |

| 1x AGP    | Yes             | Yes  |

| 2x AGP    | Yes             | Yes  |

| 4x AGP    | Yes             | No   |

The AGP interface supports 4x AGP signaling. AGP semantic (PIPE# or SBA[7:0]) cycles to SDRAM are not snooped on the host bus. AGP FRAME# cycles to SDRAM are snooped on the host bus. The GMCH supports PIPE# or SBA[7:0] AGP address mechanisms, but not both simultaneously. Either the PIPE# or the SBA[7:0] mechanism must be selected during system initialization. High priority accesses are supported. Only memory writes from the hub interface to AGP are allowed. No transactions from AGP to the hub interface are allowed.

#### **Display Cache Interface**

The GMCH supports a Display Cache SDRAM controller with a 32-bit 133 MHz SDRAM array. The DRAM type supported is industry standard Synchronous DRAM (SDRAM) like that of the system memory. The local memory SDRAM controller interface is fully configurable through a set of control registers.

#### 2.2.4. Hub Interface

The hub interface is a private interconnect between the GMCH and the ICH.

#### 2.2.5. Intel<sup>®</sup> 82815 Chipset GMCH Integrated Graphics Support

The GMCH includes a highly integrated graphics accelerator. Its architecture consists of dedicated multimedia engines executing in parallel to deliver high performance 3D, 2D and motion compensation video capabilities. The 3D and 2D engines are managed by a 3D/2D pipeline preprocessor allowing a sustained flow of graphics data to be rendered and displayed. The deeply pipelined 3D accelerator engine provides 3D graphics quality and performance via per-pixel 3D rendering and parallel data paths which allow each pipeline stage to simultaneously operate on different primitives or portions of the same primitive. The GMCH graphics accelerator engine supports perspective-correct texture mapping, trilinear and anisotropic Mip-Map filtering, Gouraud shading, alpha-blending, fogging and Z-buffering. A rich set of 3D instructions permit these features to be independently enabled or disabled.

For the GMCH, a Display Cache (DC) can be used for the Z-buffer (textures and display buffer(s) are located only in system memory). If the display cache is not used, the Z-buffer is located in system memory.

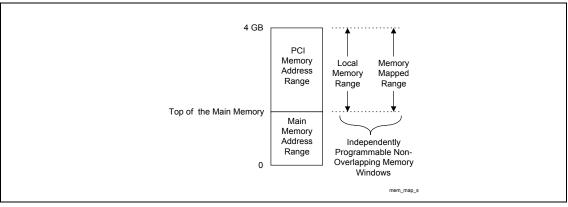

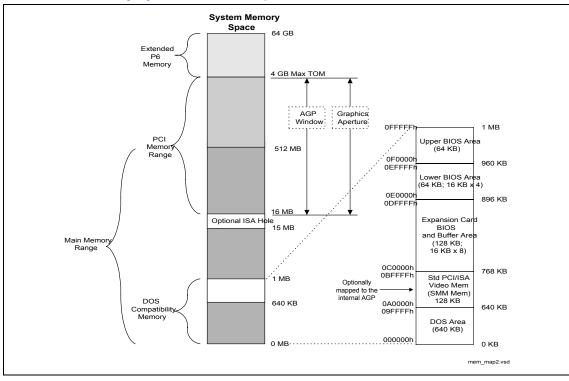

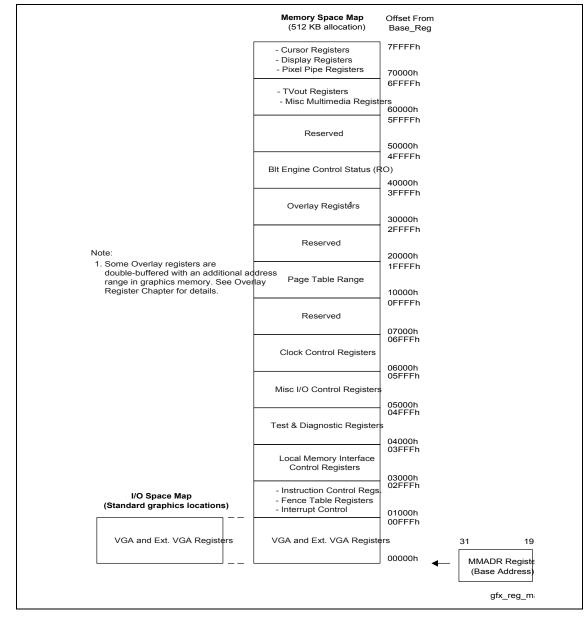

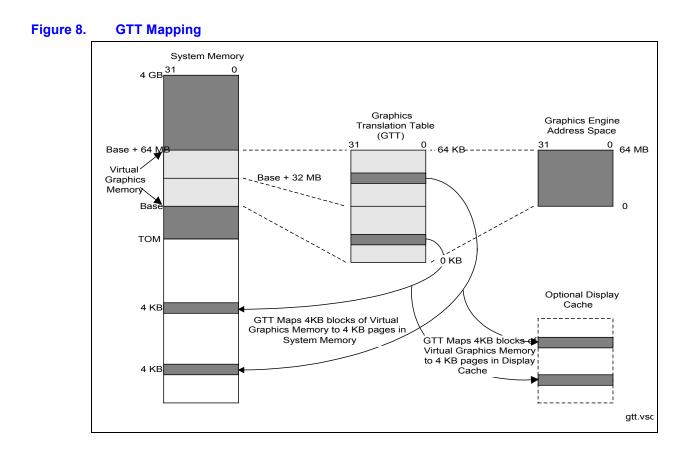

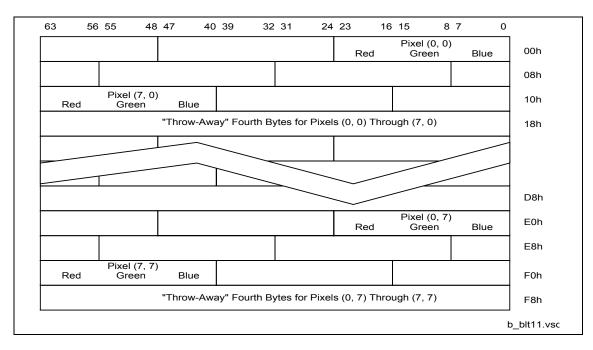

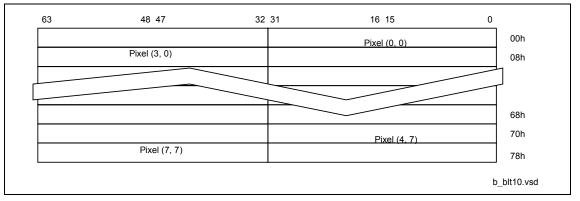

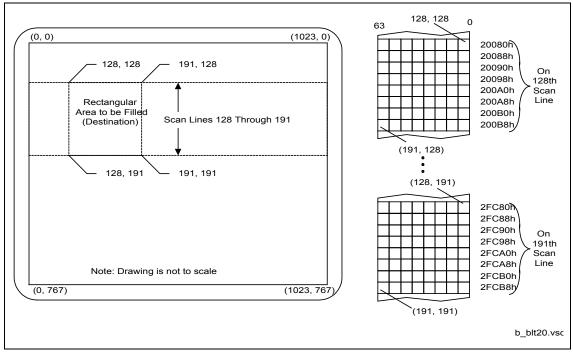

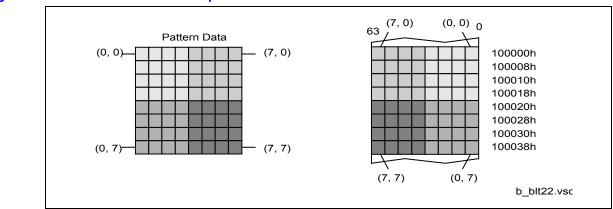

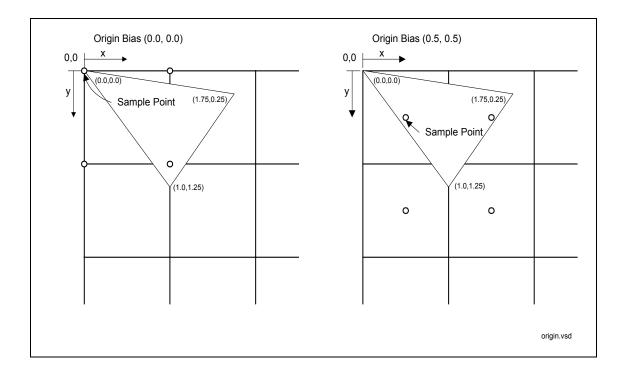

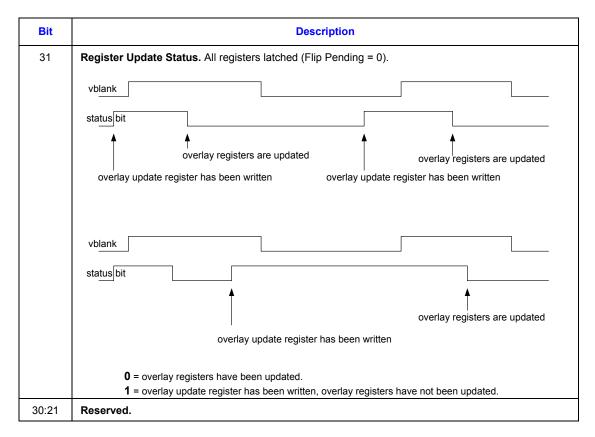

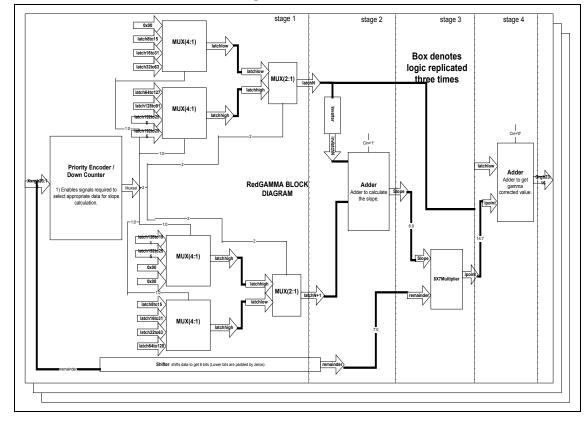

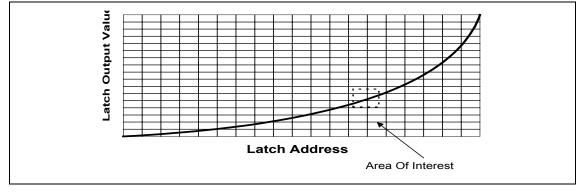

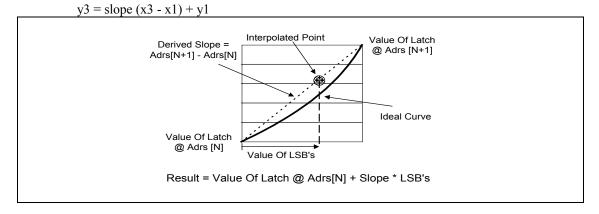

The GMCH integrated graphics accelerator's 2D capabilities include BLT and arithmetic STRBLT engines, a hardware cursor and an extensive set of 2D registers and instructions. The high performance 64-bit BitBLT engine provides hardware acceleration for many common Windows\* operations.