# 82357 INTEGRATED SYSTEM PERIPHERAL (ISP)

- Provides Enhanced DMA Functions

- ISA/EISA DMA Compatible Cycles

- All Transfers are Fly-By Transfers

- 32-Bit Addressability

- Seven Independently Programmable Channels

- Provides Timing Control for 8-, 16-, and 32-Bit DMA Data Transfers

- Provides Timing Control for Compatible, Type "A", Type "B", and Type "C" (Burst) Cycle Types

- 33 Mbytes/sec Maximum Data Transfer Rate

- Provides Refresh Address Generation

- Supports Data Communication

Devices and Other Devices That

Work from a Ring Buffer in Memory

- -- Incorporates the Functionality of Two 82C37A DMA Controllers

- Provides High Performance Arbitration

- For CPU, EISA/ISA Bus Masters, DMA Channels, and Refresh

- Incorporates the Functionality of Two 82C59A Interrupt Controllers

- 14 Independently Programmable Channels for Level-or-Edge Triggered Interrupts

- Five Programmable 16-Bit Counter/ Timers

- Generates Refresh Request Signal

- System Timer Interrupt

- Speaker Tone Output

- Fail-Safe Timer

- Periodic CPU Speed Control

- 82C54 Programmable Interval Timer Compatible

- Provides Logic for Generation/Control of Non-Maskable Interrupts

- Parity Errors for System and Expansion Board Memory

- 8 μs and 32 μs Bus Timeout

- Immediate NMI Interrupt via Software Control

- Fail-Safe Timer

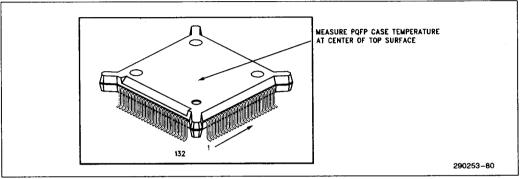

- 132-Pin PQFP Package

(See Packaging Specifications: Order Number 240800, Package Type NG)

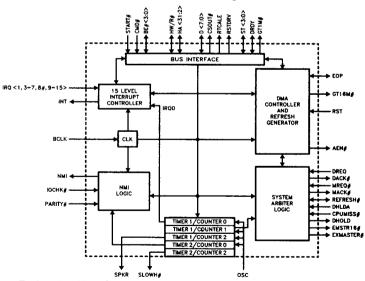

### 82357 Internal Block Diagram

386™ and i486™ are Trademarks of Intel Corporation.

October 1992 Order Number: 290253-006

290253-78

1-215

## 82357 Integrated System Peripheral (ISP)

| CON     | TENTS                                            | PAGE  |

|---------|--------------------------------------------------|-------|

| 82357   | INTEGRATED SYSTEM PERIPHERAL                     | . 0.5 |

|         | FUNCTIONAL HIGHLIGHTS                            |       |

| 1.0 ISF | SYSTEM INTERFACE ILLUSTRATION                    | 1-221 |

| 2.0 FU  | NCTIONAL OVERVIEW                                | 1-221 |

| 2.1     | Master and Slave Modes                           | 1-221 |

| 2.2     | DMA Controller                                   | 1-221 |

| 2.3     | System Arbiter                                   | 1-222 |

| 2       | 2.3.1 Priorities of Requesters                   | 1-223 |

| 2       | 2.3.2 Preemption of EISA Masters and DMA Devices | 1-223 |

| 2       | 2.3.3 Arbitration During Non-Maskable Interrupts | 1-224 |

| 2       | 2.3.4 DREQ and DACK Latency Control              | 1-224 |

| 2.4     | Refresh Generation                               | 1-224 |

| 2.5     | Interrupt Controller                             | 1-225 |

| 2.6     | Non-Maskable Interrupt (NMI)                     | 1-226 |

| 2.7     | Interval Timers                                  | 1-227 |

| 2.8     | Register Access                                  | 1-228 |

| 3.0 DN  | IA CONTROLLER                                    | 1-228 |

| 3.1     | DMA Transfer Modes                               | 1-228 |

| 3       | 3.1.1 Single Transfer Mode                       | 1-228 |

| 3       | 3.1.2 Block Transfer Mode                        | 1-229 |

| 3       | 3.1.3 Demand Transfer Mode                       | 1-229 |

| 3       | 3.1.4 Cascade Mode                               | 1-229 |

| 3.2     | Transfer Types                                   | 1-229 |

| 3       | 3.2.1 Write Transfer                             | 1-229 |

| 3       | 3.2.2 Read Transfer                              | 1-229 |

| 3       | 3.2.3 Verify Transfer                            | 1-229 |

| 3.3     | Autoinitialize                                   | 1-229 |

| 3.4     | Channel Priority                                 | 1-230 |

|         | 3.4.1 Fixed Priority                             | 1-230 |

| . 3     | 3.4.2 Rotating Priority                          | 1-230 |

| 3.5     | Buffer Chaining                                  | 1-230 |

| 3.6     | DMA Enhanced Timing                              | 1-232 |

| :       | 3.6.1 Compatible Timing                          | 1-232 |

| :       | 3.6.2 Type "A" Timing                            | 1-232 |

| ;       | 3.6.3 Type "B" Timing                            | 1-232 |

| :       | 3.6.4 Type "C" (Burst Timing)                    | 1-232 |

| • |  |

|---|--|

|   |  |

|   |  |

|   |  |

| CONTENTS                                                    | PAGE  |

|-------------------------------------------------------------|-------|

| 3.7 Register Description                                    |       |

| 3.7.1 Stop Registers (Ring Buffer Data Structure)           | 1-232 |

| 3.7.2 DMA Memory Low Page Register                          | 1-234 |

| 3.7.3 DMA Memory High Page Register                         | 1-234 |

| 3.7.3.1 Address Compatibility Mode                          | 1-235 |

| 3.7.4 Current Address Register (READ/WRITE)                 | 1-235 |

| 3.7.4.1 Address Shifting when Programmed for                |       |

| 16-Bit I/O Count By Words                                   | 1-235 |

| 3.7.5 Current Word Register (READ/WRITE)                    | 1-236 |

| 3.7.6 Base Page, Base Address and Base Word Count Registers |       |

| 3.7.7 Command Register                                      | 1-236 |

| 3.7.8 Mode Register                                         | 1-237 |

| 3.7.9 Extended Mode Registers (WRITE ONLY)                  | 1-237 |

| 3.7.9.1 8-Bit I/O, "Count By Bytes" Mode                    | 1-238 |

| 3.7.9.2 16-Bit I/O, "Count By Words"                        |       |

| (Address Shifted) Mode                                      | 1-238 |

| 3.7.9.3 16-Bit I/O, "Count By Bytes" Mode                   | 1-238 |

| 3.7.9.4 32-Bit I/O "Count By Bytes" Mode                    | 1-238 |

| 3.7.9.5 EOP Input/Output Selection                          |       |

| 3.7.9.6 Stop Register Selection                             | 1-238 |

| 3.7.9.7 Summary of the DMA Transfer Sizes                   | 1-238 |

| 3.7.10 Request Register (Write Only)                        |       |

| 3.7.11 Mask Register                                        |       |

| 3.7.12 Status Register                                      | 1-240 |

| 3.7.13 Set Chaining Mode Register                           |       |

| 3.7.14 Set Chaining Mode Status Register                    |       |

| 3.7.15 Channel Interrupt Status Register                    |       |

| 3.7.16 Chain Buffer Expiration Control Register             |       |

| 3.8 Software Commands                                       | 1-243 |

| 3.8.1 Clear Byte Pointer Flip-Flop                          |       |

| 3.8.2 Master Clear                                          |       |

| 3.8.3 Clear Mask Register                                   | 1-244 |

| 3.9 Terminal Count/EOP Summary                              | 1-244 |

| 4.0 BUS ARBITRATION                                         |       |

| 4.1 Bus Timeout                                             |       |

| 4.1.1 8 μs Bus Timeout                                      |       |

| 4.1.2 32 µs Bus Timeout                                     |       |

| 4.2 4 μs Limit on DMA Transfers                             |       |

| 4.3 EISA Bus Master Status Latch                            |       |

| 2.0. Bas master status Lateri                               | 1-246 |

| CO    | <b>NTENTS</b> P                                                   | AGE   |

|-------|-------------------------------------------------------------------|-------|

| 5.0 I | NTERRUPT CONTROLLER                                               | 1-247 |

| 5.    | 1 Interrupt Controller I/O Address Map                            | 1-247 |

|       | .2 Interrupt Definition Table                                     |       |

| 5.    | .3 Interrupt Request Register (IRR) and In-Service Register (ISR) | 1-248 |

| 5.    | .4 Priority Resolver                                              | 1-248 |

| 5.    | .5 Interrupt Mask Register (IMR)                                  | 1-248 |

| 5.    | .6 INT (Interrupt)                                                | 1-248 |

| 5.    | .7 INTA # /(ST2 #) (Interrupt Acknowledge)                        | 1-248 |

| 5.    | .8 Interrupt Sequence                                             | 1-249 |

| 5     | .9 80 x 86 Mode                                                   | 1-249 |

| 5     | .10 Programming the Interrupt Controller                          | 1-250 |

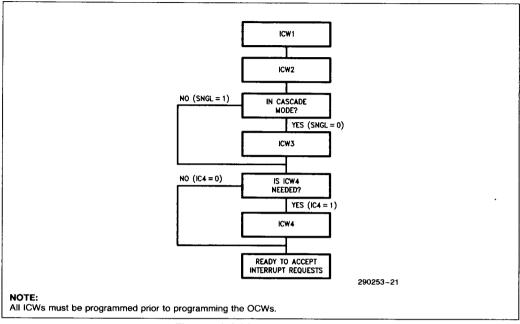

|       | .11 Initialization Command Words                                  |       |

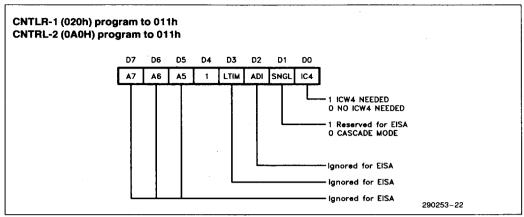

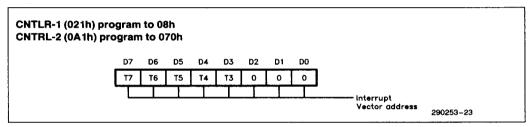

|       | 5.11.1 Initialization Command Words 1 and 2 (ICW1, ICW2)          | 1-251 |

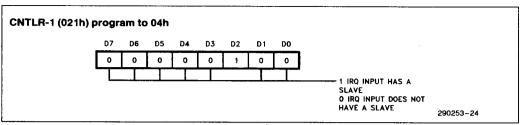

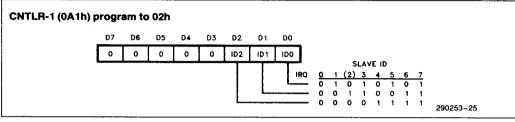

|       | 5.11.2 Initialization Command Word 3 (ICW3)                       | 1-252 |

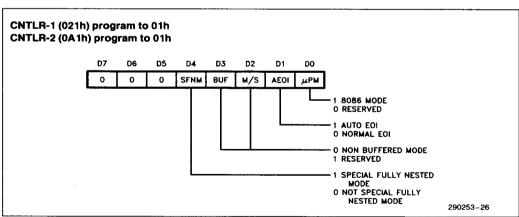

|       | 5.11.3 Initialization Command Word 4 (ICW4)                       | 1-253 |

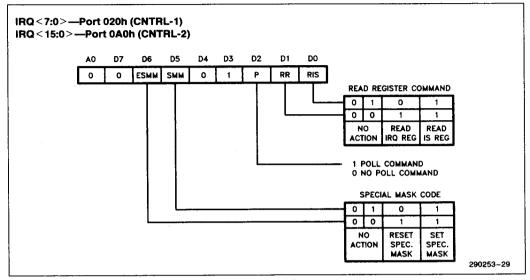

| 5     | .12 Operation Control Words (OCWS)                                | 1-254 |

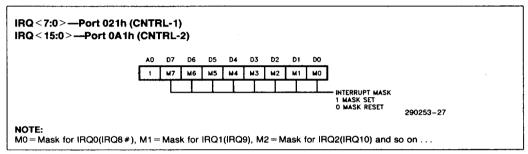

|       | 5.12.1 Operation Control Word 1 (OCW1)—Read/Write                 |       |

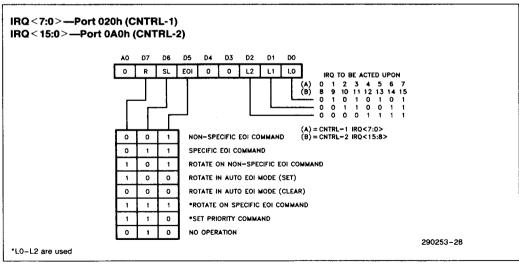

|       | 5.12.2 Operation Control Word 2 (OCW2)                            | 1-254 |

|       | 5.12.3 Operation Control Word 3 (OCW3)                            | 1-255 |

| 5     | .13 End-Of-Interrupt Operation                                    |       |

|       | 5.13.1 End Of Interrupt (EOI)                                     |       |

|       | 5.13.2 Automatic End Of Interrupt (AEOI) Mode                     |       |

| 5     | .14 Modes of Operation                                            |       |

|       | 5.14.1 Fully Nested Mode                                          |       |

|       | 5.14.2 The Special Fully Nested Mode                              |       |

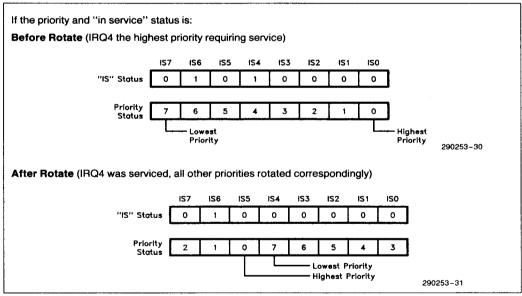

|       | 5.14.3 Automatic Rotation (Equal Priority Devices)                |       |

|       | 5.14.4 Specific Rotation (Specific Priority)                      | 1-257 |

|       | 5.14.5 Poll Command                                               | 1-257 |

|       | 5.14.6 Cascade Mode                                               | 1-258 |

|       | 5.14.7 Edge and Level Triggered Modes                             |       |

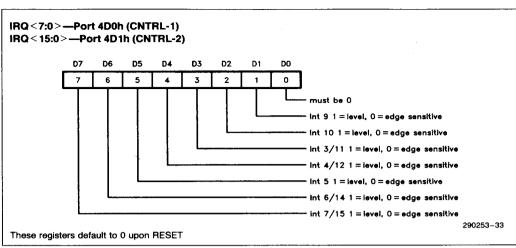

|       | 5.14.7.1 Edge/Level Triggered Control Register (ELCR)             |       |

| 5     | .15 Interrupt Masks                                               |       |

|       | 5.15.1 Masking on an Individual Interrupt Request Basis           |       |

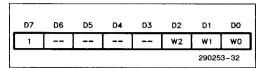

|       | 5.15.2 Special Mask Mode                                          |       |

| 5     | 16 Reading the Interrupt Controller Status                        |       |

| CONTENTS                                                                                                                                                                                                                                                                                                    | PAGE                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 6.0 NON-MASKABLE INTERRUPT PORTS 6.1 NMI Status and Control (Port 061h) 6.2 NMI Extended Status and Control (Port 0461h)                                                                                                                                                                                    | 1-260                                     |

| 6.3 Software NMI Generation (Port 0462h) 6.4 NMI Enable/Disable and Real-Time Clock Address (Port 070h)                                                                                                                                                                                                     | 1-262                                     |

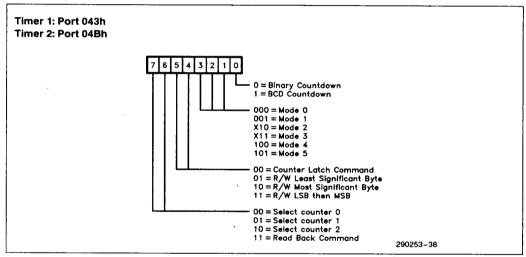

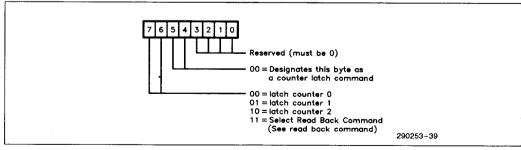

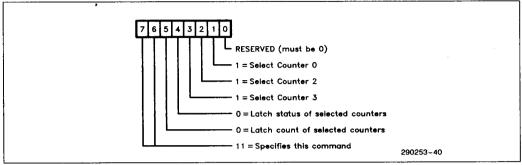

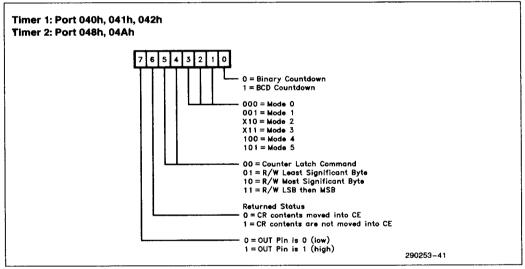

| 7.0 INTERVAL TIMER 7.1 Programming the Interval Timer 7.1.1 Interval Timer Control Word Format 7.1.2 Interval Timer Control Latch Command 7.1.3 Interval Timer Read Back Command                                                                                                                            | 1-262<br>1-263                            |

| 8.0 DETAILED SIGNAL DESCRIPTION  8.1 Signals Used during Arbitration  8.2 Signals Used during DMA and Register Access  8.3 Signals Used during an Interrupt Sequence  8.4 Counter/Timer, NMI and Miscellaneous Utility Signals                                                                              | 1-265<br>1-267                            |

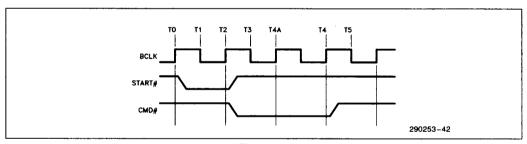

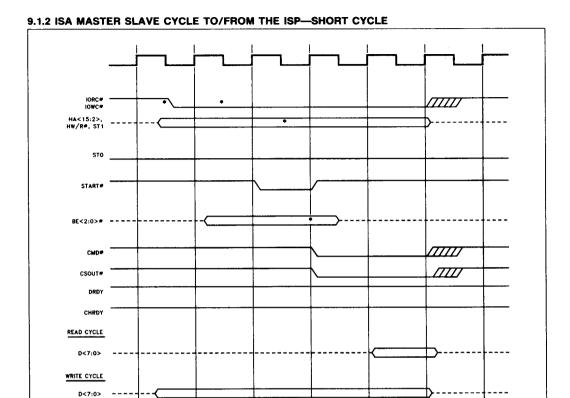

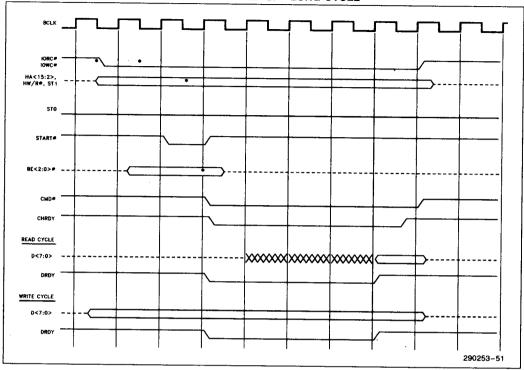

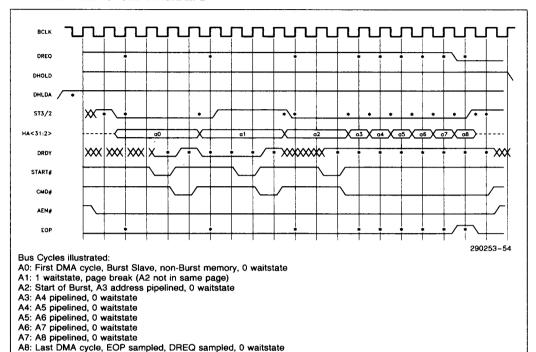

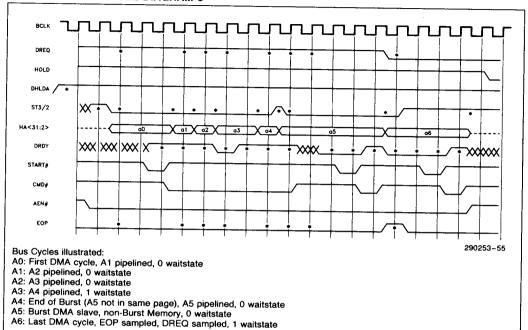

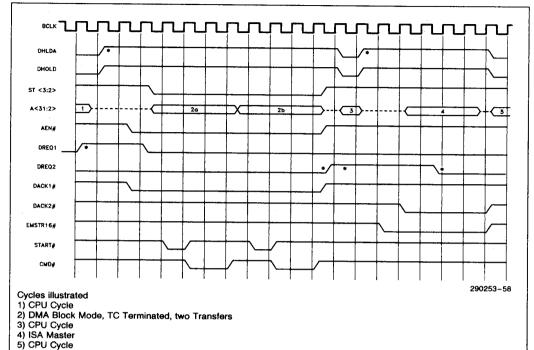

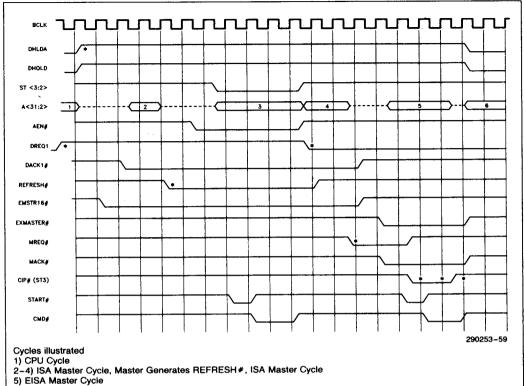

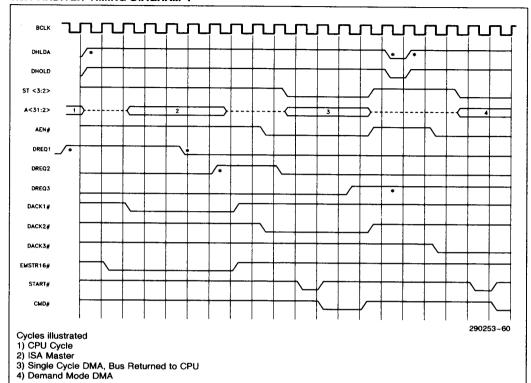

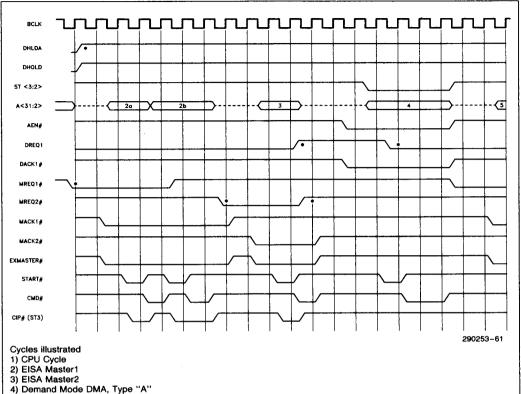

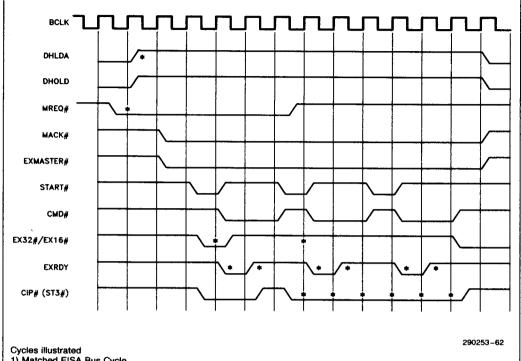

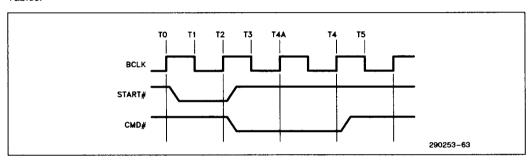

| 9.0 BASIC FUNCTION TIMING DIAGRAMS  9.1 Slave Mode  9.1.1 EISA Master or Host CPU Cycle to/from ISP  9.1.2 ISA Master Slave Cycle to/from the ISP—Short Cycle  9.1.3 ISA Master Slave Cycle to/from the ISP—Long Cycle  9.2 DMA Master Mode                                                                 | 1-273 1-273 1-274 1-275 1-276             |

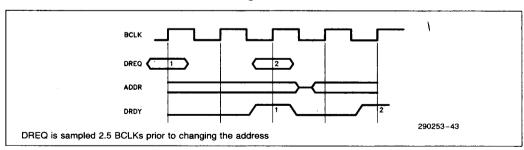

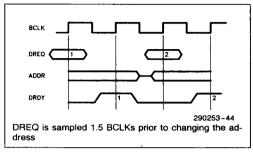

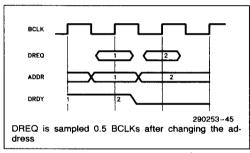

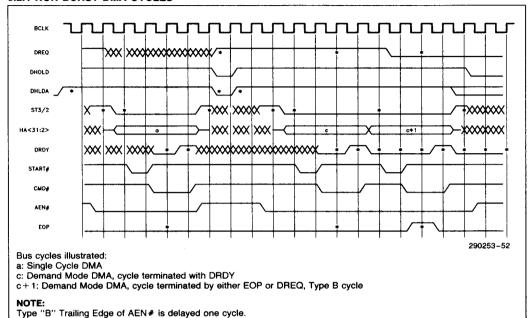

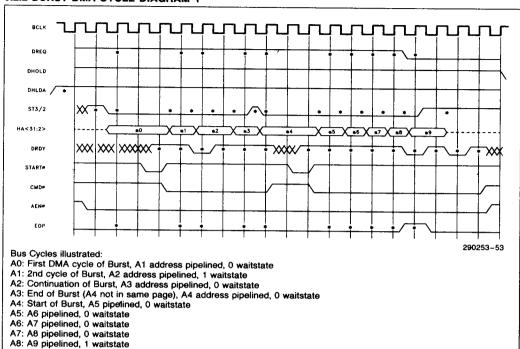

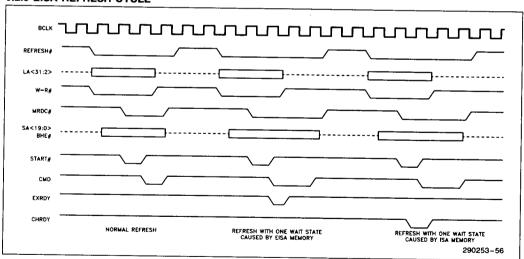

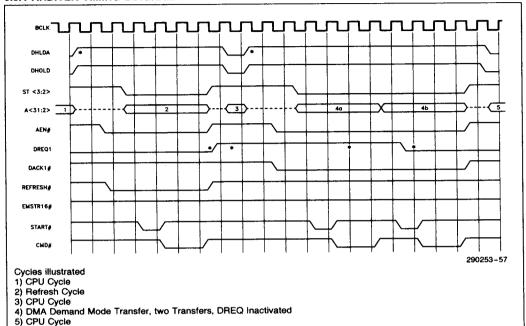

| 9.2.1 Non-Burst DMA Cycles 9.2.2 Burst DMA Cycle Diagram 1 9.2.3 Burst DMA Cycle Diagram 2 9.2.4 Burst DMA Cycle Diagram 3 9.2.5 EISA Refresh Cycle 9.3 Arbiter Timing Diagrams 9.3.1 Arbiter Timing Diagram 1 9.3.2 Arbiter Timing Diagram 2 9.3.3 Arbiter Timing Diagram 3 9.3.4 Arbiter Timing Diagram 4 | 1-277 1-278 1-279 1-280 1-281 1-282 1-283 |

| 9.3.5 Arbiter Timing Diagram 5 9.3.6 Arbiter Timing Diagram 6—CIP# (ST3#) Timing  10.0 D.C. SPECIFICATIONS 10.1 Maximum Ratings 10.2 D.C. Specification Tables                                                                                                                                              | 1-285<br>1-286<br>1-286                   |

| CONTENTS                             | PAGE  |

|--------------------------------------|-------|

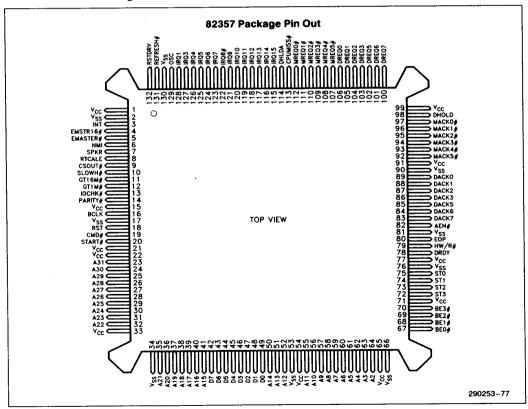

| 11.0 A.C. SPECIFICATIONS             | 1-287 |

| 11.1 A.C. Characterization Tables    | 1-287 |

| 11.2 A.C. Characteristic Waveforms   | 1-291 |

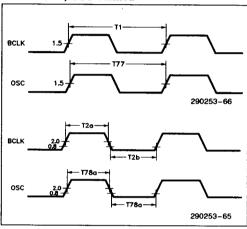

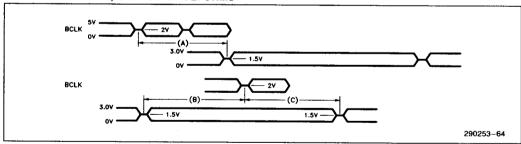

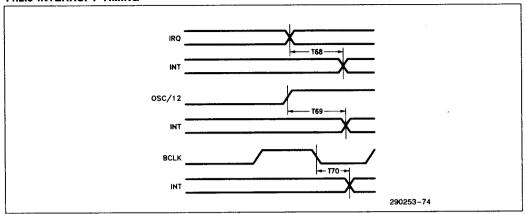

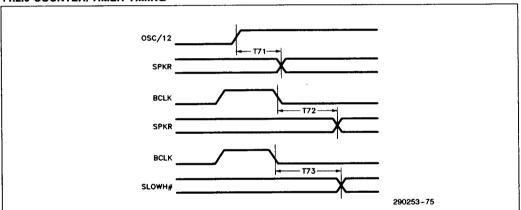

| 11.2.1 BCLK, OSC Timing              | 1-291 |

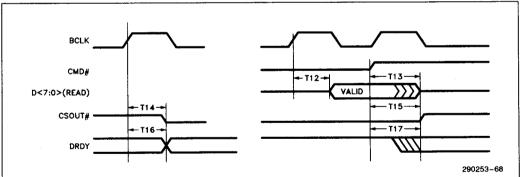

| 11.2.2 Slave Mode Timing             | 1-292 |

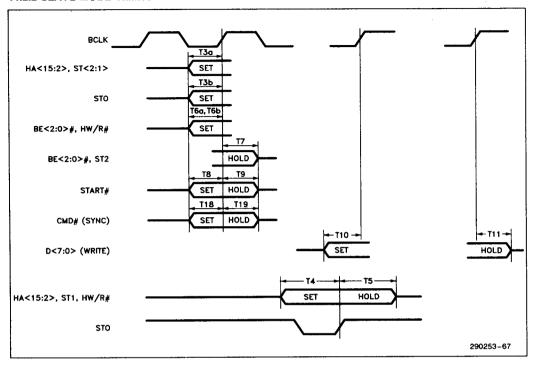

| 11.2.3 DMA Master Timing             | 1-293 |

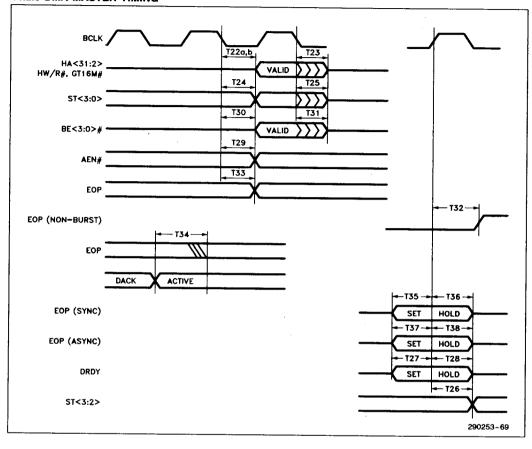

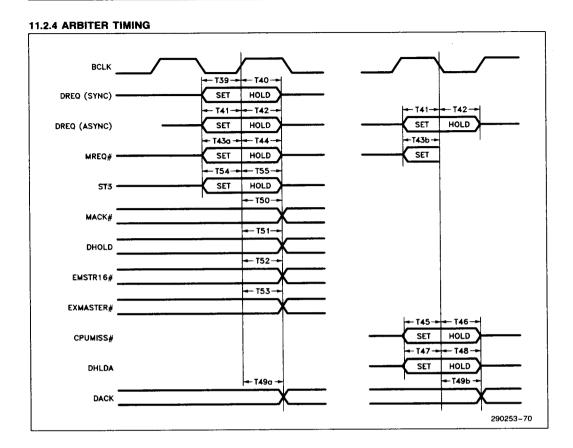

| 11.2.4 Arbiter Timing                | 1-294 |

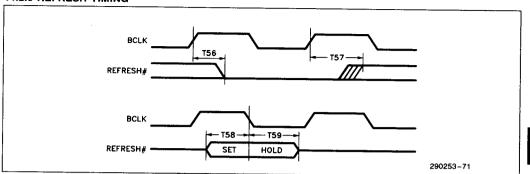

| 11.2.5 Refresh Timing                | 1-295 |

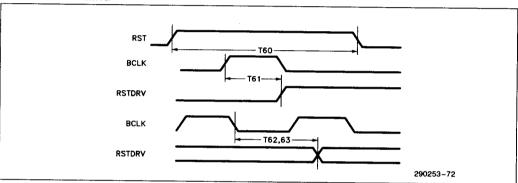

| 11.2.6 Reset Timing                  | 1-295 |

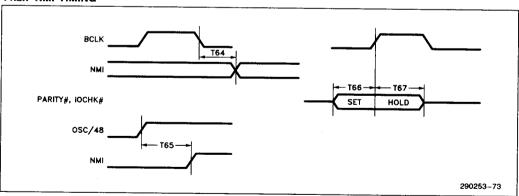

| 11.2.7 NMI Timing                    | 1-295 |

| 11.2.8 Interrupt Timing              | 1-296 |

| 11.2.9 Counter/Timer Timing          |       |

| 11.2.10 RTCALE, GT1M# Timing         | 1-296 |

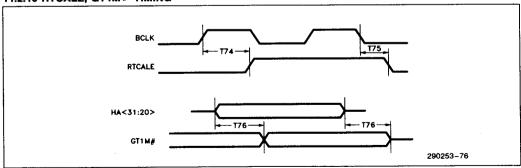

| 12.0 ISP PIN AND PACKAGE INFORMATION | 1-297 |

| 12.1 Signal Overview                 | 1-297 |

| 12.2 132 Package                     | 1-298 |

| 12.3 Device Pinout                   | 1-299 |

| 13.0 ISP PORT ADDRESS / I/O DECODING | 1-300 |

| 14.0 THERMAL SPECIFICATION           | 1-304 |

| 15.0 REVISION SUMMARY                | 1-305 |

The 82357 is a multi-function support peripheral that is designed to work in conjunction with the 82358 or 82358DT EISA Bus Controller to provide most of the system functions necessary in EISA specific applications.

The 82357 is comprised of several computer system functions that are typically found in separate LSI and VLSI components. These include: a high performance seven-channel programmable DMA Controller; an arbitration scheme that allows efficient bus sharing among multiple EISA masters, the host CPU, and DMA devices; a 16 level programmable interrupt controller which provides level-or-edge triggered interrupt capability on a channel-by-channel basis; non-maskable interrupt logic for multiple NMI control and generation; refresh address generation and control; and five counter/timers which provide a system timer interrupt, diskette time-out, DRAM refresh requests, and other system timing operations.

The DMA controller on the 82357 provides the timing control signals necessary to support a DMA data transfer rate of 33 Mbytes/sec. The DMA controller includes full function 32-bit addressability with control signal support for the transfer of data between devices of different data path widths using a single channel. Each channel functions independently in several modes.

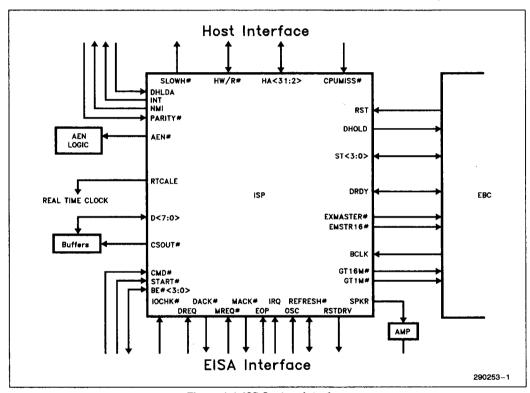

## 1.0 ISP SYSTEM INTERFACE ILLUSTRATION

The ISP connects to the Host bus, EISA bus, X bus and EBC (Bus Controller). These connections are illustrated in Figure 1-1.

### 2.0 FUNCTIONAL OVERVIEW

The following is a brief discussion of the functionality and features of the 82357. The DMA Controller, Arbiter, Interrupt controller, NMI's, and Timer/Counters each have a corresponding detailed section later in this data sheet.

### 2.1 Master and Slave Modes

The 82357 is either a slave device or a master device.

In slave mode, the ISP monitors the address lines and decodes all bus cycles attempting to read or write any of its internal registers. In slave mode, either an EISA master or the host CPU can read or write to any of the ISP's internal registers. 16-bit ISA

masters can read or write to any of the ISP's 82C37 PCAT compatible registers. The registers that cannot be accessed by an ISA master are located in the I/O space of 00H-0FH and 000H-0DFH. The ISP will disable these registers upon granting the ISA master the bus. In slave mode, the ISP also detects and responds to interrupt acknowledge cycles.

In master mode, the 82357 becomes the master of the bus system. It may peform either DMA cycles or refresh cycles at this time.

The arbiter on the ISP determines which mode the device is in.

### 2.2 DMA Controller

The DMA circuitry incorporates the functionality of two 82C37 DMA controllers with seven independently programmable channels, (Channels 0–3 and Channels 5–7). DMA Channel 4 is used to cascade the two controllers together and will default to cascade mode in the Mode register. In addition to accepting requests from DMA slaves, the DMA also responds to requests that are initiated by software. Software may initiate a DMA service request by setting any DMA channel Request register bit to a 1.

Any DMA channel may be programmed for 8-, 16-, or 32-bit DMA device size and ISA compatible, Type "A", Type "B", or burst DMA Type "C" modes. The 82357 provides the timing controls and the 82358 EISA Bus Controller performs the data size translations necessary for the DMA transfer. The DMA memory addressing circuitry supports full 32-bit addresses for DMA devices. Each channel includes a 16-bit ISA compatible Current register which holds the 16 least-significant bits of the 32-bit address, a Low Page register which contains the eight second most significant bits, and a High Page register which contains the eight most significant bits of the 32-bit address.

The channels can also be programmed for any of four transfer modes. The transfer modes include single, block, demand, or cascade. Each of the three active transfer modes, (single, block, and demand), can perform three different types of transfers, (read, write, or verify). The DMA Controller also features refresh address generation, buffer chaining, auto-initialization, and support for a Ring Buffer Data Structure in memory. Stop registers are used to help support Data Communication or devices that work from a Ring Buffer in memory (refer to Section 3.7.1 "USE OF STOP REGISTERS").

The DMA controller is at any time either in master mode or slave mode. In master mode, the DMA controller is either servicing a DMA slave's request for DMA cycles, generating refresh cycles, or allowing a 16-bit ISA master to use the bus via a cascaded DREQ signal. In slave mode, the 82357 monitors the bus and decodes and responds to I/O read and write commands that address its registers.

When the DMA is in master mode and servicing a DMA slave, it works in conjunction with the 82358 EISA bus controller to create bus cycles on the system bus. The DMA places addresses and the memory read/write (HW/R#) signal on the host CPU bus. It instructs the bus controller when to start and what

type of bus cycle to run with the ST0 and ST1 lines. The bus controller informs the DMA when to place a new address on the bus with the DRDY signal.

## 2.3 System Arbiter

The system arbiter evaluates requests for the bus coming from several sources which include the DREQ lines (DMA channels), MREQ# lines, refresh requests (Timer 1 Counter 1), and the host CPU (CPUMISS#). The DREQ lines are used by 8-, 16-, or 32-bit DMA slave devices to request DMA service and by existing 16-bit ISA masters to request the bus; the MREQ# lines are used by new 16- or 32-bit

Figure 1-1. ISP System Interface

EISA masters for general bus request; the CPUM-ISS# line is used by the host CPU when requesting bus access; and Timer 1 Counter 1 specifically is used to generate internal requests for refresh. The default master of the bus is the CPU. It is granted the bus if there are no requesters.

The DMA channels, when used by 16-bit ISA masters for direct access to the bus, must be placed in Cascade mode. In Cascade mode, the DMA controller will respond to DREQ with DACK# and EMSTR16#, but HW/R#, ST0, ST1, A <31:2>, and BE < 3:0># outputs will be disabled.

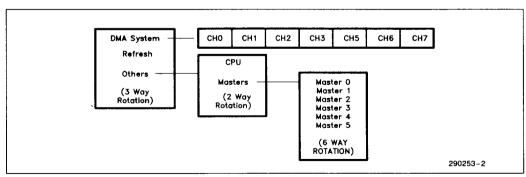

#### 2.3.1 PRIORITIES OF REQUESTERS

The ISP uses a three way rotating priority arbitration method. At each level, the devices which are considered equal are given a rotating priority. On a fully loaded bus, the order in which the devices are granted bus access is independent of the order in which they assert a bus request, since devices are serviced based on their position in the rotation. The arbitration scheme assures that DMA channels access the bus with minimal latency. As an example, in a system with DMA-2, a CPU, and two masters, all requesting the bus continuously, the grant sequence would be as follows:

DMA-2 CPU DMA-2 Master-1 DMA-2 CPU DMA-2 Master-2 and Repeat.

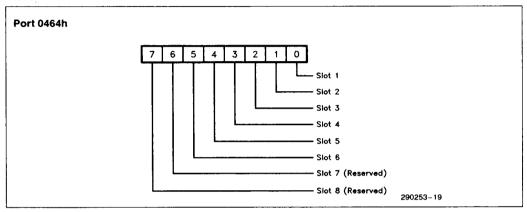

The priorities and the assignments are as shown in Figure 2-1.

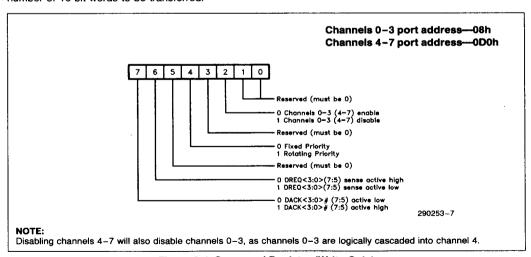

The DREQ lines can be placed in either fixed or rotating priority. The default mode is fixed and by programming the Command registers, the priority can be modified for rotate mode. The MREQ# lines are placed in rotate mode and cannot be changed.

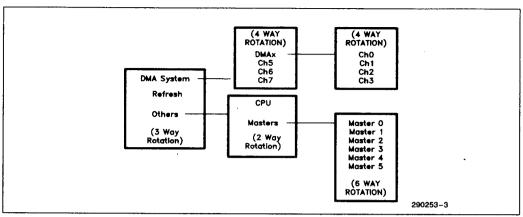

An example of programming the Command register to rotating priority is shown in Figure 2-2.

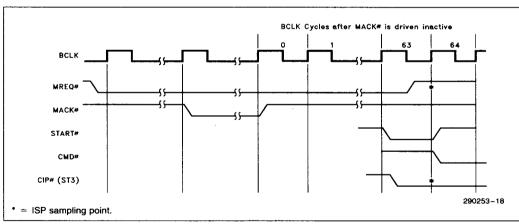

## 2.3.2 Preemption of EISA Masters and DMA Devices

An EISA bus master or a DMA slave device (that is not programmed for compatible timing) will be preempted from the bus by another device that requests use of the bus. This will occur regardless of the priority of the pending request. An EISA bus master must release the bus within 64 BCLKs (8  $\mu s$ ) after the arbiter drives its MACK # line inactive. If the bus is not released within the allowable time, a bus timeout (NMI) is generated and the RESDRV signal is driven active to reset the offending bus master. For DMA devices not using compatible timing mode, the DMA controller stops the DMA transfer and releases the bus within 32 BCLK (4  $\mu s$ ) of a preemption.

If the main CPU is currently using the bus and another device requests use of the bus, the ISP will immediately drive HOLD active and wait for the CPU or CACHE to drive DHLDA active. The CPU will be allowed to hold the bus as long as required to finish its current cycle without a 8 µs timeout (NMI) being generated. However, if the slave device that the CPU is addressing does not release EXRDY or CHRDY within 32 µs (256 BCLKs), a timeout (NMI) will be generated (refer to the following paragraph).

A slave which does not release EXRDY or CHRDY can cause the CMD# active time to exceed 32  $\mu$ s (256 BLCKs). To prevent the system from locking up, a bus timeout (NMI) will be generated. The counting of the 256 BLCKs starts at the request for the bus from another source. This will allow Burst cycles to run unimpeded if there are no pending requests.

16-bit ISA masters using the DREQ lines and cascaded DMA channels cannot be preempted from the bus via the ISP unless CMD# active exceeds 32  $\mu$ s (256 BLCKs).

Figure 2-1. Arbitration Priority

Figure 2-2. DMA Channels in Rotating Priority

## 2.3.3 ARBITRATION DURING NON-MASKABLE INTERRUPTS

If a non-maskable interrupt (NMI) is pending at the CPU, and the CPU is requesting the bus, then the external bus masters and the DMA controller will be by-passed each time they come up for rotation. This will give the CPU the bus bandwidth it requires to process the interrupt as fast as possible. The bus masters will still execute if the CPU is able to execute out of a local cache and does not require the bus.

## 2.3.4 DREQ AND DACK LATENCY CONTROL

The ISP arbiter maintains a minimum DREQ to DACK latency on DMA channels programmed to operate in compatible timing mode. This is to support older devices such as the 8272A. This is implemented as an eight BCLK delay for DREQs coming into the Priority resolution logic. The DREQs are effectively delayed by eight BCLKs prior to being seen by the arbiter logic. Software requests will not have this minimum request to DACK latency.

### 2.4 Refresh Generation

The refresh system uses the combined functions of the Interval Counter/Timers, Arbiter, and DMA. Interval Counter 1/Timer 1 generates an internal refresh request, the Arbiter detects a Refresh signal from either the Counter/Timer or the REFRESH# input and determines when the refresh will be done, and the DMA drives the refresh address out onto the host bus. Counter 1 Timer 1 should be programmed to provide a request for refresh about every 15 µs.

Requests for refresh cycles are generated by two sources: Timer 1 Counter 1 and 16-bit ISA masters that activate REFRESH# when they have bus ownership. EISA bus masters need not supply refresh cycles since the refresh controller can preempt the bus master and perform the necessary refresh cycles. 16-bit ISA bus masters that hold the bus longer than 15 μs must supply memory refresh cycles.

Each time an internal refresh request is not serviced within the normal 15  $\mu s$  interval, a counter is incremented. The counter counts up to four incomplete refresh requests. When a request cycle occurs, the pending refresh counter is decremented. Only one refresh cycle will be run and the bus will be released to the requester with the highest priority. If more refreshes are queued up, the bus will immediately be arbitrated for again, without waiting for the normal 15  $\mu s$  interval. If a refresh request is sensed while four refresh requests are pending, the incoming refresh request will be dropped. The bus is requested whenever one or more pending refreshes are recorded.

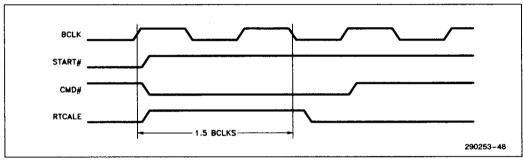

The DMA controller drives the refresh address out onto the LA < 15:2> address bus (14 bits of refresh address) and also enables the BE < 3:0> # lines so that they can be translated to SA < 1:0> lines. The High and Low Page register contents will also be placed on the LA < 31:16> bus during refresh. The refresh cycle lasts from the leading edge of START# through the rising edge of CMD# (two BCLKs) unless wait states are added by the memory slave negating EXRDY (EISA slaves) or CHRDY (ISA slaves). The 82358 bus controller, upon seeing REFRESH#, knows to run refresh cycles instead of DMA cycles.

The refresh address bit order on the LA < 15:2> and SA < 15:0> bus is as follows:

| 13 | 12 | 11 | 10 | 9  | 8  | 1 | 0 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | <br>Refresh<br>Counter Bits    |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------------------------------|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | LA < >,<br>SA < ><br>Addresses |

The 14-bit refresh counter will be reset to 0 upon RST. The Page register is located at I/O address 08FH and can be either read or written. The refresh High Page register is located at I/O address 048FH and can also be either read or written. When writing to the Low Page register, the upper Page register is not cleared to zero.

## 2.5 Interrupt Controller

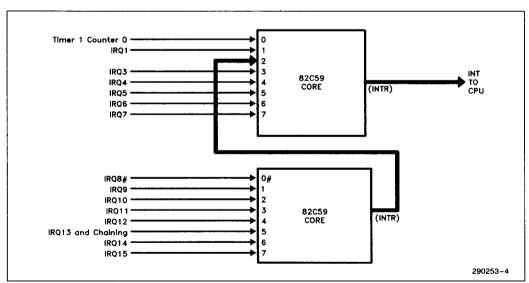

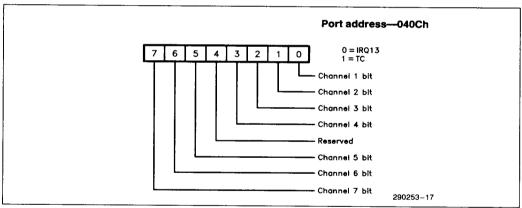

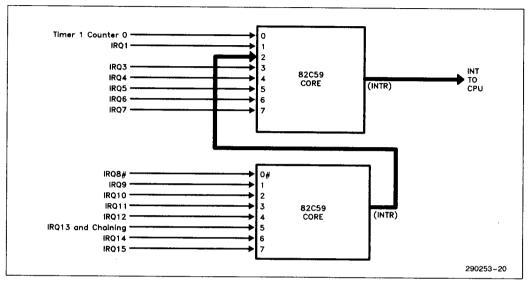

The 82357 provides an ISA compatible interrupt controller which incorporates the functionality of two 82C59 interrupt controllers. The two controllers are cascaded so that 14 external and two internal interrupts are possible. The master interrupt controller provides IRQ <7:0> and the slave interrupt controller provides IRQ <15:8#> (see Figure 2-3). The two internal interrupts are used for internal functions only and are not available externally. IRQ2 is used to cascade the two controllers together and IRQ0 is used as a system timer interrupt and is tied to interval Timer 1, Counter 0. The remaining 14 interrupt lines (IRQ1, IRQ3-IRQ15) are available for external system interrupts. IRQ13 is also shared internally with the chaining interrupt as well as being available for external use.

In addition to the ISA features, the ability to do interrupt sharing is included. A register is defined (ELCR) which allows an edge and level senses selection to be made on an individual channel by channel basis instead of on a complete bank of channels. Only the interrupt channels that connect to the EISA/ISA bus may be programmed for level sensitive mode. IRQ (0, 1, 2, 8 #, 13) must be programmed for edge sensitive operation. IRQ8# is active low edge sensitive only.

Figure 2-3. Block Diagram of the Interrupt Controller

## 2.6 Non-Maskable Interrupt (NMI)

An NMI is an interrupt requiring immediate attention and has priority over the normal interrupt lines (IRQX). The 82357 indicates error conditions by generating a non-maskable interrupt. An NMI can be caused by either a hardware or software mechanism.

NMI interrupts are caused by the following conditions:

- Parity errors on the mother board memory. The system board reports any parity errors from its memory system on the PARITY# line.

- Parity errors on the add-in memory boards on the ISA expansion bus. IOCHK# is driven low when this error occurs.

- Timeout of the fail-safe timer Counter 0 on the interval Timer 2 used to prevent the system from locking up. This NMI is sensed with a rising edge detect latch.

- 4. Timeout of an 8 μs 32-bit "bus" master timeout. If a 32-bit bus master retains the bus more than 8 μs after MACK# goes inactive, the 82357 will drive the NMI and RESDRV signals active together. The RESDRV signal will remain active until the NMI has been reset.

#### NOTE:

An NMI will not be generated in the case of the CPU holding onto the bus longer than the 8  $\mu s$  timeout.

- 5. Timeout of the 32 µs CMD# active timer.

- Software writing to the NMI I/O interrupt port (0462H). This is a special port which, when written, causes an immediate NMI interrupt, provided port 070h is enabled.

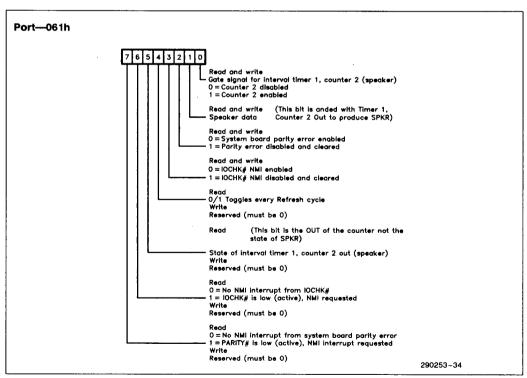

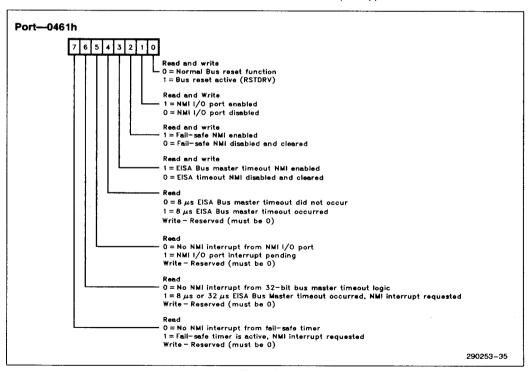

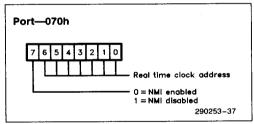

The NMI logic incorporates four different 8-bit registers. These registers are addressed as Port(061h), Port(070h), Port(0461h), and Port(0462h). The status of Ports (0461h) and (061h) are read by the CPU to determine which source caused the NMI. Bits set to 1 in these ports show which device requested an NMI interrupt. After the NMI interrupt routine processes the interrupt, the NMI status bits are cleared by the software. This is done by setting the corresponding enable/disable bit high. Port(070h) is the mask register for the NMI interrupts. This register can mask the NMI signal and also disable or enable all NMI sources. Writing to Port(0462h) with any data will cause an immediate NMI interrupt if enabled.

If it is desired to reset the system bus without resetting other devices in the system (standard system board devices are not reset), the Port(0461h) Bit <0> can be written with a (1). This bit should be held in this state for the desired RSTDRV active time and then returned to its normal state (0).

If a 32-bit bus master tries to hold the bus beyond the 8  $\mu s$  limit, or if CMD# is active for more than 32  $\mu s$ , the ISP will drive the NMI and RSTDRV signals active together. The RSTDRV signal will remain active until the NMI has been reset by resetting bit <3> to 0 in I/O Port 0461h.

## NMI Source Enable/Disable and Status Port Bits

| NMI Source          | IO Port Bit<br>for Status Reads | IO Port Bit<br>for Enable/Disable |

|---------------------|---------------------------------|-----------------------------------|

| PARITY#             | Port 061h, Bit 7                | Port 061h, Bit 2                  |

| Fail Safe Timer     | Port 0461h, Bit 7               | Port 0461h, Bit 2                 |

| IOCHK#              | Port 061h, Bit 6                | Port 061h, Bit 3                  |

| Bus Timeout         | Port 0461h, bit 6               | Port 0461h, Bit 3                 |

| Write to Port 0462h | Port 0461h, Bit 5               | Port 0461h, Bit 1                 |

7

To ensure that all NMI requests are serviced, the NMI service routine software needs to incorporate a few very specific requirements. These requirements are due to the edge detect circuitry of the host microprocessor, 80386 or 80486. The software flow would need to be the following:

- NMI is detected by the processor on the rising edge of the NMI input.

- 2. The processor will read the status stored in Ports 061h, and 0461h to determine what sources caused the NMI. The processor may then reset the register bits controlling the sources that it has determined to be active. Between the time the processor reads the NMI sources and resets them, an NMI may have been generated by another source. The level of the NMI will then remain active. This new NMI source will not be recognized by the processor because there was no edge on NMI.

- 3. The processor must then disable all NMI's by writing Bit <7> of Port 070h high and then enable all NMI's by writing Bit <7> of Port 070h low. This will cause the NMI output to transition low then high if there are any pending NMI sources. The CPU's NMI input logic will then register a new NMI.

## 2.7 Interval Timers

The 82357 contains five counter/timers that are equivalent to those found in the 82C54 programmable interval timer. The counter timers are addressed as though they are contained in two separate 82C54 timers. Timer 1 contains three counters and Timer 2 contains two counters. Counter 1 of Timer 2 is not implemented in EISA systems. Each timer provides three frequencies or counters for the system. The 8 MHz counters use BCLK for a clock source; the others use a division of the 14.31818 MHz OSC input. The 14.31818 MHz OSC input is either divided by 12 or 48 to provide the necessary frequencies.

The outputs of the timers are directed to key system functions. Interval Timer 1, Counter 0 is connected to the interrupt controller IRQ0 and provides a system timer interrupt for a time-of-day, diskette timeout, or other system timing functions. Counter 1 generates a refresh-request signal and Counter 2 generates the tone for the speaker.

Interval Timer 2, Counter 0 is the fail-safe timer that can generate NMI interrupts on the NMI line at reqular intervals as a means of preventing the system from locking up. Counter 1 is not implemented. Counter 2 is used to slow down the CPU by means of pulse-width modulation and is tied to the SLOWH# output. To use the slow function, the counter must be programmed. If the counter is not programmed, SLOWH# will not go active. Counter 2 is placed in the one-shot mode and is triggered by the refresh request signal generated by Timer 1/ Counter 1 only. If the counter has been programmed, the Counter 2 output (SLOWH#) will stop the CPU for the programmed period of the one-shot every time a refresh request occurs. To enable the one-shot, select Mode 1 (one-shot) operation by writing to I/O address 4Bh a value of 92h.

#### NOTE:

Refresh cycles will not necessarily be generated during the time the SLOWH# signal is active, the Arbiter will determine when the refresh cycle will be placed on the bus.

Because the slow function depends upon the refresh-request frequency of another counter, chaining the refresh-request frequency will affect the period of Counter 2 output (SLOWH#) signal. Timer 2 Counter 2 is not configured for the one-shot mode and is not programmed for a counter value until a speed reduction in the system is required. At such time, the value programmed depends on the system speed desired.

| Figure   | 2-4 | liete | the | Interval | Timer | Functions.   |

|----------|-----|-------|-----|----------|-------|--------------|

| i igui e | 2-4 | 11313 | uie | miterval | (     | i unicaciis. |

|          | Interval Timer Function      | ns                            |

|----------|------------------------------|-------------------------------|

|          | Interval Timer 1             | Interval Timer 2              |

| Function | Counter 0<br>System Timer    | Counter 0<br>Fail-Safe Timer  |

| Gate     | Always On                    | Always On                     |

| Clock In | 1.193 MHz (OSC/12)           | 0.298 MHz (OSC/48)            |

| Out      | INT-1 IRQ0                   | NMI Interrupt                 |

|          | Counter 1<br>Refresh Request | *                             |

| Gate     | Always On                    |                               |

| Clock In | 1.193 MHz (OSC/12)           |                               |

| Out      | Refresh Request              |                               |

|          | Counter 2                    | Counter 2                     |

| Gate     | Programmable<br>Port 61h     | Refresh Request               |

| Clock In | 1.193 MHz (OSC/12)           | 8 MHz (BCLK)                  |

| Out      | Speaker                      | CPU Speed Control<br>(SLOWH#) |

Figure 2-4. Interval Timer Functions

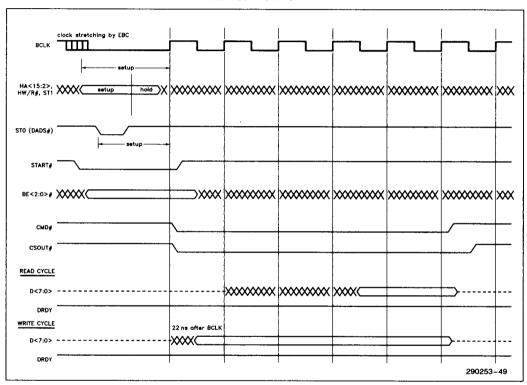

## 2.8 Register Access

To the system, the ISP appears as an 8-bit EISA slave. The following signals are used to access the ISP's internal registers:

D<7:0>, HA<15:2> and BE<2:0>#, HW/R#, ST<2:0>, CMD#, START#, DRDY, and CSOUT#

The number of BCLKs required to complete an ISP access depends on the master accessing the ISP and the register being accessed. Non-ISA masters will always see a default 8-bit I/O cycle (6 BCLKs). An ISA master will either see an 8-bit I/O cycle without wait states (3 BCLKs) or an 8-bit I/O cycle with wait states (6 BCLKs) depending on the register being accessed.

Because the ISP does not have a designated output signal to instruct the master of the ISP's bus size, the 82358 bus controller will do all necessary bus conversions and use the 8-bit ISA timing to access the ISP registers. In order to lengthen bus cycles begun by ISA masters for slower ISP registers, the DRDY signal is used to activate the EBC's CHRDY signal. The EBC will combinatorially connect the DRDY signal to CHRDY if an 8-bit I/O is the target of an ISA master's cycle. This will ensure that the CMD# pulse width will be at least five BCLKs long for the slower registers.

## 3.0 DMA CONTROLLER

### 3.1 DMA Transfer Modes

The ISP DMA supports four transfer modes: Single, Block, Demand, and Cascade.

### NOTE:

Memory to Memory Transfers are not supported by the ISP.

### 3.1.1 SINGLE TRANSFER MODE

In Single Transfer mode the device is programmed to make one transfer only. The word count will be decremented and the address decremented or incremented following each transfer. When the word count "rolls over" from zero to FFFFFFH, or an external End of Process (EOP) is encountered, a Terminal Count (TC) will cause an Autoinitialize if the channel has been programmed to do so. If Chaining is enabled the next chain buffer will be enabled if available.

DREQ must be held active until DACK# becomes active in order to be recognized. If DREQ is held active throughout the single transfer, the bus will be released to the CPU after a single transfer. The bus will be immediately requested again, and, upon winning the bus, another single transfer will be performed. This allows other devices a chance to execute if they require the bus.

### 3.1.2 BLOCK TRANSFER MODE

In Block Transfer mode the device is activated by DREQ to continue making transfers during the service until a TC, caused by word count going to FFFFFH, or an external EOP, is encountered. DREQ need only be held active until DACK becomes active. An Autoinitialization will occur at the end of the service if the channel has been programmed for it. In this mode, it is possible to lock out other devices for a period of time (including refresh) if the transfer count is programmed to a large number.

#### 3.1.3 DEMAND TRANSFER MODE

In Demand Transfer mode the device is programmed to continue making transfers until a TC is encountered or an external EOP is encountered, or until DREQ goes inactive. Thus transfers may continue until the I/O device has exhausted its data capacity. After the I/O device has had a chance to catch up, the DMA service is reestablished by means of a DREQ. During the time between services when the system is allowed to operate, the intermediate values of address and word count are stored in the DMA controller Current Address and Current Word Count registers. A TC can cause an Autoinitialize at the end of the service if the channel has been programmed for it.

### 3.1.4 CASCADE MODE

This mode is used to cascade more than one DMA controller together for simple system expansion. This allows the DMA requests of the additional device to propagate through the priority network circuitry of the preceding device. The priority chain is preserved and the new device must wait for its turn to acknowledge requests. In this architecture, Channel 0 of the second controller (ch4) is used to cascade the first controller to provide a total of seven channels.

Cascade mode is also used to allow direct access of the system by 16-bit ISA bus masters. These devices use the DREQ and DACK signals to arbitrate for the system bus and then they drive the address and command lines to control the bus.

In Cascade Mode, the DMA controller will respond to DREQ with DACK# but the HW/R#, address, and ST0-ST3 outputs will be disabled.

Channel 4 is used to connect the second half of the DMA system, this channel is not available for any other purpose.

## 3.2 Transfer Types

Each of the three active transfer modes can perform three different types of transfers. These are Read, Write and Verify.

## 3.2.1 WRITE TRANSFER

Write transfers move data from an I/O device to memory starting with the DMA activating HW/R# and the ST<3:0> lines, the Bus Controller will then activate IORC# and the appropriate EISA or ISA control signals to indicate a memory write depending on which bus the memory is determined to be.

#### 3.2.2 READ TRANSFER

Read transfers move data from memory to an I/O device starting with the DMA deactivating HW/R# and activating the ST<3:0> lines, the Bus Controller will then activate IOWC# and the appropriate EISA or ISA control signals to indicate a memory read, depending on which bus the memory is determined to be.

### **3.2.3 VERIFY TRANSFER**

Verify transfers are pseudo transfers. The DMA controller operates as in Read or Write transfers generating addresses, and producing TC, etc. However, no ST < 3:0 > signals are activated so the Bus Controller does not activate the memory and I/O control lines. Only the DACK lines will go active. Since no EISA cycles are broadcasted in this mode, the LA bus is not copied to the SA bus. Internally the DMA controller will count BCLKs so that the DACK lines have a defined pulse width. This pulse width is nine BCLKs long. If Verify transfers are repeated during Block or Demand DMA requests, each additional pseudo transfer will add eight BCLKs. The DACK lines will not be toggled for repeated transfers.

### 3.3 Autoinitialize

By programming a bit in the Mode register, a channel may be set up as an Autoinitialize channel. During Autoinitialize initialization, the original values of the Current page, Current address and Current Word Count registers are automatically restored from the Base Page, Address, and Word count registers of that channel following TC. The Base registers are loaded simultaneously with the Current registers by the microprocessor and remain unchanged throughout the DMA service. The mask bit is not set when the channel is in Autoinitialize. Following Autoinitialize the channel is ready to perform another DMA service, without CPU intervention, as soon as a valid DREQ is detected.

## 3.4 Channel Priority

For priority resolution the DMA consists of two logical channel groups—channels 0-3 and channels 4-7. Each group may be in either Fixed or Rotate mode, as determined by the Command register.

#### 3.4.1 FIXED PRIORITY

The initial fixed priority structure is as follows:

High priority Low priority (0, 1, 2, 3) 5, 6, 7

Channel 0 has the highest priority, then 1, 2, 3, 5, 6, and channel 7 has the lowest priority.

#### 3.4.2 ROTATING PRIORITY

Rotation allows for "fairness" in priority resolution. The priority chain rotates so that the last channel serviced is assigned the lowest priority in the channel group (0-3, 5-7).

Channels 0-3 rotate as a group 4, and are always placed between Channel 5 and Channel 7 in the priority list.

Channels 5-7 rotate as a group of 4—this is, the three channels (5-7) plus the channel 0-3 group.

Figure 3-1 will demonstrate rotation:

|                                    | High            | Low     |

|------------------------------------|-----------------|---------|

| Initial setting—                   |                 |         |

| Group 0-3 is in rotation mode,     |                 |         |

| Group 4-7 is in fixed mode:        | (0, 1, 2, 3) 5  | , 6, 7  |

| After servicing channel 2          | (3, 0, 1, 2) 5  | , 6, 7  |

| After servicing channel 3 —        | (0, 1, 2, 3) 5  | , 6, 7  |

| Both groups in rotation mode:      |                 |         |

| Initial setting —                  | (0, 1, 2, 3) 5  | , 6, 7  |

| After servicing channel 0 —        | 5, 6, 7, (1, 2, | 3, 0)   |

| After servicing channel 5 —        | 6, 7, (1, 2, 3, | 0), 5   |

| After servicing channel 6          | 7, (1, 2, 3, 0) | , 5, 6  |

| After servicing channel 7 —        | (1, 2, 3, 0), 5 | 6, 6, 7 |

| (Notice that the first service cau | sed double rota | ation)  |

Figure 3-1

## 3.5 Buffer Chaining

The buffer chaining mode of a channel is useful for transferring data from a peripheral to several different areas of memory within one transfer operation (from the DMA device's viewpoint). This is accomplished by causing the DMA to interrupt the host CPU for more programming information (or signal an EISA master via TC, if an EISA master needs to program the DMA) while the previously programmed transfer is still in progress. Upon completion of the previous transfer, the DMA controller will then load the new transfer information automatically. In this way, the entire transfer can be completed without interrupting the operation of the DMA device. This mode is most useful for DMA single-cycle or demand modes where the transfer process allows time for the CPU to execute the interrupt routine.

The buffer chaining mode of a channel may be entered by programming the address and count of a transfer as usual. After the initial address and count is programmed, the Base registers are selected via the "Set Chaining Mode" register "Chaining mode Enabled" bit. The address and count for the second transfer and both the "Chaining mode Enabled" and the "program complete" bits of the Set Chaining Mode register should be programmed at this point, before starting the DMA process. When, during the DMA process, the Current Buffer is expired, the Base address, page, and Count registers will be transferred to the Current registers and a signal that the buffer has been expired is sent to the programming master.

This signal will be an IRQ13 if the master is the Host CPU, or a TC if the programming master is an EISA device. The type of programming master is indicated in the DMA's Set Chaining Mode Register, Bit 4. If the Host CPU is the programming master for the Channel, TC will be generated only if the Current buffer expires and there is no Next Buffer stored in the Base registers.

Upon the expiration of a Current Buffer, the new Base register contents should be programmed and both the "Chaining mode Enabled" and "program complete" bits of the "Set Chaining Mode" register should be set. This resets the interrupt, if the Host CPU was the programming master, and allows for the next Base register to Current register transfer. If the "program complete" bit is not set before the current transfer reaches TC, then the DMA controller will set the Mask Bit and the TC bit in the Status register and stop transferring data. In this case, an over-run is likely to occur. To determine if this is the case, a read from the Status register or the Mask register can be done (the Mask register has been made readable). If the channel is masked or has registered a TC, the DMA channel has been stopped and the full address, count, and chaining mode must be programmed to return to normal operation.

Figure 3-2. Buffer Chaining Programming Flow

Note that if the Host CPU is the programming master, an interrupt will only be generated if a Current Buffer expires and chaining mode is enabled, it will not occur during initial programming. The "Channel Interrupt Status" register will indicate pending interrupts only. That is, it will indicate an empty Base register with "Chaining Mode" enabled. When Chaining mode is enabled, only the Base registers are written by the processor, and only the Current registers can be read. The Current registers are only updated on a TC.

## 3.6 DMA Enhanced Timing

#### 3.6.1 COMPATIBLE TIMING

Compatible timing is provided for DMA slave devices, which, due to some design limitation, cannot support one of the faster timings. Compatible timing runs at 1125 ns/single cycle and 1000 ns/cycle during the repeated portion of a BLOCK or DEMAND mode transfer.

## 3.6.2 TYPE "A" TIMING

Type "A" timing is provided to allow shorter cycles when used with EISA memory. If 8/16-bit ISA memory is decoded, the system automatically reverts to ISA DMA type compatible timing on a cycle-by-cycle basis. Type "A" timing runs at 875 ns/single cycle and 750 ns/cycle during the repeated portion of a BLOCK or DEMAND mode transfer. Type "A" timing varies from compatible timing primarily in shortening the memory operation to the minimum allowed by EISA memory. The I/O portion of the cycle (data setup or write. I/O read access time) is the same as with compatible cycles. The actual active command time is shorter, but it is expected that the DMA devices which provide the data access time or write data setup time should not require excess IORC# or IOWC# command active time. Because of this, most ISA DMA devices should be able to use type "A" timing.

#### 3.6.3 TYPE "B" TIMING

Type "B" timing is provided for 8/16-bit ISA or EISA DMA I/O devices which can accept faster I/O timing. Type "B" only works with EISA memory. If 8/16-bit ISA memory is decoded, the system automatically reverts to ISA DMA type compatible timing on a cycle by cycle basis. Type "B" timing runs at 750 ns/single cycle and 500 ns/cycle during the repeated portion of a BLOCK or DEMAND mode transfer. Type "B" timing requires faster DMA slave devices than compatible timing in that the cycles are shortened so that the data setup time on I/O write cycles

is shortened and the I/O read access time is required to be faster. Some of the current ISA devices should be able to support type "B" timing, but these will probably be more recent designs using relatively fast technology.

## 3.6.4 TYPE "C" (BURST TIMING)

Burst timing is provided for newly designed EISA DMA devices. The DMA slave device needs to monitor the EXRDY and IORC# or IOWC# signals to determine when to change the data (on writes) or sample the data (on reads). This timing will allow up to 33 Mbytes per second transfer rate with a 32-bit DMA device and 32-bit memory. Note that 8- or 16bit DMA devices are supported (through the programmable DMA address increment) and that they use the "byte lanes" natural to their size for the data transfer. As with all bursts, the system will revert to two BCLK cycles if the memory does not support burst. When a DMA burst cycle accesses non-burst memory and the DMA cycle crosses a page boundary into burstable memory, the EBC will continue performing non-burst cycles. This will not cause a problem since the data is transferred correctly.

## 3.7 Register Description

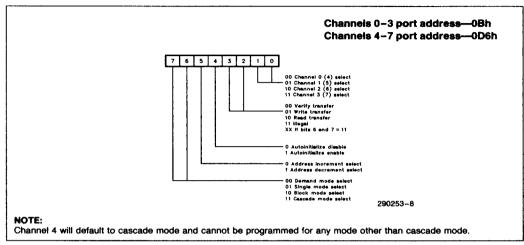

DMA Channel 4 is used to cascade the two DMA controllers together and should not be programmed for any mode other than cascade. The Mode register will default to cascade mode. Special attention should also be taken when programming the Command and Mask registers as related to channel 4 (refer to the Command and Mask register descriptions, Sections 3.7.7 and 3.7.11).

## 3.7.1. STOP REGISTERS (RING BUFFER DATA STRUCTURE)

To support a common data communication data structure (the ring buffer), a set of new DMA registers have been provided. These registers are called Stop registers. Each channel has 22-bits of register location associated with it. The 22-bits is distributed between three different registers (one 6-bit and two 8-bit). The Stop registers can be enabled or disabled by writing to the channel's corresponding Extended Mode register.

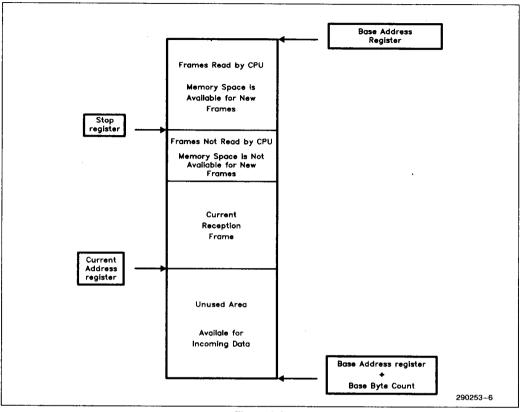

The ring buffer data structure reserves a fixed portion of memory, on doubleword boundaries, to be used for a DMA channel. Consecutively received frames or other data structures are stored sequentially within the boundaries of the ring buffer memory.

The beginning and end of the ring buffer area is defined in the Base Address register and the Base Address register + the Base Byte/Transfer Count. The incoming frames (data) are deposited in sequential locations of the ring buffer. When the DMA reaches the end of the ring buffer, indicating the byte count has expired, the DMA controller (if so programmed) will Autoinitialize. Upon autoinitialization, the Current Address register will be restored from the Base Address register, taking the process back to the start of the ring buffer. The DMA will then be available to begin depositing the incoming bytes in the ring buffers sequential locations-providing that the host CPU has read the data that was previously placed in those locations. The DMA determines that the CPU has read certain data by the value that the CPU writes into the Stop register.

Once the data of a frame is read by the CPU, the memory location it occupies becomes available for other incoming frames. The Stop register prevents

the DMA from over writing data that has not yet been read by the CPU. After the CPU has read a frame from memory it will update the Stop register to point to the location that was last read. The DMA will not deposit data into any location beyond that pointed to by the Stop register. The last address transferred before the channel is masked is the first address that matches the Stop register. (See Table 3-1). The Stop registers store values to compare against A < 23:2 > only, so the size of the ring buffer is limited to 16 Mbytes.

The Bus Controller provides I/O recovery for back-to-back CPU to 8-bit I/O cycles. For EISA master accesses, I/O recovery of at least one BCLK must be provided by software.

#### NOTE:

I/O writes must match the I/O slave size (i.e., 8-bit writes must be used to program the ISP registers). When writing to the DMA registers, the DMA channels also must be masked.

## For example:

If the stop register = 00001Ch, the last three transfers will be:

Table 3-1

|           | By Bytes  | By Words  | By Dwords |  |

|-----------|-----------|-----------|-----------|--|

| Increment | XX00001Ah | XX000018h | XX000014h |  |

|           | XX00001Bh | XX00001Ah | XX000018h |  |

|           | XX00001Ch | XX00001Ch | XX00001Ch |  |

| Decrement | XX000021h | XX000023h | XX000027h |  |

|           | XX000020h | XX000021h | XX000023h |  |

|           | XX00001Fh | XX00001Fh | XX00001Fh |  |

Figure 3-3 is a diagram of a ring buffer data structure.

Figure 3-3

## 3.7.2 DMA MEMORY LOW PAGE REGISTER (READ/WRITE)

Each channel has an 8-bit Low Page register associated with it. The DMA memory Low Page register contains the eight second most-significant bits of the 32-bit address (16–23). It works in conjunction with the DMA controller's High Page register and Current Address register to define the complete (32-bit) address for the DMA channels and corresponds to the "Current Address" register for each channel. This 8-bit register is read or written directly by the processor or bus master. It may also be re-initialized by an Autoinitialize back to its original value. Autoinitialize takes place only after a TC or EOP.

## 3.7.3 DMA MEMORY HIGH PAGE REGISTER (READ/WRITE)

Each channel has an 8-bit High Page register. The DMA memory High Page register contains the eight most-significant bits of the 32-bit address (24–31). It works in conjunction with the DMA controller's Low Page register and Current Address register to define the complete (32-bit) address for the DMA channels and corresponds to the "Current Address" register for each channel. This 8-bit register is read or written directly by the processor or bus master. It may also be re-initialized by an Autoinitialize back to its original value. Autoinitialize takes place only after a TC or EOP.

1

This register is reset to 00h during the programming of both the low page register and the Current Address register. Thus, if this register is not programmed after the other address and Low Page registers are programmed, then its value will be zero. In this case, the DMA channel will operate the same as an 82C37 (from an addressing standpoint). This is the address compatibility mode.

If the high 8-bits of the address are programmed after the other addresses, then the channel will modify its operation to increment (or decrement) the entire 32-bit address. This is unlike the 82C37 "Page" register in the original PCs which could only increment to a 64K boundary (for 8-bit channels) or 128K (for 16-bit channels). This is extended address mode. In this mode, the EISA bus controller should generate the signals MRDC# and MWTC# only for addresses below 16 Mbytes.

### 3.7.3.1 Address Compatibility Mode

Whenever the DMA is operating in Address Compatibility mode, the addresses do not increment or decrement through the HIGH and LOW Page registers, and the high page register is set to 00h. This is compatible with the 82C37 and Page register implementation used in the PC AT\*. This mode is set when any of the lower three address bytes of a channel are programmed. If the upper byte of a channel's address is programmed last, the channel will go into Extended Address Mode. In this mode the high byte may be any value and the address will increment or decrement through the entire 32-bits. When programming the page register in compatible mode, the current address must also be programmed.

After RST all channels will be set to Compatibility Mode. The Master Clear command will also reset the proper channels to Compatibility Mode. The mode bits are stored in individual flip-flops on a perchannel basis.

## 3.7.4 CURRENT ADDRESS REGISTER (READ/WRITE)

Each channel has a 16-bit Current Address register. This register holds the value of the 16 least significant bits (0–15) of the full 32-bit address used during DMA transfers. The address is automatically incremented or decremented after each transfer and the intermediate values of the address are stored in the Current Address register during the transfer. This register is written to or read from by the microprocessor or bus master in successive 8-bit bytes. It may also be re-initialized by an Autoinitialize back to its original value. Autoinitialize takes place only after a TC or EOP.

## 3.7.4.1 Address Shifting when Programmed for 16-bit I/O Count by Words

To maintain compatibility with the implementation of the DMA in the PC AT which used the 82C37, the DMA will shift the addresses when the Extended Mode register is programmed for, or defaulted to, transfers to/from a 16-bit device count by words. The address shifting is shown in Table 3-2. Note that the least significant bit of the Low Page resister is dropped in 16-bit shifted mode.

Table 3-2

| Output<br>Address | 8-Bit I/O<br>Programmed<br>Address | 16-Bit I/O<br>Programmed<br>Address<br>(Shifted) | 32-Bit I/O<br>Programmed<br>Address | 16-Bit I/O<br>Programmed<br>Address<br>(No Shift) |  |

|-------------------|------------------------------------|--------------------------------------------------|-------------------------------------|---------------------------------------------------|--|

| AO                | A0                                 | "0"                                              | A0                                  | A0                                                |  |

| A < 16:1>         | A < 16:1 >                         | A < 15:0 >                                       | A < 16:1 >                          | A < 16:1 >                                        |  |

| A < 31:17 >       | A < 31:17 >                        | A<31:17>                                         | A < 31:17 >                         | A < 31:17 >                                       |  |

<sup>\*</sup> PC AT is a trademark of IBM.

## 3.7.5 CURRENT WORD REGISTER (READ/WRITE)

Each channel has a 24-bit Current Word Count register. This register determines the number of transfers to be performed. The actual number of transfers will be one more than the number programmed in the Current Word Count register (i.e., programming a count of 100 will result in 101 transfers). The word count is decremented after each transfer. The intermediate value of the word count is stored in the register during the transfer. When the value in the register goes from zero to 0FFFFFFH, a TC will be generated.

Following the end of a DMA service it may also be re-initialized by an Autoinitialization back to its original value. Autoinitialize can occur only when a TC occurs. If it is not Autoinitialized, this register will have a count of FFFFFFH after TC.

To maintain compatibility with the 82C37, programming either the low byte, bits<7:0>, or the middle byte, bits<15:8>, will clear the high byte bits<23:16>. This provides compatibility with the previous software that does not know of the existence of the upper byte of the word count.

When the Extended Mode register is programmed for, or defaulted to, transfers to/from an 8-bit I/O, the Word count will indicate the number of bytes to be transferred.

When the Extended Mode register is programmed for, or defaulted to, transfers to/from a 16-bit I/O, with shifted address, the Word count will indicate the number of 16-bit words to be transferred.

When the Extended Mode register is programmed for transfers to/from a 16- or 32-bit I/O, the Word Count will indicate the number of bytes to be transferred. The number of bytes does not need to be a multiple of two or four in this case.

## 3.7.6 BASE PAGE, BASE ADDRESS AND BASE WORD COUNT REGISTERS (WRITE ONLY)

Each channel has a set of Base Page, Base Address and Base Word Count registers. These registers store the original value of their associated Current registers. During Autoinitialize these values are used to restore the Current registers to their original values. The Base registers are written simultaneously with their corresponding Current register in 8-bit bytes in the Program Condition by the microprocessor. These registers cannot be read by the microprocessor.

During Chaining Mode, these registers will store the information about the next buffer in the Chain, if programmed.

### 3.7.7 COMMAND REGISTER (WRITE ONLY)

This 8-bit register controls the operation of the DMA. It is programmed by the microprocessor in the Program Condition and is cleared by Reset or a Master Clear instruction. Figure 3-4 lists the function of the command bits.

Figure 3-4. Command Register (Write Only)

1-236

## 3.7.8 MODE REGISTER (WRITE ONLY)

Each channel has a 6-bit Mode register associated with it. When the register is being written, bits 0 and 1 determine which channel is to be selected. This register is reset upon RST and Master Clear. Its reset value is Verify transfer, Autoinitialize disable, Address increment, Demand mode. Channel 4 defaults to cascade mode. (See Figure 3-5.)

Figure 3-5. Mode Register (Write Only)

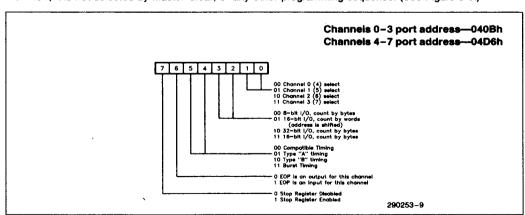

### 3.7.9 EXTENDED MODE REGISTERS (WRITE ONLY)

Each channel has a 16-bit Extended Mode register associated with it. The register is used to program the DMA device data size and timing mode. When the register is being written, bits 0 and 1 determine which channel is to be selected.

The default programmed values for channels 0-3 are, 8-bit I/O Count by Bytes, Compatible timing, EOP output and Stop registers disabled. The default values for channels 4-7 are, 16-bit I/O Count by Words with shifted address, Compatible timing, EOP output and Stop register disabled. The default is selected upon reset with RST, it is not selected by Master Clear, or any other programming sequence. (See Figure 3-6.)

Figure 3-6. Extended Mode Registers (Write Only)

### 3.7.9.1 8-Bit I/O, "Count By Bytes" Mode

In 8-bit I/O, "count by bytes" mode, the address counter can be programmed to any address. The count register is programmed with the number of bytes minus 1 to transfer. In this mode, byte assembly/disassembly is not available (or necessary) so the timing used when 8- or 16-bit memory is sensed is compatible with the original ISA products.

## 3.7.9.2 16-Bit I/O, "Count By Words" (Address Shifted) Mode

In "count by words" mode (address shifted), the address counter can be programmed to any even address, but must be programmed with the address value shifted right by one bit. The Page registers are not shifted, this results in the least significant bit of the Low Page register being ignored. In this mode, burst timing and byte assembly/disassembly is not available so the timing used when 8- or 16-bit memory is sensed is compatible with the original ISA products. The Count register is programmed with the number of words minus 1 to be transferred.

## 3.7.9.3 16-Bit I/O, "Count By Bytes" Mode

In 16-bit "count by bytes" mode, the address counter can be programmed to any byte address. For most DMA devices, however, it should be programmed only to even addresses. If the address is programmed to an odd address, the DMA controller will do a partial word transfer during the first and last transfer if necessary. The bus controller logic will do the byte/word assembly necessary to read or write any size memory device and both the DMA and bus controllers support burst for this mode. In this mode, the Address register is incremented or decremented by two and the byte count is decremented by the number of bytes transferred during each bus cycle. The Count register is programmed with the number of bytes —1 to be transferred.

### 3.7.9.4 32-Bit I/O, "Count By Bytes" Mode

In 32-bit I/O "count by bytes" mode, the address counter can be programmed to any byte address. For most DMA devices, however, it should be programmed only to addresses evenly divisible by four.

If the address is programmed to a value that is not divisible by four, then the DMA controller will do partial transfers for the first and last transfers if necessary. The bus controller logic will do the byte/word assembly necessary to read or write any size memory device and both the DMA and bus controllers support burst for this mode. In this mode, the Address register is incremented or decremented by four and the byte count is decremented by the number of bytes transferred during each bus cycle. The Count register is programmed with the number of bytes minus 1 to be transferred.

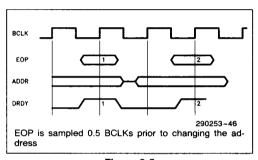

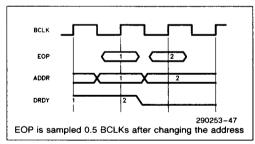

## 3.7.9.5 EOP Input/Output Selection

Bit 6 of the Extended Mode register selects whether the EOP signal is to be used as an input or an output during DMA transfers. The EOP I/O selection is programmable on a channel by channel basis. EOP will generally be used as an output, as was available on the PCAT. The input function was added to support Data Communication and other devices that would like to trigger an autoinitialize when a collision or some other event occurs. The direction of EOP is switched when DACK# is changed. There may be some overlap of the ISP driving the EOP signal along with the DMA slave, however, during this overlap both devices will be driving the signal to a low level (inactive).

#### 3.7.9.6 Stop Register Selection

Bit 7 of this register selects whether the Stop registers associated with this channel are to be used or not. Normally the Stop Registers will not be used. This function was also added to help support Data Communication or other devices that work from a Ring Buffer in memory (refer to Section 3.7.1).

### 3.7.9.7 Summary of the DMA Transfer Sizes

Table 3-3 lists each of the DMA device transfer sizes. The column labeled "Word Count register" indicates that the register contents represents either the number of bytes to transfer or the number of 16-bit words to transfer. The column labeled "Current Address Register Increment/Decrement" indicates the number added to or taken from the Current Address register after each DMA transfer cycle. The Mode Register determines if the Current Address register will be incremented or decremented.

Table 3-3

| DMA Device Data Size<br>and Word Count       | Word Count<br>Register | Current Address<br>Increment/Decrement |  |  |

|----------------------------------------------|------------------------|----------------------------------------|--|--|

| 8-Bit I/O, Count by Bytes                    | Bytes                  | 1                                      |  |  |

| 16-Bit I/O, Count by Words (Address Shifted) | Words                  | 1                                      |  |  |

| 16-Bit I/O, Count by Bytes                   | Bytes                  | 2                                      |  |  |

| 32-Bit I/O, Count by Bytes                   | Bytes                  | 4                                      |  |  |

1-238

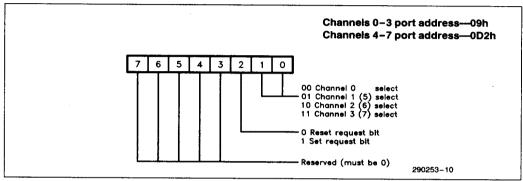

## 3.7.10 REQUEST REGISTER (WRITE ONLY)

Each channel has a Request bit associated with it in one of the two 4-bit Request registers. The Request register is used by software to initiate a DMA request. The DMA responds to the software request as though DREQ<x> is active. These requests are non-maskable and subject to prioritization by the Priority Encoder network (refer to Section 3.4). Each register bit is set or reset separately under software control or is cleared upon generation of a TC. The entire register is cleared upon RST, it is not cleared upon a RSTDRV output. To set or reset a bit, the software loads the proper form of the data word. When the register is being written, bits 0 and 1 determine which channel is to be selected. In order to make a software request, the channel must be in Block Mode. (See Figure 3-7.)

Figure 3-7. Request Register (Write Only)

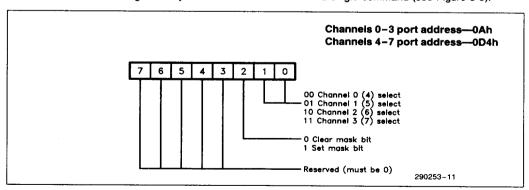

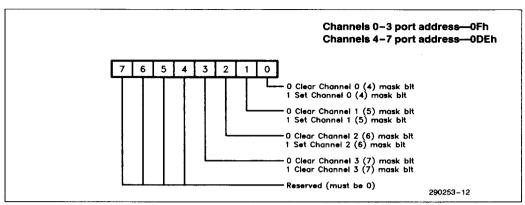

### 3.7.11 MASK REGISTER

Each channel has associated with it a mask bit which can be set to disable the incoming DREQ. Each mask bit is automatically set when the Current Word Count register reaches terminal count (unless the channel is programmed for autoinitialization or chaining mode). Each bit of the two, 4-bit registers may also be set or cleared under software control. The entire register is also set by a RESET and Master Clear. This disables all DMA requests until a clear Mask register instruction allows them to occur. The instruction to separately set or clear the mask bits is similar in form to that used with the Request register. (See Figure 3-8.)

## NOTE:

If the channel 4 mask bit is set, the channels logically cascaded into it are also masked.

All four bits of the Mask register may also be read or written with a single command (see Figure 3-9).

Figure 3-8. Write Single Mask Bit (Write Only)

1-239

Figure 3-9. Write All Mask Register Bits (Read/Write)

### 3.7.12 STATUS REGISTER (READ ONLY)

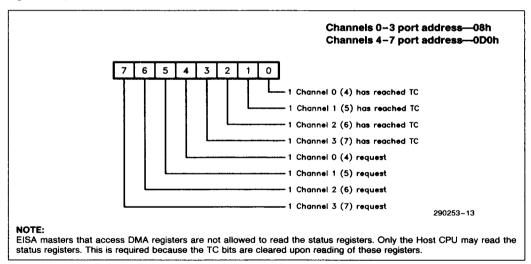

The Status register contains information about the status of the devices that may be read by the CPU. This information includes which channels have reached a terminal count and which channels have pending DMA requests. Bits 0-3 are set every time a TC is reached by that channel. These bits are cleared upon Reset and on each Status Read. Bits 4-7 are set whenever their corresponding channel is requesting service. (See Figure 3-10.)

Figure 3-10. Status Register (Read Only)

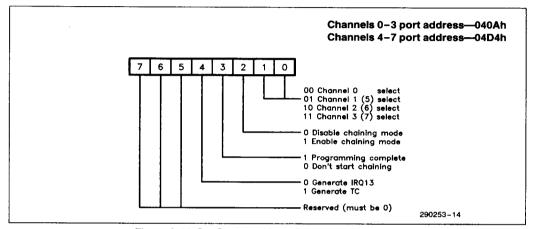

## 3.7.13 SET CHAINING MODE REGISTER (WRITE ONLY)

Each channel has a Chaining Mode register associated with it. The Chaining Mode register is used to enable or disable DMA buffer chaining and to indicate when the DMA Base registers are being programmed. When the register is being written, bits 0 and 1 determine which channel is to be selected. The chaining status and interrupt status for all channels can be determined by reading the Set Chaining Mode Status, Channel Interrupt Status, and Chain Buffer Expiration Control registers. The Chaining Mode register is reset to zero upon RST, access (read or write) of a channel's Mode register or Extended Mode register, or a Master Clear. The values upon reset are disable chaining mode and generate IRQ13. (See Figure 3-11.)

Refer to "Buffer Chaining" section for additional information about Buffer Chaining.

Figure 3-11. Set Chaining Mode Register (Write Only)

The **Enable Chaining mode** bit is used to control the chaining mode logic. If the bit is programmed to a 1 after the initial DMA address and count are programmed, then the Base address and Count registers will become available for programming the next chain buffer.

After the Base registers are programmed (as indicated above), the **Enable Chaining mode** and the **Programming Complete** bits are set to begin a DMA chaining sequence. The DMA channel is then ready to begin transferring data (assuming the mask bit is cleared).

When a chaining mode interrupt or TC (for EISA programming masters) occurs, the next Address and Count registers should be programmed and the **Programming Complete** bit should be set to set up for the next transfer. When the Programming Complete bit is set, the Enable Chaining Mode bit and the Generate IRQ bit both need to be written to the correct state. Upon this programming the interrupt request for that channel is reset, if it was active.

Bit 4 of the Set Chaining Mode register is used to determine the response to the expiration of a DMA buffer. Normally the Host CPU needs to be informed to program the next set of Base registers. In this case bit 4 should be set to a zero to generate an IRQ13. If an EISA bus master is using the DMA to assist in data transfer, then bit 4 can be set to a 1 to generate an EOP(TC) instead of an IRQ13. The EISA master can then use the EOP(TC) in the same way that the CPU uses an interrupt. In this mode the EOP signal will only be driven active while the Channel that caused it is running as determined by the DACK lines.

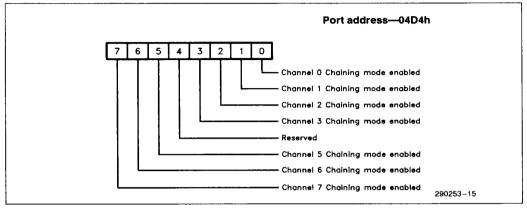

### 3.7.14 SET CHAINING MODE STATUS REGISTER (READ ONLY)

This register is read only and is used to determine if Chaining mode for a particular channel is enabled or disabled. A "1" read in this register indicates that the channel's chaining mode is enabled. A "0" indicates that the chaining mode is disabled. All Chaining mode bits are disabled after a reset. After the DMA is used in Chaining mode the CPU will need to clear the Chaining mode enable bit if non-Chaining mode is desired. This bit is programmed in bit 2 of the Set Chaining Mode register. (See Figure 3-12.)

Figure 3-12. Set Chaining Mode Status Register (Read Only)

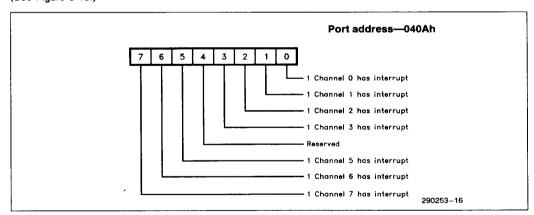

## 3.7.15 CHANNEL INTERRUPT STATUS REGISTER (READ ONLY)

Channel Interrupt Status is a read only register and is used to indicate the source (channel) of a DMA chaining interrupt on IRQ13. The DMA controller drives IRQ13 active after reaching terminal count, with chaining mode enabled. It does not drive IRQ13 active during the initial programming sequence that loads the Base registers. (See Figure 3-13.)

Figure 3-13. Channel Interrupt Status Register (Read Only)

## 3.7.16 CHAIN BUFFER EXPIRATION CONTROL REGISTER (READ ONLY)

This register is read only and reflects the outcome of the expiration of a chain buffer. If a channel bit is set to a 0, IRQ13 will be activated, otherwise a TC will be issued. This bit is programmed in bit 4 of the Set Chaining Mode register. (See Figure 3-14.)

### 3.8 Software Commands

These are additional special software commands which can be executed in the Program Condition. They do not depend on any specific bit pattern on the data bus. The three software commands are: (1) Clear Byte Pointer Flip-Flop (2) Master Clear and (3) Clear Mask Register.

## 3.8.1 CLEAR BYTE POINTER FLIP-FLOP

This command is executed prior to writing or reading new address or word count information to the DMA. This initializes the flip-flop to a known state so that subsequent accesses to register contents by the microprocessor will address upper and lower bytes in the correct sequence.

When the Host CPU is reading or writing DMA registers, two Byte Pointer Flip-Flops are used; one for channels 0-3 and one for channels 4-7. Both of these act independently. There are separate software commands for clearing each of them (0Ch for Channels 0-3, 0D8h for Channels 4-7).