**Preliminary Information**

#### **Preliminary Information**

#### © 1999 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, AMD Athlon, and combinations thereof, AMD-750, AMD-751, and AMD-756 are trademarks of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

## Contents

| 1 | Features   |         |                                                                                                                                                                                                                                                                                                                        | 1                          |

|---|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   |            | 1.1     | PCI-to-ISA Bridge                                                                                                                                                                                                                                                                                                      | . 3                        |

|   |            | 1.2     | Enhanced IDE Controllers                                                                                                                                                                                                                                                                                               | . 3                        |

|   |            | 1.3     | Universal Serial Bus Controller                                                                                                                                                                                                                                                                                        | . 4                        |

|   |            | 1.4     | Plug-n-Play Support                                                                                                                                                                                                                                                                                                    | . 4                        |

|   |            | 1.5     | Power Management                                                                                                                                                                                                                                                                                                       | . 4                        |

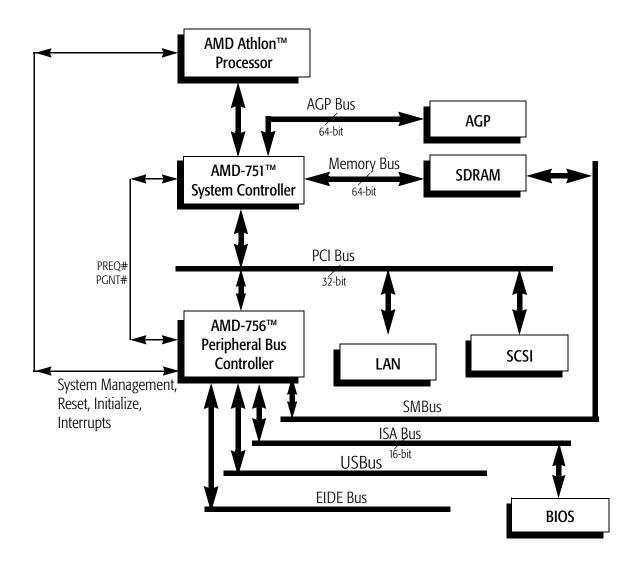

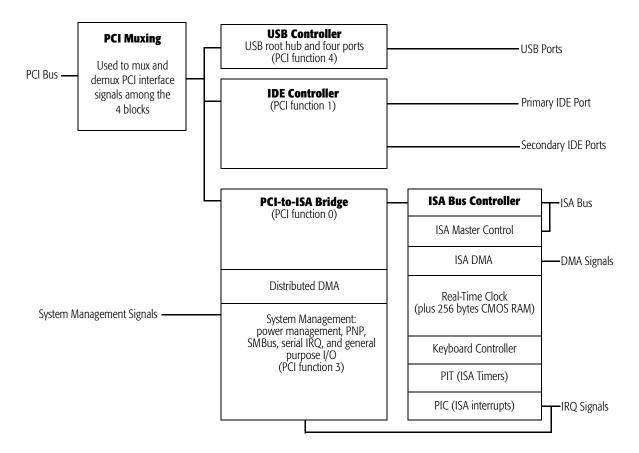

| 2 | Overview   |         |                                                                                                                                                                                                                                                                                                                        | 7                          |

|   |            | 2.1     | PCI-to-ISA Bridge                                                                                                                                                                                                                                                                                                      | . 9                        |

|   |            |         | 2.1.1PCI Bus Master Mode2.1.2PCI Bus Target Mode                                                                                                                                                                                                                                                                       |                            |

|   |            | 2.2     | ISA Bus Controller                                                                                                                                                                                                                                                                                                     | 11                         |

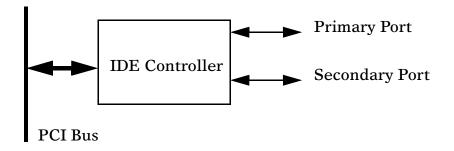

|   |            | 2.3     | EIDE Controller                                                                                                                                                                                                                                                                                                        | 12                         |

|   |            | 2.4     | Universal Serial Bus (USB)                                                                                                                                                                                                                                                                                             | 13                         |

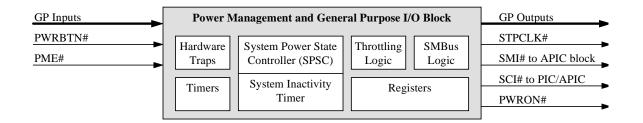

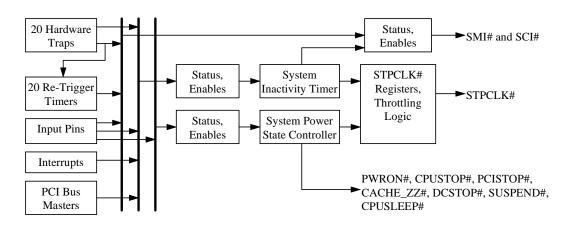

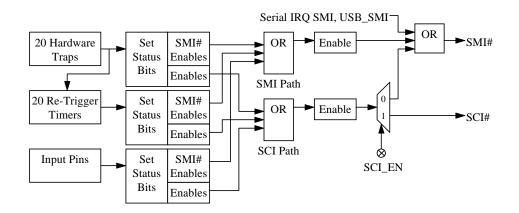

|   |            | 2.5     | Power Management                                                                                                                                                                                                                                                                                                       | 13                         |

| 3 | Ordering   | nform   | ation                                                                                                                                                                                                                                                                                                                  | 15                         |

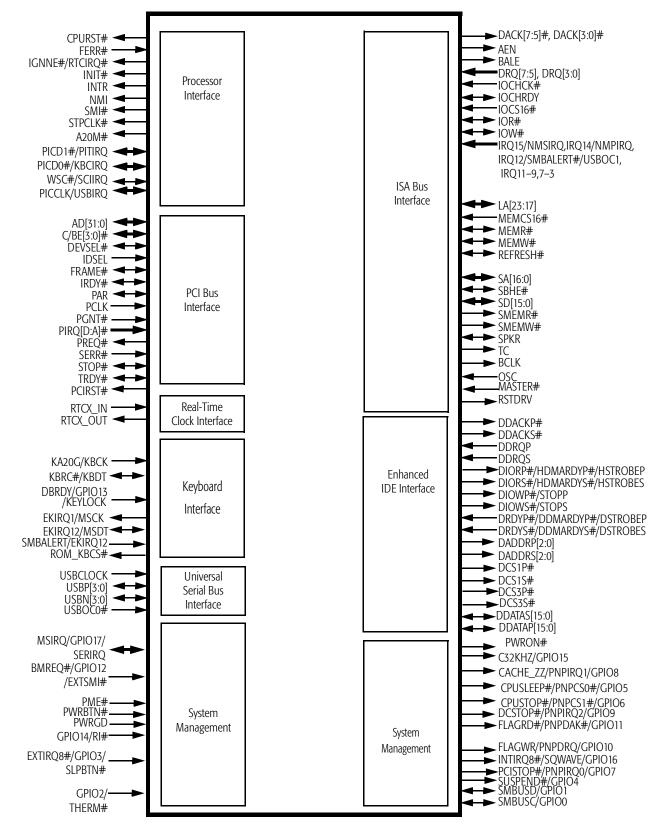

| 4 | Signal Des | criptio | ons                                                                                                                                                                                                                                                                                                                    | 17                         |

|   |            | 4.1     | Signal Terminology                                                                                                                                                                                                                                                                                                     | 17                         |

|   |            | 4.2     | Processor Interface                                                                                                                                                                                                                                                                                                    | 18                         |

|   |            |         | <ul> <li>4.2.1 A20M# (Processor A20 Mask)</li> <li>4.2.2 CPURST# (Processor Reset)</li> <li>4.2.3 FERR# (Floating Point Error)</li> <li>4.2.4 IGNNE# (Ignore Numeric Exception)</li> <li>4.2.5 INIT# (Initialization)</li> <li>4.2.6 INTR (Processor Interrupt)</li> <li>4.2.7 NMI (Non-Maskable Interrupt)</li> </ul> | 18<br>18<br>19<br>19<br>19 |

|     | 4.2.8  |                                                                                                        |      |

|-----|--------|--------------------------------------------------------------------------------------------------------|------|

|     | 4.2.9  |                                                                                                        |      |

|     |        | PICD0# and PICD1# (Interrupt Message Data Bits)                                                        |      |

|     |        | WSC# (Write Snoop Complete)                                                                            |      |

|     | 4.2.12 | STPCLK# (Stop Clock)                                                                                   | 21   |

| 4.3 | PCI B  | us Interface                                                                                           | . 22 |

|     | 4.3.1  | AD[31:0] (PCI Address/Data Bus) Summary                                                                |      |

|     | 4.3.2  | C/BE[3:0]# (PCI Command/Byte Enable)                                                                   |      |

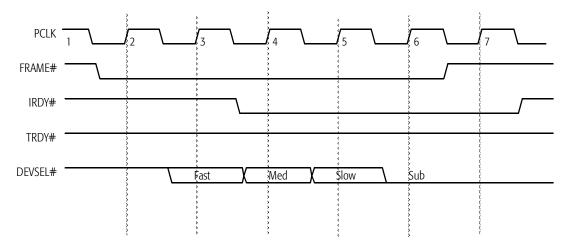

|     | 4.3.3  | DEVSEL# (PCI Bus Device Select)                                                                        |      |

|     | 4.3.4  | FRAME# (PCI Bus Cycle Frame)                                                                           |      |

|     | 4.3.5  | IDSEL (PCI Initialization Device Select)                                                               |      |

|     | 4.3.6  | IRDY# (PCI Bus Initiator Ready)                                                                        |      |

|     | 4.3.7  | PAR (PCI Bus Parity)                                                                                   |      |

|     | 4.3.8  | PCIRST# (PCI Reset)                                                                                    | 26   |

|     | 4.3.9  | PCLK (PCI Bus Clock)                                                                                   | 26   |

|     |        | PGNT# ( <i>PCI Grant</i> )                                                                             |      |

|     | 4.3.11 | PIRQ[D:A]# (PCI Interrupt Requests)                                                                    | 27   |

|     | 4.3.12 | PREQ# ( <i>PCI Request</i> )                                                                           | 27   |

|     | 4.3.13 | SERR# (System Error)                                                                                   | 27   |

|     | 4.3.14 | STOP# ( <i>Stop</i> )                                                                                  | 28   |

|     | 4.3.15 | TRDY# (PCI Target Ready)                                                                               | 28   |

| 4.4 | ISA B  | us Interface                                                                                           | . 29 |

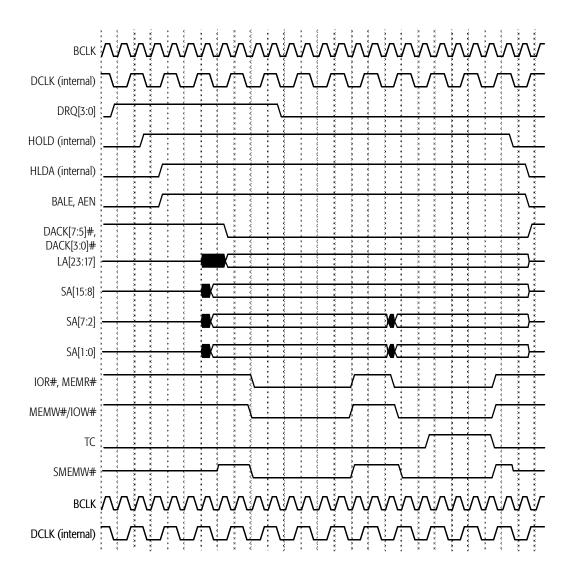

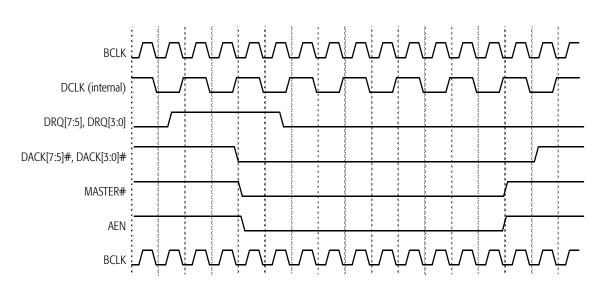

|     | 4.4.1  | AEN (Address Enable)                                                                                   | 29   |

|     | 4.4.2  | BALE (Bus Address Latch Enable)                                                                        | 29   |

|     | 4.4.3  | BCLK (Bus Clock)                                                                                       | 29   |

|     | 4.4.4  | DACK[7:5]#, DACK[3:0]# (DMA Acknowledge)                                                               |      |

|     | 4.4.5  | DRQ[7:5], DRQ[3:0] (DMA Request)                                                                       | 30   |

|     | 4.4.6  | IOCHCK# (I/O Channel Check)                                                                            |      |

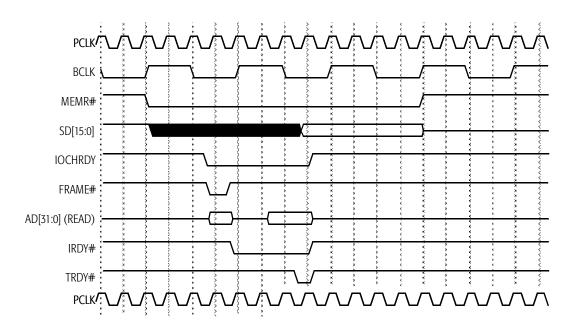

|     | 4.4.7  | IOCHRDY (I/O Channel Ready)                                                                            |      |

|     | 4.4.8  | IOCS16# (16-Bit I/O Chip Select)                                                                       |      |

|     | 4.4.9  | IOR# (I/O Read)                                                                                        |      |

|     | 4.4.10 | IOW# (I/O Write)                                                                                       |      |

|     |        | IRQ15, IRQ14, IRQ[12:9], IRQ[7:3] (Interrupt Requests)                                                 |      |

|     |        | NMPIRQ (Native Mode Primary IDE Port IRQ)                                                              |      |

|     |        | NMSIRQ (Native Mode Secondary IDE Port IRQ)                                                            |      |

|     |        | LA[23:17] (Unlatched Address)                                                                          |      |

|     |        | MASTER# (ISA Master Cycle Indicator)                                                                   |      |

|     |        | MEMCS16# (16-Bit Memory Chip Select)                                                                   |      |

|     |        | MEMR# (Memory Read)                                                                                    |      |

|     |        | MEMW# (Memory Write)                                                                                   |      |

|     |        | OSC (Oscillator)                                                                                       |      |

|     |        | REFRESH# (Refresh)                                                                                     |      |

|     |        | ROM_KBCS# (ROM and Keyboard Chip Select)                                                               |      |

|     |        | RSTDRV (Reset Drive)                                                                                   |      |

|     | 7.7.44 | $\mathbf{M} = \mathbf{M} \mathbf{M} \mathbf{M} \mathbf{M} \mathbf{M} \mathbf{M} \mathbf{M} \mathbf{M}$ |      |

|     | 4.4.24<br>4.4.25<br>4.4.26 | SA[16:0] (System Address Bus)SBHE# (System Byte High Enable)SD[15:0] (ISA System Data)SMEMR# (Standard Memory Read)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36<br>36<br>36 |

|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|     |                            | SMEMW# (Standard Memory Write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|     |                            | SPKR (Speaker)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|     | 4.4.29                     | TC (Terminal Count)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37             |

| 4.5 | Ultra                      | DMA Enhanced IDE Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38             |

|     | 4.5.1                      | DADDRP[2:0] (Primary IDE Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38             |

|     | 4.5.2                      | DADDRS[2:0] (Secondary IDE Address)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 38             |

|     | 4.5.3                      | DCS1P# (Primary Port Chip Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38             |

|     | 4.5.4                      | DCS1S# (Secondary Port Chip Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39             |

|     | 4.5.5                      | DCS3P# (Primary Port Chip Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39             |

|     | 4.5.6                      | DCS3S# (Secondary Port Chip Select)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|     | 4.5.7                      | DDATAP[15:0] (Primary IDE Data Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|     | 4.5.8                      | DDATAS[15:0] (Secondary IDE Data Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|     | 4.5.9                      | DDACKP# (Primary IDE DMA Acknowledge)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

|     | 4.5.10                     | DDACKS# (Secondary IDE DMA Acknowledge)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41             |

|     |                            | DDMARDYP# (Primary Device DMA Ready,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

|     |                            | Ultra DMA Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41             |

|     | 4.5.12                     | DDMARDYS# (Secondary Device DMA Ready,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|     | UltraI                     | DMAMode) 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|     | 4.5.13                     | DDRQP (Primary IDE DMA Request)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41             |

|     |                            | DDRQS (Secondary IDE DMA Request)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|     |                            | DIORP# (Primary I/O Read)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

|     | 4.5.16                     | DIORS# (Secondary I/O Read)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42             |

|     |                            | DIOWP# (Primary I/O Write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

|     |                            | DIOWS# (Secondary I/O Write)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|     |                            | DRDYP# (Primary Device Ready)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

|     |                            | DRDYS# (Secondary Device Ready)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|     |                            | DSTROBEP (Primary Device Strobe, Ultra DMA Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|     |                            | DSTROBES (Secondary Device Strobe, Ultra DMA Mode) .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |